## ENTIRE LOAD EFFICIENCY AND DYNAMIC PERFORMANCE IMPROVEMENTS FOR DC-DC CONVERTERS

by

OSAMA A. ABDEL-RAHMAN B.S. Princess Sumaya University for Technology, 2003 M.S. University of Central Florida, 2005

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2007

Major Professor: Issa Batarseh

UMI Number: 3256902

#### UMI Microform 3256902

Copyright 2007 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 © 2007 OSAMA A. ABDEL-RAHMAN

To my parents

#### **ABSTRACT**

Demands for DC-DC converters are continuously increasing for the application in many areas such as telecommunications, cellular telephones, networking products, notebook and desktop computers, industrial instrumentation, and automotive electronics. These areas are continually being upgraded with regard to their specifications and power requirements; this puts the emphasis on power electronics and power management. DC-DC converters are able to supply energy at high standards and specifications, which leads DC-DC converters to be continually upgraded in order to fulfill other application requirements such as efficiency, dynamic performance, thermo, noise and size.

The scope of this work can be summarized into three main aspects for DC-DC power converters. The first aspect is soft switching topologies to improve conversion efficiency for On-Board Converters or Point of load (POL) converters (chapters 2, 3); the second aspect is load adaptive control techniques to improve all load efficiency for battery powered DC-DC converters that are applied to mobile devices (chapters 4, 5); and the third aspect is dynamic performance control techniques to improve load transient in voltage regulators (chapters 6, 7). Topologies and control techniques for DC-DC converters are presented after reviewing loads powering requirements and steady-state and transients design challenges.

Following is a quick overview of the presented topologies and control techniques that sum up the work of this research:

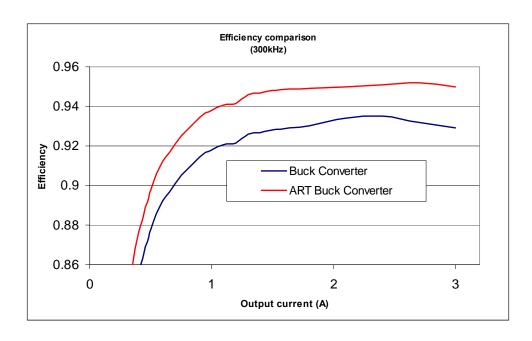

- In chapter 2, Active Resonant Tank (ART) cells are presented to achieve Zero-Voltage-Switching (ZVS) and eliminate body-diode conduction and its reverse recovery in dc-dc converters with Synchronous Rectifiers (SRs). ART cells extend the benefits of utilizing SRs to higher voltage applications, since switching losses tend to be more significant in higher voltage ratings SRs because they have worse parasitic. The concept of current injection in ART cells is generally introduced and detailed analyses are provided based on a buck converter. Experimental results show that efficiency improvement is achieved due to the reduced switching loss, body diode's conduction, and reverse-recovery loss.

- In chapter 3, LCC ZVS Buck Converter with Synchronous Rectifier is presented. The concept of the LCC ZVS buck converter topology introduces an inductive load in the bridge leg and changes the switching commutation mechanism of the SR to achieve Zero-Voltage-Switching (ZVS) and eliminate body-diode conduction and its reverse. Compared with the conventional SR buck converter, reverse-recovery-related switching and ringing loss are eliminated; compared with QSW buck converter, the output current ripple is significantly reduced and the output capacitance is dramatically reduced.

- In chapter 4, load Adaptive Control for Improved Light Load Efficiency and Performance of Voltage Regulator (VR) is presented. Analytical studies of VR losses and voltage ripple deviation are presented and discussed, yielding to proposed control technique, namely "Pulse Sliding\*\*" (PSL) control technique, which results in improved VR conversion efficiency with low and controlled voltage ripple and improved dynamic

response. The presented control method achieves the advantages of both variable frequency and fixed frequency controls and eliminates their disadvantages by utilizing information obtained from the inductor peak current, compensation error signal and output capacitor current, resulting in an optimum non-linear switching frequency modulation. PSL is compared with other control methods by both analyses and experiments.

- In chapter 5, a load adaptive voltage regulator that achieves high efficiency extended to light and heavy load regions is presented. It is named as "Adaptive FET Modulation" (AFM) since multiple FETs with different specifications are paralleled; the number of driven FETs and their gate driving voltage are adaptive to load current. The capability of adaptive modulation of FETs' parasitic charges and resistances along with adaptive gate driving voltage allows achieving the best FET optimization for wide load range. AFM operates at fixed switching frequency for almost the whole load range, so it has no affect on the conventional buck operation and its dynamic performance, in addition to having simple implementation.

- In chapter 6, the discussion centers upon a control method that dynamically modulates the PWM ramp signal peak during DCM or Mode Hoping operation with inverse relationship to the compensator error signal, as a result modulate the PWM modulator gain to minimize the required error signal change during load transient, so that the

compensator reaches steady state faster and lower output voltage deviation during load transient is achieved.

- In chapter 7, an approach to significantly limit the voltage overshoot and undershoot during load transient and reduces the number of capacitors, without compromising on the efficiency, cost or size of the dc/dc converter. It allows optimization of power stage efficiency for the dc operation with less concern of dynamic performance, while an additional switching circuit; that utilizes the output capacitor current to rapidly detect load transient; is activated during load step up to deliver the shortage charge to the output capacitor, and to pull out the extra charge from the output capacitor during load step down. Therefore, lower voltage deviation is achieved during load transient.

- Finally, the work is summarized and concluded, and references are listed

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to my advisor, Professor Issa Batarseh, for his assistance and support and his efforts to plant the seeds of this work. His personality, directing experience and critical thinking were an example for me to follow.

I would like to thank Dr. Hong Mao for his training and advising, the members of the Intel team for their support, including: Dr. Lilly Huang, Dr. Jaber Abu-Qahouq and Alan Hallberg, and the ASTEC/Emerson team for their support, including: Dr. Hong Mao, Mr. Geof Potter and Mr. Brad Higgins.

Special thanks are also extended to this dissertation approval committee: Professor Issa Batarseh, Professor Wasfy Mikhael, Dr. John Shen, Dr. Yan Fe Lui, and Dr. Jaber Abu-Qahouq. I would like to express my appreciation to other members and colleagues at the Power Electronics Laboratory. I am also grateful for all my friends.

I am grateful to the University of Central Florida faculty and staff for their cooperation.

Finally, I would like to express my undying love and gratitude to my mother Muyasar, my father Adel, my sister Inas, my brothers Iyas and Ahmad, and last but not least, my lovely wife Cherine and her family, whose love, encouragement and support have been the root of my success.

This work is supported partially by several agencies and companies including Intel Corp., ASTEC Power/Emerson, and the University of Central Florida.

Osama Abdel-Rahman

*May 2007*

## **TABLE OF CONTENTS**

| LIST OF | FIGURESXIV                                                                     |

|---------|--------------------------------------------------------------------------------|

| LIST OF | TABLESXX                                                                       |

| СНАРТЕ  | R 1: INTRODUCTION1                                                             |

| 1.1     | Soft switching topologies                                                      |

|         | 1.1.1 Literature review of soft switching topologies                           |

|         | 1.1.2 Proposed soft switching topologies                                       |

|         | 1.1.2.1 Active Resonant Tank (ART) for zero-voltage-switching DC-              |

|         | DC converters with synchronous rectifiers 6                                    |

|         | 1.1.2.2 LCC ZVS buck converter with synchronous rectifier                      |

| 1.2     | All load efficiency improvement control techniques                             |

|         | 1.2.1 Literature review of all load efficiency improvement techniques          |

|         | 1.2.2 Proposed load adaptive techniques for all load efficiency improvement 13 |

|         | 1.2.2.1 On load adaptive control of voltage regulators for power               |

|         | managed loads: control schemes to improve converter                            |

|         | efficiency and performance                                                     |

|         | 1.2.2.2 Adaptive FET modulation for voltage regulator efficiency               |

|         | improvement                                                                    |

| 1.3     | Dynamic performance improvement methods                                        |

|         | 1.3.1 Literature review of dynamic performance improvement methods             |

|         | 1.3.2 Proposed dynamic performance improvement methods                         |

|     |      | 1.3.2.1 Dynamic PWM ramp signal to improve load transient in DCM |    |

|-----|------|------------------------------------------------------------------|----|

|     |      | and Mode-Hoping operation                                        | 16 |

|     |      | 1.3.2.2 Transient response improvement in DC-DC converters using |    |

|     |      | output capacitor current for faster transient detection          | 16 |

| CHA | APTE | R 2: ACTIVE RESONANT TANK (ART) FOR ZERO-VOLTAGE-                |    |

|     |      | SWITCHING DC-DC CONVERTERS WITH SYNCHRONOUS                      |    |

|     |      | RECTIFIERS                                                       | 18 |

|     | 2.1  | General concept                                                  | 18 |

|     | 2.2  | Current injection cell to achieve zero-voltage-switching (ZVS)   | 21 |

|     | 2.3  | Implementation of the current injection cell with (ART)          | 22 |

|     | 2.4  | Modes of operation analyses                                      | 24 |

|     | 2.5  | Features and design considerations                               | 37 |

|     | 2.6  | Topology derivation                                              | 40 |

|     | 2.7  | Experimental results                                             | 42 |

|     | 2.8  | Conclusion                                                       | 47 |

| CHA | APTE | R 3: LCC ZVS BUCK CONVERTER WITH SYNCHRONOUS                     |    |

|     |      | RECTIFIER                                                        | 48 |

|     | 3.1  | General concept                                                  | 48 |

|     | 3.2  | Converter description and modes of operation                     | 49 |

|     | 3.3  | Losses and ripple analyses                                       | 55 |

|     | 3.4  | Design considerations                                            | 60 |

| 3.5    | Experimental results                                                      | 62  |

|--------|---------------------------------------------------------------------------|-----|

| 3.6    | Conclusion                                                                | 66  |

| СНАРТЕ | CR 4: ON LOAD ADAPTIVE CONTROL OF VOLTAGE                                 |     |

|        | REGULATORS FOR POWER MANAGED LOADS: CONTROL                               |     |

|        | SCHEMES TO IMPROVE CONVERTER EFFICIENCY AND                               |     |

|        | PERFORMANCE                                                               | 68  |

| 4.1    | VR Power Losses Study                                                     | 68  |

|        | 4.1.1 Quick overview on VR losses sources                                 | 68  |

|        | 4.1.2 Power loss effects as a function of the load                        | 70  |

| 4.2    | Studies on light load efficiency improvement techniques                   | 71  |

|        | 4.2.1 Mode-Hopping effect                                                 | 72  |

|        | 4.2.2 Linear variable frequency effect                                    | 73  |

| 4.3    | Output voltage ripple analyses                                            | 77  |

| 4.4    | Pulse-Sliding technique (PSL)                                             | 86  |

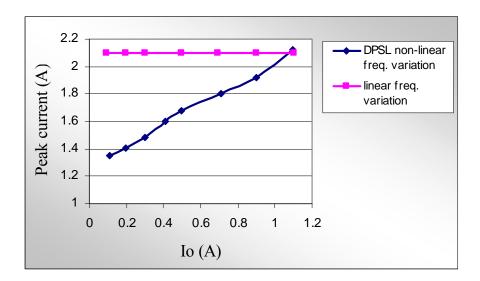

|        | 4.4.1 PSL with fixed current peak limiting (FPSL):                        | 88  |

|        | 4.4.2 PSL with dynamic current peak limiting (DPSL):                      | 91  |

| 4.5    | Input voltage feed forward to compensate for switching frequency drift at |     |

|        | variable line voltages                                                    | 94  |

| 4.6    | Frequency modulation effect on the transient response                     | 97  |

| 4.7    | Experimental results                                                      | 101 |

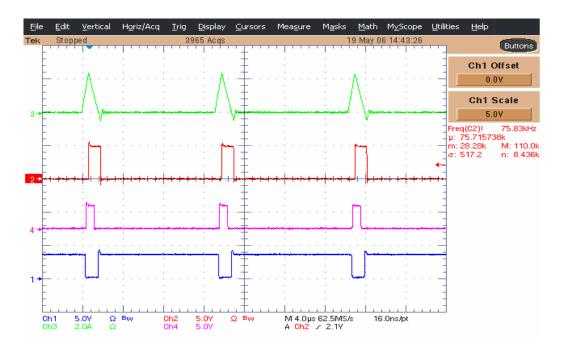

|        | 4.7.1 PSL logic circuit operation experimental results                    | 102 |

|        | 4.7.2 Peak current limit experimental results                             | 103 |

|                                                           | 4.7.3 Output voltage ripple experimental results                                                                                                                                                       |                             |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                                                           | 4.7.4 Frequency variation experimental results                                                                                                                                                         | 107                         |

|                                                           | 4.7.5 Efficiency experimental results                                                                                                                                                                  | 108                         |

|                                                           | 4.7.6 Transient response experimental results                                                                                                                                                          | 110                         |

|                                                           | 4.7.7 Closed loop Bode-Plots                                                                                                                                                                           | 112                         |

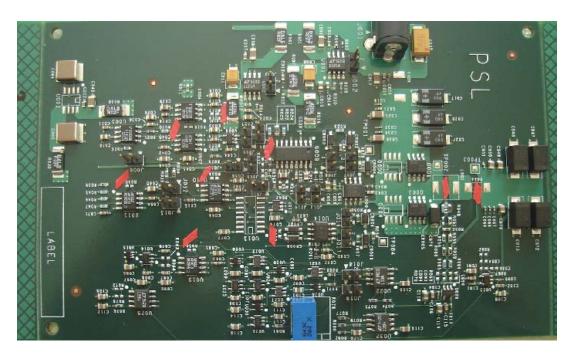

|                                                           | Figure 4.27 shows a picture of the prototype that was used to verify the                                                                                                                               |                             |

|                                                           | presented PSL concept and to obtain the experimental results presented                                                                                                                                 |                             |

|                                                           | above                                                                                                                                                                                                  | 113                         |

| 4.8                                                       | Conclusion                                                                                                                                                                                             | 114                         |

| CHAPTE                                                    | R 5: ANALYSES AND DESIGN OF ADAPTIVE FET MODULATION                                                                                                                                                    |                             |

|                                                           | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT                                                                                                                                                           | 116                         |

| 5.1                                                       |                                                                                                                                                                                                        |                             |

|                                                           | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT                                                                                                                                                           | 117                         |

| 5.1                                                       | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM                                                                                                                                           | 117<br>122                  |

| 5.1<br>5.2                                                | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses                                                                                                                            | 117<br>122<br>127           |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses  AFM implementation                                                                                                        | 117 122 127 131             |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses  AFM implementation.  Design considerations                                                                                | 117 122 127 131 136         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses                                                                                                                            | 117 122 127 131 136         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses  AFM implementation  Design considerations  Experimental results  Conclusion                                               | 117 122 127 131 136 142     |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                    | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses  AFM implementation  Design considerations  Experimental results  Conclusion  R 6: DYNAMIC PWM RAMP SIGNAL TO IMPROVE LOAD | 117 122 127 131 136 142     |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>CHAPTE</b>   | FOR VOLTAGE REGULATOR EFFICIENCY IMPROVEMENT  Concept of AFM  Loss analyses  AFM implementation  Design considerations  Experimental results  Conclusion  R 6: DYNAMIC PWM RAMP SIGNAL TO IMPROVE LOAD | 117 122 127 131 136 142 143 |

| 6.3    | Theoretical proof of load transient improvement | 146 |

|--------|-------------------------------------------------|-----|

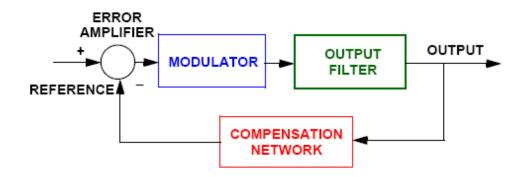

| 6.4    | Control loop analyses                           | 148 |

| 6.5    | Experimental results                            | 152 |

| 6.6    | Conclusion                                      | 157 |

| СНАРТЕ | R 7: TRANSIENT RESPONSE IMPROVEMENT IN DC-DC    |     |

|        | CONVERTERS USING OUTPUT CAPACITOR CURRENT FOR   |     |

|        | FASTER TRANSIENT DETECTION                      | 158 |

| 7.1    | Principle of operation and implementation.      | 158 |

| 7.2    | Experimental results                            | 162 |

| 7.3    | Conclusion                                      | 166 |

| СНАРТЕ | R 8: SUMMARY AND FUTURE RESEARCH WORK           | 167 |

| 8.1    | Summary                                         | 167 |

| 8.2    | Future research work                            | 170 |

| DEFEDE | NCES                                            | 173 |

## LIST OF FIGURES

| Fig. 1. 1: Example of Power Consumption Benchmark of an Intel Centrino® Mobile        |    |

|---------------------------------------------------------------------------------------|----|

| Technology based system under different usage and applications conditions:            |    |

| Top Curve for Platform Power and Bottom Curve for CPU Power.                          | 10 |

| Fig. 1. 2: (a) Buck VR and (b) Typical buck VR and efficiency curve.                  | 12 |

| Fig. 2. 1: Cells in non-isolated dc-dc converters                                     | 18 |

| Fig. 2. 2: Concept of current injection cell in a Buck converter                      |    |

| Fig. 2. 3: Key Concept of current injection cell.                                     | 20 |

| Fig. 2. 4: Active resonant tank (ART) cells                                           | 24 |

| Fig. 2. 5: Buck converter with ART cell.                                              | 25 |

| Fig. 2. 6: Equivalent circuits of modes of operation                                  | 35 |

| Fig. 2. 7: Key waveforms for Buck converter with ART cell.                            | 36 |

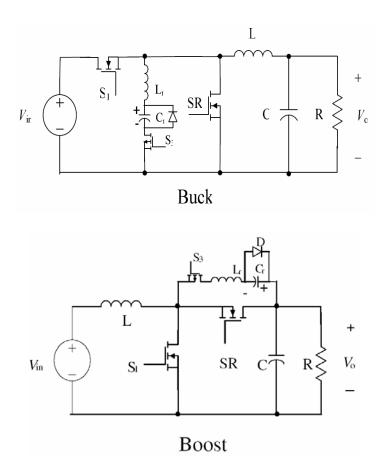

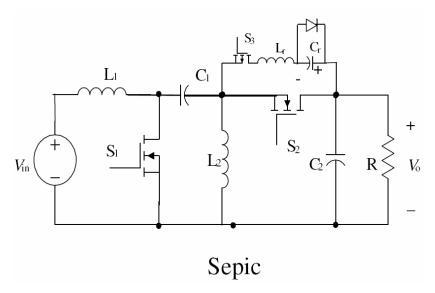

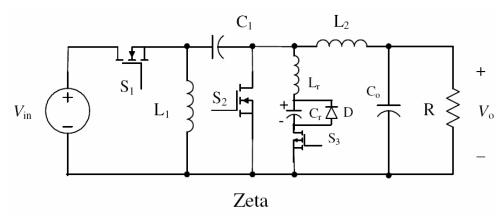

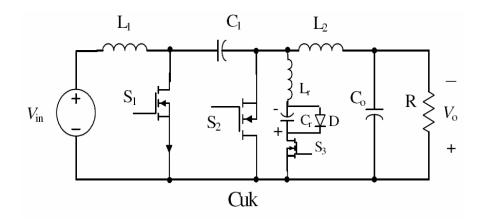

| Fig. 2. 8: ART concept applied to main non-isolated dc-dc converter topologies        | 42 |

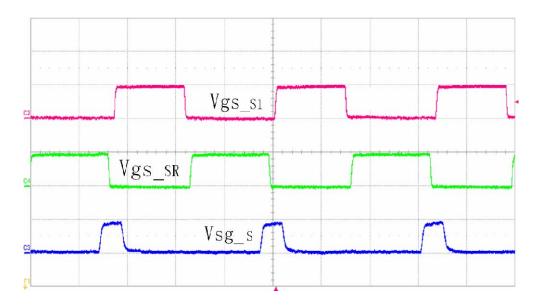

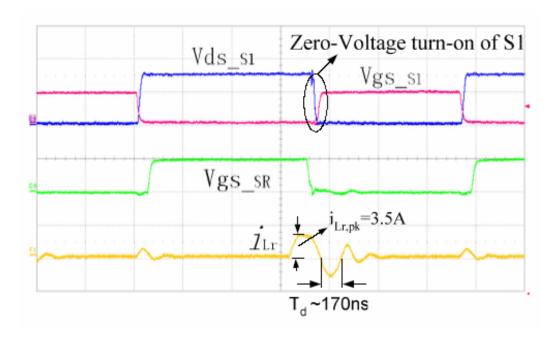

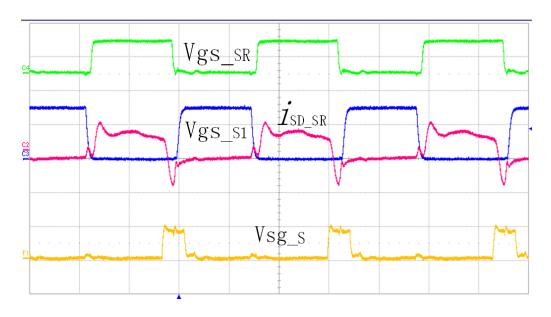

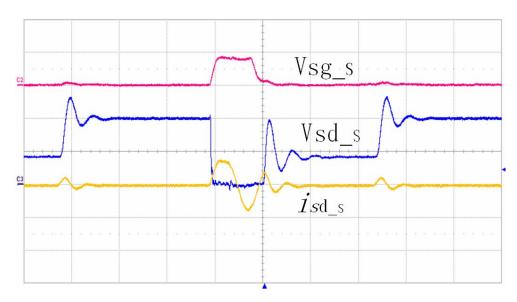

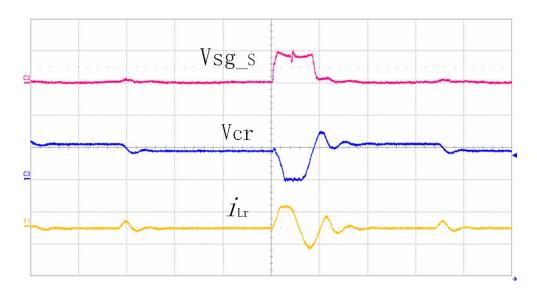

| Fig. 2. 9: Experimental waveforms                                                     | 46 |

| Fig. 2. 10: Efficiency comparison                                                     | 46 |

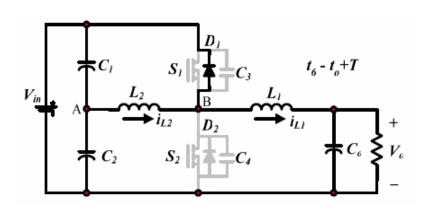

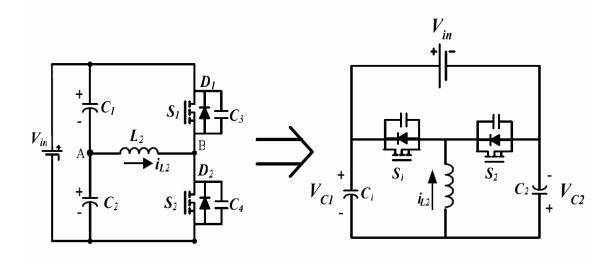

| Fig 3. 1: LCC ZVS buck converter                                                      | 49 |

| Fig 3. 2: Key waveforms.                                                              | 50 |

| Fig 3. 3: Modes of operation                                                          | 54 |

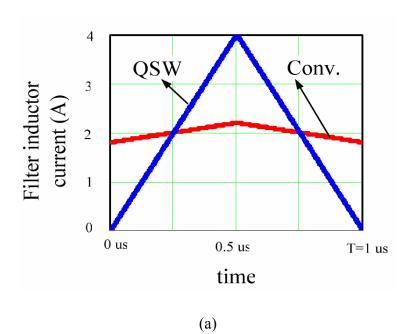

| Fig 3. 4: (a) current waveforms for QSW and conventional buck converters. (b) current |    |

| waveforms for LCC buck                                                                | 58 |

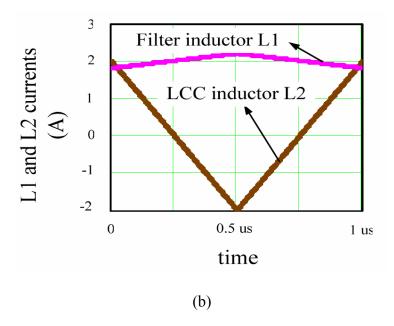

| Fig 3. 5: (a) Input current waveforms for the three converters. (b) Input rms current vs.   |    |

|---------------------------------------------------------------------------------------------|----|

| output current for the three converters.                                                    | 59 |

| Fig 3. 6: Simplified circuit of LCC cell forming a buck-boost converter                     | 60 |

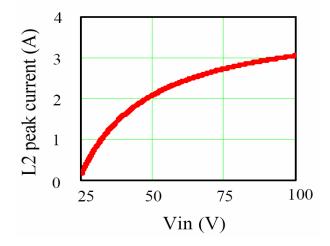

| Fig 3. 7: Inductor L2 peak current vs. Input voltage                                        | 61 |

| Fig 3. 8: Waveform of the conventional buck converter and QSW buck converter at 1           |    |

| MHz                                                                                         | 63 |

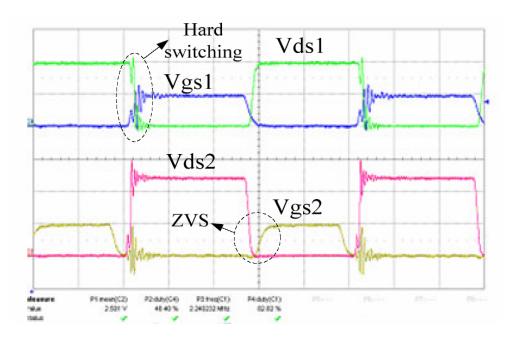

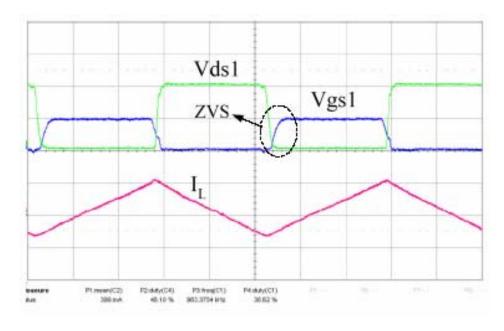

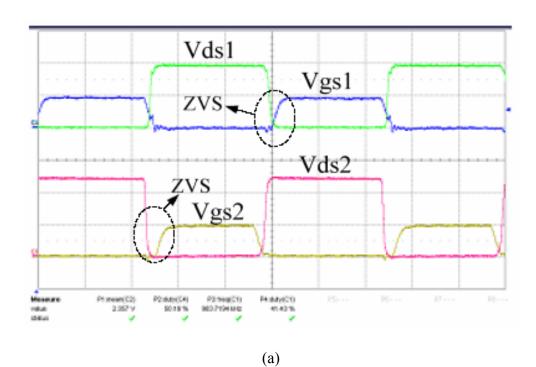

| Fig 3. 9: Waveforms of the presented LCC ZVS buck converter at 1MHz                         | 64 |

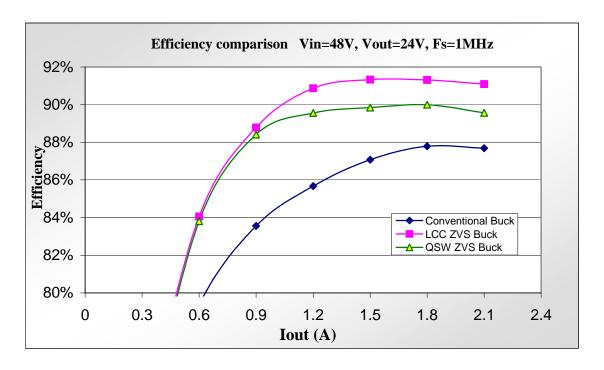

| Fig 3. 10: Efficiency comparison at 1MHz.                                                   | 65 |

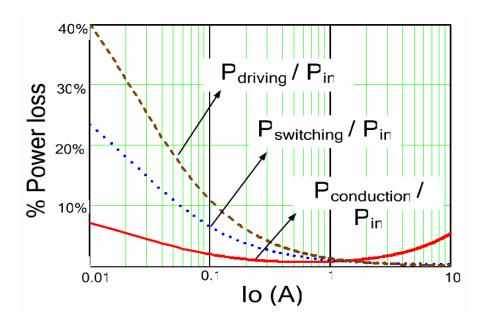

| Fig.4. 1: Power Losses normalized to input power.                                           | 71 |

| Fig.4. 2: Power Losses normalized to input power at fixed switching frequency with MH       |    |

| technique                                                                                   | 73 |

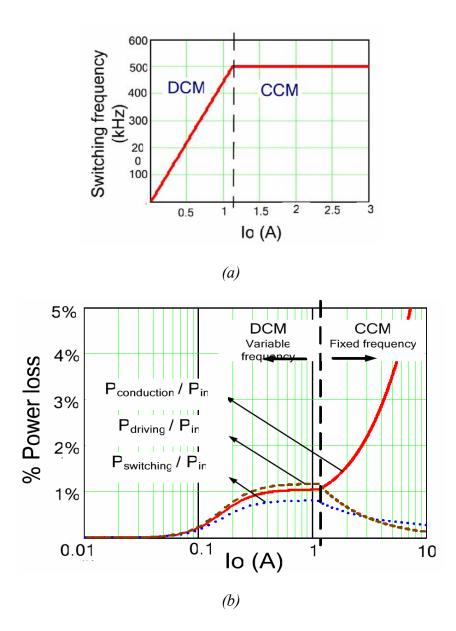

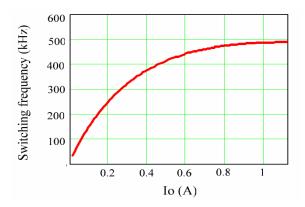

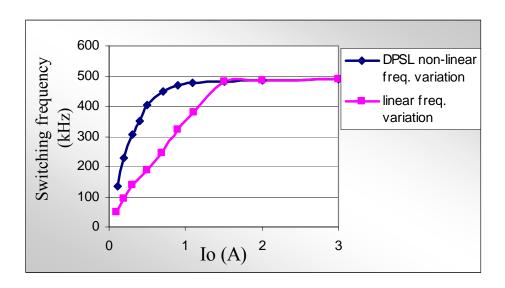

| Fig.4. 3: (a) Switching frequency vs. load current when frequency varies linearly based     |    |

| on the compensation error signal. (b) Power Losses normalized to input power                |    |

| with linear frequency variation and MH techniques.                                          | 76 |

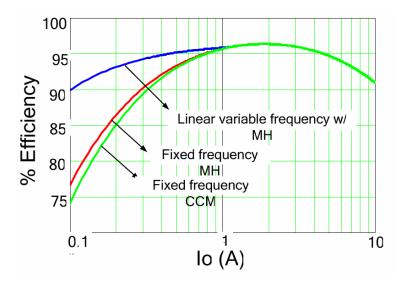

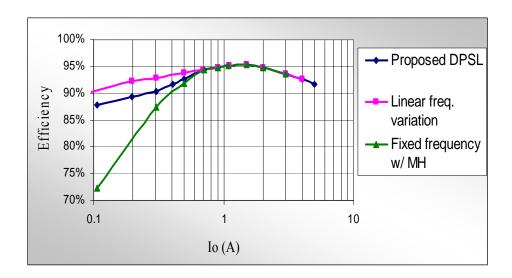

| Fig.4. 4: Efficiency vs. Load Current Comparison for fixed frequency CCM operation,         |    |

| fixed frequency MH and linear variable frequency with MH                                    | 77 |

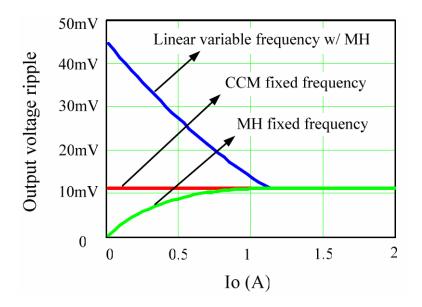

| Fig.4. 5: Output voltage ripple vs. output current for CCM operation, MH and linear         |    |

| variable frequency with MH.                                                                 | 80 |

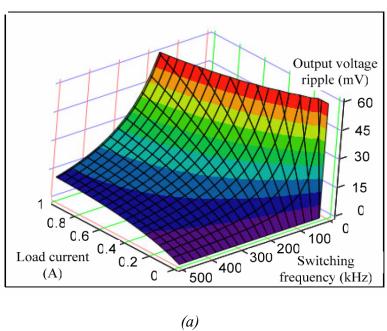

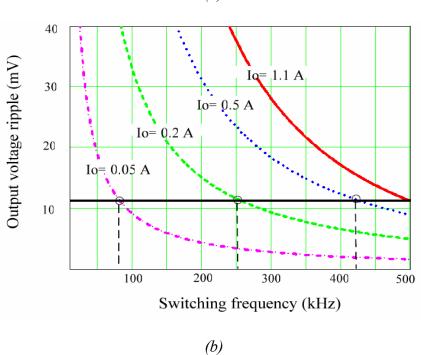

| Fig.4. 6: (a) 3D surface plot of voltage ripples vs. frequency vs. load current in DCM load |    |

| range, and (b) Voltage ripple vs. frequency for different values of load current            | 81 |

| Fig.4. 7: Switching frequency required for fixed voltage ripple vs. Load current            | 83 |

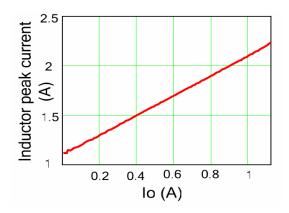

| Fig.4. 8: Inductor peak current vs. load current for switching frequency varying non-          |     |

|------------------------------------------------------------------------------------------------|-----|

| linearly for fixed voltage ripple equal to CCM ripple                                          | 83  |

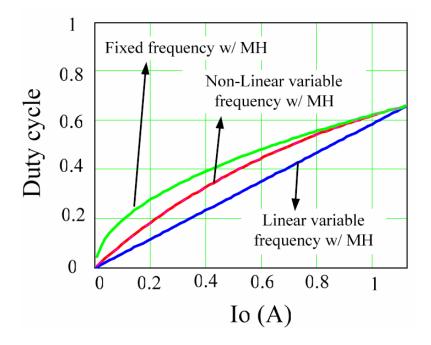

| Fig.4. 9: Duty cycle in DCM vs. Load Current.                                                  | 85  |

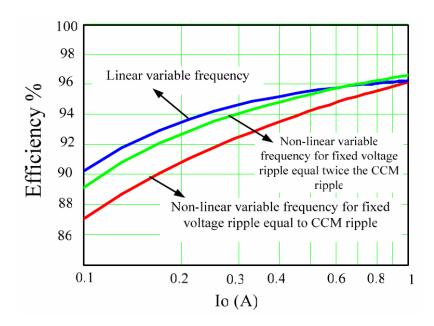

| Fig.4. 10: Efficiency vs. Load current comparison between linear frequency modulation,         |     |

| non-linear frequency modulation for fixed output voltage ripple equal to CCM                   |     |

| ripple, and non-linear frequency modulation for fixed output voltage ripple                    |     |

| equal to twice the CCM ripple.                                                                 | 86  |

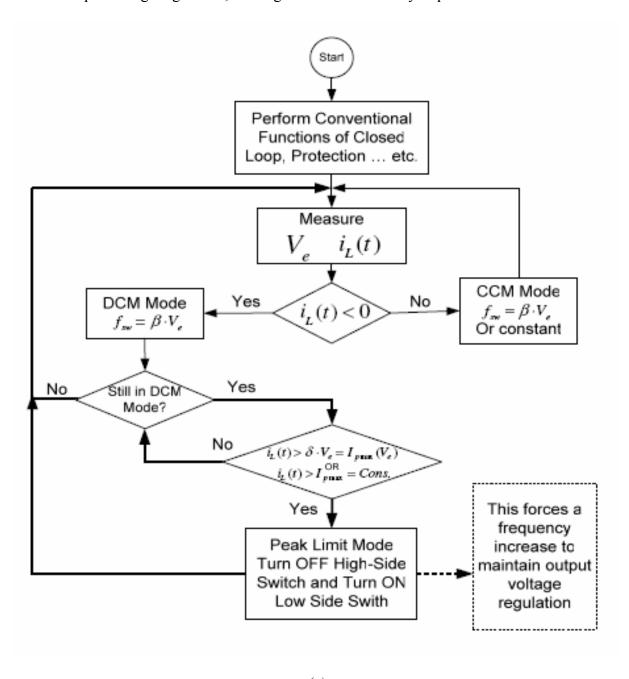

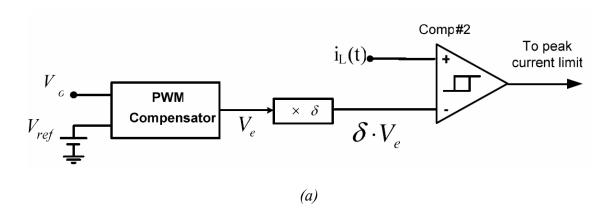

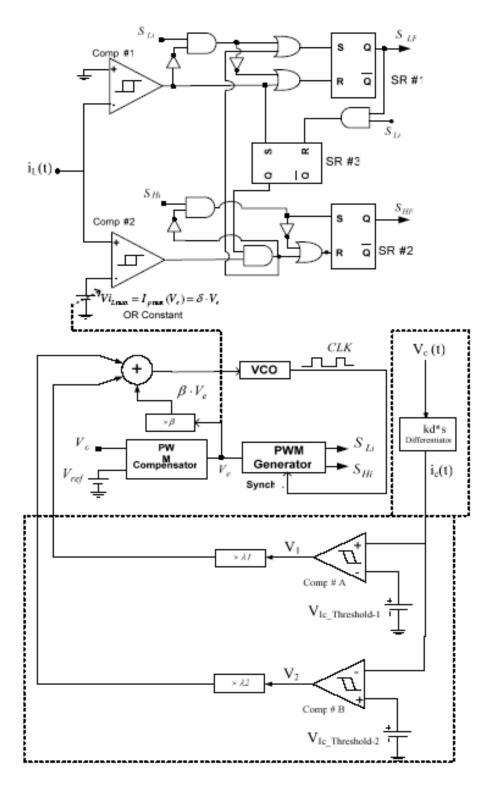

| Fig.4. 11: (a) PSL Controller Flowchart and (b) Implementation Example                         | 90  |

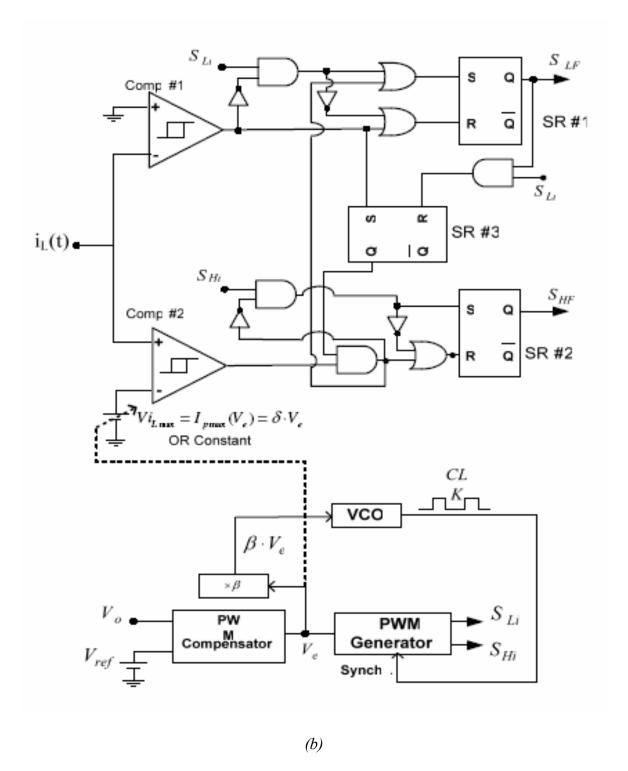

| Fig.4. 12: Voltage ripple vs. load current for the case of setting the peak current limit to a |     |

| constant value that assures a voltage ripple at very light load equal to twice the             |     |

| CCM voltage ripple.                                                                            | 91  |

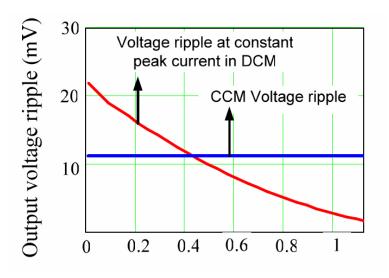

| Fig.4. 13: (a) Implementation of peak current limit based on compensator error signal.         |     |

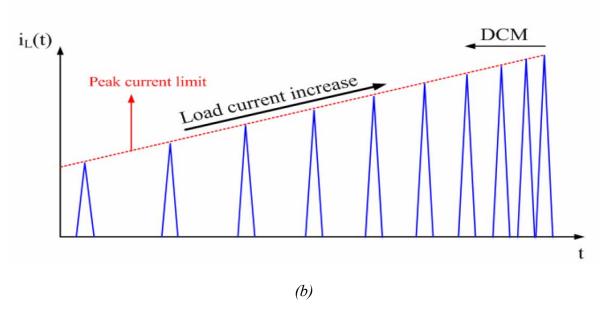

| (b) Inductor current vs. time as load current varies.                                          | 93  |

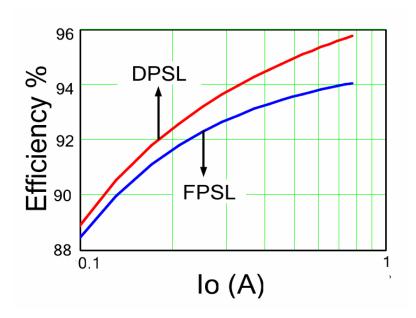

| Fig.4. 14: Efficiency comparison between FPSL and DPSL methods.                                | 94  |

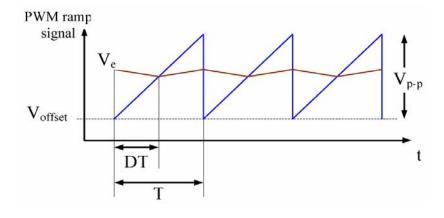

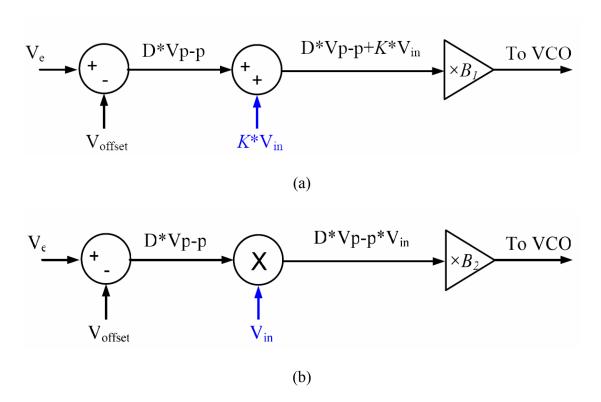

| Fig.4. 15: PWM Modulation and Ramp Signal                                                      | 96  |

| Fig.4. 16: Two methods of input voltage feed forward to eliminate frequency modulation         |     |

| and peak inductor limit dependency on the input voltage                                        | 97  |

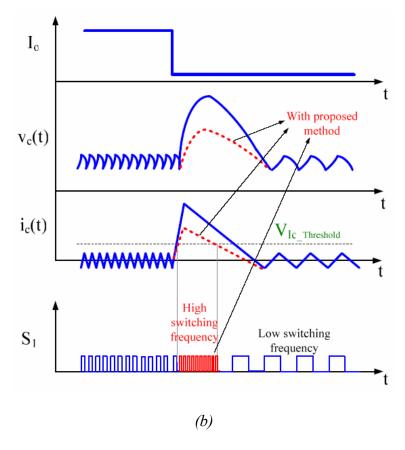

| Fig.4. 17: (a) Implementation of transient improvement for PSL method and (b) output           |     |

| capacitor's voltage and current waveforms associated with step-down load                       |     |

| transient                                                                                      | 101 |

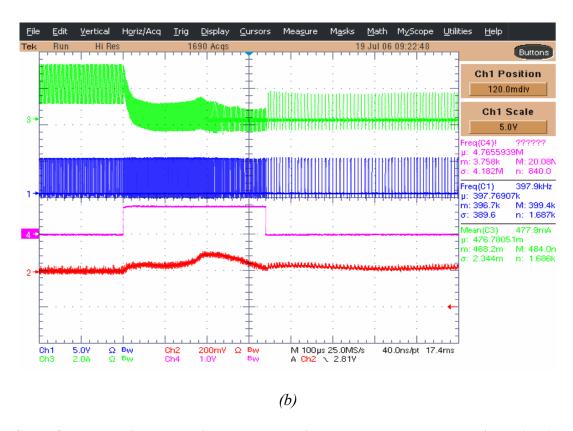

| Fig.4. 18: PSL logic circuit operation experimental waveforms                                  | 103 |

| Fig.4. 19: A plot of the inductor peak current vs. load current measured from the          |     |

|--------------------------------------------------------------------------------------------|-----|

| experimental prototype                                                                     | 104 |

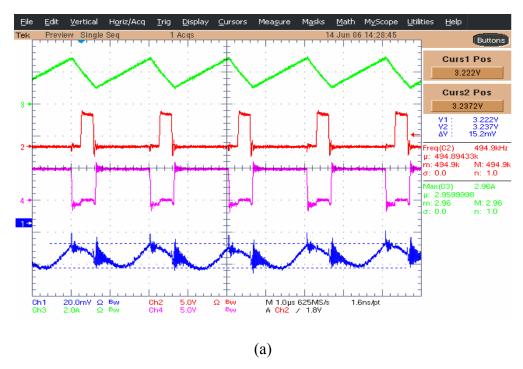

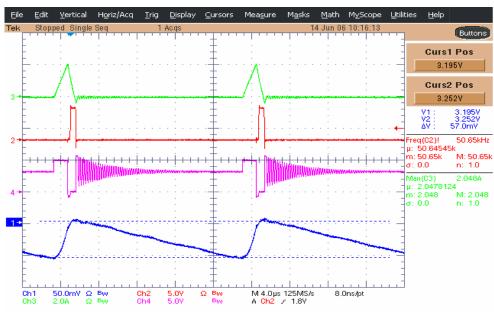

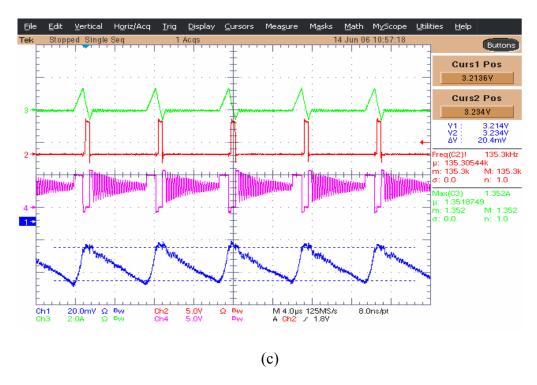

| Fig.4. 20: Experimental Waveforms at Different Loads: (a) CCM at Io=2A, (b) DCM at         |     |

| Io=100mA with linear frequency variation (c) DCM at Io=100mA with PSL                      |     |

| non-linear frequency variation.                                                            | 106 |

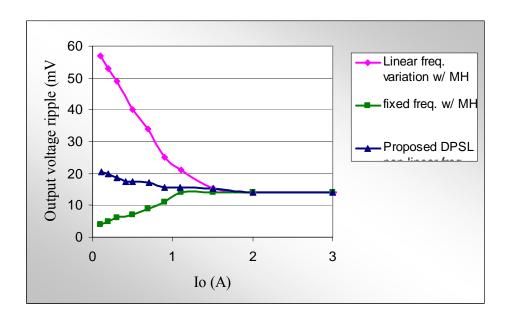

| Fig.4. 21: Output voltage ripple vs. output current comparison obtained from               |     |

| experimental prototype.                                                                    | 107 |

| Fig.4. 22: Switching frequency vs. load current for linear frequency variation control and |     |

| the presented PSL control.                                                                 | 108 |

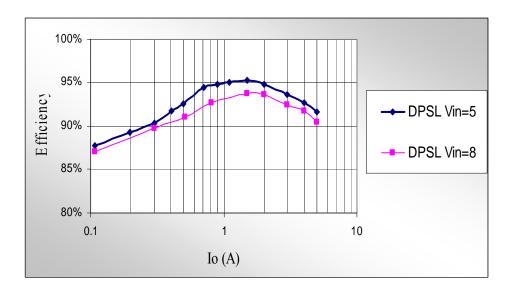

| Fig.4. 23: Efficiency comparison between DPSL and the other techniques                     | 109 |

| Fig.4. 24: DPSL efficiency for different input voltages                                    | 110 |

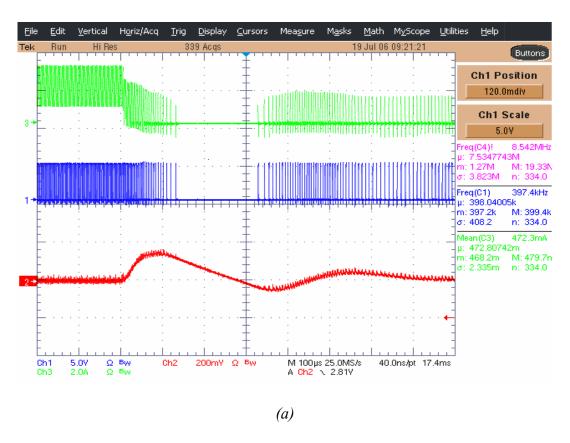

| Fig.4. 25: (a) Load step down transient (2A-0.1A) without applying transient               |     |

| improvement method. (b) Load step down transient (2A-0.1A) with applying                   |     |

| transient improvement method.                                                              | 112 |

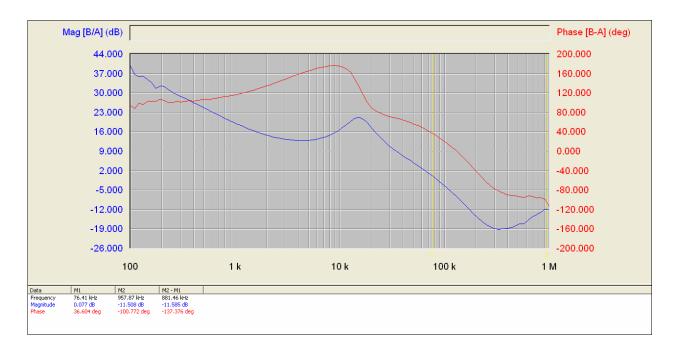

| Fig.4. 26: Closed loop Bode-plots of the PSL VR.                                           | 113 |

| Fig.4. 27: Picture of the experimental prototype                                           | 114 |

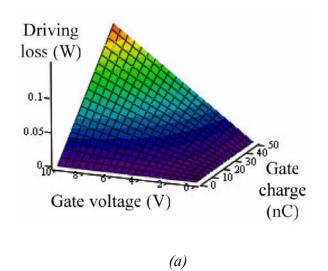

| Fig. 5. 1. (a) Driving loss vs. Cata valtage vs. Cata change (b) Cata change vs. Cata      |     |

| Fig. 5. 1: (a) Driving loss vs. Gate voltage vs. Gate charge. (b) Gate charge vs. Gate     |     |

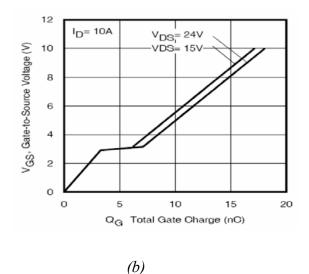

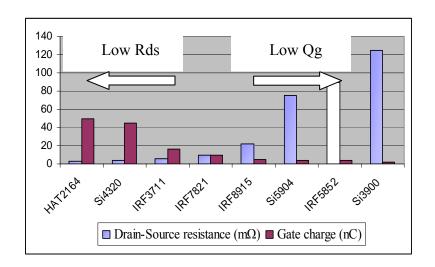

| voltage. c) Driving loss vs. Gate voltage vs. Gate capacitance                             | 119 |

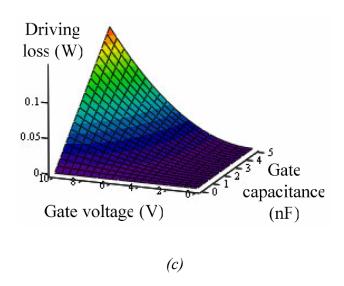

| Fig. 5. 2: (a) Conduction loss vs. RMS current vs. FET resistance (b) FET resistance vs.   |     |

| gate voltage.                                                                              | 119 |

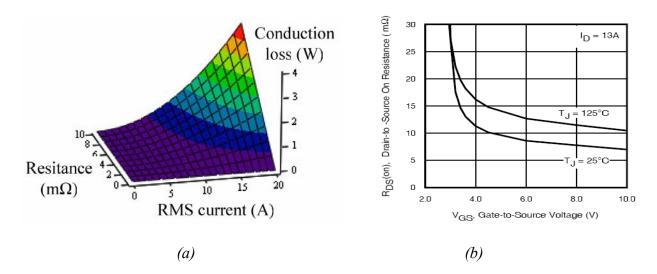

| Fig. 5. 3: Several FETs' gate charge and resistance specifications                         | 120 |

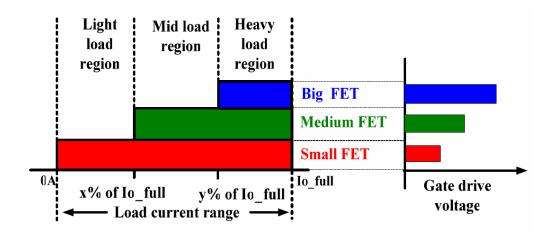

| Fig. 5. 4: Operational concept of proposed AFM                                             | 121 |

| Fig. 5. 5: Power losses normalized by the input power for a conventional design        | 123 |

|----------------------------------------------------------------------------------------|-----|

| Fig. 5. 6: Equivalent parallel FETs' specifications                                    | 124 |

| Fig. 5. 7: (a) Conduction and driving losses normalized to input power                 | 126 |

| Fig. 5. 8: (a) basic implementation of proposed AFM.                                   | 130 |

| Fig. 5. 9: Safe operation design consideration at step up load                         | 132 |

| Fig. 5. 10: Typical inductor value case                                                | 133 |

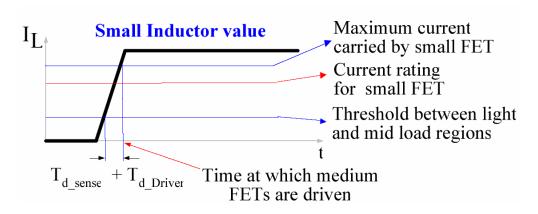

| Fig. 5. 11: Small inductor value case                                                  | 133 |

| Fig. 5. 12: (a) Implementation of the proposed safe operation circuit for low inductor |     |

| value case (b) Waveforms of the proposed circuit                                       | 136 |

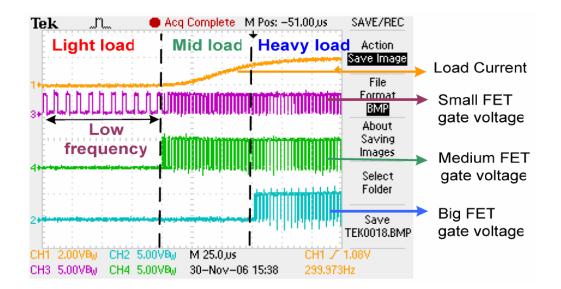

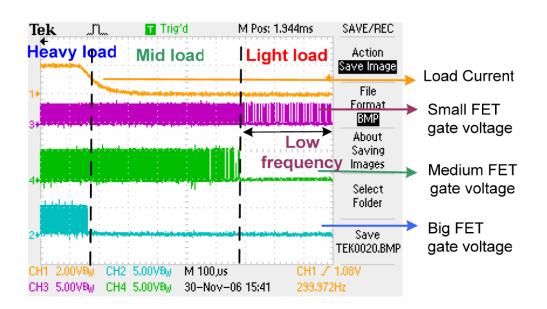

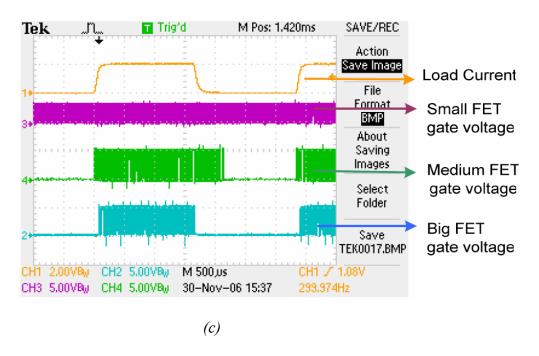

| Fig. 5. 13: Experimental waveforms of the proposed AFM operation.                      | 139 |

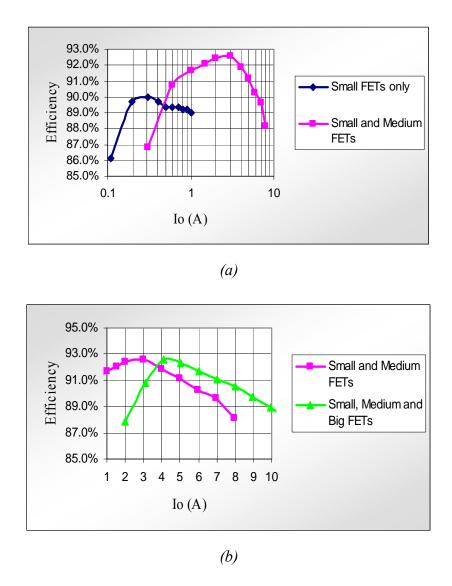

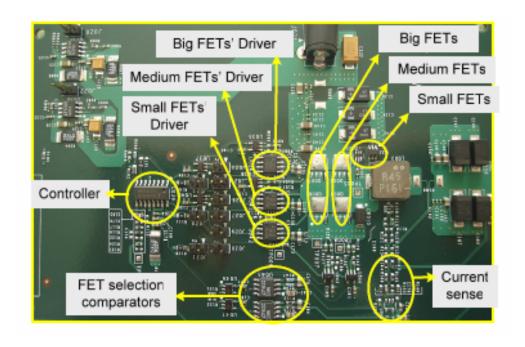

| Fig. 5. 14: (a) Efficiency comparison between small and medium FETs.                   | 140 |

| Fig. 5. 15: Picture of the experimental prototype                                      | 141 |

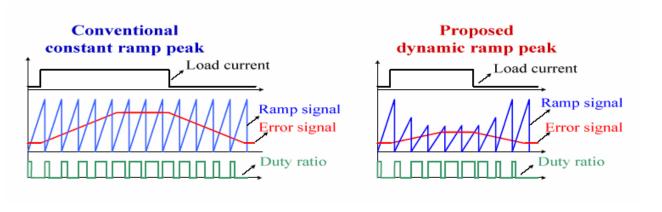

| Fig. 6. 1: PWM for the conventional constant ramp signal peak and for the proposed     |     |

| dynamic ramp signal peak during load transient                                         |     |

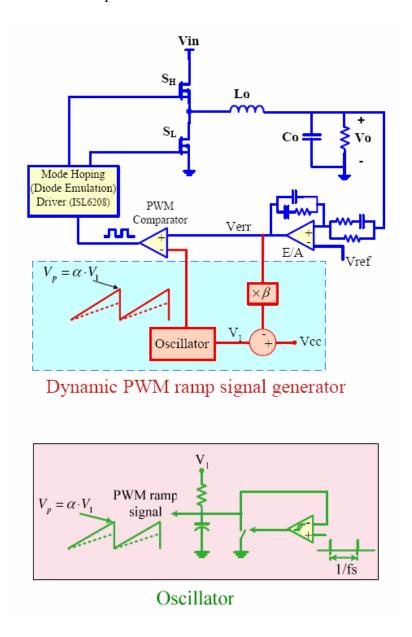

| Fig. 6. 2: Implementation of the proposed control method                               |     |

| Fig. 6. 3: Basic blocks of Buck regulator.                                             |     |

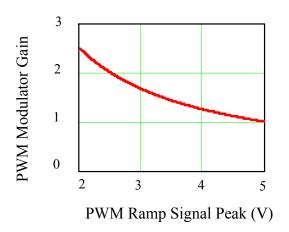

| Fig. 6. 4: PWM modulator gain vs. ramp signal peak, and closed loop buck regulator     |     |

| Bode-Plots for different PWM ramp signal peaks                                         |     |

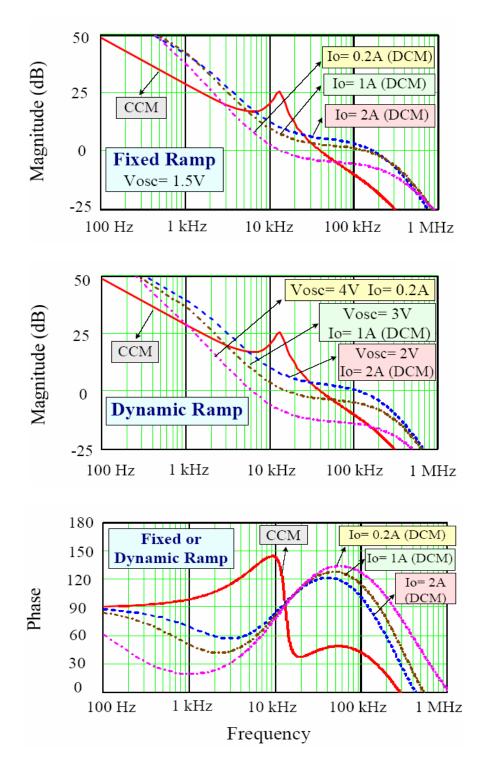

| Fig. 6. 5: Comparison between the bode plots of a closed loop buck regulator for fixed |     |

| ramp peak control and the proposed dynamic ramp peak control                           |     |

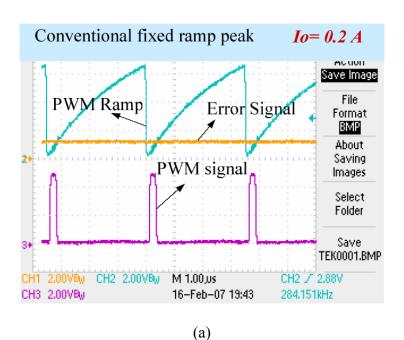

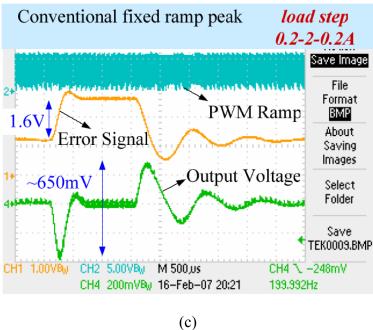

| Fig. 6. 6: Conventional fixed ramp peak control waveforms.                             |     |

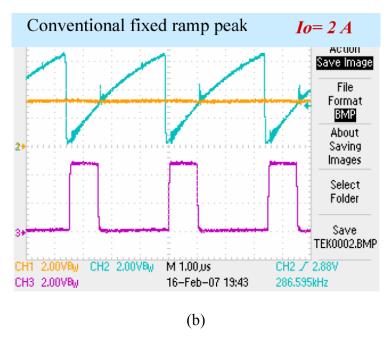

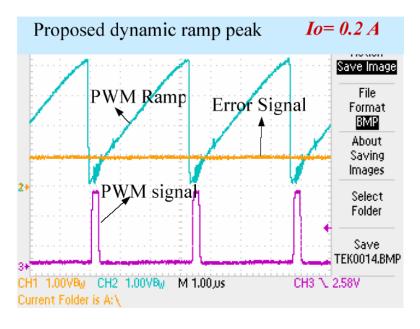

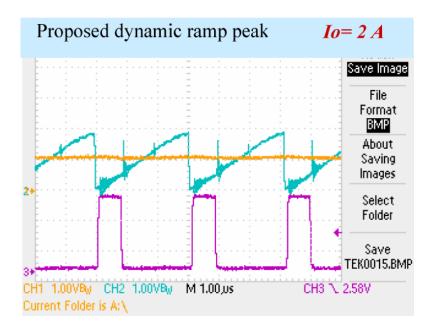

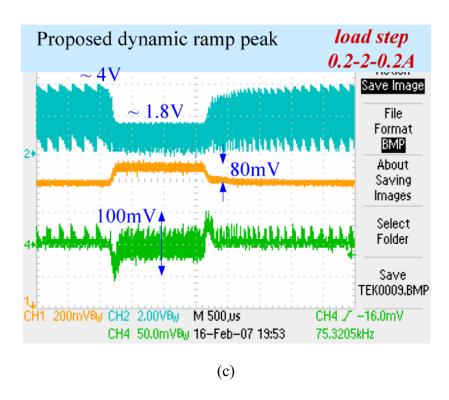

| Fig. 6. 7: Proposed dynamic ramp peak control waveforms.                               | 156 |

|                                                                                        |     |

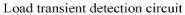

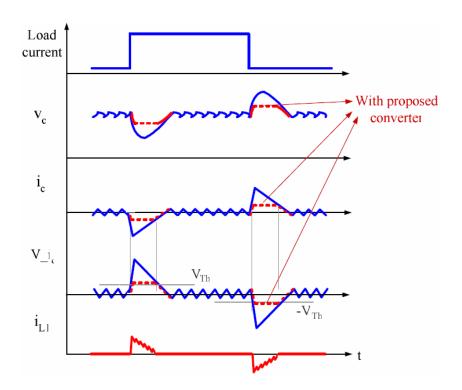

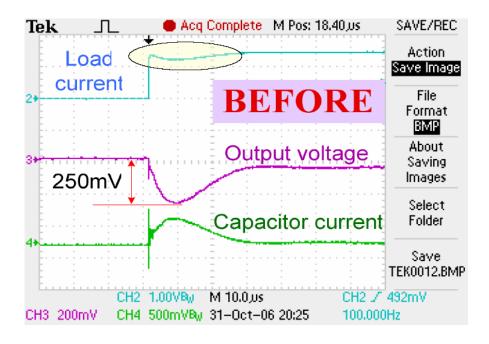

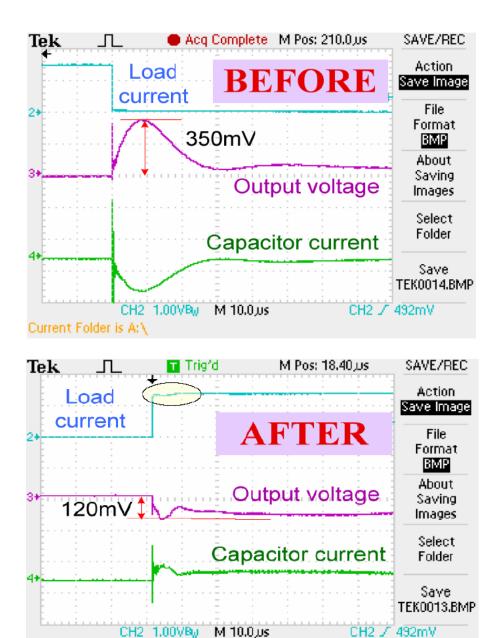

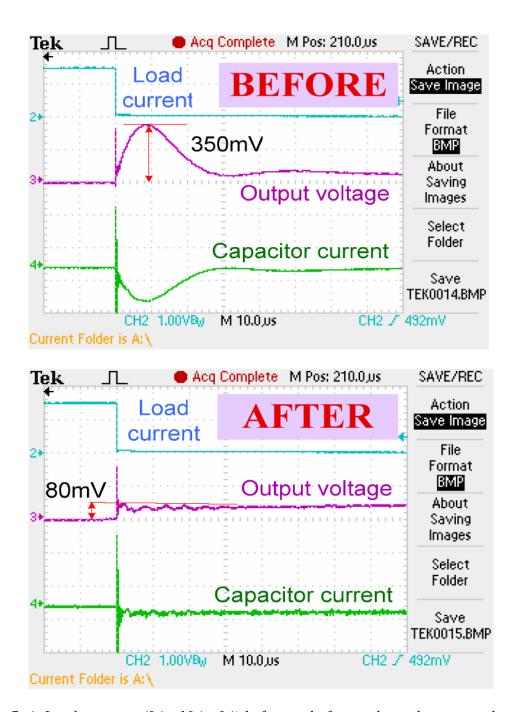

| Fig 7. 1: Proposed converter implementation and key waveforms                           | . 161 |

|-----------------------------------------------------------------------------------------|-------|

| Fig 7. 2: Load step-up transient (0A - 10A step) before and after applying the proposed |       |

| converter                                                                               | . 163 |

| Fig 7. 3: Load step-down transient (10A - 0A step) before and after applying the        |       |

| proposed converter.                                                                     | . 164 |

| Fig 7. 4: Load transient (0A - 10A - 0A) before and after applying the proposed         |       |

| converter                                                                               | . 165 |

## LIST OF TABLES

| Table 4. 1: Conduction Losses for Buck VR                                   | 69  |

|-----------------------------------------------------------------------------|-----|

| Table 4. 2: Switching Losses, Gate Drive Losses and Core Losses for Buck VR | 69  |

|                                                                             |     |

| Table 5. 1: FETs specifications                                             | 122 |

#### **CHAPTER 1: INTRODUCTION**

Demands on DC-DC converters are continuously increasing to be applied in many areas such as telecommunications, cellular telephones, networking products, notebook and desktop computers, industrial instrumentation, and automotive electronics. DC-DC converters must be able to supply energy at high standards and specifications, which forces DC-DC converters to a continuous improvement to be able to fulfill other applications requirements pertaining to efficiency, dynamic performance, thermo, noise and size.

DC-DC converters are mostly required to be physically small; this requires the increase of switching frequency since high switching frequency permits capacitors and magnetic components to have smaller size; also, faster switching frequency has the benefit of better dynamic performance for faster response. The issue that rises up when increasing the switching frequency is the efficiency since switching frequency and efficiency are inversely proportional. On the other hand, converters with smaller sizes face thermal issues especially at high currents due to increased conduction losses. Given that power losses transform to heat, it is more challenging to dissipate this heat out of converters with smaller sizes; the temperature rise caused by poor heat flow degrades device performance and therefore the converter's efficiency.

In order for a power converter to operate at high switching frequency while maintaining good performance, high efficiency, and acceptable temperature, it is essential to investigate where and how energy is lost inside the power converter. Mainly, losses in power converters are divided into switching losses and conduction losses.

Switching losses are due to electrical charges lost in the process of turning on and off the switching devices; they are basically the energy lost in charging and discharging the FET's gate capacitor, or what are called driving losses: energy losses associated with the FET's junction capacitor, reverse recovery losses of diodes, or FET's body diode and other switching losses caused by the switching devices parasitics. These kinds of losses get more significant at higher frequencies. In order to reduce such losses, many techniques can be applied to recover the energy stored in the MOSFET's gate capacitor. In addition to applying soft switching where switching devices can switch at zero voltage or zero current, soft switching also lowers EMI noise and speeds the turn on speed and lower the gate drive power in some cases due to the absence of Miller's effect.

Conduction losses are due to the energy flow through components and switching devices. They are basically the energy lost in the components resistance: the switches' on-resistance and diodes or MOSFET's body diode voltage drop. These kinds of losses get more significant in high-current applications. In order to reduce conduction losses, energy must be processed through the least possible number of components with avoidance of circulating energy; components and switching devices should be selected to have the least resistance and voltage drop. In addition, converter parameters such as inductor value, switching frequency, and the input-to-output voltage ratio should be designed properly that considers current ripple and its rms, since conduction losses are directly related to rms current value.

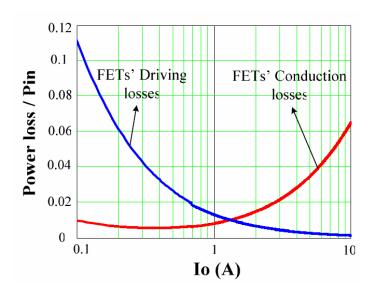

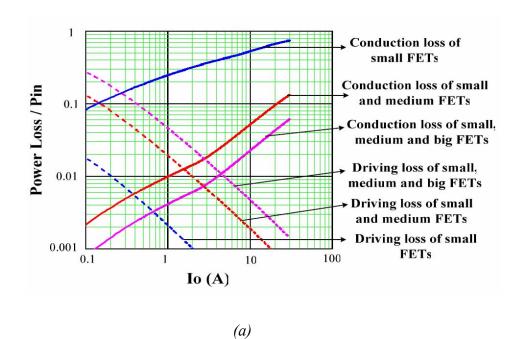

Understanding the causes behind each loss, it is possible to reduce the type of losses that can be dominantly affecting the converter's efficiency. For example, in order to improve efficiency at heavy loads, it is beneficial to reduce conduction losses even at the expense of increased switching losses since conduction losses dominate the total power loss ate heavy load. On the other hand, if light load efficiency improvement is desired, it is beneficial to reduce switching losses even at the expense of increased conduction losses since switching losses dominates the total power losses at light loads.

Power requirements vary from one application to another. In mobile applications, the main concern is to extend the battery life, such applications draw light power most of the time. Therefore, it is essential to improve the light load efficiency for converters applied in battery powers devices. Load adaptive schemes can be used to adapt power delivery to different load demands [61, 62]. This could be done by adjusting control parameters or by modifying the hardware/components structure of the power stage, or both. While in other applications such as telecommunications, converters have higher input voltages, compared to mobile applications, and are required to deliver higher currents. Thus, it is necessary to reduce power losses at heavy load in order to limit the temperature rise. Applying soft switching to such applications is desired since switching losses are more significant at higher input voltages [63-65]; also, FETs' parasitics tend to be worse for higher voltage rating FETs.

Demanding high power applications, such as fast processors and pulsed loads, require new levels of performance from dc-dc converters. The requirements of high slew rate of load current with minimal output voltage deviation along with high conversion efficiency, small size and low cost, are all contradicting requirements for the dc-dc converter design. Literature includes many approaches to significantly limit the voltage overshoot and undershoot during load transient and reduce the number of capacitors, without compromising on the efficiency, cost, or size of the dc-dc converter.

Following are literature reviews and brief introductions of proposed soft switching topologies, load adaptive control techniques, and dynamic performance improvement methods.

#### 1.1 Soft switching topologies

#### 1.1.1 Literature review of soft switching topologies

With demanding powering requirements of fast transient response and high power density, the converters' switching frequencies keep increasing resulting in increased switching loss. Recently, soft-switching techniques drew a lot of attention in reducing switching loss and EMI noises. Among them, particularly, zero voltage switching (ZVS) techniques are desirable for MOSFET-type switches. ZVS multi-resonant converters (MRCs) technique utilizes all major parasitic of the power stages and all semiconductor devices in MRC operate with ZVS [1], which substantially reduces the switching losses and noise. Quasi-resonant converters (QRCs) were introduced to overcome the disadvantages of conventional PWM converters operating at high

switching frequency by achieving ZVS for the active switch and zero current switching (ZCS) for the rectifier diode [2,11]. However, the switches in both QRCs and MRCs have to withstand high voltage stress or high current stress [12, 14], which restricts the applications of those resonant converters. By reducing the filter inductance in the conventional PWM converters, ZVS quasi-square-wave (QSW) technique offers ZVS for both the active and passive switches without increasing the switches' voltage stress [3, 4, 13]. However, QSW converters suffer high current stress in components, as a result, conduction losses are greatly increased, and active switches turn off at high currents. In [5-6], a similar concept of QSW is presented with an LC cell in parallel with the active switch or rectifier diode. The cell consists of a small inductor Lr in series with a large capacitor Cc, and the cell's high inductor current ripple is utilized to achieve ZVS turn-on for the active switch. However, the current ripple in the cell's inductor Lr is more than twice that of the one in the filter inductor, and the associated conduction and turn-off loss increase is significant.

To facilitate ZVS while preserving the advantages of the PWM technique, hybrid topologies incorporate PWM technique and resonant converters in order to minimize circulating energy and corresponding conduction loss and switching loss. Adding an auxiliary switch across the resonant converter in a ZVS-QRC derives ZVS-PWM converter, which can be considered as hybrid circuits of ZVS-QRCs and PWM converters [9], wherein ZVS is achieved for the power switch and the converter operates at a constant switching frequency. However, the power switch suffers from a high voltage stress that is proportional to the load range. Compared with ZVS-PWM converter, zero-voltage-transition PWM (ZVT-PWM) converters [10, 12] are more

desirable since soft switching is achieved without increasing switch voltage and current stress. By adding an auxiliary shunt network to discharge switch junction capacitance and shift the rectifier diode current, ZVS is achieved for switch and reverse recovery of rectifier diode is attenuated.

#### 1.1.2 Proposed soft switching topologies

## 1.1.2.1 Active Resonant Tank (ART) for zero-voltage-switching DC-DC converters with synchronous rectifiers

Active Resonant Tank (ART) cells are to achieve Zero-Voltage-Switching (ZVS) and eliminate body-diode conduction and its reverse recovery in dc-dc converters with Synchronous Rectifiers (SRs). During transition of the switches, SRs' parasitic body diodes unavoidably carry load current, which decreases conversion efficiency because voltage drop across body diodes is much higher than that across SRs. In addition, reverse recovery of the body diodes leads to increased switching losses and Electromagnetic Interference (EMI). Even so, in low-output-voltage dc-dc converters, SRs are widely utilized to reduce rectifier conduction loss and improve converter efficiency since the saved conduction losses overcome the switching losses. However, in higher voltage applications, which require the higher voltage rating FETs or SRs, the benefits of utilizing SRs are limited since switching losses tend to be more significant. This is so because SRs with higher voltage ratings have worse parasitic, and conduction losses appear to be less since the current is less for the same power level. With the proposed cells of active resonant tank, the body diodes are never involved during switching transition, and thus body diode conduction

loss is saved, and reverse-recovery-related switching loss and ringing are eliminated, in addition to achieving zero voltage switching (ZVS) for the active or main switch. The resonant tank cells consist of a network including LC resonant tank and an active switch. Basically, prior to the turn-off of the SR, the energy stored in the tank capacitor is released through the resonant inductor to reverse the current in the SR to avoid body diode conduction and eliminate recovery loss, and then discharge the main switch junction capacitance, so that the main switch turns on at ZVS. During the following interval, the resonant tank cell recharges in a resonant manner. Since energy communication occurs only during switching transition, conduction loss dissipated in the resonant tank is limited. Moreover, the auxiliary active switch turns on at ZCS and turns off at ZVS and the SRs operate at ZVS. The concept of ART cells is introduced in a general manner, and detailed analyses are provided based on a buck converter, and experimental results show that efficiency improvement is achieved due to the reduced switching loss, conduction of the body diode and reverse-recovery loss.

#### 1.1.2.2 LCC ZVS buck converter with synchronous rectifier

The motivation is the same as that for the ART converter discussed above, which is the limitation of SR usage in high voltage applications due the increased switching losses. This differs from the ART since it has no additional switch which makes it a passive cell instead of an active cell or tank.

The concept of the LCC ZVS buck converter topology is introducing an inductive load in the bridge leg and changing the switching commutation mechanism of the low-side SR switch. In

other words, in the conventional buck converter with SR, the SR operates at capacitive load. When the SR turns off, the current flows through the body diode; as a result, the reverse recovery of the body diode occurs with the turn-on of the high-side switch. While in the proposed converter, the SR turns off at inductive load, and the inductive current will not flow through the body diode of the SR. Moreover, the inductive current is utilized to discharge the junction capacitance and achieve ZVS for the high-side switch. Therefore, compared with the conventional SR buck converter, reverse-recovery-related switching and ringing loss is eliminated; and compared with QSW buck converter, the output current ripple is significantly reduced and the output capacitance is dramatically reduced. A prototype was built to compare the conventional Buck converter, QSW buck converter, and the proposed LCC ZVS buck converter. The experimental test shows that the proposed converter is advantageous over the conventional buck converter at high switching frequency, where the switching loss dominates the total power loss. The experimental test results also show that the LCC buck converter is advantageous over QSW converter in current and output voltage ripples and efficiency in wide range of switching frequency; it also has half the input current di/dt compared to the QSW converter.

#### 1.2 All load efficiency improvement control techniques

### 1.2.1 Literature review of all load efficiency improvement techniques

Unlike many Voltage Regulator (VR) applications where achieving high efficiency toward the full load is the most important factor—even at the expense of low efficiency under light load—

high efficiency at all load conditions including light load is required in other applications such as those that are battery-powered and have constrains in energy consumption [17-20]. For such applications, this becomes even more important when the load power consumption is dynamically varied with applications or usage conditions such as DSP (Digital Signal Processor) and ICs (Integrated Circuits) in portable computers and handheld devices. On the other hand, other applications target achieving maximum efficiency at heavy load with less concern of light load efficiency in order to minimize the generated heat inside the converter [20].

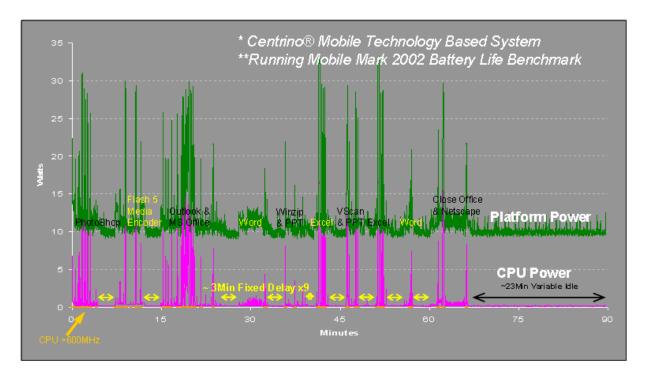

Figure 1.1 shows a power consumption of an Intel Centrino® Mobile Technology based system under different usage or application conditions [23] as an example. As can be noted, both the CPU power and platform power drawn from the power delivery or VR vary rapidly and frequently with time as usage conditions or applications change. This load/power variation covers a wide load range including light loads. Moreover, as DSPs and the platform become more power managed (by software or hardware), the percentage of time during which a specific VR or power delivery operates at lighter loads becomes larger. Therefore, platform power delivery efficiency at all load levels including lighter loads is very important for extended energy savings and battery life.

Power conversion structure, parameters, components and control are usually selected and optimized to: 1) peak efficiency at specific load or power level, at the expense of lower efficiency at other load levels, 2) to satisfy performance requirements such as steady-state ripple and transient deviation specifications, and 3) to reduce size and cost. To improve efficiency and

performance, load adaptive schemes can be used to adapt power delivery to different load demands. For example, this could be done by adjusting the control or control parameters of the power stage, by adjusting the hardware/components structure of the power stage, or by adjusting both. The objective is always to achieve the best possible power conversion efficiency with the best possible steady-state and dynamic performance over wide load range, which should meet load requirements and demands with minimum size and cost.

Fig. 1. 1: Example of Power Consumption Benchmark of an Intel Centrino® Mobile Technology based system under different usage and applications conditions: Top Curve for Platform Power and Bottom Curve for CPU Power.

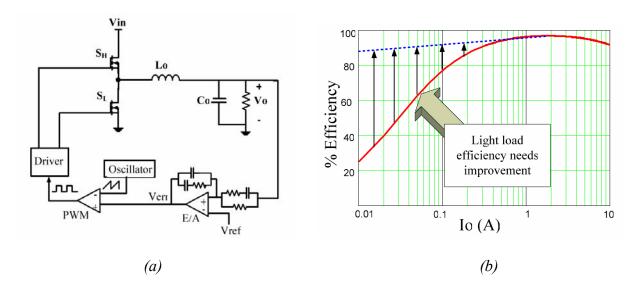

Figure 1.2 shows an example of a typical buck VR and efficiency curve. In order to "flatten" such efficiency curve or improve light load efficiency, several techniques can be applied such as

Mode-Hopping and Pulse Skipping [17, 18, 28, 29, 35]. In Mode-Hopping technique (MH), the DC-DC Buck VR operates in both synchronous and asynchronous modes. It operates in synchronous mode at CCM (Continuous Conduction Mode) under medium to heavy load demands, where the inductor current does not reach zero or below. It operates in asynchronous mode at DCM (Discontinuous Conduction Mode) under light load demands, where the inductor current starts approaching the zero amperes point, to mainly reduce conduction losses [20, 29]. While in Pulse-Skipping or variable switching frequency technique, the VR switching frequency is lowered as the load becomes smaller in order to reduce switching and driving losses. This can be implemented by using hysteretic control or variable frequency PWM control [21, 31]. Both techniques result in efficiency improvement especially under light loads. However, they also cause an increase in output voltage ripple and possibly impact the dynamic and steady-state performances of the VR [33, 34], which are important for ICs operation performance, especially for those that are highly integrated and operate under a low normal voltage level. In [22], the gate drive voltage dynamically scales relative to load current, so that gate drive loss is reduced at light load. Efficiency improvement due to this technique is limited since there are other switching losses that degrade light load efficiency besides driving losses.

Fig. 1. 2: (a) Buck VR and (b) Typical buck VR and efficiency curve.

In [46], a multiphase buck converter technique with non-uniform current sharing and phase-picking was proposed, which also improves light load efficiencies. However, multiphase buck topology is more favorable in high current applications. In low power applications that do not require more than one phase and that are area constrained, it is preferred to process power through a single phase and optimize the design for a wide range of load current.

Another way to improve light load in interleaved multi-phase buck is through what is called the "baby buck" [26], a small phase that is optimized for low power is activated only at light load conditions.

In a tapped inductor buck [27], the duty ratio is extended mainly to reduce peak current, which reduces turn off losses. But the leakage inductance of the tapped inductor causes a severe voltage spike across switching devices. And the energy trapped in the leakage inductance is also

dissipated in each switching cycle and generates large power losses. Many techniques are used to solve the voltage spike problem and recover the leakage inductance energy. But these techniques require additional parts or more complicated magnetic design, which takes away the simplicity feature of a buck regulator.

#### 1.2.2 Proposed load adaptive techniques for all load efficiency improvement

# 1.2.2.1 On load adaptive control of voltage regulators for power managed loads: control schemes to improve converter efficiency and performance

Efficiency improvement, especially at light load currents, is important in many applications including those that are battery powered and have energy consumption constraints. However, controlled steady-state and dynamic performance should be maintained while improving efficiency. An analytical study of VR losses and voltage ripple deviation is presented and discussed, yielding to a proposed control technique, namely "Pulse Sliding\*\*" (PSL) control technique, which results in an improved VR conversion efficiency with low and controlled voltage ripple and improved dynamic response. The proposed control method achieves the advantages of both variable frequency and fixed frequency controls and eliminates their disadvantages by utilizing information obtained from the inductor peak current, compensation error signal and output capacitor current, resulting in an optimum non-linear switching frequency modulation. PSL is compared to other control methods by both analyses and experiments. Experimental results highly agree with theoretical analyses.

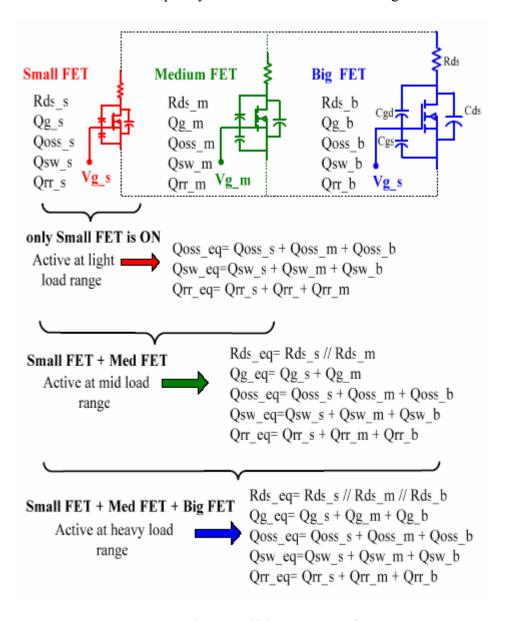

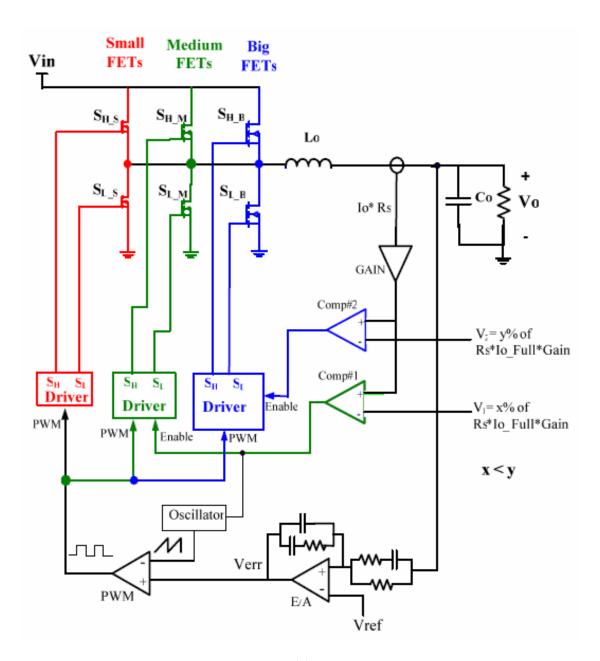

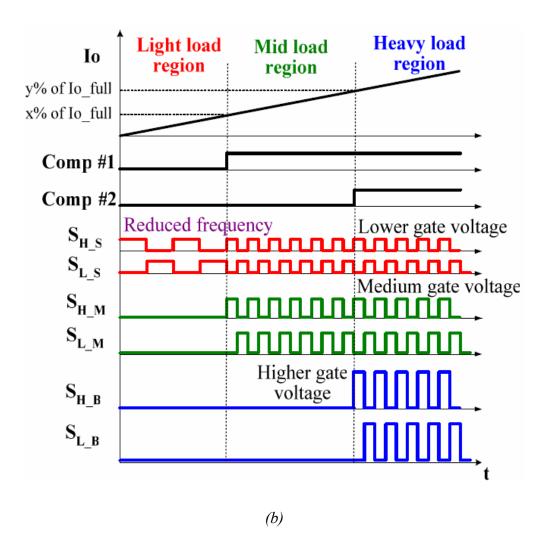

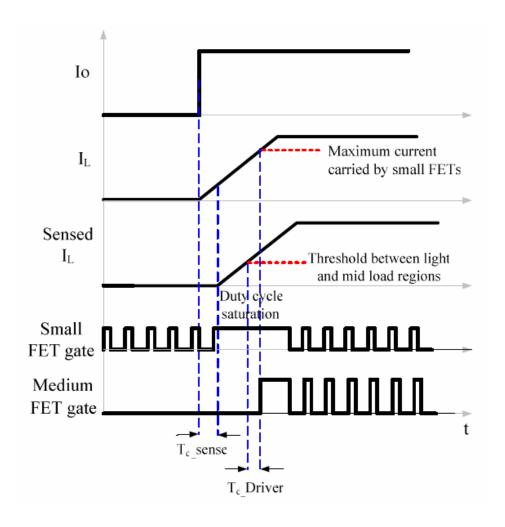

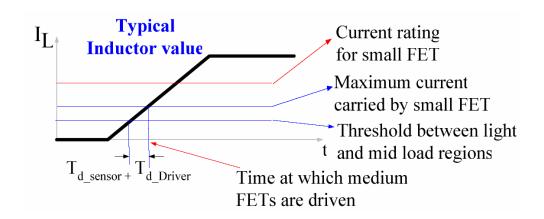

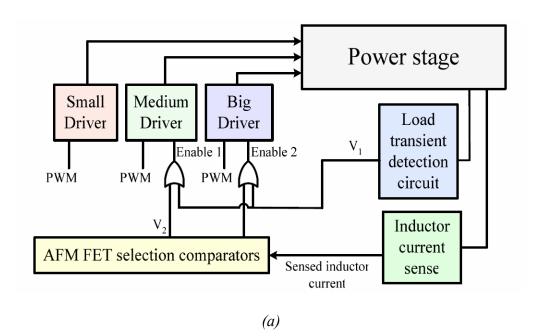

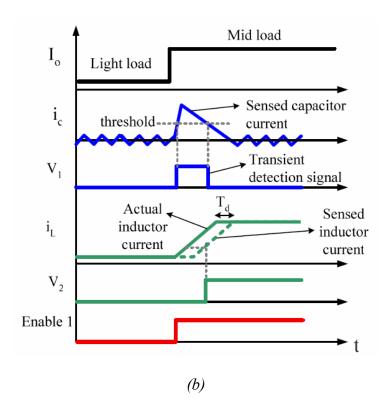

#### 1.2.2.2 Adaptive FET modulation for voltage regulator efficiency improvement

A load adaptive voltage regulator that achieves high efficiency extended to light and heavy load regions is named "Adaptive FET Modulation" (AFM). Since multiple FETs with different specifications are paralleled, the number of driven FETs and their gate driving voltage is adaptive to load current. The capability of adaptive modulation of FETs' parasitic charges and resistances along with adaptive gate driving voltage allow achievement of the best FET optimization for wide load range. AFM operates at fixed switching frequency for almost the whole load range, so it has no effect on the conventional buck operation and its dynamic performance, in addition to having simple implementation. Concept, design, analyses and experimental results of the AFM are presented.

#### 1.3 Dynamic performance improvement methods

#### 1.3.1 Literature review of dynamic performance improvement methods

With the continuous upgrades of CPU's, challenges keep rising for voltage regulators to meet the power requirements, such as the low output voltage, high current with high slew rate, and high efficiency with high power density and good thermal performance. Some of these requirements contradict each other, such as the high slew rate and high efficiency. A high slew rate needs small filter inductance, but this leads to high current ripple which increases the conduction and switching losses. Interleaved multiphase VR can reduce the input and output current ripples and it has good distributed thermal capability which is commonly used in desktop and laptop

computer system to power the CPU [48]. In high slew transient, the VR current cannot catch up with load current immediately: the unbalanced current will be provided by filter and decoupling capacitors; thus, two transient voltage spikes occur in the VR output voltage [46]. The first voltage spike is determined by ESR, ESL of capacitors, and the second voltage spike is mainly determined by the energy stored in filter inductors related to the close-loop bandwidth [46, 47]. In order to reduce the transient voltage spikes, typically a large number of capacitors are mounted close to the processor on the motherboard for lower ESRs, ESLs. Unfortunately, the available space on the motherboard makes it difficult to add more capacitors for the increasing slew rate. Furthermore, increased motherboard capacitors have limited effect on the voltage spike suppression due to the existence of resistance and inductance of PCB traces and socket [46, 48]. The effective way to reduce the second voltage spike is to reduce the delay times in controller, especially in large signal transients. There are three main delay times in VRs: LC filter, compensation network, and the IC propagation delay times. How to reduce those delay times in a simple way is a challenge and needs a tradeoff between fast transient response and high efficiency.

The barrier of output VR current slew rate is determined by the VR equivalent inductance and its applied voltage. High switching frequency operation helps to reduce its LC filter for high bandwidth, but it introduces higher switching loss. Recently many other efforts have been put into the VRs to improve the transient response by reducing the output impedance or load line [49-56, 59, 60].

#### 1.3.2 Proposed dynamic performance improvement methods

#### 1.3.2.1 Dynamic PWM ramp signal to improve load transient in DCM and Mode-Hoping operation

The requirement of high slew rate of load current with minimal output voltage deviation is challenging. In case of load transient in CCM operation, the duty ratio is almost constant over the load current range; it slightly changes to compensate the extra losses and keep output voltage regulation. While in DCM and Mode Hoping operation, duty ratio varies significantly in case of load transient, the control loop is required to update the compensation error signal, consequently, the duty ratio, as load current varies. Since it takes longer time for the compensator to reach the steady state in cases of large duty cycle variation (DCM operation), the output voltage deviation during load transient is drastically increased when operating in DCM compared to CCM operation. Proposed is a new control method that dynamically modulates the PWM ramp signal peak, which in turn modulates the PWM modulator gain, to minimize the required error signal change during load transient, so that the compensator reaches steady state faster. Therefore, lower output voltage deviation during load transient can be achieved.

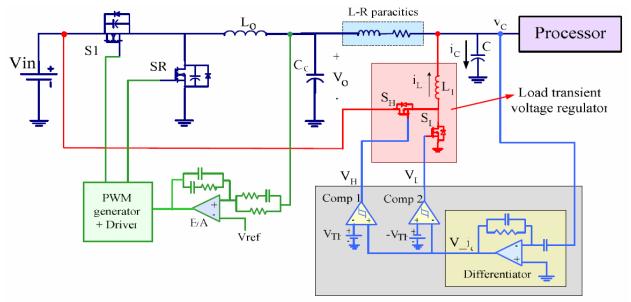

# 1.3.2.2 Transient response improvement in DC-DC converters using output capacitor current for faster transient detection

Proposed is a new approach to significantly limit the voltage overshoot and undershoot during load transient and reduce the number of capacitors without compromising on the efficiency, cost

or size of the dc-dc converter. It allows optimization of the power stage efficiency for the dc operation with less concern of dynamic performance, while an additional switching circuit; that utilizes the output capacitor current to rapidly detect load transient, is activated during load step up to deliver the shortage charge to the output capacitor, and to pull out the extra charge from the output capacitor during load step down. Therefore, lower voltage deviation is achieved during load transient.

# CHAPTER 2: ACTIVE RESONANT TANK (ART) FOR ZERO-VOLTAGE-SWITCHING DC-DC CONVERTERS WITH SYNCHRONOUS RECTIFIERS

### 2.1 General concept

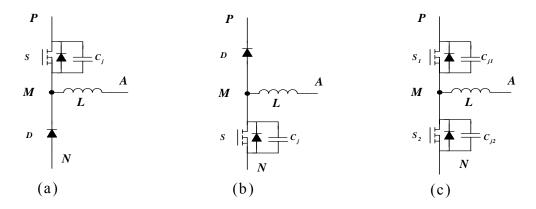

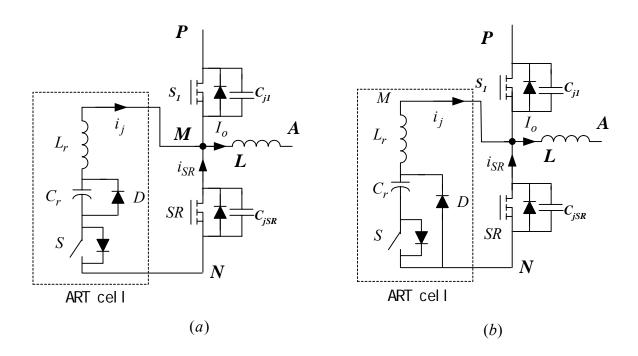

Buck, boost, and buck-boost dc-dc converters are the most common non-isolated dc-dc converters. Each converter is composed of a 3-terminal cell as shown in Fig. 2.1, wherein Fig. 2.1 (a) shows a cell with a diode rectifier for Buck and Buck-Boost converters, where Cj is MOSFET's junction capacitance. Figure 2.1 (b) shows a cell for Boost converter with diode rectifier. Replacing the rectifier diode by an SR in the three basic dc-dc converters, a common cell is derived as shown in Fig. 2.1(c). For Buck and Buck-Boost converters, MOSFET S1 functions as an active switch and MOSFET S2 functions as a SR, and vice versa for the Boost converter,

- (a) Buck and Buck-Boost's cell

- (b) Boost's cell

- (c) Common cell with a SR

Fig. 2. 1: Cells in non-isolated dc-dc converters

Reviewing the principle of switching commutation in a conventional dc-dc converter with a SR, the active switch operates at hard switching, while SR operates at ZVS turn-on. Buck converter cell is shown in Fig. 2.2 with the current injection cell excluded, and the associated key waveforms are shown in Fig. 2.3(a) assuming switches are ideal and the inductance current is constant. When Switch S1 turns off, inductor current charges junction capacitance C<sub>j1</sub> and discharges junction capacitance C<sub>iSR</sub> until voltage across C<sub>iSR</sub> reaches zero, and the body diode Db SR conducts current; after that SR turns on with ZVS and inductor current freewheels through SR. Freewheeling mode ends up with the turn-off of the SR forcing inductor current to shift from SR to its body diode Db SR. Then Switch S1 turns on with the junction capacitance C<sub>11</sub> discharging through S1. Due to the SR's body-diode reverse-recovery current, the active switch S1 suffers from extra turn-on loss and the SR's body diode suffers from hard turn-off loss. In short, in the Buck converter, active switch S1 operates at undesirable conditions due to hard turn-on; the SR operates at ZVS turn-on, but the body diode's reverse recovery leads to extra switching loss and EMI problems. Because the body diodes' reverses-recovery characteristic becomes worse with increase of MOSFETs' voltage rating, SR's applications are still limited to low voltage range.

Fig. 2. 2: Concept of current injection cell in a Buck converter

Fig. 2. 3: Key Concept of current injection cell

# 2.2 Current injection cell to achieve zero-voltage-switching (ZVS)

From the analyses of switching operation in Buck converter, we observe that the SR's turn-on and Switch  $S_1$ 's turn-off are desirable, while the SR's turn-off and Switch  $S_1$ 's turn-on are undesirable due to  $S_1$ 's hard turn-on and reverse-recovery of the SR's body diode. The ideal switching operation is: all switches of the body diodes conduct prior to turn-on of the switches, and all switches turn off with inductive load instead of capacitive load. In other words, to avoid hard turn-off of the body diode, the current commutation sequence must be from a switch to the body diode of the other switch instead of from a body diode of a switch to the other switch.

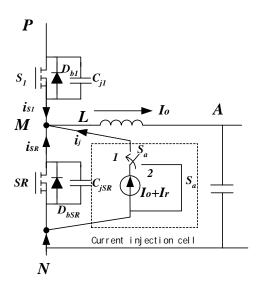

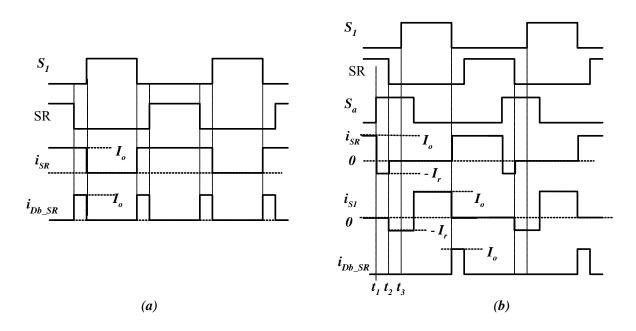

As shown in Fig. 2.2, a current injection cell is placed in parallel with the SR to help Buck converter to achieve an ideal switching commutation discussed above. Switch Sa is turned "on" at Position "1" to inject current  $I_r + I_o$  in the converter. The key waveforms are given in Fig. 2.3(b) assuming switches are ideal and the inductance current is constant. Basically, the cell is utilized to ensure the SR turns off at inductive load and its body diode is not involved in during the turn-off interval. During freewheeling mode while  $t < t_1$ , SR carries freewheeling current:  $i_{ss}(t) = I_o$ . At  $t = t_1$ , the cell is activated and a current is injected into the node M, where the equation  $i_{ss} + i_j = I_o$  is satisfied, forcing SR current to reverse with  $i_{ss}(t_1) = -I_r$ . At  $t = t_2$ , SR turns off and current  $I_r$  charges the junction capacitance  $C_{ss}$  and discharges  $C_{j1}$ , and eventually the body diode  $D_{b1}$  is involved to carry current  $I_r$ . At  $t = t_3$ , Switch S1 turns on at ZVS. During the interval  $t_1 < t < t_3$ , SR's body diode never conducts, thus the body diode reverse recovery loss is eliminated; moreover, the active switch  $S_1$  achieves ZVS with the help of current injection cell.

Therefore, both the SR and the active switch operate at ZVS conditions, and the converter operates at desirable conditions.

#### 2.3 Implementation of the current injection cell with (ART)

Fig. 2.4 shows two candidate circuits consisting of a LC tank and an active switch. Assuming the resonant capacitor Cr is pre-charged to  $2V_{PN}$  and SR is on to carry freewheeling current  $I_o$ . With the turn-on of the active switch S, the capacitor Cr starts to charge the resonant inductor Lr as a resonant manner through the switch SR. Ignoring the power loss during the resonance, the current in the resonant inductor Lr is given by:

$$i_{Lr}(t) = \frac{2V_{PN}}{L_r \omega_o} \sin(\omega_o t) \qquad (0 \le t \le \frac{\pi}{2\omega_o})$$

Eq. 2. 1

The resonant capacitor voltage is given by:

$$v_{cr}(t) = 2V_{PN}\cos(\omega_o t) \qquad (0 \le t \le \frac{\pi}{2\omega_o})$$

Eq. 2. 2

where  $\omega_o = \frac{1}{\sqrt{L_r C_r}}$ , the resonance ends with resonant capacitor voltage reaches zero:  $V_{Cr} = 0$ ,

and the resonant current reaches its maximum as:

$$I_j = I_{L_r \max} = \frac{2V_{PN}}{Z_0}$$

Eq. 2. 3

Where the circuit characteristic impedance,  $Z_0$ , defined as:

$$Z_0 = \sqrt{\frac{L_r}{C_r}}$$

Eq. 2. 4

After that, resonant inductor current freewheels through the diode D in the ART cell. If the injected current is larger than output current,  $I_j > I_o$ , the SR current is reversed during the freewheeling duration of the resonant inductor,  $I_{SR} = I_o - I_j$ . Later on, SR turns off, the additional inductor energy is utilized to charge the junction capacitance  $C_{jSR}$  and discharge  $C_{j1}$ . Therefore, the additional inductor energy must be at least equal to the energy stored in  $C_{jSR}$  and  $C_{j1}$  for the body diode of switch  $S_1$  to conduct and for the switch  $S_1$  to turn on at ZVS, this condition implies the following:

$$\frac{1}{2}L_r(I_j - I_o)^2 \ge \frac{1}{2}(C_{jSR} + C_{j1})V_{PN}^2$$

Eq. 2. 5

With the turn-on of the switch  $S_1$ , the node M is connected to a voltage source, the inductor current decreases to zero and becomes negative, then the resonant capacitor starts charging in a resonant manner. During the capacitor-charging period, the cell switch S turns off at ZVS. The resonance ends with inductor current going back to zero and the capacitor voltage reaches  $2V_{PN}$ . It should be noted that the cell switch is activated only during the current commutation interval from the SR to  $S_1$ .

Fig. 2. 4: Active resonant tank (ART) cells

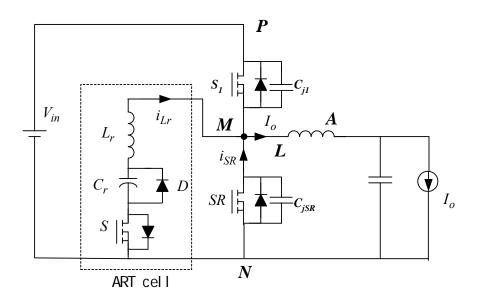

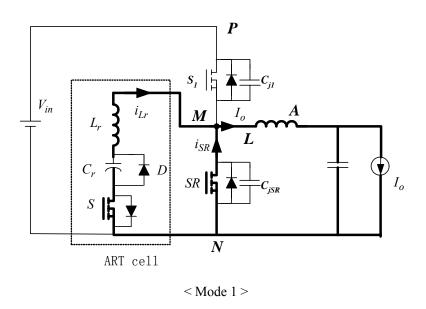

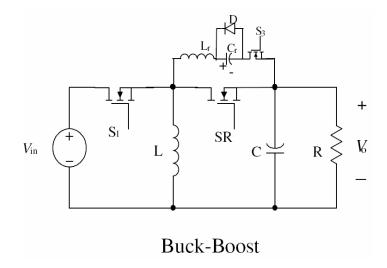

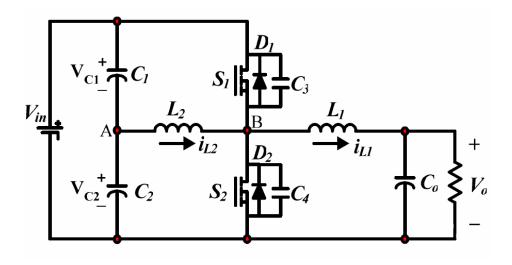

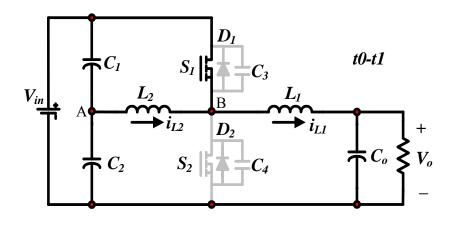

#### 2.4 Modes of operation analyses

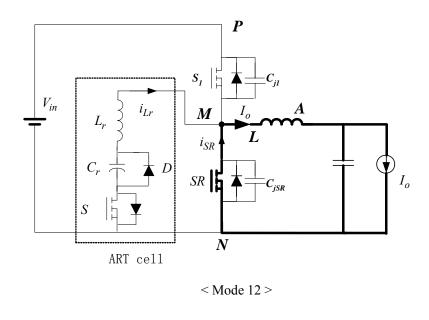

The ART cell can be applied to common bridge cells of non-isolated converters. Since the cell's principle of operation is similar in different topologies, this section presents detailed analyses of the SR Buck converter with the ART cell as an example, as shown in Fig. 2.5. The ART switch is implemented using a P-channel MOSFET that requires a negative gate driving voltage.

To simplify the analyses of operation, components are considered ideal except otherwise indicated. The output filter inductance is assumed large enough and the inductor current is constant in all the modes. The main equivalent circuits for main operation modes are shown in

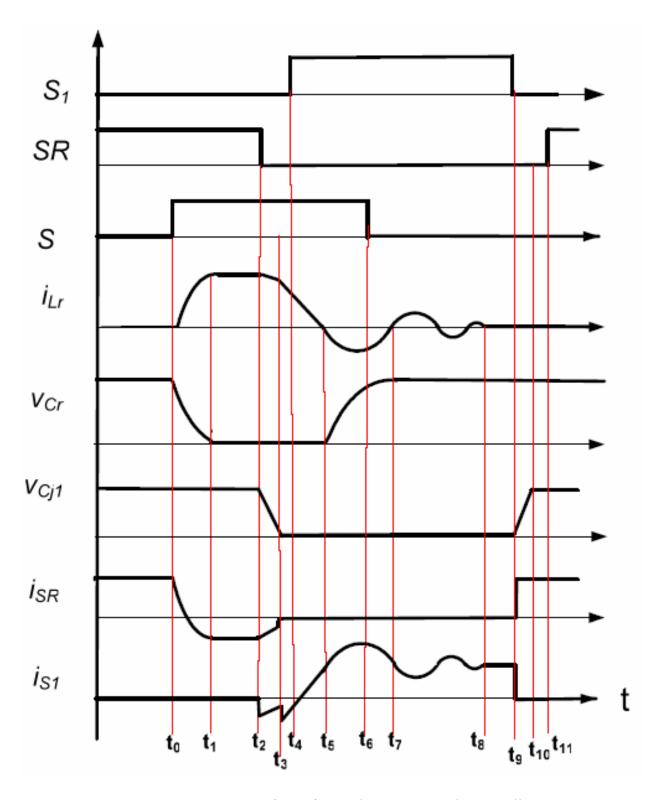

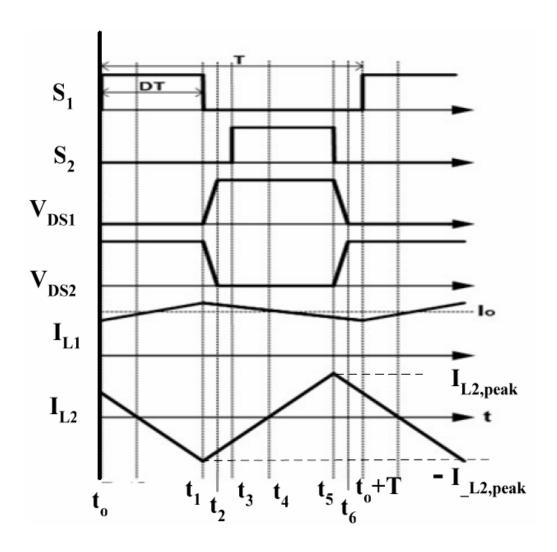

Fig. 2.6 and the key waveforms are shown in Fig, 2.7; it should be noted that the time scale in Fig. 2.7 is magnified during the transition period between switches S1 and SR in order to clarify the modes of operation of the presented ART cell. The modes of operation are described as follows:

Fig. 2. 5: Buck converter with ART cell

**Mode 1** ( $t_0 < t < t_1$ ): The resonant capacitor Cr was pre-charged with  $v_{Cr}(t_0) = 2Vin$ , and the filter inductor L freewheels through the SR. This mode starts with turn-on of the switch S at  $t=t_0$ , where the inductor current  $i_j(t_0) = 0$ . Cr charges Lr at resonant manner; the associated voltage and current are given by:

$$i_{Lr}(t) = \frac{2V_{in}}{L_r\omega_o}\sin(\omega_o t) \qquad (0 \le t \le \frac{\pi}{2\omega_o})$$

Eq. 2. 6

$$v_{Cr}(t) = 2V_{in}\cos(\omega_o t) \qquad (0 \le t \le \frac{\pi}{2\omega_o})$$

Eq. 2. 7

Where

$$\omega_o = \frac{1}{\sqrt{L_r C_r}}$$

The mode ends at  $t = t_1 = \frac{\pi}{2\omega_o}$  with the capacitor voltage discharged to zero, and the resonant current reaching maximum value:

$$i_{Lr}(t_1) = \frac{2V_{in}}{\omega_o L_r}$$

Eq. 2. 8

Fig. 2.6 a

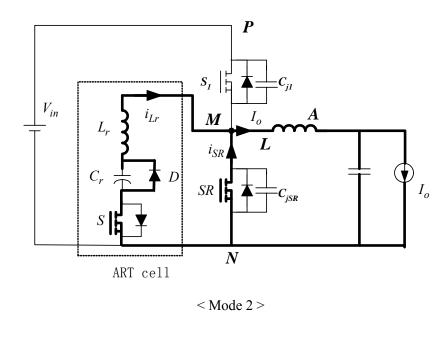

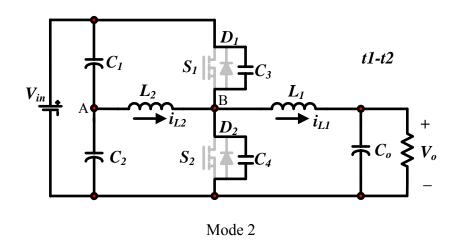

Mode 2  $(t_1 < t < t_2)$ : With the resonant capacitor Cr voltage reaching zero, the diode D in the cell carries current, and the inductor is trapped in the short-circuit loop. Assuming the inductor

current value  $i_{Lr}(t_1) > I_o$ , the SR current is reversed with the value of  $(i_{Lr}(t_1) - I_o)$ . As a matter of fact, inductor L freewheels through the ART cell during this mode.

Fig.2.6 b

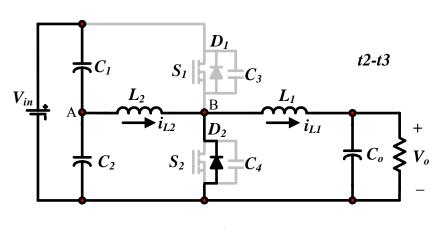

*Mode 3* (t2 < t < t3): SR turns off at t = t2, and the inductor current previously flowing through the SR charges the junction capacitance  $C_{jSR}$  and discharges  $C_{j1}$  until the switch of the S1 body diode conducts in Mode 4.

111040

Fig.2.6 c

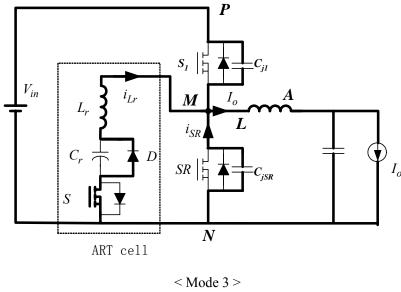

**Mode 4**  $(t_3 < t < t_4)$ : When the junction capacitance voltage across the switch S<sub>1</sub> is discharged to zero  $t = t_3$ , body diode conducts to carry current. To ensure body-diode conduction, the following estimated condition should be satisfied:

$$\frac{1}{2}L_r(\frac{2V_{in}}{\omega_o L_r} - I_o(t_2))^2 \ge \frac{1}{2}(C_{jSR} + C_{j1})V_{in}^2$$

Eq. 2. 9

The inductor current at t<sub>3</sub> satisfy:

$$\frac{1}{2}L_r(\frac{2V_{in}}{\omega_o L_r} - i_{Lr}(t_3))^2 = \frac{1}{2}(C_{jSR} + C_{j1})V_{in}^2$$

Eq. 2. 10

Solving Equation (2.10) obtains the inductor current at t<sub>3</sub>:

$$i_{Lr}(t_3) = \frac{2V_{in}}{\omega_o L_r} - V_{in} \sqrt{\frac{C_{jSR} + C_{j1}}{L_r}}$$

Eq. 2. 11

According to Equation (2.9), there is shown  $i_{Lr}(t_3) \ge I_o$ . During this mode, through the body diode of the switch  $S_1$ , the resonant inductor current  $i_{Lr}$  resets towards a steady-state value of  $I_o$ . The inductor current resets as the following slew rate:

$$\frac{di_{Lr}(t)}{dt} = \frac{V_{in}}{L_r} \qquad (t_3 \le t \le t_4)$$

Eq. 2. 12

Fig.2.6 d

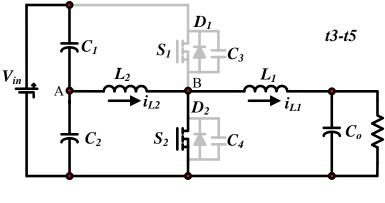

*Mode 5* ( $t_4 < t < t_5$ ): At t = t<sub>4</sub>, the switch S<sub>1</sub> turns on at ZVS. The resonant inductor current continues to decrease with the slew rate in Equation (2.12). When the resonant inductor current decreases to output filter inductor current  $I_0$ , the current in the switch S<sub>1</sub> reverses the direction and becomes positive. After that, the S<sub>1</sub> current increases and the resonant inductor current decreases with the same slew rate as in Equation (2.12).

Fig.2.6 e

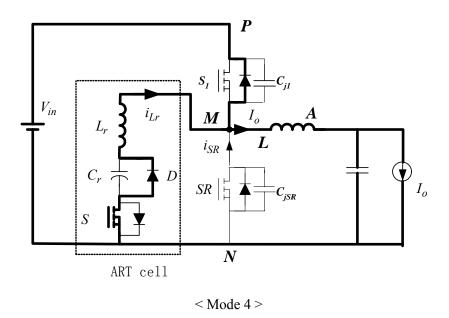

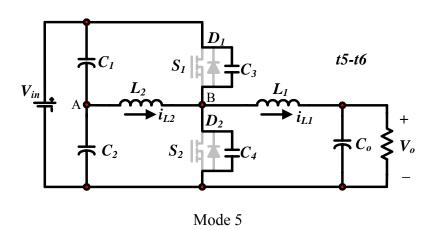

**Mode 6** ( $t_5 < t < t_6$ ): When the switch  $S_1$  current increases to the filter inductor current  $I_0$ , the resonant inductor current reverses the direction and becomes negative, then the diode D is blocked, and the resonant capacitor Cr is involved in a resonance. The ART tank is charged in a resonant manner, and the resonant inductor current is given by:

$$i_{Lr}(t) = \frac{-V_{in}}{L_r \omega_o} \sin \omega_o(t - t_5)$$

$(t_5 \le t \le t_5 + \frac{\pi}{\omega_o})$  Eq. 2. 13

The resonant capacitor voltage is given by:

$$v_{Cr}(t) = V_{in}(1 - \cos \omega_o(t - t_5))$$

$(t_5 \le t \le t_5 + \frac{\pi}{\omega_o})$  Eq. 2. 14

where

$$\omega_o = \frac{1}{\sqrt{L_r C_r}}$$

.

Fig. 2.6 f

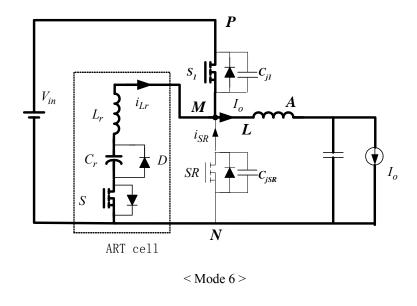

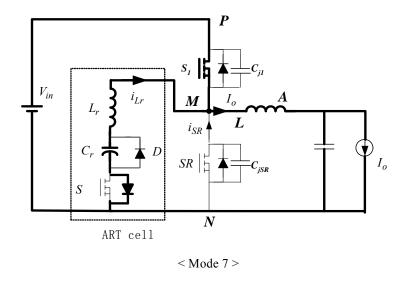

Mode 7 ( $t_6 < t < t_7$ ): The ART cell's switch S turns off at ZVS and the carried resonant current shifts to its body diode and the resonance continues as described in Equations (2.13) and (2.14) in Mode 6. The sinusoidal resonant current rises to the peak and then decreases towards zero. The resonance ceases with the capacitor voltage reaching the peak ( $v_{Cr}(t_7) = 2V_{in}$ ) and the inductor current reaches zero ( $i_r(t_7) = 0$ ). The total duration of time in Mode 6 and 7 is determined by the parameters of the ART.

$$\Delta T = t_7 - t_5 = \pi \sqrt{L_r C_r}$$

Eq. 2. 15

Fig. 2.6 g

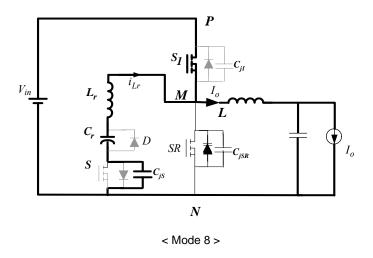

*Mode 8* ( $t_7 < t < t_8$ ): At  $t=t_7$ , the voltage across the resonant capacitor reaches  $2V_{in}$ , and the resonant inductor current becomes zero. After that, the circuit goes into damped ringing caused by the involvement of the switch S junction capacitor. When body diode of switch S was conducting in mode 7, the junction capacitor of switch S was not charged; at the beginning of mode 8, the body diode stops conducting and the junction capacitor of switch S is charged towards a steady-state voltage level Vin. This forms a resonant circuit composed of the input voltage Vin, resonant inductor Lr, resonant capacitor  $C_r$  and the junction capacitor of the switch S, all in series as shown in Fig. 2.6(h). Considering the capacitance value of the capacitor Cr is much greater than that of the junction capacitor  $C_{js}$ , the resonant inductor Lr and the junction capacitor  $C_{js}$  determine the resonant manner; the resonant frequency is estimated by:

$$\omega_r = \frac{1}{\sqrt{L_r C_{is}}}$$

Eq. 2. 16

Fig. 2.6 h

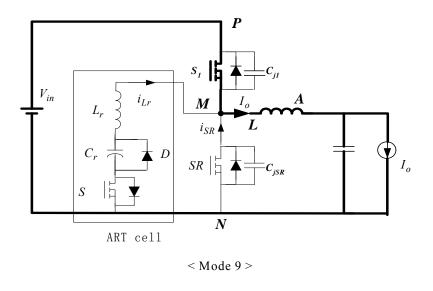

Mode 9 ( $t_8 < t < t_9$ ): The ringing is dampened by the equivalent resistance along the path of the resonant loop. At  $t = t_8$ , the ART cell is naturally inactive and separated from the converter. In this mode, the output filter is charged and the input power is delivered to the output.

Fig.2.6 i

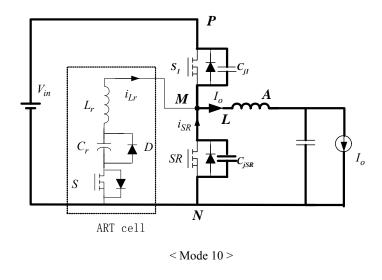

*Mode 10* ( $t_9 < t < t_{10}$ ): At  $t = t_9$ , the switch  $S_1$  turns off, the filter inductor charges the junction capacitance  $C_{j1}$  and discharges  $C_{jSR}$ .

Fig.2.6 j

*Mode 11* ( $t_{10} < t < t_{11}$ ): When the junction capacitance voltage reaches zero, the SR body diode conducts carrying the output inductor current, which provides ZVS turn-on condition for the SR.

Fig.2.6 k

*Mode 12* ( $t_{II} < t < t_0 + T$ ): During the body-diode conduction interval, the SR turns on at ZVS, and the converter enters into inductor freewheeling mode. With the turn-on of the switch S, the converter goes back to Mode 1.

Fig. 2.6 l

Fig. 2. 6: Equivalent circuits of modes of operation

Fig. 2. 7: Key waveforms for Buck converter with ART cell

#### 2.5 Features and design considerations

As discussed above, by adding an ART cell in parallel with synchronous rectifiers in non-isolated dc-dc converters, the SR's body diode conduction and the related reverse recovery are eliminated, and the ART cell energy is released for the active switch to turn on at ZVS. In addition, the ART cell's auxiliary switch S turns on at ZCS and turns off at ZVS; thus, the related switching loss is minimized. Since the ART cell is activated only during the switching transition, the conduction loss in the cell is limited.

The presented topology is advantageous especially for high voltage synchronous rectifiers. Generally, the synchronous rectification is limited to applications with low voltage ratings of MOSFETs (usually below 150V) because the SR's body-diode reverse recovery becomes more significant with the increase of MOSFET voltage ratings. In the meanwhile, with ever-decreasing on-resistance of MOSFETs, conduction loss can be dramatically reduced with synchronous rectifiers replacing Schottky or ultra-fast-recovery diodes in high-voltage rectification applications. The presented ART cell provides a solution to the problem and allows high-voltage MOSFETs to be used as SRs since reverse recovery and related loss are eliminated.

The resonant inductance  $L_r$  and capacitance  $C_r$  values determine the time constant of the ART resonant tank. To ensure the body diode is not conducting at its worst, that of full load and low-

line input, the ART cell must store and release sufficient energy. According to Equation (2.9), the resonant inductor peak current satisfies if

$$i_{Lr,pk} = i_{Lr}(t_2) > I_o(t_2)$$

Eq. 2. 17

The body diode conduction can be avoided when the SR turns off and the active switch  $S_1$  could probably achieve ZVS. In an engineering design, output filter inductance is finite, and the output current ripple is necessary considered. At  $t = t_2$ , the output filter inductor current almost reaches the low peak, and the full load current is:

$$I_{o,\text{max}} = I_o(t_2) + \frac{\Delta I_o}{2}$$

Eq. 2. 18

Where  $\Delta I_o$  is the output inductor current ripple. Approximately, the ART cell is designed to make the resonant inductor peak current satisfy  $i_{Lr,pk} = I_{o,\max}$ , the condition of Equation (2.17) is satisfied, and thus body diode conduction is eliminated and Switch S1 has a good chance to achieve ZVS. The resonant inductor peak current can be obtained and designed as equal to full load current:

$$i_{Lr,pk} = 2V_{in,\min} \sqrt{\frac{C_r}{L_r}} = I_{o,\max}$$

Eq. 2. 19

Where  $V_{in,min}$  is the low-line input voltage. As described in Mode 7, during the time while the ART cell is being recharged, the auxiliary switch S turns off at ZVS. To secure the auxiliary switch S has sufficient time to turn off with ZVS during the cell-recharging period, the ART cell's recharging period of time has to be sufficiently long. Meanwhile, the recharging time should be limited to reduce conduction loss of the cell. According to Equation (2.15), the ART

recharging time is determined by the cell's parameters. We assume the required time for recharging is  $T_d$ , the cell parameters satisfy:

$$\pi \sqrt{L_r C_r} = T_d$$

Eq. 2. 20

By solving Equation (2.18) and (2.19), the ART cell parameters are designed as follows: