Dynamic modeling of PWM and single-switch single-stage power factor correction converters

Zhu, Guangyong

ProQuest Dissertations and Theses; 1999; ProQuest Dissertations & Theses (PQDT)

pg. n/a

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand corner and continuing from left to

right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning

300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

## DYNAMIC MODELING OF PWM AND SINGLE-SWITCH SINGLE-STAGE POWER FACTOR CORRECTION CONVERTERS

By

GUANGYONG ZHU B.E., Hunan University, P. R. China, 1984 M.E., Tsinghua University, P. R. China, 1987

A dissertation submitted in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

in the Department of Electrical and Computer Engineering

in the College of Engineering

at the University of Central Florida

Orlando, Florida

Fall Term 1999

Major Professor: Dr. Issa Batarseh

UMI Number: 9950349

#### UMI Microform 9950349

Copyright 2000 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **ABSTRACT**

The concept of averaging has been used extensively in the modeling of power electronic circuits to overcome their inherent time-variant nature. Among various methods, the PWM switch modeling approach is most widely accepted in the study of closed-loop stability and transient response because of its accuracy and simplicity. However, a non-ideal PWM switch model considering conduction losses is not available except for converters operating in continuous conduction mode (CCM) and under small ripple conditions. Modeling of conduction losses under large ripple conditions has not been reported in the open literature, especially when the converter operates in discontinuous conduction mode (DCM). In this dissertation, new models are developed to include conduction losses in the non-ideal PWM switch model under CCM and DCM conditions. The developed model is verified through two converter examples and the effect of conduction losses on the steady state and dynamic responses of the converter is also studied.

Another major constraint of the PWM switch modeling approach is that it heavily relies on finding the three-terminal PWM switch. This requirement severely limits its application in modeling single-switch single-stage power factor correction (PFC) converters, where more complex topological structures and switching actions are often encountered. In this work, we developed a new modeling approach which extends the

PWM switch concept by identifying the charging and discharging voltages applied to the inductors. The new method can be easily applied to derive large-signal models for a large group of PFC converters and the procedure is elaborated through a specific example. Finally, analytical results regarding harmonic contents and power factors of various PWM converters in PFC applications are also presented here.

#### ACKNOWLEDGMENTS

I'd like to express my sincere appreciation to my advisor, Dr. Issa Batarseh, for giving me the opportunity to work toward my Ph.D. degree at UCF and providing me with a pleasant and productive research environment. His sharp academic insight and strong encouragement pushed me steadily to my present achievement. This work would not have been completed without his excellent technical guidance and continued support. In particular, his warm personality and friendship made my experience at this university one of the most cherished of my life.

I'd also like to thank my former advisor, Dr. Adrian Ioinovici, for bringing me into the wonderful field of power electronics. His extensive knowledge and serious attitude toward research has provided me with a role model in my academic study.

I wish to take this opportunity to thank Dr. Huai Wei and Dr. Peter Kornetzky for providing me with the experimental data used in this work. Stimulating and productive discussions with them and, especially those with Mr. Chris Iannello and Dr. Shiguo Luo, helped me extend my understanding of power electronics. Their friendship made my study a joyful and rewarding experience.

I am extremely grateful to my wife, Karen, for always being there with her love, care and support and for sharing with me my joy and success. I am greatly indebted to her

and to our daughter, Joanna, for letting me turn my attention away from them and concentrate on my research over the years.

Finally, I'd like to express my deepest gratitude and appreciation toward my parents and sisters, who always stood by me in the difficult years. This work, in large part, is a confirmation of their confidence in me.

# **TABLE OF CONTENTS**

| CHAPTER 1 INTRODUCTION                                                  | 1      |

|-------------------------------------------------------------------------|--------|

| 1.1. Origin of Harmonics                                                | 2      |

| 1.2. Single-Switch Single-Stage PFC Converters                          | 8      |

| 1.3. Dissertation Outline                                               |        |

| CHAPTER 2 AVERAGE MODELING TECHNIQUE OF DC/DC                           |        |

| CONVERTERS                                                              | 17     |

| 2.1. Introduction                                                       | 17     |

| 2.2. State-Space Average Modeling                                       | 20     |

| 2.2.1. Continuous conduction mode                                       |        |

| 2.2.2. Discontinuous conduction mode                                    | 24     |

| 2.3. Three-Terminal PWM Switch Modeling                                 | 28     |

| 2.3.1. Continuous conduction mode                                       | 29     |

| 2.3.2. Discontinuous conduction mode                                    | 32     |

| 2.4. The PWM Switch Model of the Flyback and Weinberg Converters        | 36     |

| 2.4.1. The flyback converter                                            | 36     |

| 2.4.2. The Weinberg converter                                           | 39     |

| 2.5. Challenges in Modeling PFC Converters                              | 43     |

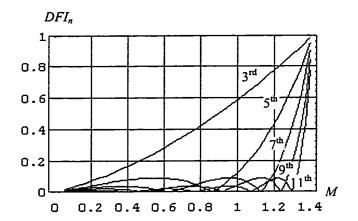

| CHAPTER 3 POWER FACTOR AND HARMONICS IN PWM CONVER                      | TERS47 |

| 3.1. Introduction                                                       | 47     |

| 3.2. Definition of Power Factor and Total Harmonic Distortion           | 48     |

| 3.3. Power Factor and Harmonic Current Distortion of Basic PFC Circuits | 50     |

| 3.3.1. Buck PFC circuit                                                        | 52           |

|--------------------------------------------------------------------------------|--------------|

| 3.3.2. Boost PFC circuit                                                       | 55           |

| 3.3.3. Buck-boost PFC circuit                                                  | 60           |

| 3.4. Output Voltage of the PFC Stage                                           | 61           |

| 3.5. Verification of the Power Factor and Harmonic Current Distortion in Basic | ic PFC       |

| Circuits                                                                       | 65           |

| 3.6. Summary                                                                   | 70           |

| CHAPTER 4 SMALL-SIGNAL MODELING OF A SINGLE-SWITCH AC                          | C/ <b>DC</b> |

| PFC CIRCUIT BASED ON STATE-SPACE AVERAGING METHOD                              | 71           |

| 4.1. Introduction                                                              | 71           |

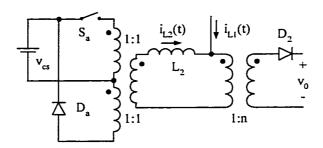

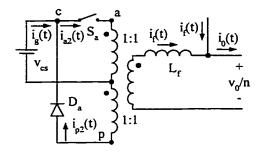

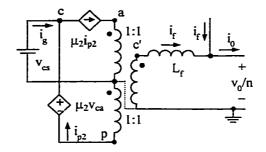

| 4.2. Review of the Circuit Operation                                           | 74           |

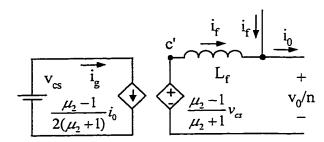

| 4.3. State-Space Averaging Model                                               | 81           |

| 4.3.1. Steady state model                                                      | 83           |

| 4.3.2. Small signal dynamic model                                              | 85           |

| 4.4. Experimental Verification                                                 | 92           |

| 4.5. Summary                                                                   | 98           |

| CHAPTER 5 PWM SWITCH MODELING OF SINGLE-SWITCH POWE                            | E <b>R</b>   |

| FACTOR CORRECTION CONVERTERS                                                   | 99           |

| 5.1. Introduction                                                              | 99           |

| 5.2. Correcting the Pspice Large-Signal Model for DCM PWM Converters           |              |

| 5.2.1. Analysis and modification of the model                                  | 103          |

| 5.2.2. Verification of the modified model                                      | 105          |

| 5.3. Modeling of Conduction Losses in PWM Converters                           | 107          |

| 5.3.1. Conduction losses in DCM converters                                     | 108          |

| 5.3.2. Conduction losses in CCM converters                                     | 112          |

| 5.3.3. Verification of the non-ideal PWM switch model                          | 114          |

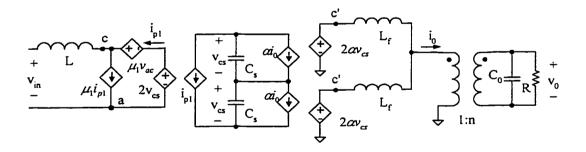

| 5.4. Dynamic Modeling of Single-Switch PWM PFC Converters                      | 123          |

| 6.4.1 Desiration of the DVM assistab model                                     | 123          |

| 5.4.2. Verification of the derived model                             | 137    |

|----------------------------------------------------------------------|--------|

| 5.4.3. Application of the modeling technique to other PFC converters | 141    |

| 5.5. Summary                                                         | 142    |

| CHAPTER 6 CLOSED LOOP DESIGN OF A DISTRIBUTED POWER                  | SUPPLY |

| SYSTEM WITH POWER FACTOR CORRECTION                                  | 143    |

| 6.1. Introduction                                                    | 143    |

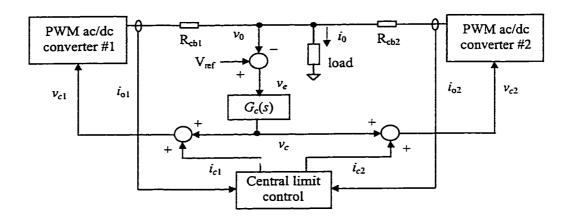

| 6.2. Closed-Loop Design of Two Parallel PFC Converters               | 145    |

| 6.2.1. Description of central limit control scheme                   | 145    |

| 6.2.2. Voltage loop controller design                                | 147    |

| 6.2.3. Current loop controller design                                | 151    |

| 6.3. Simulation Results of the DPS with Power Factor Correction      | 154    |

| 6.4. Summary                                                         | 158    |

| CHAPTER 7 CONCLUSIONS                                                | 160    |

| LIST OF REFERENCES                                                   | 163    |

# LIST OF TABLES

| Table 1-1.IEEE 519 voltage distortion limits                                      | 5   |

|-----------------------------------------------------------------------------------|-----|

| Table 1-2.IEC 1000-3-2 harmonic current limits for class D electric equipment     | 5   |

| Table 3-1.Input harmonic current contents and power factors of the three basic PF | ·C  |

| circuits                                                                          | 69  |

| Table 5-1.Netlist of the Pspice VMLSDCM model                                     | 104 |

| Table 5-2.Netlist of the Pspice LOSSY_LSDCM model                                 | 115 |

| Table 5-3.Netlist of the Pspice FORWARD_LSDCM model                               | 137 |

| Table 6-1 Harmonic contents in the line current (220V line and 4A load current)   | 158 |

# LIST OF FIGURES

| Fig. 1-1. | Maximum permissible harmonic current per watt for class D electric              |     |

|-----------|---------------------------------------------------------------------------------|-----|

|           | equipment                                                                       | .5  |

| Fig. 1-2. | The PFC converter block diagram                                                 | .9  |

| Fig. 1-3. | Three basic DC/DC converters                                                    | 10  |

| Fig. 1-4. | Inductor or line current waveform in CCM for boost PFC converter                | l 2 |

| Fig. 1-5. | Line current waveform of the DCM Buck-boost PFC circuit in a half line          |     |

|           | cycle                                                                           | ι3  |

| Fig. 1-6. | Block diagram of the single-switch single-stage AC/DC converter with            |     |

|           | PFC                                                                             | l 4 |

| Fig. 1-7. | Three typical S <sup>4</sup> -PFC AC/DC converter topologies: (a) Boost/flyback |     |

|           | combination circuit, (b) Boost/forward combination circuit, (c)                 |     |

|           | Boost/forward combination circuit                                               | l 6 |

| Fig ?-1.  | General block diagram of a switched-mode DC/DC regulator                        | 8   |

| Fig. 2-2. | Inductor current waveform in CCM operation                                      | 21  |

| Fig. 2-3. | Inductor current waveform in DCM operation                                      | 25  |

| Fig. 2-4. | A PWM switch and its equivalent circuit model: (a) a PWM switch, (b)            |     |

|           | equivalent circuit model                                                        | 30  |

| Fig. 2-5. | Small signal model of the PWM switch                                            | 32  |

| Fig. 2-6. | The PWM switch model in DCM                                                     | 34  |

| Fig. 2-7. | Small signal model of the PWM switch in DCM                                     | 35  |

| Fig. 2-8. | Topology of the flyback converter                                               | 37  |

| Fig. 2-9. | PWM switch model of the flyback converter: (a) CCM model, (b) DCM               |     |

|           | model                                                                           | 38  |

| Fig. 2-1 | 0. Topology of the Weinberg converter                                              | 40  |

|----------|------------------------------------------------------------------------------------|-----|

| Fig. 2-1 | 1. PWM switch model of the Weinberg converter: (a) CCM model, (b) DCM              |     |

|          | model                                                                              | .40 |

| Fig. 3-1 | . Buck converter operating in DCM: (a) Buck converter, (b) input current in        |     |

|          | a switching period                                                                 | 53  |

| Fig. 3-2 | . Harmonic current distortion factor of the buck converter vs. conversion          |     |

|          | ratio                                                                              | 55  |

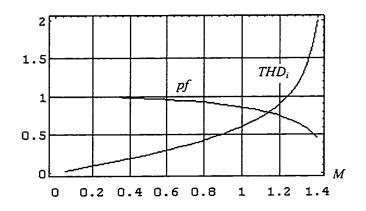

| Fig. 3-3 | . Power factor and total harmonic distortion of the buck converter vs.             |     |

|          | conversion ratio                                                                   | 55  |

| Fig. 3-4 | . Boost converter operating in DCM: (a) Boost converter, (b) input current in      |     |

|          | a switching period                                                                 | 56  |

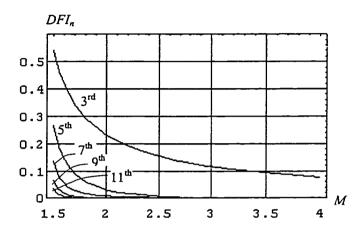

| Fig. 3-5 | . Harmonic current distortion factor of the boost converter vs. conversion         |     |

|          | ratio                                                                              | 59  |

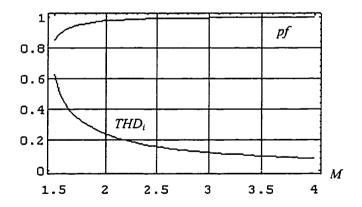

| Fig. 3-6 | . Power factor and total harmonic distortion of the boost converter vs.            |     |

|          | conversion ratio                                                                   | 59  |

| Fig. 3-7 | . Buck-boost converter operating in DCM: (a) buck-boost converter, (b)             |     |

|          | input current in a switching period                                                | 60  |

| Fig. 3-8 | . A flyback/flyback combination PFC circuit                                        | 63  |

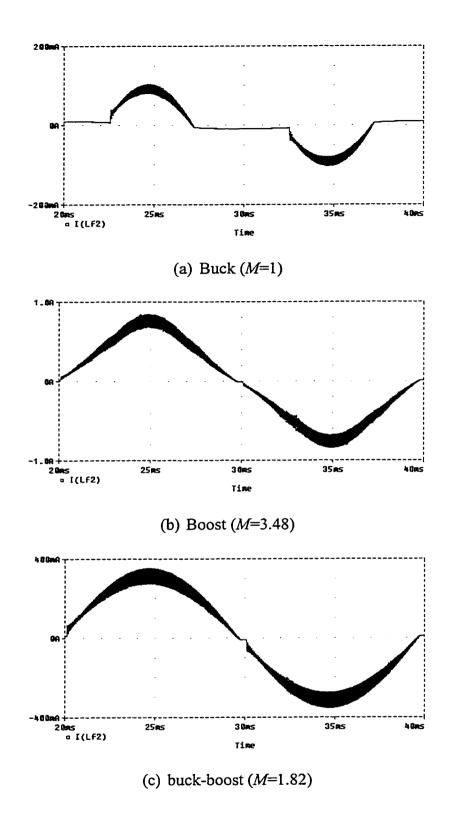

| Fig. 3-9 | . Simulated waveforms of input currents drawn from the line source: (a)            |     |

|          | Buck ( <i>M</i> =1), (b) Boost ( <i>M</i> =3.48), (c) buck-boost ( <i>M</i> =1.82) | 68  |

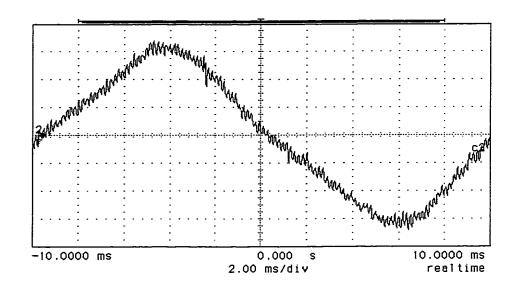

| Fig. 3-1 | 0. Experimental input current waveform of an AC/DC converter (vertical             |     |

|          | scale: 0.25A/div)                                                                  | 69  |

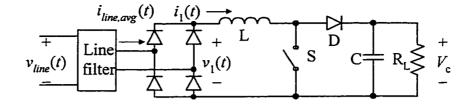

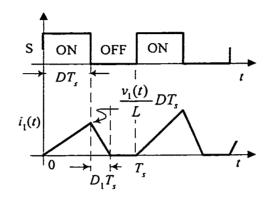

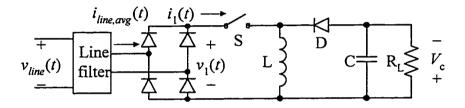

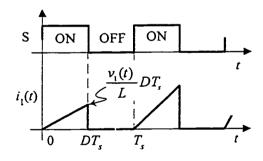

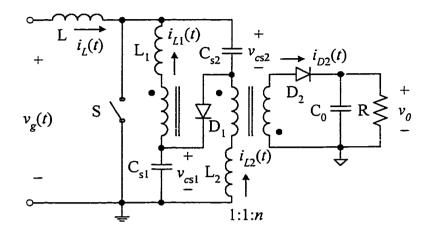

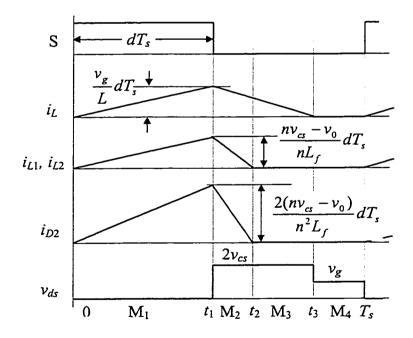

| Fig. 4-1 | . Basic circuit diagram of the PFC converter                                       | 75  |

| Fig. 4-2 | . Key waveforms of the converter                                                   | 75  |

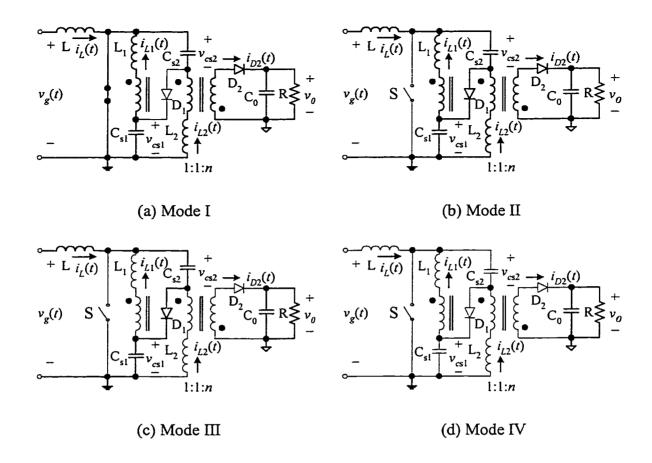

| Fig. 4-3 | . Equivalent circuit of the PFC converter in each mode: (a) Mode I, (b)            |     |

|          | Mode II, (c) Mode III, (d) Mode IV                                                 | 76  |

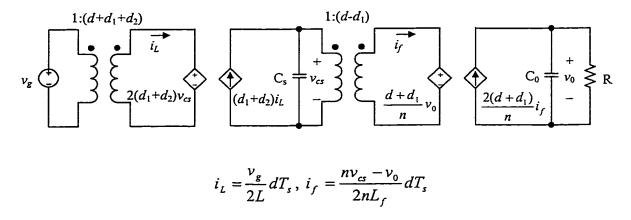

| Fig. 4-4 | . Equivalent circuit of the averaged model                                         | 82  |

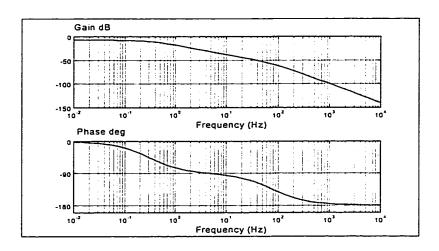

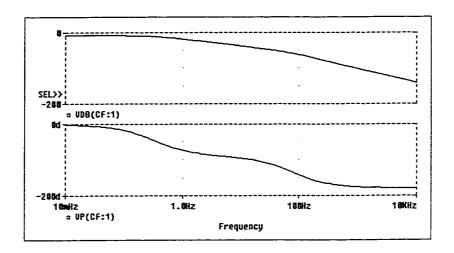

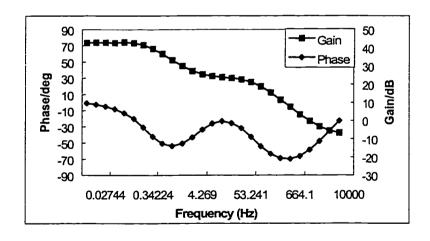

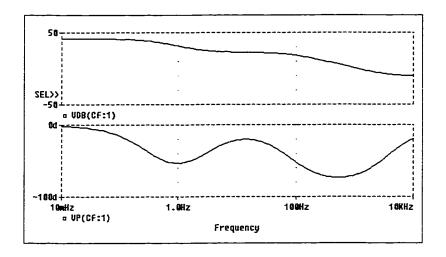

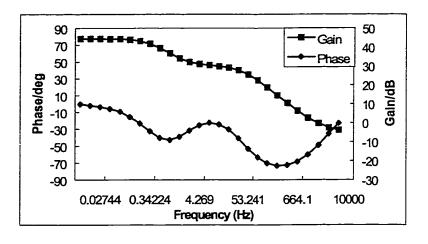

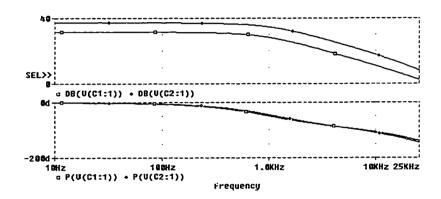

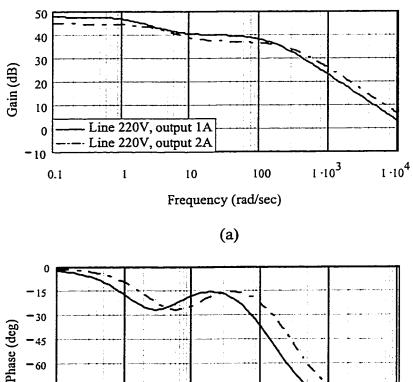

| Fig. 4-5 | Frequency responses for (a) input-to-output, and (b) control-to-output             | 89  |

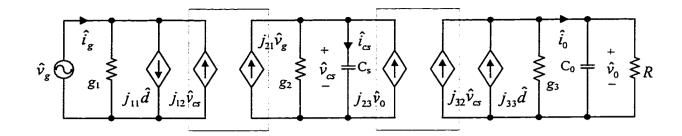

| Fig 4-6  | Small signal equivalent circuit model                                              | 92  |

| Fig. | 4-7.  | Simulated small signal frequency responses for (a) input-to-output, and (b)                     |

|------|-------|-------------------------------------------------------------------------------------------------|

|      |       | control-to-output93                                                                             |

| Fig. | 4-8.  | Measured control-to-output frequency characteristics with the input of (a)                      |

|      |       | 120V (rms), and (b) 120V DC94                                                                   |

| Fig. | 4-9.  | Simulated control-to-output frequency characteristic with output capacitor                      |

|      |       | ESR included95                                                                                  |

| Fig. | 4-10. | Frequency response for a 110V DC input: (a) measured, (b) simulated96                           |

| Fig. | 4-11. | Frequency response for a 150V DC input: (a) measured, (b) simulated97                           |

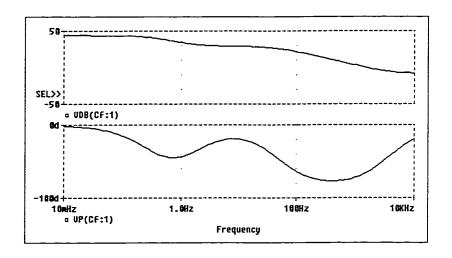

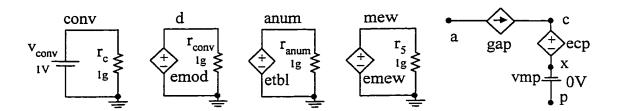

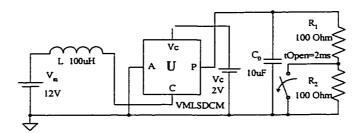

| Fig. | 5-1.  | Pspice circuit diagram for DCM PWM switch model104                                              |

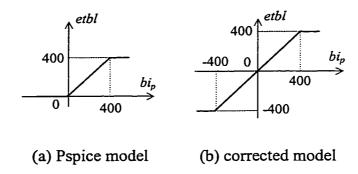

| Fig. | 5-2.  | Controlled voltage source <i>etbl</i> vs. current $i_p$ ( $b = 2L_{fi}f_s$ ): (a) Pspice model, |

|      |       | (b) corrected model105                                                                          |

| Fig. | 5-3.  | Schematic diagram of the boost converter using the Pspice VMLSDCM                               |

|      |       | model106                                                                                        |

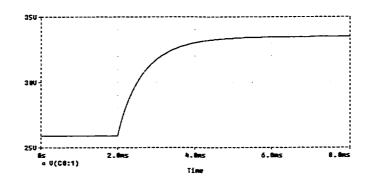

| Fig. | 5-4.  | Output voltage of the boost converter with the corrected VMLSDCM                                |

|      |       | model106                                                                                        |

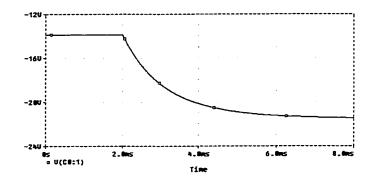

| Fig. | 5-5.  | Output voltage of the boost converter with the existing Pspice VMLSDCM                          |

|      |       | model107                                                                                        |

| Fig. | 5-6.  | Inductor current with ideal (solid line) and non-ideal (dashed line)                            |

|      |       | components108                                                                                   |

| Fig. | 5-7.  | DCM PWM switch circuit model with conduction losses                                             |

| Fig. | 5-8.  | Ideal inductor current waveform for CCM condition113                                            |

| Fig. | 5-9.  | Simulation results for the Buck converter with small conduction losses118                       |

| Fig. | 5-10. | Simulation results for the Boost converter with small conduction losses118                      |

| Fig. | 5-11. | Simulation results for the Buck converter with large conduction losses119                       |

| Fig. | 5-12. | Simulation results for the Boost converter with large conduction losses119                      |

| Fig. | 5-13. | Control-to-output transfer functions of the ideal (◊) and non-ideal (□) Buck                    |

|      |       | converters with a load resistance of 6Ω121                                                      |

| Fig. | 5-14. | Input-to-output transfer functions of the ideal (◊) and non-ideal (□) Buck                      |

| -    |       | converters with a load resistance of 6O                                                         |

| Fig. 5-1: | 5. Control-to-output transfer functions of the ideal (0) and non-ideal (1) Boost |

|-----------|----------------------------------------------------------------------------------|

|           | converters with a load resistance of $12\Omega$                                  |

| Fig. 5-1  | 6. Input-to-output transfer functions of the ideal (◊) and non-ideal (□) Boost   |

|           | converters with a load resistance of $12\Omega$                                  |

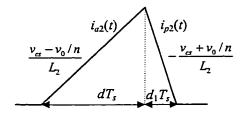

| Fig. 5-1  | 7. Leakage inductor current waveform $(i_{L2}(t))$ 124                           |

| Fig. 5-1  | 3. A fictitious circuit which generates the current waveform in Fig. 5-17125     |

| Fig. 5-19 | 9. Simplified fictitious switching circuit of Fig. 5-18                          |

| Fig. 5-20 | ). PWM switch model of the fictitious switching circuit128                       |

| Fig. 5-2  | 1. Simplified PWM switch model of the fictitious switching circuit129            |

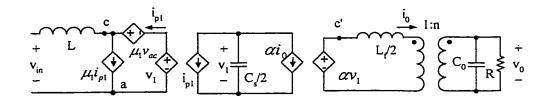

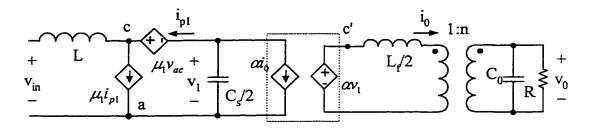

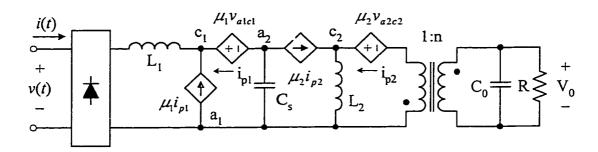

| Fig. 5-22 | 2. The complete large-signal circuit model of the PFC converter131               |

| Fig. 5-2  | 3. Simplified circuit model of the PFC converter ( $v_1=2v_{cs}$ )               |

| Fig. 5-2  | 4. The final large-signal circuit model of the PFC converter $(v_1=2v_{cs})$ 133 |

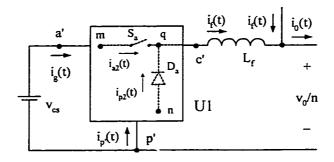

| Fig. 5-2  | 5. Switching circuit block diagram of the output stage134                        |

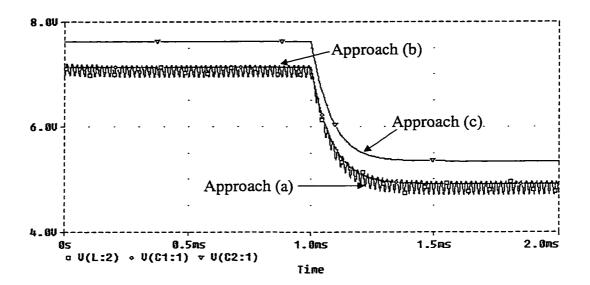

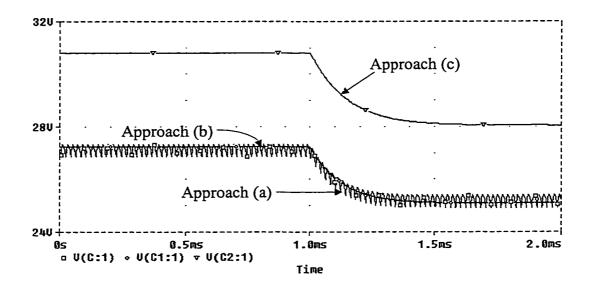

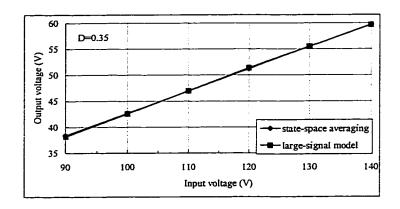

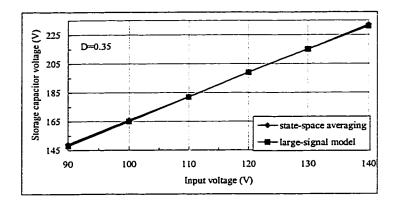

| Fig. 5-2  | 6. Steady-state output and capacitor voltages from two approaches: (a) output    |

|           | voltage vs. input voltage, (b) storage capacitor voltage vs. input voltage138    |

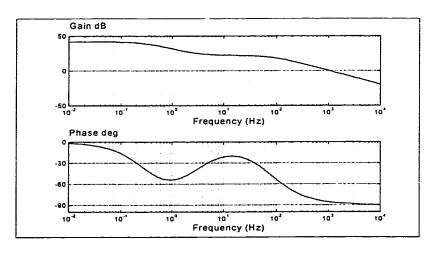

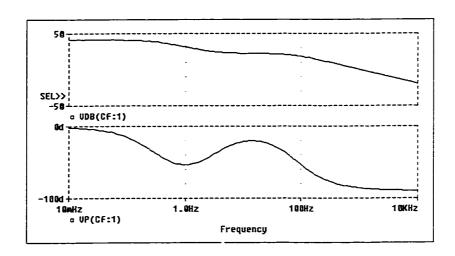

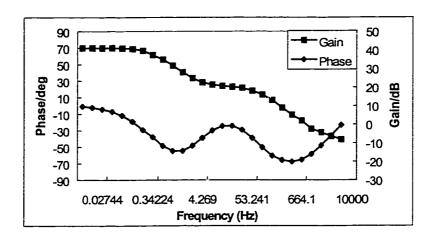

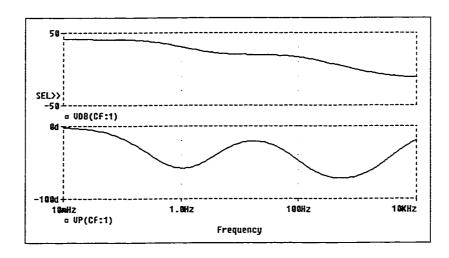

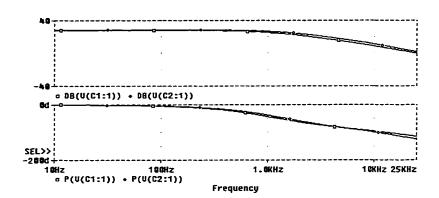

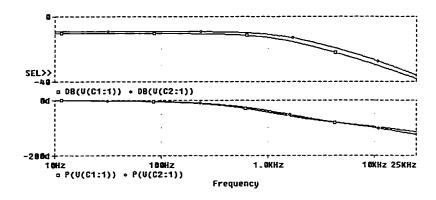

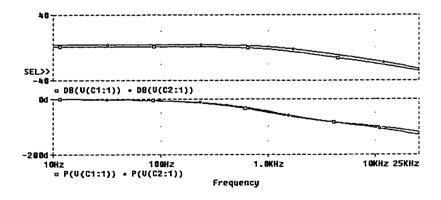

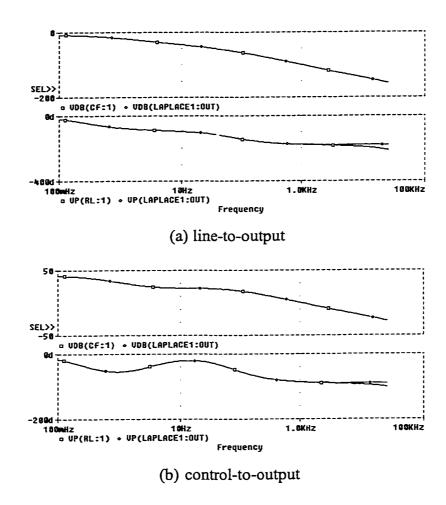

| Fig. 5-2  | 7. Bode plots of the small-signal frequency responses of the derived model (◊-   |

|           | state space averaging model,   -derived model): (a) line-to-output, (b)          |

|           | control-to-output139                                                             |

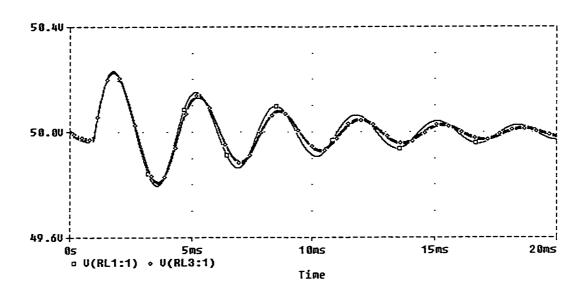

| Fig. 5-2  | 3. Load voltage transient waveforms predicted by simulating the actual circuit   |

|           | (thick line) and the model under $50\Omega$ to $100\Omega$ load change           |

| Fig. 5-29 | 9. Large signal models for the PFC converters given in Figs. 1-7(a) and 1-       |

|           | 7(b): (a) Boost/flyback combination circuit, (b) Boost/forward combination       |

|           | circuit141                                                                       |

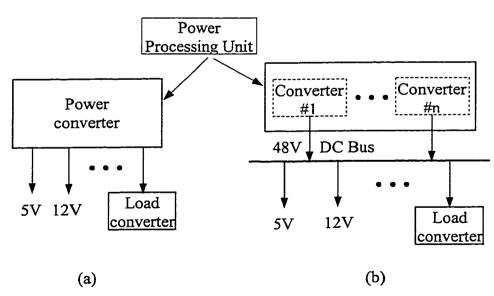

| Fig. 6-1. | Block diagram of two power supply systems: (a) centralized, (b) distributed 144  |

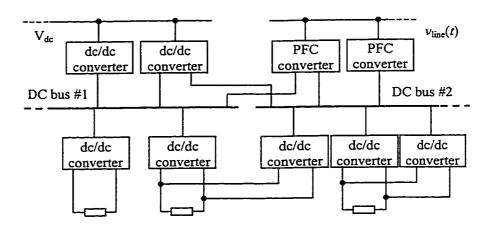

| Fig. 6-2. | Block diagram of a typical distributed power system146                           |

| Fig. 6-3. | Block diagram of a CLC scheme147                                                 |

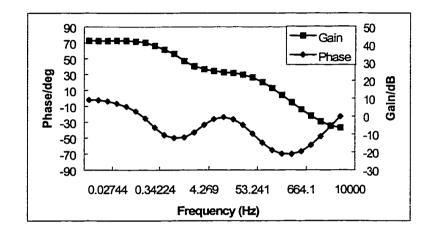

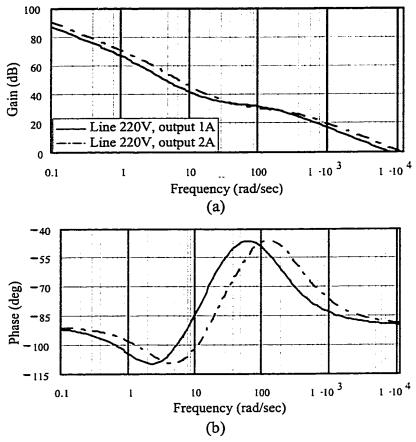

| Fig. 6-4. | Control-to-output voltage frequency response of the AC/DC converter: (a)         |

|           | magnitude, (b) phase148                                                          |

| Fig 6-5   | Voltage loop gain for each AC/DC converter: (a) magnitude, (b) phase150          |

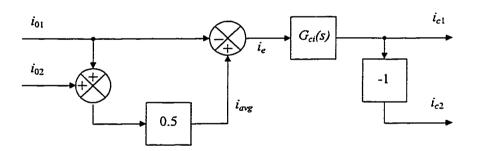

| Fig. 6-6.  | Central limit current control scheme                                                    |

|------------|-----------------------------------------------------------------------------------------|

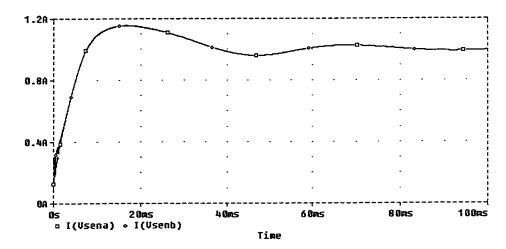

| Fig. 6-7.  | Output current waveforms with $G_{ci}(s) = 0.2$                                         |

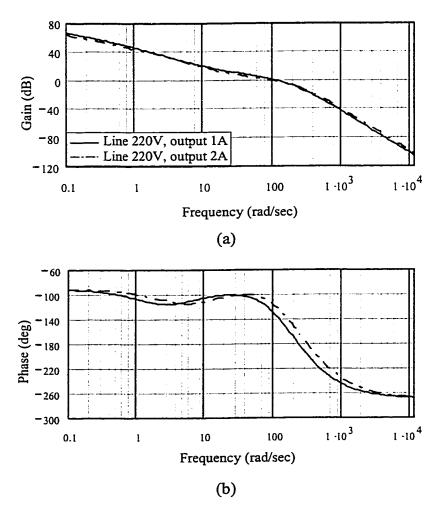

| Fig. 6-8.  | Current loop gain for each AC/DC converter with $G_{ci}(s) = \frac{10^4}{s}$ : (a)      |

|            | magnitude, (b) phase153                                                                 |

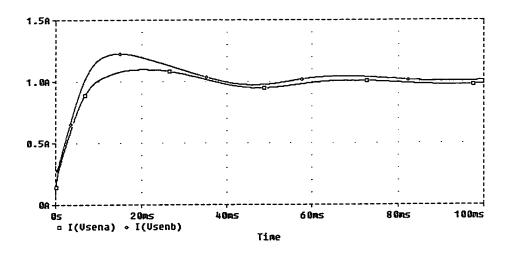

| Fig. 6-9.  | Output current waveforms with $G_{ci}(s) = \frac{10^4}{s}$                              |

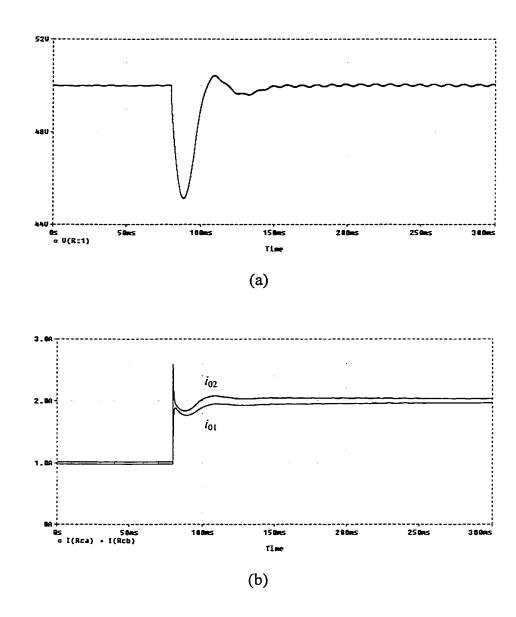

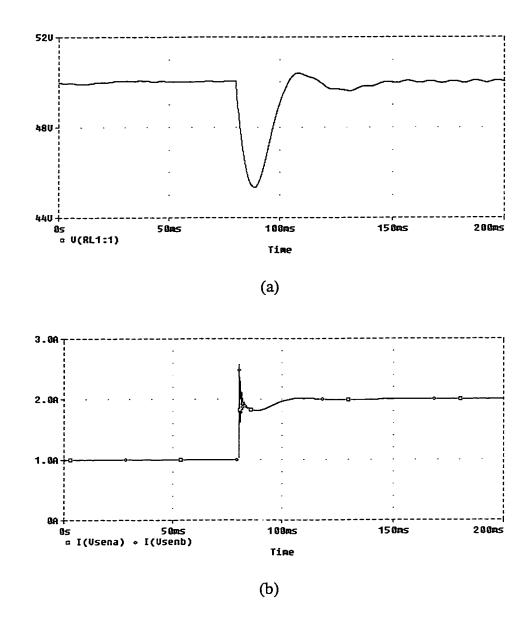

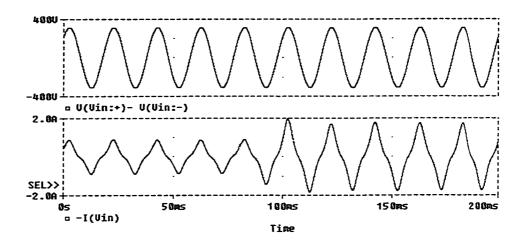

| Fig. 6-10. | Simulation waveforms using the actual switching circuit and a constant                  |

|            | current controller: (a) load voltage $(v_0)$ , (b) output current of each converter 155 |

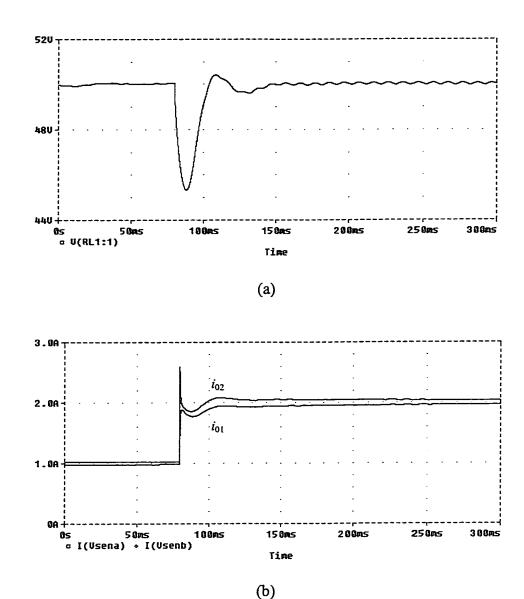

| Fig. 6-11. | Simulation waveforms using the large-signal model and a constant current                |

|            | controller: (a) load voltage ( $\nu_0$ ), (b) output current of each converter          |

| Fig. 6-12. | Simulation waveforms using the large-signal model and a constant current                |

|            | controller: (a) load voltage ( $\nu_0$ ), (b) output current of each converter          |

| Fig. 6-13. | Input voltage and current waveforms with sudden load change $(2A \rightarrow 4A)$       |

|            | at <i>t</i> =80ms158                                                                    |

## **CHAPTER 1**

### INTRODUCTION

Modeling of switched-mode DC/DC converters is a very important research area in power electronics. The need for dynamic models of the power stage lies in fact that the DC/DC converter goes through different circuit topologies within each switching period, depending on its operation modes. The overall response of all state variables with respect to external disturbances needs to be predicted such that this response could be controlled and minimized through properly designed control circuits. The purpose of the feedback loop is to remedy any undesirable dynamic nature and to optimize the overall performance of the power regulator. Once the model or the transfer function of the power stage is found, sophisticated control theory can be applied to design the controllers characterized in terms of the concepts such as loop gain, bandwidth and stability margins.

The quality of power supply systems is evaluated from its voltage magnitude, frequency and waveform. In early stages, power systems were subjected only to some inconsistent transient disturbances such as breaker operation, load change and equipment fault, etc., as well as the effects of transformer nonlinearity. Voltage and current distortions were generally very small. During normal operation, power engineers were mainly concerned about providing a voltage with stable magnitude and frequency. Power

quality were maintained at a satisfactory level through improvement of the transmission and distribution network, improvement of the equipment design and manufacturing as well as reactive power management and balancing on the busbars.

#### 1.1 Origin of Harmonics

The origin of harmonics can be traced back to the beginning of this century when mercury arc rectifiers emerged and found wide applications in electrochemical industry and high voltage direct current (HVDC) transmission in the 1930s. Since then, power system safe operation has encountered a new challenge: harmonics. Nonlinear loads, such as rectifiers, absorb non-sinusoidal current which is rich in high frequency components-harmonic currents, when connected to the ac line. These harmonic currents generate harmonic voltages when flowing through system impedance. They are superimposed on the fundamental voltage and subsequently distorted the bus voltage waveform.

The first noticeable effect of the consistent harmonic disturbances was on the communications systems because of their electromagnetic interference (EMI) with adjacent communication lines [1, 5]. Since the mid-60s, harmonic problem has gradually attracted attention in the power engineering and is now becoming a pressing issue mainly because of the following reasons:

Increased use of high power semiconductor switching components in energy conversion and motor drives such as in rolling mill machines, electric arc furnaces, HVDC, traction systems, etc. Loads with nonlinear characteristics such as rectifiers have gradually constituted the major portion of electrical loads in most of the power systems.

2) High power rectifier loads usually dissipate large amount of reactive power during their normal operation, resulting in voltage fluctuation and excessive energy loss on the transmission lines. To improve system power factor and voltage regulation, shunt capacitors are used to provide the reactive power compensation. However, in a harmonic environment, these capacitors will resonant with system impedance at certain harmonic frequencies and cause greater voltage distortion, causing more serious harmonic pollution in power systems.

Most of the electrical equipment has been designed and manufactured to operate efficiently assuming ideal sinusoidal environment. In a polluted system, however, its operation may be deviated from the designed normal conditions. In additional to telephone interference, power system harmonics are found to be the major threat to the safe operation of the power systems. Some of their influences are [1-7]:

- 1) Affect the smooth operation of motors because of the presence of additional torque generated by the negative sequence harmonic currents.

- 2) Results in excessive heating in transformers and motors by increasing magnetic core losses.

- Generate abnormal audible noises and mechanical vibration of the transformers and motors.

- 4) Cause malfunction of protection relays.

- 5) Accelerate aging of insulating media.

- 6) Increase instrument error.

- 7) Overloading shunt capacitor banks.

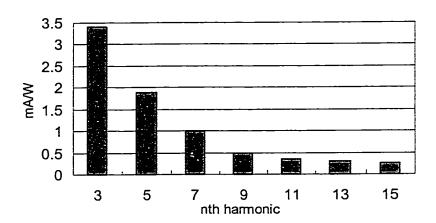

In view of the proliferation of the power electronic equipment connected to the utility grid, some national and international harmonic standards have been developed to limit harmonic current injection or to limit the harmonic voltages at the point of common coupling (PCC) [7-10] to protect power system safe operation. The two that draw most attention are the recommended IEEE 519-1992 [8] and the IEC 1000 family [9]. Table 1-1 shows the voltage distortion limits set by the standard IEEE 519. The underlined consideration of the standard is to prevent harmonic currents generated by nonlinear loads from interfere with other customers. In other words, the electric utility and the user of electric equipment are both responsible for improving the power quality. IEC 1000-3-2 classifies power electronics equipment with a maximum input current less than or equal to 16A per phase into four categories. Among those the harmonic limits of the class D received the most attention since most of the switch-mode power conversion systems fall into this category. It also has a profound impact to the power electronics industry as it set the harmonic emission level for individual power equipment. Table 1-2 shows the harmonic current limits of this class and Fig. 1-1 gives a graphic presentation of the second column on maximum harmonic current per watt that can be generated by electric equipment. The IEC 1000 standard, once approved by the European Standardization Committee for Electrical Products, will be enforced by law in Europe in January 2001.

Table 1-1. IEEE 519 voltage distortion limits

| Bus voltage at PCC     | Individual voltage<br>distortion (%) | Total voltage distortion THD (%) |

|------------------------|--------------------------------------|----------------------------------|

| 69kV and below         | 3.0                                  | 5.0                              |

| 69.001kV through 161kV | 1.5                                  | 2.5                              |

| 161.001kV and above    | 1.0                                  | 1.5                              |

Table 1-2. IEC 1000-3-2 harmonic current limits for class D electric equipment

| Harmonic order, n      | Maximum permissible harmonic current per watt, mA/W | Maximum permissible harmonic current, A |

|------------------------|-----------------------------------------------------|-----------------------------------------|

| 3                      | 3.4                                                 | 2.30                                    |

| 5                      | 1.9                                                 | 1.14                                    |

| 7                      | 1.0                                                 | 0.77                                    |

| 9                      | 0.5                                                 | 0.4                                     |

| 11                     | C.35                                                | 0.33                                    |

| 13≤n≤39, odd harmonics | 3.85/n                                              | Refer to class A                        |

Fig. 1-1. Maximum permissible harmonic current per watt for class D electric equipment.

Solution for harmonic reduction and power quality improvement can be achieved by installing harmonic compensation equipment beside the rectifier loads or by modifying conversion topologies as well as developing new conversion techniques.

The purpose of installing harmonic compensation equipment is to provide an alternate path for harmonic currents generated by the nonlinear loads to prevent them from flowing into the power systems. The following approaches have been proven to be very successful in the past several decades [11-17].

- 1) Installing harmonic filter banks: to avoid resonance between reactive power compensation capacitors and system impedance at some harmonic frequencies, a carefully designed reactor is inserted into the capacitor branches such that the inductor-capacitor tuned to particular frequencies to provide a low impedance path to bypass one or more harmonic currents. The method is very effective for balanced systems where load variation is moderate.

- 2) In systems where the load is subjected to large changes such as with the rolling mill machine, a Static Var Compensator (SVC) can be installed. The SVC contains a filter bank which is responsible for filtering out the harmonic currents and a reactive power regulator to compensate for variations in reactive power consumed by the load.

- 3) Time-domain reactive power compensation: also called active filtering. This method is based on the theory that the distorted current absorbed by a nonlinear load can be decomposed into two perpendicular components: active component and reactive component. The active component has the same shape and is in phase with the supplying voltage. Its magnitude is determined by the active power of the load.

Active filters eliminate harmonic currents by injecting a controlled current into the system with its magnitude equals that of the reactive component of the load current but has a 180° phase difference.

Active filtering is becoming a viable alternative solution to SVC since it achieves both harmonic elimination and reactive power compensation at the same time. It is also insensitive to changes in system and load operation conditions.

In addition to relying on external equipment and devices to prevent harmonic currents from polluting power systems, harmonic problem can also be alleviated effectively by minimizing harmonic current being generated. The traditional three-phase six pulse phase-controlled rectifier contains 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup>, 17<sup>th</sup>, ..., harmonic currents with magnitude of 1/5, 1/7, 1/11, 1/13, 1/17, ..., with respected to the fundamental current component for each harmonic current. By combining two six pulse rectifiers with 30° phase shift in between, a three phase twelve pulse phase-controlled rectifier is obtained, with which the 5<sup>th</sup>, 7<sup>th</sup>, 17<sup>th</sup>, ..., harmonic currents can be significantly reduced, leaving only the smaller 11<sup>th</sup>, 13<sup>th</sup>, ..., harmonic currents present in the line current [2, 18].

It is noted that harmonic currents generated by many nonlinear loads including the six and twelve pulse rectifiers are in the frequency range of 2kHz. An alternative approach to perform power conversion from ac to dc is to utilize power electronic high frequency switching converters for input current shaping. This technique is called *active* power factor correction (PFC). The essence of this technique is to move the low

frequency harmonic current components to much higher frequency range (>50kHz) where they are much easier to handle. Advantages of PFC technique include:

- 1) The bulk and heavy line frequency transformer is ruled out.

- 2) The line current of the PFC converter is in phase with the line voltage, no reactive power compensation needed.

AC/DC power conversion circuits from low to medium power level for computers, television sets, communication systems, etc., contribute a large portion of power electronics applications because of the huge quantities involved. Switched-mode PFC power supplies are rapidly replacing earlier linear power supplies across the full spectrum of these applications. This dissertation is devoted to the analysis and modeling of the PFC converters.

## 1.2 Single-Switch Single-Stage PFC Converters

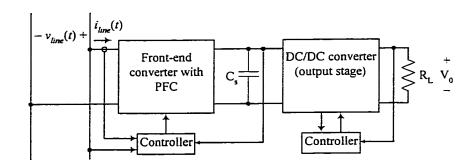

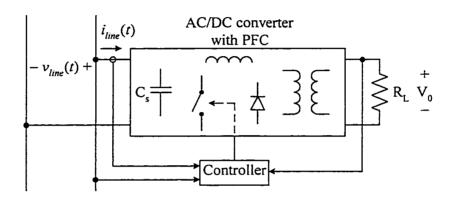

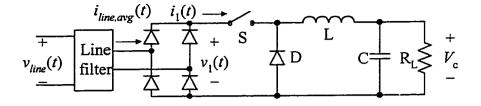

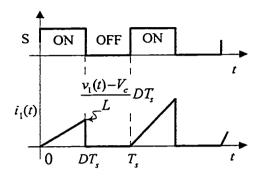

Figure 1-2 shows a block diagram for the PFC converter configuration. The frontend converter performs ac to dc conversion as well as line current shaping to obtain unity power factor. It serves as the interface between the line and the output stage converter which provides the required dc power to the load.

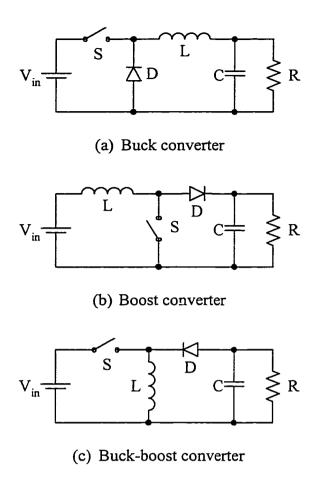

Most of the switched-mode DC/DC converters can be directly utilized as the PFC converter by incorporating a full bridge diode rectifier at their input. Figure 1-3 shows three basic DC/DC converter topologies. However, it should be noted that they present different input characteristics. For example, except in some special cases, the Buck converter and its derivations are not quite suited for power factor correction as they draw

zero current from the line when the instantaneous input voltage is lower than the output voltage, exhibiting a dead zone in their input v-i characteristics [19-23].

Fig. 1-2. The PFC converter block diagram.

It should also be noted that energy balance from input to output for DC/DC converters is maintained in each switching cycle under steady-state operation conditions. However, this power balance for AC/DC converters is only valid over each half line cycle. This basic difference between AC/DC and DC/DC operations implies that a large energy storage tank must be present in the PFC circuit to accommodate large changes of the instantaneous input power and to sustain adequate power to the output converter in order to keep the load voltage constant. Generally speaking, this energy storage tank could be composed of inductors or capacitors or both. In many practical circuits, however, energy stored in electric rather than magnetic form is preferred and usually one or more capacitors are adopted. The need for storage capacitors is shown in Fig. 1-2 as C<sub>s</sub>. For some simple circuits, this C<sub>s</sub> could be the output capacitor of the converters in Fig. 1-3.

Fig. 1-3. Three basic DC/DC converters.

Since power transferred from line to the storage capacitors varies sinusoidally and the load draws constant power from the capacitors, it is expected that voltage across the capacitors contains large secondary harmonic ripple. Very often, this voltage is very high and is also not in the right voltage level required by the load. To obtain a smooth and tightly regulated load voltage, an output stage DC/DC regulator is required, as shown in Fig. 1-2. Noted that the front-end PFC converter and the load converter are independent and are separately controlled, this type of AC/DC conversion configuration is called two-stage scheme.

Input current shaping method can be roughly classified into CCM and DCM approaches depending on the inductor current of the PFC converter. If, within each switching period, the inductor current always greater than zero, the PFC converter is said to operate in continuous conduction mode, or CCM. Otherwise, it operates in discontinuous conduction mode.

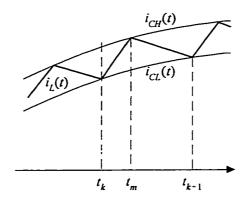

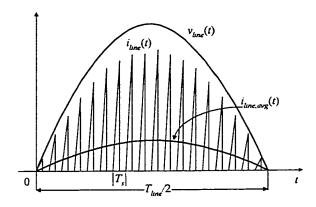

Figure 1-4 shows the line current waveform when a CCM boost circuit is adopted as the front-end PFC converter. There are a number of control methods to enable the line current to track the line voltage. In Fig. 1-4, inductor current  $i_L(t)$  is controlled to be within two sinusoidal current command limits, high limit  $i_{H,limit}(t)$  and low limit  $i_{L,limit}(t)$ . If  $i_L(t)$  decreases below  $i_{L,limit}(t)$ , PFC converter controller turns on the switch to allow line voltage to charge the inductor. When the current reaches  $i_{H,limit}(t)$ , the controller turns off the switch. This type of control strategy is called hysteresis control with  $i_{H,limit}(t)$ - $i_{L,limit}(t) = k_1$  or  $i_{H,limit}(t) = k_2 i_{L,limit}(t)$ , where  $k_1$  and  $k_2$  are constants  $(k_2 > 1)$ . Obviously the inductor current charging and discharging time are changing with the line voltage, resulting in variable switching frequency control.

Variable frequency current control can also be achieved without high limit  $i_{H,limit}(t)$  command (constant on-time control with  $t_m - t_k = k$ , k is a constant) or without low limit  $i_{L,limit}(t)$  command (constant off-time control with  $t_{k+1} - t_m = k$ , k is a constant).

Variable frequency control makes input filter and closed-loop design difficult. A typical constant frequency control method is the peak current control. In Fig. 1-4, if  $t_{k+1}$  -  $t_k = T_s$ ,  $T_s$  is the switching period and is constant, and also only the high current limit  $i_{H,limit}(t)$  is used. Constant frequency peak current control suffers from a subharmonic

instability when the resulting charging time is greater than 50% of the switching period  $T_s$ . To avoid this problem, a stabilizing ramp with proper negative slope is required.

Fig. 1-4. Inductor or line current waveform in CCM for boost PFC converter.

Analysis and design of PFC converters employing these CCM methods to obtain unity power factor can be found in [24-36]. In [37-45] application of average current control and other CCM input current shaping techniques were also discussed.

Differences among these methods depend largely on how line current information is obtained. In addition to line current sensing, most of these methods also ask for sensing the line voltage to provide reference to the current command as shown in Fig. 1-2. It inevitably results in a complex control design.

The same PFC circuit can also achieve high power factor without resorting to the above complicated control loop design. This can be done by changing the operation mode of the PFC converter to DCM. In DCM operation, input energy transferred to the inductor when the switch is on is completely moved to the storage capacitors within each switching period. The peak inductor current is proportional to the line voltage when

charging time (or switch duty cycle) is fixed. The input current is now a train of high frequency triangular pulses whose average value over a switching cycle follows automatically and closely the line voltage as shown in Fig. 1-5 for the buck-boost example. Because of this "automatic" input current shaping property and simple feedback controller requirement, PFC converters employing DCM operation have been explored extensively and successfully and various topologies are available [22, 46-53].

Fig. 1-5. Line current waveform of the DCM Buck-boost PFC circuit in a half line cycle.

It is seen from Fig. 1-2 that the two-stage scheme has separate controllers for the front-end PFC stage and the output DC/DC stage. The active switch in each power stage is controlled independently. In recent years research efforts have been made to combine these two stages and to allow a single active switch to be shared by both stages to reduce manufacturing cost. The underlined strategy of this consideration is to use one controller and one switch to perform both power factor correction and output voltage regulation. It is found that by proper arrangement of the storage capacitors the two active switches can

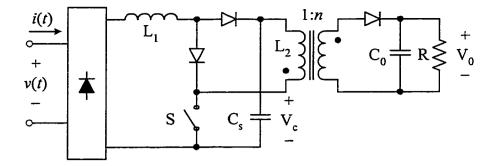

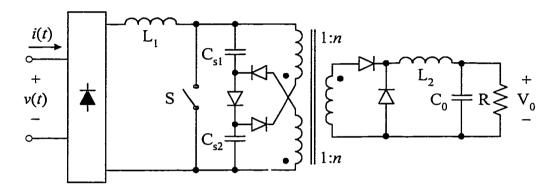

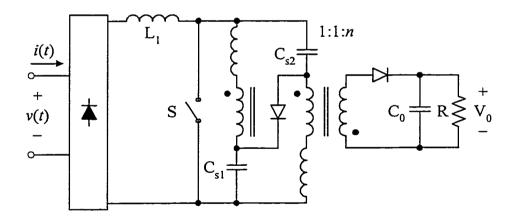

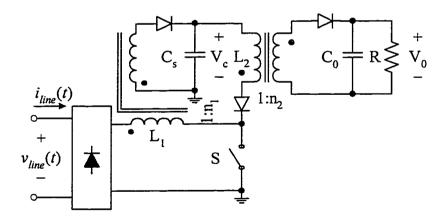

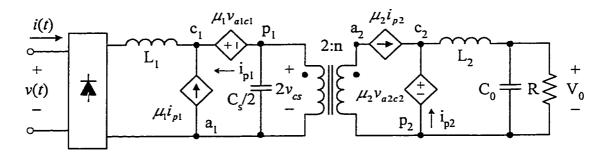

operate in unison and therefore their functions can be realized by one switch. Figure 1-6 shows the block diagram of this configuration which is usually referred to as the single-switch single-stage (S<sup>4</sup>) scheme. Numerous S<sup>4</sup>-PFC topologies have been reported and can be found in [20-22, 24-27, 29-32, 34-53]. Some typical S<sup>4</sup>-topologies are shown in Figure 1-7 [22, 49].

Fig. 1-6. Block diagram of the single-switch single-stage AC/DC converter with PFC.

It should be noted that since the active switch in S<sup>4</sup>-PFC converters carries the total current previously handled by two separate switches in the two-stage scheme, requirement on the power handling capability of the switch is high. A common phenomenon associated with S<sup>4</sup>-PFC converters is that the active switch suffers from a high voltage stress under high line and a high current stress under low line. High voltage stress is a result of high storage capacitor voltage and is also dependent on circuit operation modes. Since the PFC converter draws constant power from the line in each line cycle, switch current increases as line voltage decreases. The situation becomes even

worse when PFC converters operate in DCM. Refer to Fig. 1-5, it is noticed that since inductor current is pulsating, the peak current flowing through the switch is at least twice the average inductor or line current. For this reason, S<sup>4</sup>-PFC converters with DCM operation are only suitable for applications with power levels below a few hundred watts. At power levels greater than 1kW, CCM operation relying on more complicated control scheme becomes the dominant solution [24, 53].

#### 1.3 Dissertation Outline

Power factor correction technique is an important research topic in power electronics. Chapter 2 will give an overview of the modeling techniques based on the average concept for switched-mode DC/DC converters. The harmonic and power factor properties of PFC converters will be studied in Chapter 3. Small signal behaviors of an S<sup>4</sup>-PFC converter are first derived in Chapter 4 using the well-known state-space averaging method. The result is used as a reference to the PWM switch model to be derived in Chapter 5. An implementation error in the professional version of Pspice software for the conventional PWM model is first identified here and corrected as reported in Chapter 5. Improvement of this model under non-ideal conditions will also be described. The emphasis of this chapter is to introduce a new modeling approach based on the functionality of the inductors in deriving large-signal models for S<sup>4</sup>-PFC converters. Application of the large-signal model for a specific PFC converter will be shown in Chapter 6. Summary and conclusions will be given in Chapter 7.

(a) Boost/flyback combination circuit

(b) Boost/forward combination circuit

(c) Boost/forward combination circuit

Fig. 1-7. Three typical S<sup>4</sup>-PFC AC/DC converter topologies.

#### **CHAPTER 2**

## AVERAGE MODELING TECHNIQUE OF DC/DC CONVERTERS

#### 2.1 Introduction

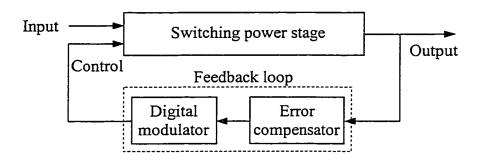

Theoretically, switched-mode DC/DC regulators can be considered as a closed loop control system that consists of two functional blocks as shown in Fig. 2-1: power stage and feedback control circuit. The power stage, such as the three basic converters shown in Fig. 1-3, performs the energy transfer from the input source to the load. It can be operated either in DCM or CCM. The feedback control circuit can normally be characterized by an analog error compensator and a digital modulator. The error compensator is composed of an amplifier and a compensation network. It generates a voltage command signal according to the output voltage and/or inductor current that are to follow a preset reference value. The digital modulator is composed of a ramp signal generator, a comparator as well as a timing network to control the turn-on and -off of the active switch to achieve the controlled energy transfer in the power stage. For constant frequency pulse-width-modulation (PWM) control, this digital modulator is usually modeled as a constant gain.

It has been mentioned that the purpose of developing proper models for switchedmode converters is to study their dynamic behaviors with respect to external disturbances and to allow sophisticated control theory to be applied to optimize converter responses. The difficulty in modeling switching converters arises from the inherently non-linear characteristics of the power converter. To most power supply design engineers, calculating and determining steady-state operation condition is not a problem and a unique operation point can always be found. However, predicting how circuit variables react with line/load changes and other disturbances is not easy. The answer is usually not unique either. Different techniques often predict different results and there are usually tradeoffs among accuracy, model complexity and the required computation time.

Fig. 2-1. General block diagram of a switched-mode DC/DC regulator.

In the past two decades, various modeling techniques have been reported. Most of them fall into two categories: discrete time-domain approach [54, 55] and averaging approach [56-58]. The operation of PWM converters is characterized by periodically changing topologies of a number of linear and time-invariant circuits. The discrete time-domain approach determines converter response by utilizing state-space equations and calculating transition matrix for each topology. It is an accurate method and is applicable

for any switching network. However, physical insight of the converter operation is unavailable and derivation of the expressions is complex and cumbersome.

On the other hand, averaging approach assumes that the time constant of the converter is much greater than the switching period and the converter's equivalent natural frequency is much smaller than the switching frequency. Fortunately, this condition is normally met in PWM converters. Although its accuracy degrades as the frequency of disturbing signals increases, derivation of the averaging model is much simpler than that of the time-domain model. In [59-61], it was shown that the increased error of the averaging approach at high frequency range is largely because of improper sampling of the output voltage with non-ideal output capacitors. By combining discrete time-domain and averaging techniques, it is possible to develop a model that is simple and accurate.

Of all the earlier approaches, the state-space averaging method [57, 58] developed by S. Cuk and R. Middlebrook in the 1970's was the most well known approach. It provided a generalized approach for a large class of PWM converters and has produced profound impact on the modeling and analysis of the DC/DC converters in the power electronics community. Since then, the concept of averaging has been explored extensively and lots of papers have been reported dealing with various improvements and theoretical foundations in average modeling [62-66, 71-77]. For example, more general models and extensions of the averaging technique that are not bounded to the small ripple condition were discussed in [71, 75, 76]. Among them, the three-terminal PWM switch model developed by V. Vorperian [62, 63] was an important contribution.

The state-space averaging and the PWM switch modeling are the most popular approaches currently being widely used by researchers and engineers in their study of stability and transient response of switching regulators. Although the PWM switch model greatly improved the modeling accuracy at high frequency range for DCM operating converters when compared with the state-space averaging, both approaches were based on the averaging concept. By averaging, detailed information about voltage and current waveforms, such as component voltage/current stresses, capacitor ESR effects, etc., are lost. In addition, both approaches give different models for converters operating in CCM and DCM. Basically it is unable to determine the operation modes simply by examining the average inductor current predicted from the model. To know whether the converter is in CCM or DCM or when the converter is going to change operation modes, power converter designers should go back to the actual switching circuit to check with the inductor current waveform. References [58] and [67] provide mathematical analysis governing converter operation modes under steady-state conditions based on circuit and operation parameters.

# 2.2 State-Space Average Modeling

The major idea of the state-space averaging method is to derive the dynamic behavior of the converter by averaging a set of linear state equations over a switching period. These state equations correspond to each topological structure the converter goes through in a switching period.

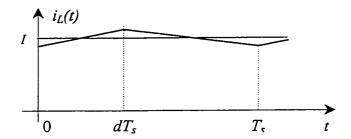

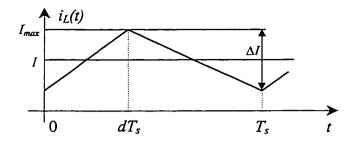

### 2.2.1 Continuous Conduction Mode

A classic PWM converter has two operation modes: continuous conduction mode (CCM) and discontinuous conduction mode (DCM). In CCM, the instantaneous inductor current does not fall to zero at any time during the switching cycle, as shown in Fig. 2-2, where d is defined as the control duty cycle; whereas in DCM, the inductor current always start at zero at the beginning of each switching cycle and return to zero before the cycle ends. In CCM, the converter undergoes two topological changes. The state-space equations for each of these two structures can be described as (x, y are state vector and output vector, respectively):

Fig. 2-2. Inductor current waveform in CCM operation.

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}_1 \mathbf{x} + \mathbf{B}_1 \mathbf{v}_s, \quad \mathbf{y} = \mathbf{C}_1 \mathbf{x} \qquad 0 \le t \le dT_s$$

(2.1)

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}_2 \mathbf{x} + \mathbf{B}_2 \mathbf{v}_s, \quad \mathbf{y} = \mathbf{C}_2 \mathbf{x} \qquad dT_s \le t \le T_s$$

(2.2)

The averaging technique suggests that these two state equations can be combined into one state equation by a set of state matrices A, B and C as follows,

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{v}_{s}, \quad \mathbf{y} = \mathbf{C}\mathbf{x} \tag{2.3}$$

where  $v_s$  is the input voltage and,

$$\mathbf{A} = d\mathbf{A}_1 + (1 - d)\mathbf{A}_2 \tag{2.4}$$

$$\mathbf{B} = d\mathbf{B}_1 + (1 - d)\mathbf{B}_2 \tag{2.5}$$

$$\mathbf{C} = d\mathbf{C}_1 + (1-d)\mathbf{C}_2 \tag{2.6}$$

To obtain the system responses of the model described by Equations 2.3 to 2.6, we assume that the input voltage  $v_s$  and the duty cycle d are perturbed around their steady-state values such that  $v_s = V_s + \hat{v}_s$ ,  $d = D + \hat{d}$ , which also cause the state vector and system output to deviate from their corresponding steady-state positions, namely  $\mathbf{x} = \mathbf{X} + \hat{\mathbf{x}}$ , and  $\mathbf{y} = \mathbf{Y} + \hat{\mathbf{y}}$ . Equation 2.3 can be written as:

$$\frac{d\hat{\mathbf{x}}}{dt} = \mathbf{A}\mathbf{X} + \mathbf{B}V_s + \mathbf{A}\hat{\mathbf{x}} + \mathbf{B}\hat{v}_s + ((\mathbf{A}_1 - \mathbf{A}_2)\mathbf{X} + (\mathbf{B}_1 - \mathbf{B}_2)V_s)\hat{d}$$

(2.7)

$$Y + \hat{y} = CX + C\hat{x} + (C_1 - C_2)X\hat{d}$$

(2.8)

Note that in obtaining the above expressions, it is assumed that the perturbations are significantly smaller than their respective steady-state values so that all the non-linear terms (multiples of perturbations) are neglected. Separating the steady state and the dynamic terms of the above linearized system results in the final state-space averaging model as given below:

# Steady-state model:

$$\mathbf{X} = -\mathbf{A}^{-1}\mathbf{B}V_{\mathbf{r}} \tag{2.9}$$

$$\mathbf{Y} = \mathbf{C}\mathbf{X} = -\mathbf{C}\mathbf{A}^{-1}\mathbf{B}V_{s} \tag{2.10}$$

# • Small-signal model:

$$\frac{d\hat{\mathbf{x}}}{dt} = \mathbf{A}\hat{\mathbf{x}} + \mathbf{B}\hat{\mathbf{v}}_s + ((\mathbf{A}_1 - \mathbf{A}_2)\mathbf{X} + (\mathbf{B}_1 - \mathbf{B}_2)V_s)\hat{d}$$

(2.11)

$$\hat{\mathbf{y}} = \mathbf{C}\hat{\mathbf{x}} + (\mathbf{C}_1 - \mathbf{C}_2)\mathbf{X}\hat{d} \tag{2.12}$$

In Equations 2.9 to 2.12, matrices A, B and C are calculated from Equations 2.4 to 2.6 by replacing d with its steady-state value D.

The significance of the small signal model as described by Equations 2.11 and 2.12 is that the frequency domain characteristic can be easily obtained using Laplace transformation. From the model, one can also derive an equivalent circuit model that provides a physical perception of the converter for design engineers.

Although the DC and the small signal model given by Equations 2.9 to 2.12 are derived from a converter with only two switching structures, this averaging approach also holds true for PWM converters with multi-topological structure changes, provided that the converter is working in CCM.

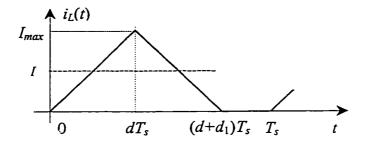

#### 2.2.2 Discontinuous Conduction Mode

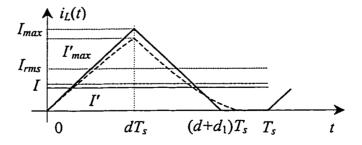

For converters working in DCM, the procedure of obtaining the DC and small signal model is basically the same as that shown above except that some modifications should be made. The major modification is the way the state variables are treated. In DCM operation, as can be seen in Fig. 2-3, the inductor current is fixed at zero at the beginning and end of each switching cycle even with small perturbations in the input and the control signal. It therefore no longer behaves as a valid state variable. This immediately reduces the order of the state-space representation and thus leads to an order-reduction dynamic model. The derivation of the model for this mode of operation is briefly summarized below.

When DCM operation is concerned, a classical PWM converter goes through three topological changes in stead of two as it does in CCM operation. Each topological stage corresponds to a different state equation. Namely,

Fig. 2-3. Inductor current waveform in DCM operation.

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}_1 \mathbf{x} + \mathbf{B}_1 \mathbf{v}_s \qquad 0 \le t \le dT_s \tag{2.13}$$

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}_2 \mathbf{x} + \mathbf{B}_2 \mathbf{v}_s \qquad dT_s \le t \le (d + d_1) T_s \qquad (2.14)$$

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}_3 \mathbf{x} + \mathbf{B}_3 \mathbf{v}_s \qquad (d+d_1) T_s \le t \le T_s \qquad (2.15)$$

Averaging the above state equations, we have,

$$\frac{d\mathbf{x}}{dt} = \mathbf{A}\mathbf{x} + \mathbf{B}\nu_{s} \tag{2.16}$$

where,

$$\mathbf{A} = d\mathbf{A}_1 + d_1\mathbf{A}_2 + (1 - d - d_1)\mathbf{A}_3 \tag{2.17}$$

$$\mathbf{B} = d\mathbf{B}_1 + d_1\mathbf{B}_2 + (1 - d - d_1)\mathbf{B}_3 \tag{2.18}$$

Recall that in continuous conduction mode, Equation 2.16 was sufficient to describe the converter characteristic. Here for discontinuous conduction mode, it could not describe the switching converter completely since it does not take into account that the inductor current falls to zero before the next switching cycle begins. It seems that as a state variable, the inductor current  $i_L(t)$  should respond to any perturbation in the input source or in the control duty cycle. On the other hand, the average current (defined as the integration of the inductor current over the time period when  $i_L(t)$  is not zero) will fluctuate to accommodate any possible perturbations. Therefore, instead of using the inductor current as a state variable, we introduce the average of the inductor current as a new variable. It is obvious that,

$$i = \frac{I_{\text{max}}}{2} = i(v_s, v_0, L, d, T_s)$$

(2.19)

where  $v_0$  is the output voltage and L is the inductance.

From Equation 2.16, it is also obvious that the system behavior depends heavily on the controlled duty cycle d and the corresponding value  $d_1$ , which is unknown and needs to be determined. With the addition of Equation 2.19, all the circuit parameters and the DCM operating condition have been included. Thus the complete state-space averaging model for DCM operation is given by:

$$\frac{d\mathbf{x}}{dt} = (d\mathbf{A}_1 + d\mathbf{A}_2 + (1 - d - d_1)\mathbf{A}_3)\mathbf{x} + (d\mathbf{B}_1 + d_1\mathbf{B}_2 + (1 - d - d_1)\mathbf{B}_3)\mathbf{v}_s$$

(2.20)

with two additional constraints:

$$\frac{di_L}{dt} = 0 ag{2.21}$$

$$i = \frac{I_{\text{max}}}{2} = i(v_s, v_0, L, d, T_s)$$

(2.22)

Follow the same procedure as that in CCM operation, the steady state and dynamic models for converters with DCM operation can also be obtained as:

### • Steady-state model:

$$\mathbf{X} = -\mathbf{A}^{-1}\mathbf{B}V_{s} \tag{1.23}$$

and

$$I = i(V_s, V_0, L, D, T_s)$$

(1.24)

where **A** and **B** are obtained from Equations 2.17 and 2.18 by using steady state values D and  $D_1$ .

Dynamic Model:

$$\frac{d\hat{\mathbf{x}}}{dt} = \mathbf{A}\hat{\mathbf{x}} + \mathbf{B}\hat{\mathbf{v}}_{s}$$

$$+ ((\mathbf{A}_{1} - \mathbf{A}_{3})\mathbf{X} + (\mathbf{B}_{1} - \mathbf{B}_{3})V_{s})\hat{d} + ((\mathbf{A}_{2} - \mathbf{A}_{3})\mathbf{X} + (\mathbf{B}_{2} - \mathbf{B}_{3})V_{s})\hat{d}_{1}$$

(2.25)

and

$$\hat{i} = \frac{\partial i}{\partial v_s} \hat{v}_s + \frac{\partial i}{\partial v_0} \hat{v}_0 + \frac{\partial i}{\partial d} \hat{d}$$

(2.26)

# 2.3 Three-Terminal PWM Switch Modeling

Unlike the systematic approach in the state-space averaging method where the derivation of the complete canonical circuit model and various transfer characteristics of a PWM converter relies on a considerable amount of matrix manipulations, the derivation of the PWM switch model solely follows a circuit oriented approach. The basic idea of this approach is to pick out the switches in the converter and to replace them with a proper equivalent circuit model. The whole process is analogous to the analysis of an amplifier circuit in electronics, where the nonlinear transistor is replaced by an h-parameter equivalent circuit. Once this is done, the amplifier can be analyzed using the well-established linear circuit analysis technique.

#### 2.3.1 Continuous Conduction Mode

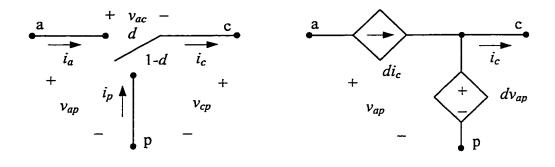

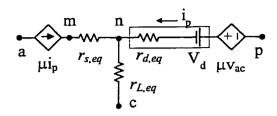

Investigation shows that the generation of classical PWM converters can be considered as a result of cyclic rotations of a three-terminal single-pole double-throw switch between the input and the output port [68]. This switch, as shown in Fig. 2-4(a), is normally implemented with an active switch and a passive switch, as is with the basic converters shown in Fig. 1-3. The active switch is usually implemented with a bipolar or a field-effect transistor whose turn on and off is directly controlled by the feedback circuit. The passive switch is usually a diode and its turn on and off is indirectly controlled by the state of the active switch and the converter topology. Since the three-terminal switch (called PWM switch with terminals a, p and c, which stands for active, passive and common, respectively) is the only nonlinear element in the converter, it is therefore responsible for the nonlinearity of PWM converters.

The averaging model of the PWM switch is shown in Fig. 2-4(b) for converters operating in CCM condition. It is obvious from Fig. 2-4(a) that current  $i_c(t)$  is an independent variable and is controlled to flow either through terminal a or p. Similarly, voltage  $v_{ap}(t)$  is independent since terminal a or p is connected to terminal c asynchronously. Therefore, it follows that,

$$i_a(t) = \begin{cases} i_c(t) & 0 \le t \le dT_s \\ 0 & dT_s \le t \le T \end{cases}$$

(2.27)

(a) a PWM switch

(b) equivalent circuit model

Fig. 2-4. A PWM switch and its equivalent circuit model.

$$i_{p}(t) = \begin{cases} 0 & 0 \le t \le dT_{s} \\ i_{c}(t) & dT_{s} \le t \le T_{s} \end{cases}$$

$$(2.28)$$

and,

$$v_{cp}(t) = \begin{cases} v_{ap}(t) & 0 \le t \le dT_s \\ 0 & dT_s \le t \le T_s \end{cases}$$

$$(2.29)$$

$$v_{ac}(t) = \begin{cases} 0 & 0 \le t \le dT \\ v_{ap}(t) & dT_s \le t \le T_s \end{cases}$$

(2.30)

Average concept implies that the relationship among the average values of these variables must satisfy,

$$i_a = di_c \tag{2.31}$$

$$i_p = (1-d)i_c \tag{2.32}$$

and

$$v_{cp} = dv_{ap} \tag{2.33}$$

$$v_{ac} = (1-d)v_{ap} \tag{2.34}$$

Using Equations 2.31 and 2.33 directly leads to the average circuit model of the PWM switch shown in Fig. 2-4(b). An equivalent form can also be obtained from Equations 2.32 and 2.34. It should be pointed out that the equivalent series resistance (ESR) of the output capacitor presents some impact on the terminal voltages. This impact can also be included into the model but a slight modification is required [62].

Figure 2-4(b) is actually the steady state circuit model of the PWM switch when all the variables are replaced by their corresponding DC values. Introducing perturbations into the terminal variables leads to the small signal model of the PWM switch.

Substitute in Equations 2.31 and 2.33 with  $d=D+\hat{d}$ ,  $i_a=I_a+\hat{i}_a$ ,  $i_c=I_c+\hat{i}_c$ ,  $v_{ap}=V_{ap}+\hat{v}_{ap}$ ,  $v_{cp}=V_{cp}+\hat{v}_{cp}$ , the perturbed terms then become as follows:

$$\hat{i}_{a} = D\hat{i}_{c} + I_{c}\hat{d}$$

$$\hat{v}_{cp} = D\hat{v}_{ap} + V_{ap}\hat{d}$$

(2.35)

This equation leads to a small signal model shown in Fig. 2-5.

As can be seen, with the PWM switch model, only the non-linear component represented by the three-terminal switch in a converter is considered. All the other elements are left untouched. This is in sharp contrast with the state-space averaging method where the whole circuit must be analyzed.

Fig. 2-5. Small signal model of the PWM switch.

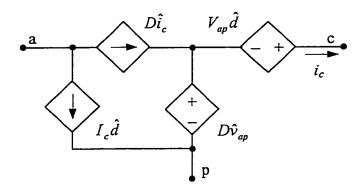

#### 2.3.2 Discontinuous Conduction Mode

For the three-terminal switch shown in Fig. 2-4(a), the model can also be developed similarly using the average concept when the converter is operating in DCM. Fig. 2-3 now represents the current in terminal c, i.e.,  $i_c(t)$ . Current  $i_a(t)$  is the portion of

$i_c(t)$  when  $0 \le t \le dT_s$  and current  $i_p(t)$  is the portion of  $i_c(t)$  when  $dT_s \le t \le (d+d_1)T_s$ . Therefore, the average values can be written as:

$$i_a = \frac{dI_{\text{max}}}{2} \tag{2.36}$$

$$i_{p} = \frac{d_{1}I_{\text{max}}}{2} \tag{2.37}$$

$$v_{ac} = \frac{LI_{\text{max}}}{dT_s} \tag{2.38}$$

$$v_{cp} = \frac{LI_{\text{max}}}{d_1 T_s} \tag{2.39}$$

These equations suggest that

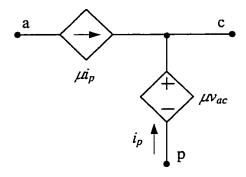

$$v_{cp} = \mu v_{ac} \tag{2.40}$$

$$i_a = \mu i_p \tag{2.41}$$

$$\mu = \frac{d^2 T_s}{2L} \frac{v_{cp}}{i_a} = \frac{d^2 T_s}{2L} \frac{v_{ac}}{i_p}$$

(2.42)

The average model for the PWM switch described by Equations 2.40 to 2.42 is shown in Fig. 2-6.

Again, the steady-state model of the PWM switch in DCM can be obtained from Equations 2.40 to 2.42 or from Fig. 2-6 where all the variables are replaced by their DC values.

Fig. 2-6. The PWM switch model in DCM.

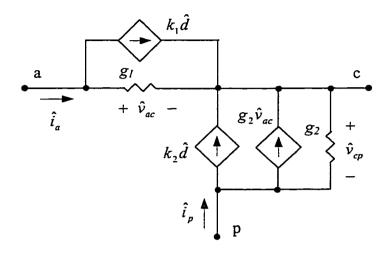

The small signal model is also obtainable through perturbation of Equations 2.40 to 2.42 and is given as:

$$\hat{i}_a = g_1 \hat{v}_{ac} + k_1 \hat{d} \tag{2.43}$$

$$\hat{i}_{p} = g_{2}\hat{v}_{ac} + k_{2}\hat{d} - g_{3}\hat{v}_{cp} \tag{2.44}$$

where  $g_1 = I_a/V_{ac}$ ,  $g_2 = 2I_p/V_{ac}$ ,  $g_3 = I_p/V_{cp}$ ,  $k_1 = 2I_a/D$  and  $k_2 = 2I_p/D$ . The circuit representation of these two equations is given in Fig. 2-7.

Fig. 2-7. Small signal model of the PWM switch in DCM.

As a final point, it should be mentioned that while use of CCM PWM switch model and the state-space averaging method yields the same results, for DCM operation, the conclusion is different. This is because the state-space average technique does not treat the discontinuous inductor current to be a state variable and hence results in a reduced order dynamic model. Whereas in PWM switch model, only the three-terminal switch is considered and linearized while all the other linear elements including the inductor with a discontinuous current are kept unchanged. The resulting linear circuit

model will certainly characterize the system with the same order as that when the converter is in CCM. The justification of this result can be found in [63].

### 2.4 The PWM Switch Model of the Flyback Converter and Weinberg Converter

### 2.4.1 The Flyback Converter

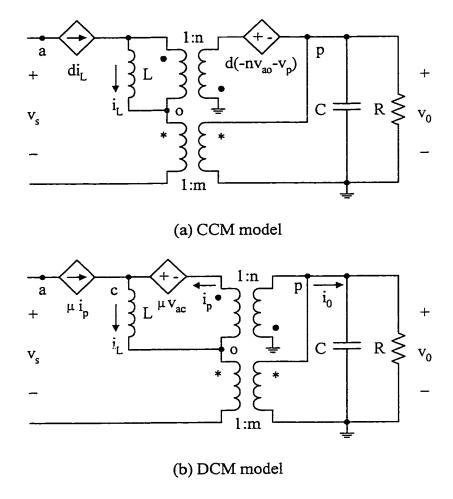

The flyback converter shown in Fig. 2-8 is chosen in this section as an example to show that the PWM switch modeling technique can also be applied to some converters that contain isolation transformers. Another reason is that a flyback structure can often be found in PFC converters either as the front-end PFC stage or the output stage. A PWM switch model developed here could be adopted directly in the modeling of PFC converters.

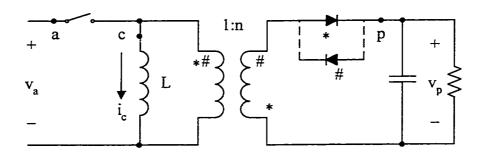

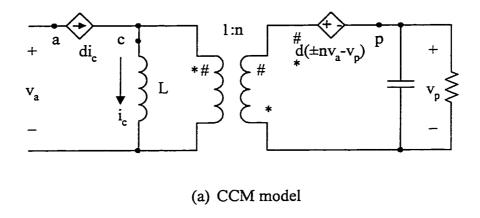

One of the obvious advantages of the PWM switch modeling approach is that the model automatically preserves the input-output property of the circuit such that there is no need for the users to concern about the output polarity. However, to keep this nice feature this approach may need some modifications when it comes with one or more isolation transformers in the converter circuit because of the polarity of the transformer. To add to the library of the well-documented models of the classical PWM converters, the models of the flyback converter is given in Fig. 2-9.

In Fig. 2-8, the "\*" and "#" signs show the two possible dot notations (polarities) of a transformer connection and the diode with the sign indicates which direction the diode should be with the corresponding transformer polarity. The justification for the

dynamic model in Fig. 2-9(a) can be clarified by comparing its state-space equations with the averaged ones of the original converter shown in Fig. 2-8. The control coefficient  $\mu$  for the DCM condition in Fig. 2-9(b) is given by,

Fig. 2-8. Topology of the flyback converter.

$$\mu = \frac{d^2}{2Lf_s} \frac{v_{ac}}{i_p} \tag{2.45}$$

and,

$$d_1 = \frac{2Lf_s}{d} \frac{i_p}{v_{ac}} \tag{2.46}$$

In the above expressions,  $f_s$  is the switching frequency, d is the duty-cycle and  $d_1$  is the relative time in a switching period the inductor current discharges to zero, respectively.

Fig. 2-9. PWM switch model of the flyback converter.

Next, Fig. 2-9(a) was taken to demonstrate that the transformer polarity does not affect the input output relation and the polarity information of the output voltage is contained in the model. Under steady-state condition, L is considered short and C is open, the following relation can be obtained from the circuit:

$$-d(\pm nv_a - v_p) = v_p \tag{2-47}$$

In the above expression, the "+" sign before  $nv_a$  corresponds to the transformer polarity indicated by "#". A transformer with this polarity should result in a negative output voltage  $v_p$  as is also predicted by the Equation 2-47 and the result is given as,

$$\frac{v_p}{v_-} = -\frac{+nd}{1-d} \tag{2-48}$$

# 2.4.2 The Weinberg Converter

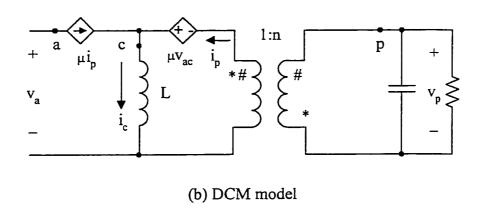

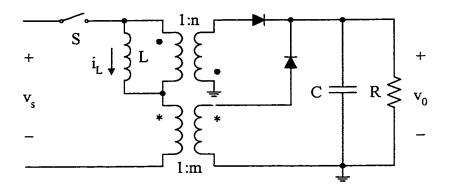

The Weinberg converter is a cascade-input, parallel-output connection of the flyback converter and a transformer [69, 70]. This converter was adopted in the space station power supply systems. Figure 2-10 shows its simplified one-switch version. However, the model given in Fig. 2-11 can also be applied to the two-switch topology with minor modifications.

Justification of the average model in Fig. 2-11(a) can be understood by comparing the state-space equations of this model and the converter circuit (Fig. 2-10) following the steps outlined in Equations 2.1 to 2.6. Both give the same results as given below:

$$L\frac{di_L}{dt} = -\left(\frac{1-d}{n} + \frac{d}{m}\right)v_0 + dv_s$$

$$C\frac{dv_0}{dt} = \left(\frac{1-d}{n} + \frac{d}{m}\right)i_L - \frac{v_0}{R}$$

(2.49)

Steady-state relations can be easily derived from Fig. 2-11(a). Consider,

Fig. 2-10. Topology of the Weinberg converter.

Fig. 2-11. PWM switch model of the Weinberg converter.

$$V_{ao} = V_s - \frac{V_0}{m}$$

and,

$$V_0 + d(-nV_{ao} - V_0) = 0$$

The well-known voltage conversion ratio M for the Weinberg converter is obtained as:

$$M \underline{\triangle} \frac{V_0}{V_s} = \frac{d}{\frac{1-d}{n} + \frac{d}{m}} \tag{2.50}$$

For the DCM operation, Fig. 2-11(b) is also a very convenient model to derive steady-state voltage conversion ratio and critical condition governing the operation modes. The derivation process is given below:

$$I_0 = \frac{I_p}{n} + \frac{\mu I_p}{m}$$

or,

$$I_{p} = \frac{mn}{m + n\mu} I_{0} \tag{2.51}$$

From Equation 2.45, we have,

$$\mu = \frac{D^2}{2Lf_s} \frac{V_s - \frac{V_0}{m}}{\frac{mn}{m + n\mu} I_0} = \frac{D^2}{k} \frac{m + n\mu}{mn} \left( \frac{1}{M} - \frac{1}{m} \right)$$

(2.52)

In Equation 2.52, M is the conversion ratio and k is defined as,

$$k \triangleq \frac{2Lf_s}{R} \tag{2.53}$$

Consider also,

$$V_0 = n\mu V_{ac} = n\mu \left(V_s - \frac{V_0}{m}\right)$$

or,

$$\mu = \frac{mM}{n(m-M)} \tag{2.54}$$

From Equations 2.52 and 2.54, we obtain,

$$M = \frac{D(\sqrt{D^2 + 4km^2} - D)}{2km}$$

(2.55)

Notice that in the above equation, M is independent of n.

The relative time  $D_1$  for the inductor current to drop to zero can be determined from Equations 2.46 and 2.54:

$$D_{1} = \frac{2Lf_{s}}{D} \frac{I_{p}}{V_{s} - \frac{V_{0}}{m}} = \frac{n(\sqrt{D^{2} + 4km^{2}} - D)}{2m}$$

(2.56)

By letting  $D_1$ =1-D, the converter enters a critical operation mode where it operates at the edge of CCM and DCM. A critical circuit parameter defined in Equation 2.53 should satisfy the following expression for this operation mode:

$$k_{crit} = \frac{1-d}{n} \left( \frac{1-d}{n} + \frac{d}{m} \right) \tag{2.57}$$

# 2.5 Challenges in Modeling PFC Converters

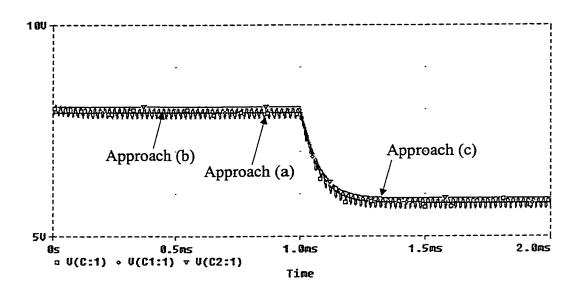

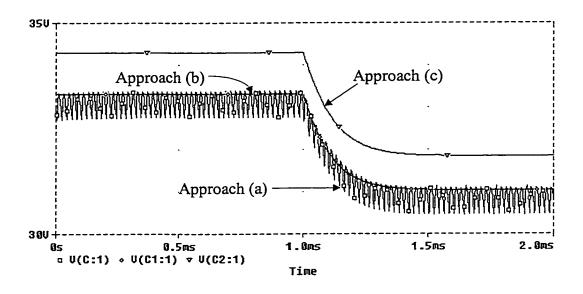

While state-space averaging technique has been proven in the past to be a powerful tool for a large family of PWM converters, it breaks down when applied to resonant and multi-resonant converters. As has been shown in Section 2.2, the averaging process requires considerable amount of algebraic manipulations even for non-resonant power converters.