Advanced techniques of single-stage power factor correction AC-DC converters

Wu, Wenkai

*ProQuest Dissertations and Theses*; 2003; ProQuest Dissertations & Theses (PQDT) pg. n/a

8 1 5 5 5

UMI

MICROFILMED 2003

## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# ADVANCED TECHNIQUES OF SINGLE-STAGE POWER FACTOR CORRECTION AC-DC CONVERTERS

by

# WENKAI WU B.S. Xi'an Jiaotong University, 1990 M.S. Tsinghua University, 1993 Ph.D. Tsinghua University, 2000

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2003

**UMI Number: 3081555**

# I MI°

# UMI Microform 3081555

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

## **ABSTRACT**

Power supplies connected to AC mains introduce harmonic currents in the utility. It is very well known that these harmonic currents cause several problems such as voltage distortion, heating, noises, and reduce the capability of the line to provide energy. This fact and the presence of Standards or Recommendations have forced the industry to use power factor correction (PFC) in power supplies.

This dissertation aims to improve the performance of the single-stage power factor correction (S<sup>2</sup> PFC) AC-DC converters with reduced cost. In the dissertation's first two chapters, an overview of current techniques for single-stage PFC AC-DC power systems is given. Further, issues and challenges of the existing systems are addressed in detail.

In the dissertation's third chapter, the existing S<sup>2</sup> PFC AC-DC approaches are topologically generalized to pursue a methodology for potential topology variation, thereafter to overcome the issues that block the applications of single stage PFC AC-DC conversion approaches.

In the dissertation's following chapters, applications of the proposed translation rule are discussed, and the subject of design of high quality S<sup>2</sup> PFC AC-DC power systems is investigated from the perspective of cost-effectivity, simplifying the conversion process while simultaneously keeping acceptable performance. The focus is put on alleviating voltage stress and current stresses, and better energy management in power conversion

that features reduced complexity and higher efficiency.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere appreciation to my advisor, Dr. Issa Batarseh for his guidance, encouragement and support. Dr. Batarseh's extensive vision and creative thinking have been the source of inspiration for me throughout this work. It was an invaluable learning experience to be one of his students.

I am grateful to my committee members, Dr. Wasfy Mikhael, Dr. Louis Chow, Dr. Takis Kasparis and Dr. Thomas Wu for their valuable suggestions and numerous help.

It has been a great pleasure to work in the Florida Power Electronics Center (Florida PEC). I would like to acknowledge the Florida PEC administrative and management staff, Mrs. Mickey Gravois, Ms. Elizabeth Plaisted for their countless help.

I would like to thank my colleagues, Mr. Weihong Qiu, Dr. Wei Gu, Dr. Shiguo Luo, Mr. Nattorn Pongratananukul, Dr. Hong Mao, Mr. Songquan Deng, Mr. Khalid Rustom, Mr. Jaber Abu-Qahouq, Dr. Peter Kornetzky, and Dr. Christopher Iannello. It was a pleasure to work with such a talented, hard-working and creative group. Further more, their friendship and help have made my stay at Florida PEC pleasant and enjoyable.

My heartfelt appreciation goes toward my family, who has always been there with their love and encouragement.

This work was supported by the National Aeronautics and Space Administration,

Air Force and the National Science Foundation under award number NASA-STTR phase

II grant # NAS10-00038.

# **TABLE OF CONTENTS**

| 1. | INTRODUCTION                                            | 1   |

|----|---------------------------------------------------------|-----|

|    | 1.1. Research Background and Motivation.                | 1   |

|    | 1.2. Dissertation Outline                               | 4   |

| 2. | REVIEW OF SINGLE-STAGE POWER FACTOR CORRECTION (P       | FC) |

|    | CONVERTERS                                              | 6   |

|    | 2.1 Introduction.                                       | 6   |

|    | 2.2 Review of Single-Stage PFC Converters               | 7   |

|    | 2.3 Issues, Trend and Challenges                        | .13 |

|    | 2.4 Summary                                             | 16  |

| 3. | TOPOLOGICAL METHODOLOGY FOR SINGLE-STAGE AC-DC P        | 'FC |

|    | CONVERTERS                                              | 17  |

|    | 3.1 Introduction                                        | 17  |

|    | 3.2 2-Terminal PFC Cell and 3-Terminal PFC Cell.        | .17 |

|    | 3.3 Topological Analysis for Key Issues                 | .19 |

|    | 3.4 Variations of PFC Cell and Their Potential Features | .21 |

|    | 3.5 Summary                                             | .23 |

| 4. | VOLTAGE STRESS SUPPRESSION TECHNIQUES                   | 24  |

| 4.1. Introduction                                                      | 24  |

|------------------------------------------------------------------------|-----|

| 4.2. Mechanism for High Intermediate Bus Voltage Stress                | 25  |

| 4.3. Several Schemes to Alleviate Bus Voltage                          | 28  |

| 4.3.1. Series-Charging, Parallel Discharging Capacitors Scheme (SCPDC) | 28  |

| 4.3.2. Bus Voltage Feedback                                            | 30  |

| 4.3.3. Utilizing Buck Topology                                         | 31  |

| 4.4. Control Schemes to Alleviate Bus Voltage                          | 31  |

| 4.4.1. DCM + CCM combination with variable frequency control           | 32  |

| 4.4.2. Both Functional Blocks Operate under Same Mode                  | 33  |

| 4.4.3. Proposed critical DCM + CCM Operation Mode                      | 34  |

| 4.5. Proposed Voltage Clamping Scheme                                  | 37  |

| 4.5.1. Conceptual overview                                             | 37  |

| 4.5.2. Design Considerations                                           | 40  |

| 4.5.3. Simulated and Experimental Results                              | 40  |

| 4.5.4. Simulation and Experimental Results                             | 49  |

| 4.5.5. Topology Derivation.                                            | 55  |

| 4.6. Summary                                                           | 56  |

| CURRENT STRESS ALLEVIATING APPROACHES                                  | 57  |

| 5.1. Introduction                                                      | 57  |

| 5.2. Peak Value Clamping Technique                                     | 57  |

| 5.2.1. Proposed Topology and Operation Principle                       | .59 |

| 5.2.2. Simulation and Experimental Results                             | 67  |

5.

|    | 5.2.3. Topology Derivations                                  | 72    |

|----|--------------------------------------------------------------|-------|

|    | 5.3. Peak Value Reduction Approach                           | 74    |

|    | 5.4. CCM approaching Schemes                                 | 76    |

|    | 5.5. Summary                                                 | 78    |

| 6. | BETTER ENERGY MANAGEMENT PHILOSOPHY                          | 79    |

|    | 6.1 Conceptual Overview                                      | 79    |

|    | 6.2 Processing Less Energy                                   | 80    |

|    | 6.2.1 System Configuration and Operation Principle           | 80    |

|    | 6.2.2 Simulated and Experimental Verifications               | 81    |

|    | 6.3 Higher Efficiency Processing Approaches                  | 83    |

|    | 6.3.1 System Configuration and Operation Principle           | 83    |

|    | 6.3.2 Control Design                                         | 84    |

|    | 6.3.3 Simulated and Experimental Verifications               | 96    |

|    | 6.4 Summary                                                  | 97    |

| 7. | A NOVEL CONTROL SCHEME FOR SINGLE-STAGE AC-DO                | PFC   |

|    | CONVERTER                                                    | 99    |

|    | 7.1. Conceptual Overview                                     | 99    |

|    | 7.2. Confined Critical Conduction Mode Control               | 102   |

|    | 7.2.1. Operation Principle                                   | 104   |

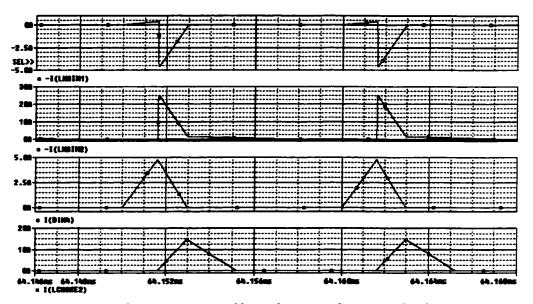

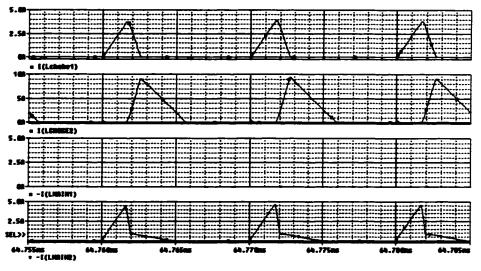

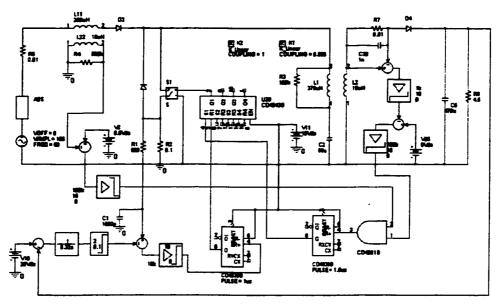

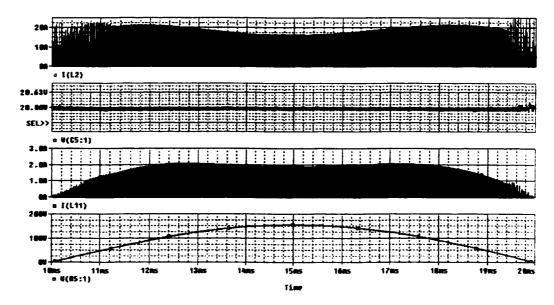

|    | 7.2.2. Simulated Verifications                               | 108   |

|    | 7.3. Derived Critical Conduction Scheme for Single-Stage PFC | AC-DC |

|    | Conversion                                                   | 112   |

| 8. | SUMMARY     | .116 |

|----|-------------|------|

| 9. | REFERENCES. | 12   |

viii

# **LIST OF FIGURES**

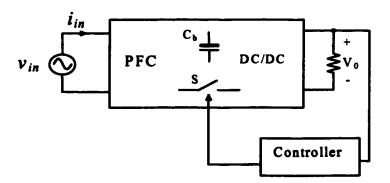

| Figure 1-1 Two-stage PFC AC-DC scheme.                                        | 1  |

|-------------------------------------------------------------------------------|----|

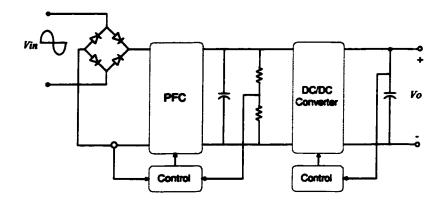

| Figure 2-1 Existing S <sup>2</sup> PFC topologies                             | 10 |

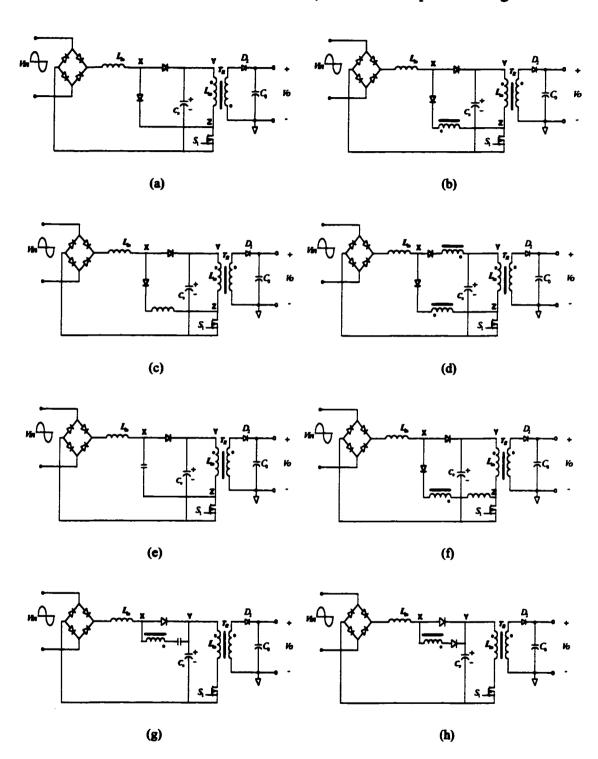

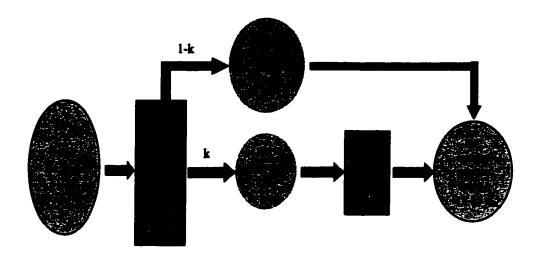

| Figure 3-1 Generalized PFC schemes                                            | 19 |

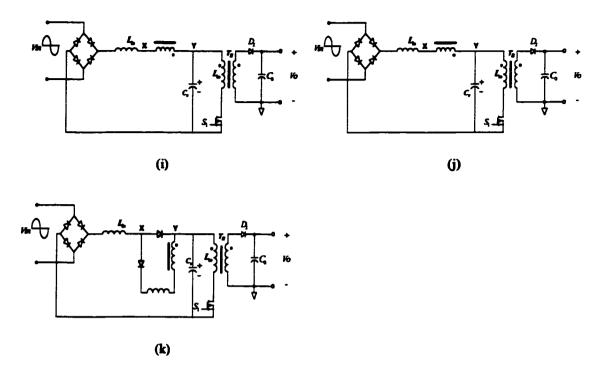

| Figure 3-2 Topology variations for the generalized schemes                    | 22 |

| Figure 4-1 General block diagram of S <sup>2</sup> PFC converters             | 25 |

| Figure 4-2 Functional block diagram of S <sup>2</sup> PFC converters          | 26 |

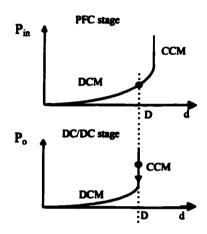

| Figure 4-3 Relationship between the input power, output power, and duty-cycle | 27 |

| Figure 4-4 A S <sup>2</sup> PFC converter with low capacitor voltage          | 29 |

| Figure 4-5 BIFRED converter with DC voltage feedback                          | 30 |

| Figure 4-6 Buck based S <sup>2</sup> PFC converter                            | 32 |

| Figure 4-7 Operation waveform of boost inductor in Fig. 4-4                   | 34 |

| Figure 4-8 Calculated curve of Vcs versus RL                                  | 36 |

| Figure 4-9 Voltage claming PFC scheme with flyboost transformer               | 38 |

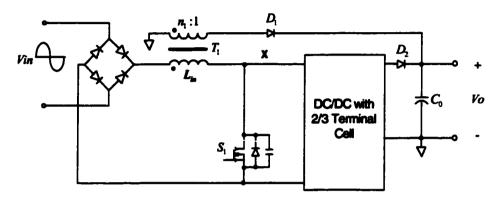

| Figure 4-10 Proposed PFC AC-DC configuration                                  | 39 |

| Figure 4-11 Proposed topology                                                 | 40 |

| Figure 4-12 Operation modes of four intervals in one switching cycle          | 42 |

| Figure 4-13 Idealized key waveforms in one switching cycle                    | 42 |

| Figure 4-14 Simulation schematics                                             | 49 |

| Figure 4-15 Simulation results                                              | 52            |

|-----------------------------------------------------------------------------|---------------|

| Figure 4-16 Universal input 20V@4.5A adapter prototype                      | 53            |

| Figure 4-17 Measured line current and voltage                               | 53            |

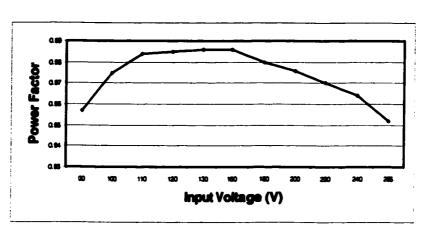

| Figure 4-18 Measured power factor vs. line voltage under full load          | 54            |

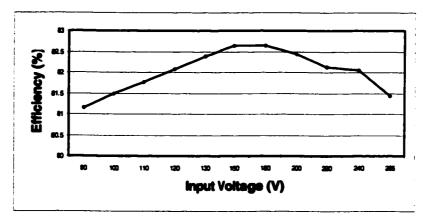

| Figure 4-19 Measured efficiency vs. line voltage under full load            | 54            |

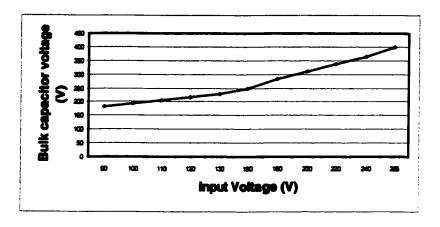

| Figure 4-20 Maximum voltage vs. line voltage under full load                | 55            |

| Figure 4-21 Topology derivation                                             | 55            |

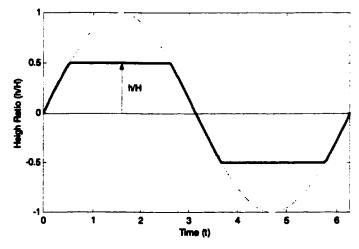

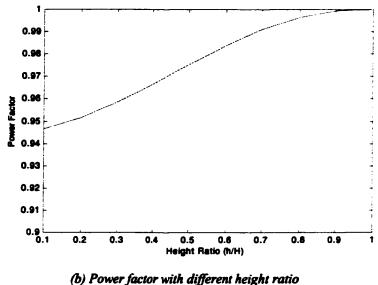

| Figure 5-1 Assorted input current waveform                                  | 58            |

| Figure 5-2 Current waveform with flat-top (a) and the power factor with dif | ferent height |

| ratio(b)                                                                    | 59            |

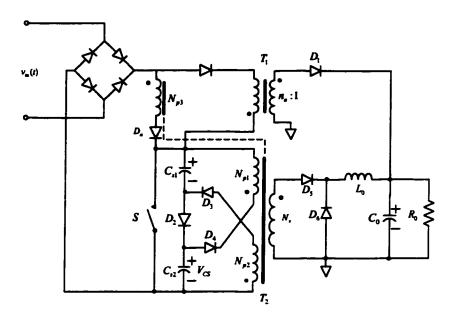

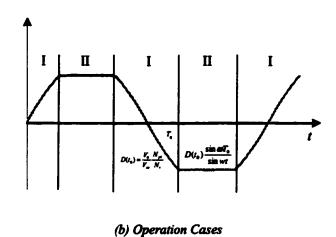

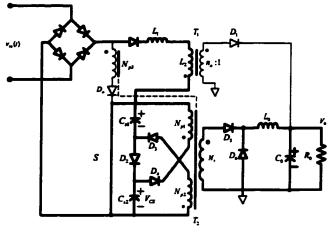

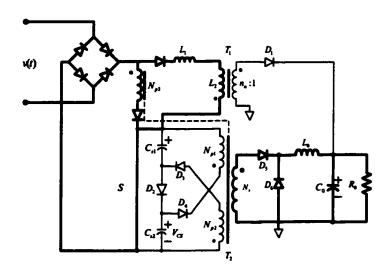

| Figure 5-3 Proposed topology and its operation case                         | 61            |

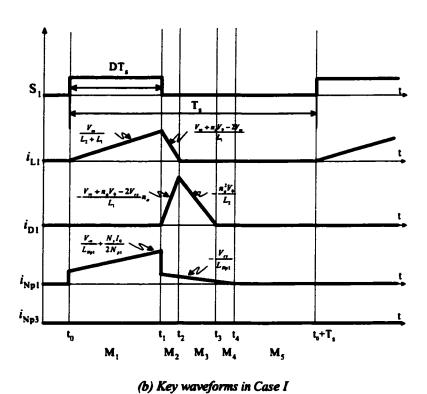

| Figure 5-4 Case I                                                           | 62            |

| Figure 5-5 Case II                                                          | 66            |

| Figure 5-6 Simulation schematics                                            | 69            |

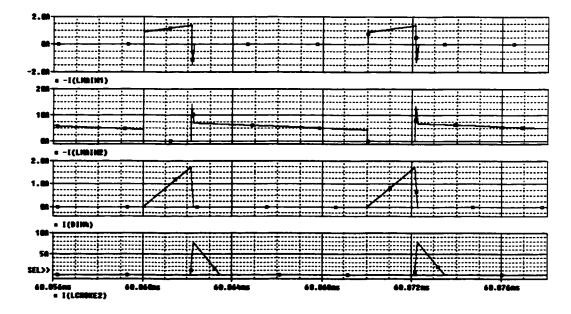

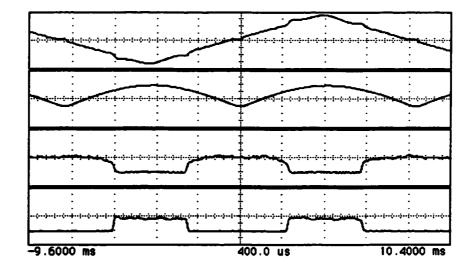

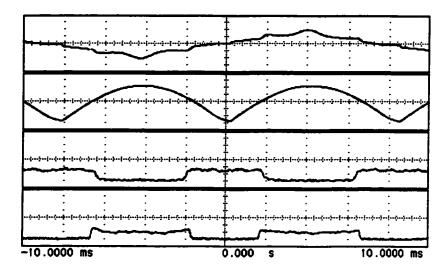

| Figure 5-7 Simulation results                                               | 71            |

| Figure 5-8 Reference voltage for PWM generation (upper trace 1V/div) and i  | nput voltage  |

| (lower trace 100V/div, Post=48/@4174)                                       | 72            |

| Figure 5-9 Experimental results                                             | 73            |

| Figure 5-10 Topology derivations                                            | 74            |

| Figure 5-11 Idealized key waveforms in one switching cycle                  | 76            |

| Figure 5-12 Simulated results for circuit shown in Fig. 4-12                | 76            |

| Figure 5-13 Single-Stage CCM PFC with resonant tank                         | 78            |

| Figure 5-14 Single stage CCM PFC operation                                              |

|-----------------------------------------------------------------------------------------|

| Figure 6-1 Energy processing schemes80                                                  |

| Figure 6-2 Less energy processing schemes                                               |

| Figure 6-3 Simulation (a) and experimental (b) results for the topology shown in Fig. 4 |

| 11(a)84                                                                                 |

| Figure 6-4 Active clamp bi-flyback converter85                                          |

| Figure 6-5 Modified control scheme86                                                    |

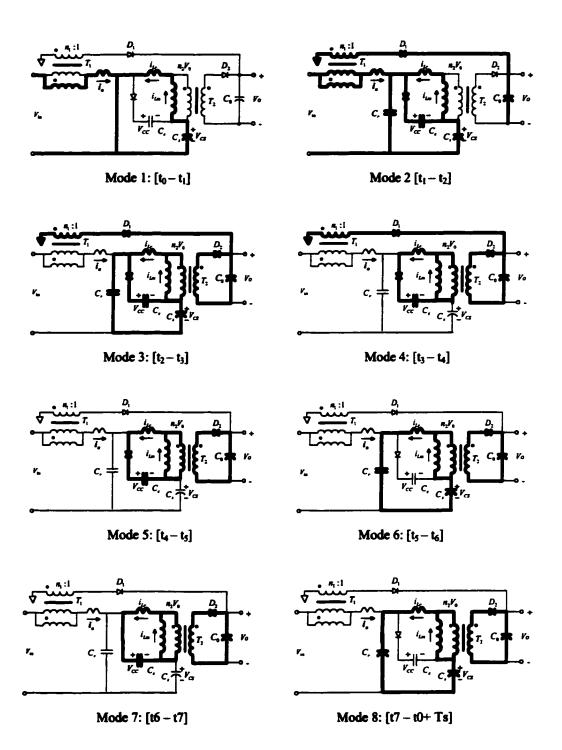

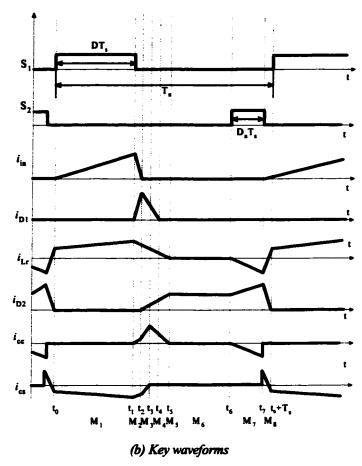

| Figure 6-6 Operation modes (a), and key waveforms in charge interval (b)88              |

| Figure 6-7 Operation modes (a), and key waveforms in discharge interval (b)95           |

| Figure 6-8 Developed prototype for NASA97                                               |

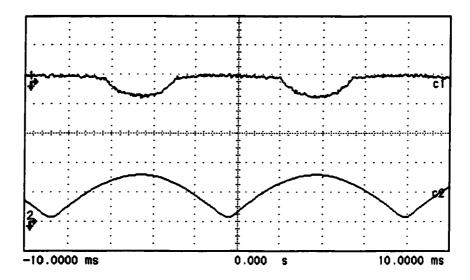

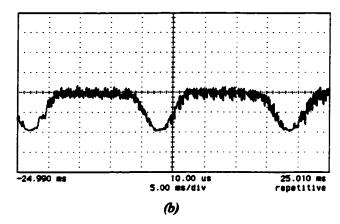

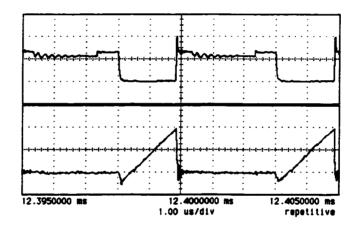

| Figure 6-9 Soft switching waveforms (Upper: Drain source voltage; Lower: Drain          |

| current)97                                                                              |

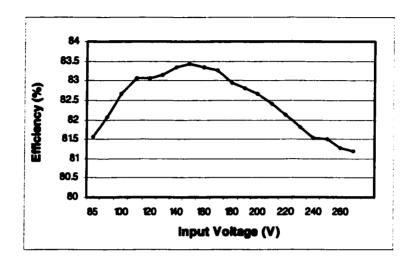

| Figure 6-10 Full load efficiency over the entire line                                   |

| Figure 7-1 The BIFRED converter                                                         |

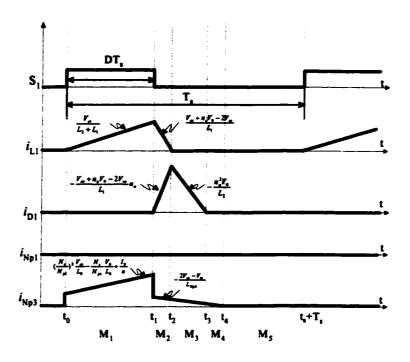

| Figure 7-2 Idealized key waveforms for BIFRED with critical conduction mode106          |

| Figure 7-3 Critical conduction mode control simulation circuit and detailed waveforms   |

| 110                                                                                     |

| Figure 7-4 Simulation waveforms in one line cycle                                       |

| Figure 7-5 Experimental setup based on the proposed topology shown in Fig. 4-           |

| 11(a)113                                                                                |

| Figure 7-6 Derived critical conduction control scheme                                   |

| Figure 7-7 Simulation results with derived critical conduction control scheme           |

#### 1 INTRODUCTION

# 1.1 Research Background and Motivation

Power conversion system design issues are becoming increasingly important in state-of-the-art electronic systems. However, the basic power architecture in current electronic systems remains the same as it was decades ago [1]. Many current power architectures are no longer effective in terms of performance and/or cost.

Power supplies connected to AC mains introduce harmonic currents in the utility. It is very well known that these harmonic currents cause several problems such as voltage distortion, heating, noises, and reduce the capability of the line to provide energy. This fact and the presence of Standards or Recommendations have forced the industry to employ power factor correction in power supplies. Active power factor corrective techniques are becoming an important feature that is compulsorily required of switching power supplies.

Unity power factor and tight output voltage regulation are achieved with the very well known two-stage approach, shown in Figure 1-1. This is probably the best option for high power AC-DC converters due to the following reasons:

- Sinusoidal line current guarantees the compliance of any Regulations.

- It is valid to operate with universal line voltage.

l

Fig. 1-1 Two-stage PFC AC-DC scheme

Voltage on the storage capacitor is controlled and it allows a good design of the second stage.

However, since two cascading converters compose the power stage, size, cost and efficiency are penalized, mainly in low to medium power applications.

Although unity power factor is the ideal objective, it is not necessary to meet the Regulations with unity power factor. For example, both IEEE 519 and IEC 1000-3-2, despite being very different in nature, allow the presence of harmonics in the line current [2]. This fact has lead to the publication of a great number of papers in the last years, with solutions that obtain some advantages over the two-stage approach. Some of these circuits are practical but others are too complex to be worth the change.

The motivation drives us to incorporate advanced power conversion techniques into the system of Fig.1-1 in order to obtain further simplification of the overall AC-DC structure. An alternative solution to realize the goal is to integrate the active PFC stage with the isolated high quality output DC-DC stage into one stage, which is known as single-stage converter with the least components and simplest controller.

Theoretically, changing the two-stage scheme to one-stage scheme can substantially mitigate the cost and complexity of PFC AC-DC converter. Then the question arises, why has such a concept not been extensively adopted in today's power systems? The answer is because there are still some of the existing technical challenges with respect to the development of viable single-stage PFC AC-DC converters, such as high voltage stress, high current stress and low efficiency, etc.

It's noted that the 2001 global market forecast indicated that the hottest trend in the external AC-DC power supply markets is the rapid growth in the higher wattage segments, typically wattage range of 50W to 150W (or higher). Compared with the lower-wattage segments, this segment is growing at a faster rate of about 16.7% per year [3]. Therefore, pursuing a cost-effective single-stage conversion scheme with improved performance, especially reduced voltage and current stresses, is still an attractive research topic.

With the effectivity of newly issued national and international Regulations, and increasing dollar market, the cost-effective S<sup>2</sup> PFC AC-DC conversion is one of the hottest research areas in power electronics. This dissertation is intended to systematically address the major technical issues in existing S<sup>2</sup> PFC AC-DC conversion and to give proper cost-effective solutions.

# 1.2 <u>Dissertation Outline</u>

The dissertation is organized into eight chapters, including the conclusion chapter, as follows:

Chapter 1 presents background and motivations of this work.

Chapter 2 offers a review for current techniques proposed for the PFC AC-DC conversion and discusses in details various issues, solution trends, and.

Chapter 3 first generalized the current S<sup>2</sup> PFC AC-DC conversion approaches into two categories, and addresses the key issues of S<sup>2</sup> PFC AC-DC converters from the view of topology. Then, several potential topology variations, applying generalized rules, are proposed to overcome the barriers summarized in Chapter 2.

Chapter 4 first introduces the mechanism of high voltage stress in single-stage PFC approaches, and briefs the documented solutions. Then, a new PFC cell with inherent voltage clamping feature, called "fly-boost", is presented based on topological methodology.

Chapter 5 presents three current stress suppression techniques. Current stress leads to lower efficiency and deteriorates EMI performance, generally, DCM operation inevitably brings about higher current stress, and CCM is preferred from the view of lower current stress. Lower current stress DCM operation scheme and high power factor CCM operation scheme are proposed for specific applications.

4

Chapter 6 investigates better energy management techniques in terms of processing less energy or processing it with higher efficiency. Unlike the two-stage schemes, in which the power being processed twice by two serially connected stages, single-stage scheme has potential to process less energy during power conversion. In this part, straight energy transfer and high efficiency processing with soft switching scheme are introduced, and the characteristics such as increased efficiency, near unity power factor and lower voltage stress are experimentally verified.

Chapter 7 proposed two novel critical conduction mode control schemes, which are tailored for proposed topology to further improve its performance.

Chapter 8 summarizes the conclusions of this work and presents suggestions for future work in related research directions.

# 2 REVIEW OF SINGLE-STAGE PFC CONVERTERS

## 2.1 Introduction

Traditional diode rectifiers used in front of the electronic equipment draw pulsed current from the utility line, which deteriorates the line voltage, produces radiated and conducted electromagnetic interference, and leads to poor utilization of the capacity of the power sources. In compliance with IEC 1000-3-2 harmonic regulation, many power factor corrected AC-DC rectifiers have been proposed in recent years. For single-phase electronics applications, passive power filters, active one- and two-stage power factor correction (PFC) rectifiers are typical approaches used to achieve high power factor and low total-harmonic-distortion (THD). Passive power filters exhibit high efficiency and low cost, but they are bulky and heavy due to the size of the line frequency inductors and capacitors.

The two-stage PFC approach uses an input current shaping converter in front of a DC-DC converter. The two converters are controlled independently to achieve high quality input current shaping and fast output voltage regulation. This method is known for its superior performance, such as high power factor, low input current harmonics, good hold-up time, and optimized design of the DC-DC converter, but at the cost of additional semiconductor switches and control circuitry that may not be justified for lower power applications. In a single-stage PFC rectifier, input-current shaping, isolation,

and fast output regulation are performed in a single-stage. A single-stage PFC rectifier typically integrates an input current shaper and an isolated DC-DC converter with a shared switch and controller. The energy storage device in between serves as a buffer for frequency isolation between the PFC and the DC-DC converter as well as provides necessary hold up time. This method provides a compromise between the performance and cost.

Comprehensive comparisons of the two approaches at manufacturing cost and performance [3] have shown that the single-stage PFC is a cost-effective solution for low power applications (typical below 200 watts).

## 2.2 Review of Single-Stage PFC Converters

The concept for single-stage PFC can be traced back to some early work presented in [4,5]. In article [4], a single power stage with dual outputs produces both the desired DC output and a boosting supply in series with the input. Without active control of the boost supply, a reasonably good input current shape results due to the natural gain characteristics of the boost resonant circuit. This circuit is original but the component count is high. Another way to realize single-stage PFC is by cascading a boost PFC with a DC-DC converter using one switch as shown in [5]. Both pulse width modulation (PWM) and frequency modulation (FM) were applied in the control circuitry. The rectifier has very high power factor. However, the circuit suffers wide frequency

variation and high voltage stress. Nevertheless, this circuit presents an early form of the single-stage PFC method that integrates a boost PFC with a DC-DC converter in a cascade fashion. A very systematic synthesis of single-stage PFC using a cascade method was initiated in [6] in 1992, in which some new PFC rectifiers, BIFRED and BIBRED, were resulted from integrating a boost input current shaper with a flyback or buck converter. The characteristic marker of these rectifiers is that the energy storage capacitor is in the series path of the energy flow. Synthesis of single-stage PFC by inserting a diode in front of the Cuk and Sepic converters have resulted in the same topologies [7,8]. In BIFRED and BIBRED, the boost PFC operates in discontinuous conduction mode (DCM) to achieve automatic input current shaping, while the DC-DC converter operates in continuous conduction mode (CCM). The DC-bus capacitor voltage has a strong dependency on the load. For universal input applications, such circuits will suffer high voltage stress at light load. Articles [7,9] use frequency modulation method to keep the DC-bus voltage under control during light load. Article [8] shows a new operation mode that operates both the boost and the flyback in DCM, which has effectively reduced the DC-bus voltage and significantly improved the input current waveform.

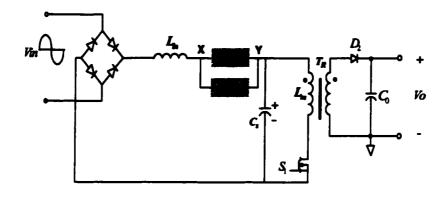

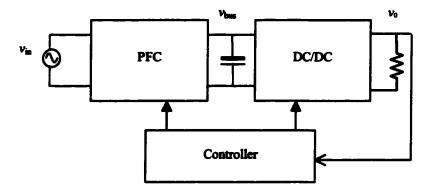

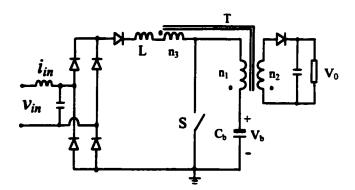

In 1994, a new family of single-stage PFC converter was synthesized in [10] that integrates a boost PFC with a DC-DC converter in such a way that the energy storage capacitor is in the parallel path of the energy flow as shown in Fig. 2-1(a). In all the PFC converters shown in [10], the boost PFC operates in DCM to achieve automatic input current shaping, while the DC-DC converter may operate in either CCM or DCM.

# However, if the DC-DC converter is in CCM, the DC-bus capacitor voltage varies with

Fig. 2-1 Existing S<sup>2</sup> PFC Topologies

the load. For universal input applications, it will suffer high voltage stress at high input voltage and light load, which requires expensive capacitors and increases the switch voltage stress. This phenomenon appears inherent to the rectifiers that cascade a boost PFC with DC-DC converter as shown in [5,6,10]. Switching frequency modulation methods were reported to alleviate the DC-bus voltage [11,12,13]. However, the switching frequency could span ten times over the whole load range in order to maintain the DC-bus voltage be low 450V, which is undesirable for the magnetic component design. Another way to suppress the DC-bus voltage is to keep the DC-DC converter in DCM for the entire load range [14,15,16], because the DC-bus voltage becomes independent of the load in DCM. However, for low-voltage applications, e.g. computer

power supplies, continuous conduction mode DC-DC converter is preferred, since it leads to lower conduction loss and smaller ripple. As a result, a compromise between the THD and the voltage stress was proposed in [17] by negative magnetic feedback using an additional transformer winding during the switch-ON interval, as shown in Fig. 2-1(b). Similar approaches were seen in [18]. Article [19] presents a comprehensive study of the magnetic feedback phenomenon and design guidelines. With this negative feedback, the conduction angle of the input current is reduced. The gained benefit is that the DC-bus capacitor voltage Vcb may be maintained below 450V, while the DC-DC converter is in CCM for heavy load, which warrants the use of low cost 450V electrolytic capacitors. A single-stage PFC method with double-negative magnetic feedbacks (feedback during both switch ON and OFF intervals) was proposed [20,21] as shown in Fig. 2-1(c). This method can also keep the voltage Vcb below 450V. In addition it enables CCM operation of both the PFC and the DC-DC converter while the input harmonics are still within the range of Class D standard. In order to reduce the conduction loss and ripple in the input, several single-stage PFC rectifiers with CCM operated PFC were proposed recently as shown in Fig. 2-1(d), (e) (f), (g). The converter in Fig. 2-1(d) was derived from the charge bump concept [23] and the converters in Fig. 2-1(e-g) are based on series insertion of a voltage source and a loss free resistor in between the diode bridge and the DC-DC converter [24-28]. A magnetic switch concept was introduced in [29-33], where the PFC usually contains one additional winding coupled to the transformer of a DC-DC converter.

Several examples are shown in Fig. 2(h), (i), (j), where the input PFC cell in Fig. 2-1(i) operates in CCM. Note that although the flyback DC-DC converter is shown in all approaches in Fig. 2-1, the discussion here are applicable to forward and other topologies as well.

Topologies variations are also found in many other forms. A parallel PFC concept was reported in [34], while three switch-states were used to provide two-dimensional control for the PFC function and fast output regulation. The performance is commendable but the implementation is very complicated. In [35,36], a flyback converter is used as PFC, which results in better input current waveform but higher current stress. An interesting method of combining a boost PFC with a forward converter with two energy storage capacitors was shown in [37]. With two capacitors, the spike due to the leakage inductance during switch turn off is subdued. Very good performance was demonstrated. Article [38] shows a new single-stage PFC rectifier that uses an AC side inductor and two additional diodes to directly connect the AC voltage to the switch. This circuit has similar operational principle as the one proposed in [10], but with less conduction loss. The rectifier proposed in [16] uses a boost bridge rectifier that shares its switches with the following flyback DC-DC converter with the intention to increase the power level. Since both the boost bridge rectifier and the flyback converter operate in DCM, the conduction loss is high. In addition, this circuit may suffer high common mode noise. Article [39] presented a rectifier that integrates a boost PFC and a half bridge DC-DC converter. Synchronized rectifiers are used to achieve high efficiency for low voltage applications. Article [40] proposed a regenerative clamping circuit for single-stage PFC to reduce the

turn-off losses and stress of the switch. In addition, the power factor is also improved. Article [41] reported a single-stage high power factor converter using the Sheppard-Taylor topology. Two possible operation regimes are described. Compared to the usual boost-buck cascade operating in the first regime, the proposed converter has a wider operating range. When operating in the second regime, the modified boost stage has the ability of producing a harmonic free input current, unlike the standard boost PFC whose current always suffers a cusp distortion. A new parallel approach for single-stage PFC was reported in [42~45] that employs an auxiliary DC-DC converter to supplement energy to the load when the direct power from the line is low. This method improves overall efficiency because only partial energy is processed twice. An additional switch is required. Extensive syntheses were performed in [46,47] that yielded many families of single-stage PFC rectifiers based on dither effect [46] and partial energy processing [47]. These two papers present interesting teaching from the principle of synthesis as well as analysis to the implementation of the new circuits, and thus are valuable to researchers in the power factor correction area.

#### 2.3 Issues, Trend and Challenges

The underlining strategy of the single-stage PFC scheme is to design the circuit in a certain way that allows its PFC circuit and power conversion circuit to share the same power switch with the same controller. From the above existing research efforts, we

found this kind of arrangement brought about several main issues, which we will discuss below.

The first issue is the high voltage stress, accompanying a wide capacitor voltage range. The high bus capacitor voltage-stress generally makes most of the existing S<sup>2</sup> converters impractical [1]. The inherent reason of high DC-bus voltage is in power unbalance between the input and the output. Although the output power is kept relatively constant over one line cycle, instantaneous AC input power always varies. As a result, a bulky capacitor is needed to handle the instantaneous power difference between the input and output, such that the output voltage is regulated tightly and free of line ripple. It is because single-stage converters have only limited capability to process unbalanced power with a single active switch and limited capacitance capacitor. The high bus capacitor voltage stress normally exists for most of single-stage PFC converters, which makes most of existing single-stage converters impractical for universal input usage. This issue is more severe under high line and light load conditions [2,4]. A high bus voltage means high component rating, high cost and low efficiency. The accompanying issue with the first one is that the wide capacitor voltage range of the single-stage PFC converters will require larger component ratings compared to the two-stage PFC converters. To make situation worse, the intermediate bus voltage is determined by many factors such as boost inductance, transformer turns ratio, and input voltage, etc. Therefore, how to characterize bus voltage and optimize designing of the power stage will be further challenges.

The second issue is the high current stress due to the DCM operation. The PFC stage in an S<sup>2</sup> PFC AC-DC converter normally operates in DCM mode to utilize its inherent current shaping capability, therefore, compared with cascading two-stage schemes, S<sup>2</sup> PFC AC-DC conversion has higher current stress. Current stress not only accompanies with increased switching losses and lower efficiency, but also brings about annoying EMI issues.

The third issue is as the result of high voltage and current stresses, the lower efficiency. The fourth issue is that one power stage and DCM operation makes S<sup>2</sup> PFC AC-DC converters only attractive for low power applications, limiting its application. Therefore, how to push the power rating higher with a low-cost single-stage approach becomes a natural objective.

Although unity power factor is the ideal objective, it is not necessary to meet today's Regulations with unity power factor. For example, both IEEE 519 and IEC 1000-3-2, even being very different in nature, allow the presence of harmonics in the line current [1,2]. This fact opens the door for the trade-off quality-cost techniques, which are capable of overcoming the above issues. Actually in the last years, a great number of papers pursue such solutions that obtain some advantages over the two-stage approach. Some of these circuits are practical, but most of them are too complex to be worth the change.

Seeking the simplest low cost S<sup>2</sup> PFC solution with better performance, including high efficiency, low voltage and current stresses, low harmonics and high power factor will be further efforts, and are the objective of this dissertation.

#### 2.4 Summary

A review of existing single-stage PFC AC-DC converters is given in this Chapter. Main issues such as high voltage stress, high current stress, low efficiency and low power rating in current S<sup>2</sup> PFC AC-DC approaches are summarized and presented as the topic needs further efforts.

# 3 TOPOLOGICAL METHODOLOGY FOR SINGLE-STAGE PFC CONVERTERS

#### 3.1 Introduction

For single-stage PFC rectifiers, the performance measures, such as efficiency, hold up time, component count and circuit complexity, component voltage and current stresses, input current quality, etc., are largely dependent on the circuit topology. In recent years, the heat wave of searching for single-stage PFC rectifiers has resulted in hundreds of published papers in the open literatures and countless topologies. This chapter presents a topological study of the representative S<sup>2</sup> PFC converters. The intention of this study is to find a topological relationship among various converters, topologically explain the main drawbacks of current S<sup>2</sup> PFC converters, and to pursue potential variations to overcome the barriers that limit the application of S<sup>2</sup> PFC converters.

#### 3.2 2-Terminal PFC Cell and 3-Terminal PFC Cell

From the review of S<sup>2</sup> PFC AC-DC converters, it is noticed that the group of circuits shown in Fig. 2, characterized by the energy storage capacitor in the parallel path

of the energy flow, represents the main stream. The focus of this Chapter is thereby on the topological rules of this group of converters. The 2-or 3-terminal concept presented in [48] is extended to study the PFC cells. In spite of different PFC realization mechanism, from a topology point of view, the input current shaping circuits in Fig. 2-1 can be symbolized as 2- or 3-terminal cells, as shown in Fig. 3-1. Each PFC cell contains an input inductor and two branches. The "charge branch" is used to charge the input inductor when the switch is ON. The "discharge branch" is used to discharge the inductor and transfer the energy from the input inductor to bulk capacitor or output when the switch is OFF. The branches are usually composed of diodes, capacitor, inductors, and extra windings of the transformer or their combinations. Terminal X is connected to the input diode bridge; terminal Y is connected to the DC-bus bulk capacitor Cs; and terminal Z is connected to the switch in the DC-DC converter.

The 2-terminal PFC cell is inserted between the input diode bridge and DC-bus capacitor. It contains one winding coupled to the transformer of a DC-DC converter in the charge branch. When the switch is ON, the voltage across the winding cancels the capacitor voltage, so that the inductor sees only the input voltage that charges the inductor. The input inductor is discharged through the discharge branch when the switch is OFF. The topologies in Fig. 2-1(g-j) are several examples of single-stage PFC with 2-terminal PFC cells.

In a 3-terminal PFC cell, the switch is connected in a series with the charge branch.

When the switch is ON, the input inductor is charged through a switch. Similar to the 2-

terminal PFC cell, the inductor current is discharged through the discharge branch. The PFC cells in topologies of Fig. 2-1 (a-f) belong to this group.

(a) 2-Terminal PFC cell scheme

(b) 3-Terminal PFC cell scheme

Fig. 3-1 Generalized PFC schemes

# 3.3 Topological Analysis for Key Issues

From above generalized S<sup>2</sup> PFC AC-DC approaches, it is found that many reported single-stage PFC converters are electrically equivalent despite that they are topologically

different, because they employ equivalent PFC cells, although their configurations are different.

Besides, the existing issues, to a certain extent, can be topologically explained:

First, in all of the existing schemes, a Boost PFC cell is serially connected with a power charge and/or discharge path. Under this arrangement, the PFC inductor is charged in ON interval, and discharged in a boost mode in OFF interval. In the other words, all the power processed in power stage should be stored in the PFC inductor first. Thereby its boost operation mode theoretically gives the explanation why the voltage across the bulk capacitor, under any case, is higher than the peak value of input voltage. Besides, the combined PFC cell and DC-DC cell need to be well matched from the view of energy transferring, since duty ratio is only determined by the DC-DC stage. Without introducing power transferring information in a DC-DC cell will certainly result in the build up of unbalanced energy, in terms of high intermediate DC-bus voltage. That is to say, in most cases, DC-bus voltage stayed in an uncontrolled condition.

Second, since all the power should be stored in the PFC inductor first, and the PFC inductor had to operate in DCM mode to utilize its inherent current shaping feature, so input current peak should be high enough to get the desired output power, with no choice to reduce its current stress.

Third, from the view of energy transfer stream, it can be found that all the energy stored in the boost inductor should be discharged to the buffer capacitor first, and then be delivered to the output. That is to say, all the energy has been processed twice, although

its structure is a so-called single-stage. This fact is another cause resulting in lower conversion efficiency.

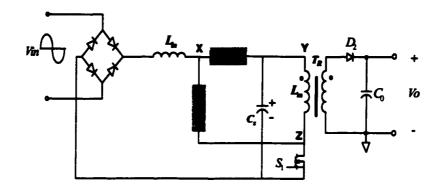

## 3.4 Variations of PFC Cell and Their Potential Features

From the above topological analysis, we found it is possible to break the confinement of current PFC cells to overcome the issues existing in current S<sup>2</sup> PFC AC-DC approaches:

First, it is not necessary that the energy stored in the PFC inductor must be discharged to the buffer capacitor; therefore, a concept to build an alternative energy transfer path arises here naturally. For example, building another discharging path straight to the output side, as shown in Fig. 3-2(a), probably gains the following benefits:

- (1) Controllable bus voltage, intuitively, less energy charged to the buffer capacitor, certainly will reduce the voltage across it. Therefore, the bus voltage may be controlled through selecting the proper energy portion being charged to the buffer capacitor.

- (2) Reduced current stress, since the discharging mode of the boost PFC inductor has already been changed. To obtain the same RMS input current, it could be carried out in a lower peak value mode.

Second, it's not necessary that all the power transferred to the output have to be stored in the Boost PFC inductor first. In fact, unlike cascading two-stage schemes, the energy had to be processed twice by two serially connected power stages. A S<sup>2</sup> PFC AC-

DC converter, from the view of its structure, it is not necessary to process the energy twice. Here an attempt arises why not push the joint "X" ahead in front of the inductor, as shown in Fig. 3-2 (b). Reducing power being charged into the PFC boost inductor can further alleviate voltage stress and provide a possibility to increase the inductance of the boost inductor to reduce the peak current; thus obtaining less current stress with higher efficiency.

(a) An alternative-discharging path for Boost inductor

(b) An bypass path for Boost inductor

Fig. 3-2 Topology variations for the generalized schemes

## 3.5 Summary

Many single-stage PFC can be viewed as a combination of the DC-DC converter with a 2-terminal or 3-terminal PFC cell. The main drawbacks of current S<sup>2</sup> PFC AC-DC converter can be explained, to a certain extent, from its topological features. In S<sup>2</sup> PFC AC-DC converters, as state-of-the-art electronic systems, it is possible to overcome the main drawbacks by breaking the confinement of current PFC cells, and employing proper topologies capable of changing current energy transferring modes.

# 4. VOLTAGE STRESS SUPPRESSION TECHNIQUES

## 4.1 Introduction

For  $S^2$  PFC converters, the DC-bus voltage stress is one of the most important issues. The inherent reason for high DC-bus voltage is the power unbalance between the input and the output. In single-stage PFC AC-DC conversion, although the output power is kept relatively constant in a certain time range, instantaneous AC input power always varies. As a result, a bulky capacitor is needed to buffer the instantaneous power difference between the input and output, such that the output voltage is regulated tightly and free of line frequency ripple. Since single-stage converters have limited capability to process unbalanced power with a single active switch, and the buffer capacitor has limited capacitance, the high voltage-stress will be built up across the buffer capacitor for most of single-stage PFC converters. Resulting high voltage normally goes beyond the tolerance of commercially available capacitors, and limits the power switches to components with higher voltage ratings, which means either high  $R_{ds,ON}$  (ON Resistance) or  $V_F$  (Forward Voltage Drop).

High bus voltage means high component rating, high cost, and low efficiency. High variable bus voltage, in fact, makes most of existing single-stage converters impractical for universal input applications. This issue is more severe in case of high line and light

load. Therefore, further efforts need to be invested to alleviate DC-bus voltage and optimize designing power stage. In this section, after briefing the existing approaches, an inherent voltage-clamping scheme is proposed, analyzed and experimentally validated.

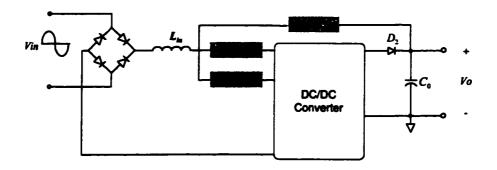

#### 4.2 Mechanism for High Intermediate Bus Voltage Stress

Figure 4-1 shows a general block diagram of S<sup>2</sup> PFC converters, which use only one active switch and one controller. In order to generalize the concept of bus voltage stress, it is desirable to use two functional blocks, a PFC block and a DC-DC block, to represent the S<sup>2</sup> PFC AC-DC converter, as shown in Fig. 4-2. The first block is a PFC stage to achieve high power factor function, which is usually a boost-like converter; the

Fig. 4-1 General block diagram of S<sup>2</sup> PFC converters

Fig. 4-2 Functional block diagram of S2 PFC converters

second functional block is a DC-DC converter to obtain tight regulation with output isolation. There is a bulky capacitor between the two functional blocks to withstand the fluctuating input power and rectified line ripple. Both PFC block and DC-DC block can operate either in DCM or in CCM. Therefore, there are four possible combinations to implement in S<sup>2</sup> PFC converters, i.e., DCM PFC + CCM DC-DC, DCM PFC + DCM DC-DC, CCM PFC + CCM DC-DC and CCM PFC +DCM DC-DC. However, these combinations present different forms of the power balance relationship. For example, the DCM PFC + CCM DC-DC combination generates a DC-bus voltage that could be as high as over 1000 V at high line and light load conditions for universal line applications [18]. Selection of switches and capacitors in this case would be limited and very costly.

Usually, it is required that the PFC block has an inherent PFC property, while using the controller regulates the output voltage of DC-DC block. On the other hand, the CCM operation for DC-DC block is preferred to reduce power losses. Therefore, for the

operating mode, the DCM PFC + CCM DC-DC is deemed to be ideal in the low to medium power level. However, critical bus voltage stress occurs in this combination. Figure 4-3 shows the relationship between the input power and the duty cycle in the PFC block, and between the output power and the duty cycle in the DC-DC block [18]. The figure explains well the reason why the unbalanced power exists.

Fig. 4-3 Relationship between the input power, output power, and duty-cycle

Since the DC-DC stage operates in CCM, the duty cycle does not change with the load variation according to Fig. 4-3. The duty cycle doesn't change immediately when the output power decreases, because of the CCM operation in the DC-DC block. Thus, the input power remains the same as that of the heavy load. There exists an unbalanced power between the input and the output. This unbalanced power has to be stored in the bulk capacitor C<sub>B</sub>, causing the DC bus voltage to increase. As a result, the output voltage will increase too. To compensate for the output voltage increase due to the increase of the bus voltage, the voltage feedback loop is operated to regulate the output voltage as a

constant. So the duty ratio has to decrease, and the input power also decreases correspondingly. This dynamic process will not stop until the input power equals the output power, and new power equilibrium is reached. In summary, power unbalance in different operating mode combination is the inherent reason for causing high bus voltage. The detailed analysis and explanation of the power balance relationship for the other combination modes have been presented in [18].

## 4.3 Several Schemes to Alleviate Bus Voltage

From the above analysis, perceptively, the bus voltage could be controlled within proper range so as to make a S<sup>2</sup> PFC converter be practical. The analysis also provides some possible approaches to resolve the bus voltage stress problem of the S<sup>2</sup> AC-DC converter at high line light load. If the power delivered by both blocks of the converter is either duty cycle dependent or independent simultaneously, the converter should have less bus voltage stress under the proper design. Some S<sup>2</sup> PFC implementation circuits with proper bus voltage have been presented in [19, 20, 21, 23]. This section classifies these circuits into the following three categories of schemes to suppress high bus voltage stress:

#### 4.3.1 Series-Charging, Parallel Discharging Capacitors Scheme (SCPDC)

A S<sup>2</sup> PFC converter with low capacitor bus voltage is proposed in [36, 37] Actually, it is a combination of a boost circuit and a forward circuit, as shown in Fig. 4-4.

There are two primary windings connected with separate bulk capacitors in series in the isolated transformer of the DC-DC stage. It is because of this unique structure, which makes the converter capacitors implement series-charging, parallel discharging capacitors scheme (SCPDC). The SCPDC means that the two energy-storage capacitors are charged in series when the switch is OFF, and discharged in parallel when the switch is ON. Thus, effectively, a two-to-one voltage division is introduced into the original single bulk capacitor, as most S<sup>2</sup> PFC converters hold, such as BIFRED and BIBRED converters.

However, although the two serially connected capacitors can handle higher voltage, the real DC-bus voltage is still high, and high voltage rating components had to be used in this conversion scheme.

Fig. 4-4 A S<sup>2</sup> PFC converter with low Capacitor voltage

#### 4.3.2 Bus Voltage Feedback

Figure 4-5 shows the modified BIFRED converter with the bus voltage feedback. The basic BIFRED converter is actually a combination of a DCM boost converter and a DC-DC flyback converter. This converter is not practical due to high DC bus voltage caused by unbalance power between two functional blocks of PFC and DC-DC. [18]

Fig. 4-5 BIFRED converter with DC voltage feedback

In the modified scheme, an additional transformer winding n3 is added on the boost inductor branch in the series. The winding then can feedback the bus capacitor voltage when the boost inductor is charged, and the feedback depth depends on the DC-bus voltage level. The feedback depth will increase when the bus voltage has an increasing trend. Thus, the input power can be automatically reduced to guarantee the balance between input and output power. As a result, the DC-bus voltage is limited within a proper range.

Based on the concept of using bus voltage feedback, some of the new topologies can be derived. In fact, this concept can be extended to most S<sup>2</sup> PFC converters, which adopted a DCM boost converter as the PFC function cell. Several derived example circuits are demonstrated in [24,25].

However, the penalty is, while obtaining low bus voltage, that input current waveform is deteriorated because of the reduced conduction angle resulted from the feedback winding, and this drawback limits its application in practical S<sup>2</sup> PFC AC-DC conversion.

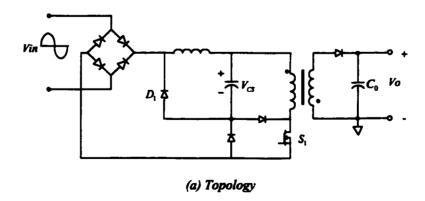

#### 4.3.3 Utilizing Buck Topology

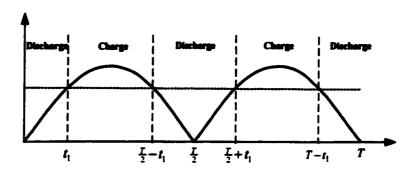

Shown in Fig. 4-6 is a buck-based S<sup>2</sup> PFC converter. In this scheme, the DC-bus voltage can be greatly reduced at light load since the output voltage of the buck converter is always lower than the input voltage. However, the reduced conduction angle is introduced when the line voltage is lower than the voltage across the bulk capacitor, which inherently leads to current harmonics and a reduced power factor.

(b) Operation modes of C. in one line cycle

Fig. 4-6 Buck based S<sup>2</sup> PFC converter

## 4.4 Control Schemes to Alleviate Bus Voltage

#### 4.4.1 DCM + CCM combination with variable frequency control

This scheme was proposed in [18]. Since the gain of the CCM DC-DC stage depends only on the duty-cycle, and the gain of the DCM boost input block depends on the frequency rather than duty-cycle, it is possible, for the DCM boost input block to regulate the capacitor voltage (without affecting the output) by a variable-frequency control. That is to say, the input power of PFC block is inversely proportional to the switching frequency at DCM with a constant duty ratio, and the unbalanced power between the input and output decreases with the increasing of switching frequency. This scheme is proven effective to resolve the bus voltage stress problem. The drawback of this approach is that large load variation range results in large range of variation in switching frequency. For a load change from full to 10% of the rated load, the switching

frequency has to be as 10 time as that of the full load to remain the same bus voltage. Such wide switching frequency variation makes it difficult to optimize the inductive components of the converter. In practical circuits, the frequency range is smaller than the theoretically calculated one because 100% efficiency is assumed in theoretical analysis.

#### 4.4.2 Both Functional Blocks Operate under Same Mode

As discussed in the last section, power unbalance in the combination DCM + CCM will cause high voltage stress on the intermediate DC-bus. However, there is no DC-bus voltage stress problem in combinations of same operating mode, either in DCM or in CCM for the two functional blocks, i.e., DCM + DCM and CCM + CCM. Taking DCM + DCM for example, the duty-cycles of the two blocks in Fig. 4-2 will simultaneously decrease with the load becoming light. As a result, the input power also decreases with output power because of decreased duty-cycle. There is no unbalanced power between the input and the output. Power balance relationship is similar in CCM + CCM combination. Thus it is concluded that there is no DC-bus voltage issue, for both functional blocks operate under the same mode with proper circuit design.

Both functional blocks operate under the same mode, i.e., (DCM PFC+ DCM DC-DC) and (CCM PFC + CCM DC-DC) combinations are practical solutions. However, the former takes a low efficiency because of higher conduction loss and turn off switching losses; the latter, generally speaking, has relatively lower power factor and higher distortion in input current.

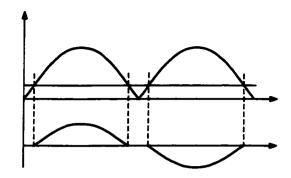

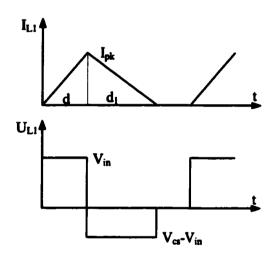

#### 4.4.3 Proposed critical DCM + CCM Operation Mode

If the DC-DC stage operates in DCM at light load, the CCM at heavy load can also limit the DC-bus voltage stress. This statement will be verified through the next theoretical analysis of an example circuit.

Figure 4-7 shows the operation waveform of a boost inductor in Fig. 4-4, and, as it can seen, the input peak current in each switching can be expressed as:

$$I_{pk} = \frac{V_{in}Sinwt}{L_i}dT_s$$

Fig. 4-7 Operation waveform of boost inductor in Fig. 4-4

The demagnetizing duration is:

$$d_1 = \frac{V_{in} \sin \alpha x}{V_{ci} - V_{in} \sin \alpha x} d$$

So, the average input current in one switching cycle can be expressed:

$$I_{avg} = \frac{1}{2} (d + d_1) I_{pk} = \frac{V_{ci} \cdot V_{in} \sin \alpha x \cdot d^2 T_i}{2L_1 (V_{ci} - V_{in} \sin \alpha x)}$$

(4-1)

Let  $m_1 = \frac{V_{cx}}{V_{in}}$ , then,

$$P_{in} = I_{avg} I_{in} = \int_{0}^{T} \frac{V_{ci} \cdot V^{2}_{in} \sin^{2} \omega t \cdot d^{2} T_{s}}{2L_{1} (V_{ci} - V_{in} \sin \omega t)} dt = \frac{d^{2} T_{s} V^{2}_{in}}{2\omega L_{1}} \int_{0}^{T} \frac{\sin^{2} x}{1 - \frac{1}{m_{1}} \sin x} dx$$

$$= P_{out} = \frac{1}{\eta} \frac{T}{2} \frac{V_{0}^{2}}{R_{L}} = \frac{1}{\eta} \frac{\pi}{\omega} \frac{V_{0}^{2}}{R_{L}}$$

After integration,

$$\frac{2m_1}{\sqrt{m_1^2 - 1}} \left(\frac{\pi}{2} + arctg \frac{1}{\sqrt{m_1^2 - 1}}\right) - \pi - \frac{2}{m_1} = f(m_1) = \frac{1}{m_1^2} \frac{\pi n^2 V_0^2}{\eta D^2 V_{in}^2} \frac{2L_1}{n^2 R_L T_r}$$

(4-2)

Let  $m_2 = \frac{V_0}{V_{cc}}$ , then:

Choose L<sub>2</sub> to operate in CCM, so:  $m_2 = D$

$$V_0^2 = \frac{m_1^2 m_2^2 V_{in}^2}{n^2} = \frac{m_1^2 D^2 V_{in}^2}{n^2}$$

And.

$$f(m_1) = \frac{2\pi}{\eta} \frac{L_1}{n^2 R_1 T_2} \tag{4-3}$$

Choose L<sub>2</sub> to operate in DCM,

$$m_2 = \frac{2}{1 + \sqrt{1 + \frac{4k}{D^2}}}$$

, where  $k = \frac{2L_2}{R_L T_s}$

Then.

$$f(m_1) = \frac{m_2^2}{D^2} \frac{2\pi}{\eta} \frac{L_1}{n^2 R_L T_r} = \frac{4}{(D + \sqrt{D^2 + \frac{8L_2}{R_r T_r}})^2} \cdot \frac{2\pi}{\eta} \frac{L_1}{n^2 R_L T_r}$$

(4-4)

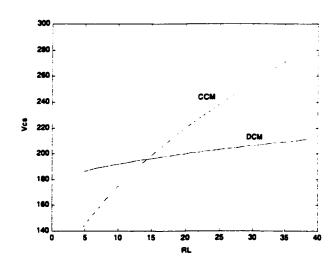

Thereafter the DC-bus voltage in different operation modes can be derived from the above analysis. Fig. 4-8 shows a design example, in which Vcs are given under different R<sub>L</sub> in two operation modes.

Critical value for L<sub>1</sub> and L<sub>2</sub> are also given as following:

For L<sub>1</sub>, because at critical point,  $m_1 = \frac{1}{1-D}$

And due to

$$\frac{V_0}{V_{in}} = \frac{V_0}{V_{ci}} \cdot \frac{V_{ci}}{V_{in}} = \frac{m_2}{1 - D}$$

So from expression (1), we can get:

$$k = \left(\frac{2}{\sqrt{D(2-D)}} \left(\frac{\pi}{2} + actg \frac{1-D}{\sqrt{D(2-D)}}\right) - \pi - 2(1-D)\right) \cdot \frac{\eta D^2}{\pi m_2^2}$$

(4-5)

$(\eta = 0.75, f_s = 500 \text{KHz}, L_1 = 30 \text{uH}, L_2 = 10 \text{uH}, D = 0.3, n = 3)$

Fig 4-8 Calculated curve of Vcs versus R<sub>L</sub>

For L<sub>2</sub>,

From

$$I_{L2,avg} = \frac{nV_{cs} - V_0}{2L_2}DT_s = \frac{V_0}{R_L}$$

And critical operation condition,  $V_0 = D \cdot nT$ ,

$$k = \frac{2L}{R_L T_s} = \frac{(1 - D)nV_{cs}}{nV_{cs}} = 1 - D \tag{4-6}$$

From the analysis above, it's not difficult to conclude such operation conditions need fine tuned parameters, and therefore, also impractical in quantity manufacturing.

## 4.5 Voltage Clamping Scheme

## 4.5.1 Conceptual Overview

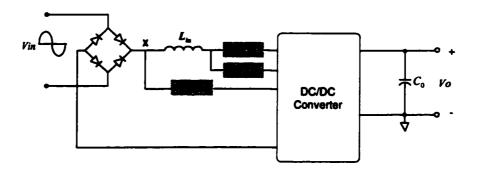

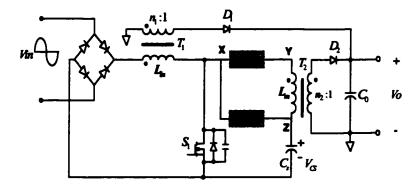

Shown in Fig. 4-9 is the configuration of a Fly-boost PFC AC-DC converter, using a Flyback transformer replace the traditional boost inductor in a generalized S<sup>2</sup> PFC AC-DC scheme with a three-terminal cell or two-terminal cell.

(a) Three-terminal scheme

(b) Two-terminal scheme

Fig. 4-9 Voltage claming PFC scheme with flyboost transformer

During the ON interval, the proposed scheme works in the same mode as previous approaches: Flyback transformer acts as a traditional boost inductor, and energy in storage capacitor  $C_i$  is discharged through the DC-DC conversion cell.

During the OFF interval, due to the huge capacitance of the output capacitor, the primary voltage of the Flyback transformer  $T_1$  is clamped to  $n_1V_0$ . Therefore,

For a single-stage PFC scheme with a three-terminal cell, as shown in Fig. 4-9(a),

$$V_X \le V_{in} + n_1 V_0 \tag{4-7}$$

$$V_z \le V_X \tag{4-8}$$

For a single-stage PFC scheme with a two-terminal cell, as shown in Fig. 4-9(b),

$$V_{\chi} \le V_{\mu} + n_1 V_0 \tag{4-9}$$

$$V_Z \le V_X - n_2 V_0 = V_X + (n_1 - n_2) V_0 \tag{4-10}$$

Therefore, theoretically, for both three-terminal schemes and two-terminal schemes, the introduction of a flyback transformer brings about inherent voltage clamping capability for the bulk capacitor.

Comparing the voltage expression in (4-8) and (4-10), an exciting case came up here. In schemes with a two-terminal cell,  $v_z$  can be designed to any desired value by properly choosing  $n_1$  and  $n_2$ , which are turn ratios of transformers  $T_1$  and  $T_2$ , respectively.

In Fig. 4-9(b), after merging the charging and discharging path, a bi-directional DC-DC cell with an input Flyback transformer constitutes the simplest configuration, as shown in Fig. 4-10. In practical applications, the voltage across the bulk capacitor should be higher than the input voltage from the view of demagnetizing of the input Flyback transformer. Therefore, a forward diode from the bridge rectifier is connected straight to the positive terminal of the bulk capacitor, keeping its voltage always above the input voltage to obtain the minimum input current distortion, as shown in Fig. 4-10.

Fig. 4-10 Proposed PFC AC-DC Configuration

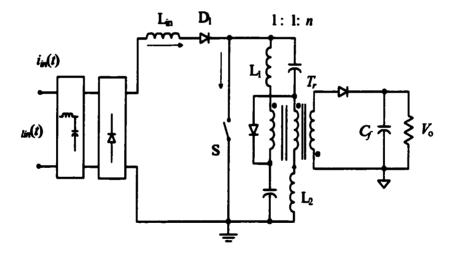

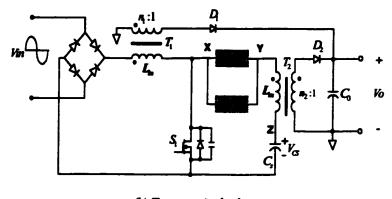

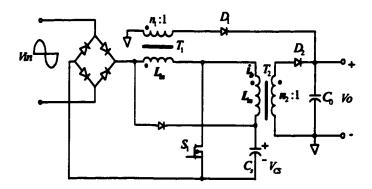

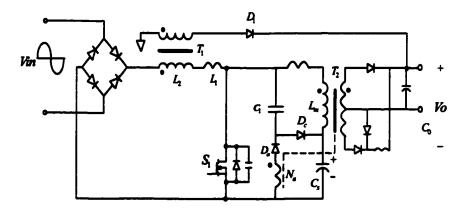

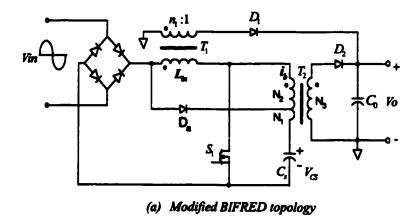

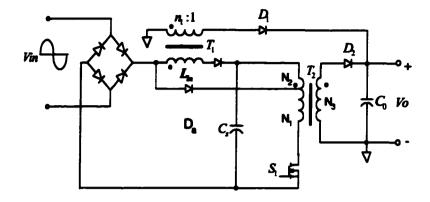

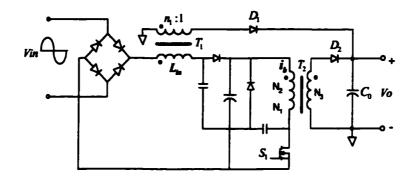

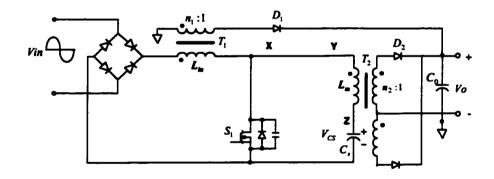

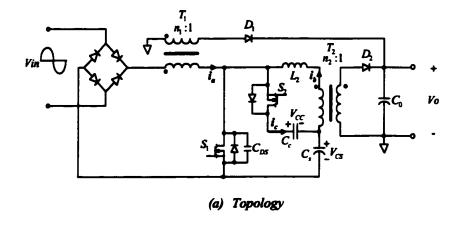

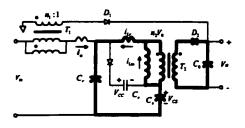

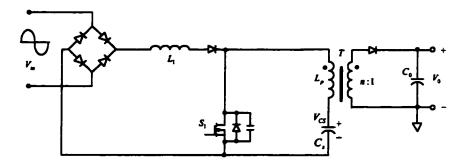

#### 4.5.2 Proposed Practical Cost-effective Topology

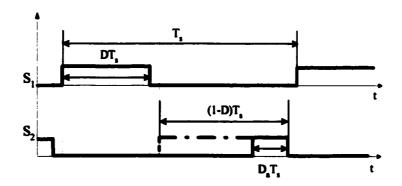

The practical  $S^2$  PFC AC-DC converter, as shown in Figure 4-11(a), basically is derived from the topology as shown in Fig. 4-10. The input PFC inductor is replaced with a Flyback transformer  $T_1$  and a small boost inductor  $L_1$ , in practical applications.  $L_1$  can be designed as the leakage inductance of transformer  $T_1$ . An additional winding  $N_a$  of DC-DC transformer  $T_2$  and a small capacitor  $C_1$  are introduced to constitute a lossless snubber, to reduce the main switch turn-off spike resulted from the leakage inductances.

Fig. 4-11 Proposed Topology

#### 4.5.3 Operation Principle and Basic Relationship

## 4.5.3.1 Operation Principle

The circuit operation will be discussed for one arbitrarily chosen switching cycle Ts, and under assumption that all components are ideal. And to simplify the analysis, lossless snubber branch constituted by  $C_1$ ,  $N_a$ ,  $D_c$  and  $D_a$ , is also neglected here.

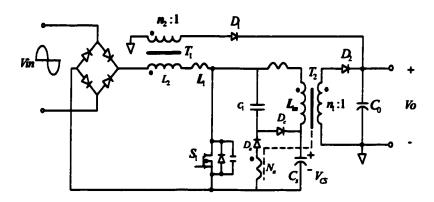

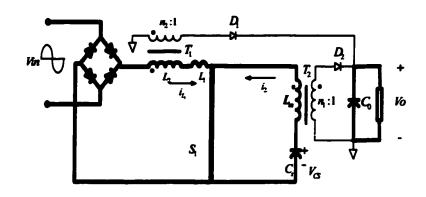

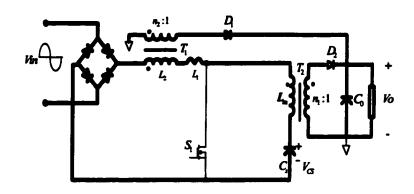

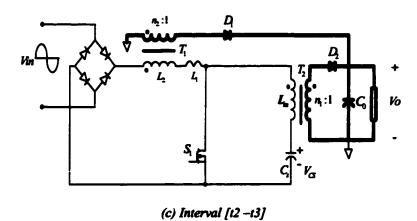

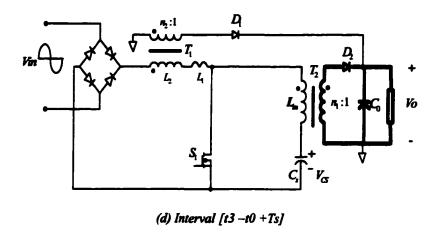

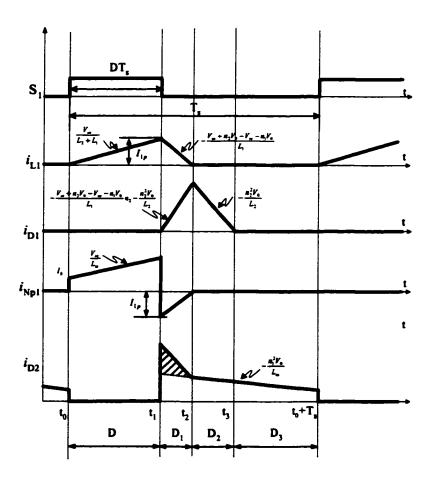

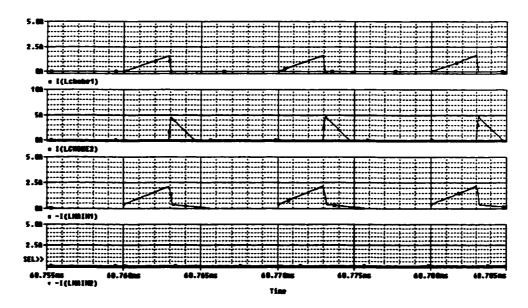

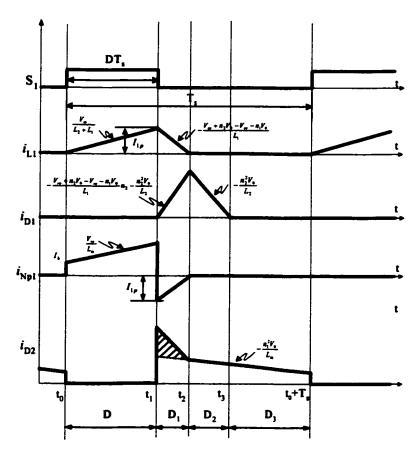

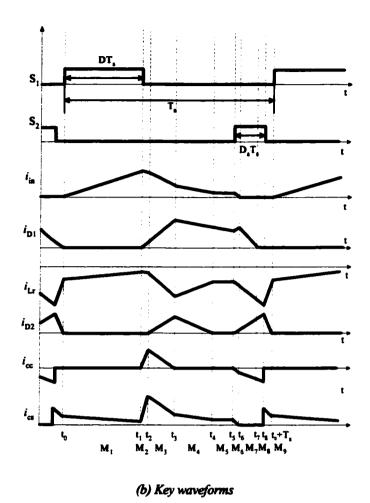

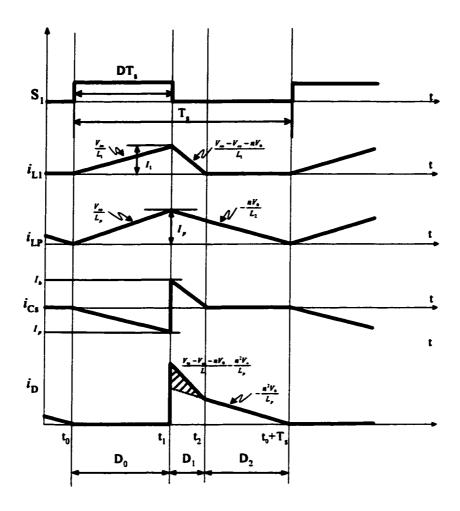

The switching cycle Ts is divided into four intervals corresponding to different circuits shown in Fig. 4-12 (a)-(d). The key waveforms are shown in Fig. 4-13.

(a) Interval [t0-t1]

(b) Interval [t1 -t2]

Fig. 4-12 Operation Modes of four intervals in one switching cycle

Fig. 4-13 Idealized Key waveforms in one switching cycle

Interval 1 [t0-t1]: At t0, the active switch is turned ON, the input voltage Vin is applied to the Flyback transformer  $T_1$  and inductor  $L_1$ , and the current  $i_{L_1}$  starts to build up linearly from zero. At the same time, the intermediate capacitor voltage  $V_{cr}$  is applied to the primary winding of transformer  $T_2$ , which also resulted in its current increase linearly.

Interval 2 [t1~t2]: When the switch is turned OFF at t1, the current  $i_{L_1}$  begins to flow through the primary winding of transformer  $T_2$ . The energy stored in the Flyback transformers  $T_1$  and  $T_2$  start to be discharged to the output. This interval ends at t2 when  $i_L$  reaches zero.

Interval 3 [t2~t3]: From moment t2, the current flowing through  $D_2$  decreases linearly with a slope  $\frac{n_1^2V_0}{L_m}$ ; and also the current flowing through  $D_1$  decays with the slope  $\frac{n_2^2V_0}{L_2}$  until it reaches zero at t3.

Interval 4 [t3~t0+Ts]: The current flowing through  $D_2$  keeps gradually decreasing with a slope  $\frac{n_1^2V_0}{L_m}$  until the switch is turned ON, starting another switching cycle at t0+Ts.

Based on the above basic operation, we can formulate some basic equations. It can be shown that the average value of the input current  $i_{L_i}$ , denoted as  $\bar{i}_{L_i}$ , over the switching cycle Ts is given by:

$$\bar{i}_{L1} = \frac{D + D_1}{2} I_p = \frac{D + D_1}{2} \frac{|V_{tt}|}{L_1 + L_2} DT_z$$

(4-11)

where the duty ratio  $D_i$  can be found from the voltage balance on  $L_i$  as:

$$D_1 = \frac{L_1 |V_{in}| D}{(V_{cr} + n_1 V_0 - n_2 V_0 - |V_{in}|)(L_1 + L_2)}$$

(4-12)

Combining Eqs. (4-11) and (4-12) and by letting:

$$A = V_{cs} + n_1 V_0 - n_2 V_0 - |V_{in}|, m = \frac{L_2}{L_1}$$

and,

$|V_{in}| = \sqrt{2}V_{max}|\sin\theta|$ ,  $\bar{i}_{L_1}$  can be rearranged as:

$$\bar{i}_{L1} = \frac{D^2 |V_{in}| T_s}{2L_1(1+m)} (1 + \frac{|V_{in}|}{A(1+m)}) \tag{4-13}$$

Similarly the average value of the output current  $i_{D_i}$  over Ts can be found from:

$$\bar{i}_{D_1} = \frac{D_1 + D_2}{2} I_{p2} = \frac{D_1 + D_2}{2} n_2 \frac{(mA - n_2 V_0) D T_s V_{in}}{A m (1 + m) L_1}$$

(4-14)

where  $D_2$  can be found from:

$$D_2 = \frac{mA - n_2 V_0}{n_2 V_0} D_1 \tag{4-15}$$

Combining Eqs. (4-12), (4-14) and (4-15),  $\bar{i}_{D_i}$  can be rearranged as:

$$\bar{i}_{D_1} = \frac{\left|V_{in}\right|^2 D^2 T_s}{2A(1+m)^2 L_1} \frac{(mA - n_2 V_0)}{V_0} \tag{4-16}$$

To implement a commercially available capacitor and its related voltage rating components, now take the voltage across the bulk capacitor as a design parameter. The averaged bulk capacitor charging current over Ts can be expressed as:

$$\bar{l}_{ch\,seg\,e} = \frac{1}{2} D_{l} I_{p} = \frac{\left|V_{in}\right|^{2} D^{2} T_{s}}{2 A L_{l} (1+m)^{2}} \tag{4-17}$$

And discharging current can be found by subtracting the current flowing in  $D_1$  and the shadowed current of  $D_2$  in Fig. 4-12 from the load current to yield,

$$\bar{i}_{disch \, \text{arg } e} = \frac{D}{n_1} \left( \frac{P_0}{V_0} - \bar{i}_{D_1} - i'_{D_2} \right) = \frac{D}{n_1} \left( \frac{P_0}{V_0} - \frac{\left| V_{in} \right|^2 D^2 T_s (mA - n_2 V_0)}{2A(1+m)^2 L_i V_0} - \frac{n_1 \left| V_{in} \right|^2 D^2 T_s}{2A(1+m)^2 L_1}$$

$$(4-18)$$

In steady state, over half a line cycle, the net charging current for the bulk capacitor should be zero, thus:

$$\int_{0}^{\pi} \bar{i}_{ch\,\text{trg}\,e} d\theta = \int_{0}^{\pi} \bar{i}_{disch\,\text{trg}\,e} d\theta \tag{4-19}$$

From Eqs. (4-17), (4-18) and (4-19), we obtain the following equation:

$$\int_{0}^{\pi} \left( \frac{D^{2}T_{s}}{2AL_{1}(1+m)^{2}} \left( 1 + \frac{D}{n_{1}} \frac{(Am - n_{2}V_{0})}{V_{0}} + D \right) |V_{in}|^{2} - \frac{DP_{0}}{n_{1}V_{0}} \right) d\theta = 0$$

(4-20)

where  $P_0$  is the output power, since input power is equal to the output power, so:

$$P_{0} = P_{in} = \frac{1}{\pi} \int_{0}^{\pi} \vec{i}_{L1} |V_{in}| d\theta$$

$$= \frac{1}{\pi} \int_{0}^{\pi} \frac{D^{2}T_{z}}{2L(1+m)} (1 + \frac{|V_{in}|}{A(1+m)}) |V_{in}|^{2} d\theta$$

(4-21)

Combining Eqs. (4-20) and (4-21) to yield the following transcendental equation set:

$$\int_{0}^{\pi} (1 + \frac{n_{1}V_{0} - DV_{cs}}{D(V_{cs} + (n_{1} - n_{2})V_{0})(1 + m) - \sqrt{2}mV_{max}\sin\theta})d\theta = 1$$

$$\int_{0}^{\pi} \frac{V_{min}^{2} D^{2} T_{s} \sin^{2} \theta}{L_{1}(1+m)} \left(1 + \frac{\sqrt{2} V_{min} \sin \theta}{(1+m)(V_{c1} + (n_{1} - n_{2})V_{0} - \sqrt{2} V_{min} \sin \theta}) d\theta = \pi P_{0}$$

(4-22)

That allows us to find numerically the voltage across the bulk capacitor as a function of the rms value of input voltage and the output voltage  $V_0$  as well as turn ratios  $n_1$ ,  $n_2$  and  $m = \frac{L_2}{L}$ .

#### 4.5.3.2 DCM operation of PFC cell

As explained in the modes analysis, if Flyback transformer  $T_1$  is not completely reset during the OFF state of the main switch, the distortion of the line current will dramatically increase. In other words, to obtain a line current close to a sinusoidal waveform under entire line and load conditions, the diode current  $i_{D_1}$  should be decreased to zero before the main switch conducts. Since the worst case happens at a full load and minimum line voltage, the DCM condition of  $i_{D_1}$  can be found from Fig. 4-13:

$$D_1 + D_2 \le 1 - D_{max}$$

(4-23)

From (4-12) and (4-15), (4-23) can be derived as:

$$D_{\max}(\frac{m|V_{\min}|}{n_2V_0(1+m)}+1) \le 1 \tag{4-24}$$

Therefore, the maximum duty ratio must be designed to meet (4-24) to guarantee no serious input current distortion happens under any case.

#### **Topology Features**

From the above analysis, we can summarize the features of the proposed topology:

- Reduced voltage stress: Inserting a Flyback transformer to the traditional input inductor brings about inherent voltage clamping capability across its primary when the switch is OFF. Besides, the storage capacitor is always charged through the transformer T₂, therefore, if L₁ is much smaller than L₂, the storage capacitor is charged in an apparent controlled mode, V₂ ≤ V₂ + (n₂ n₁)V₀. Properly selected n₁, n₂ and m can guarantee the DC-bus voltage well above the peak value of the input voltage. As a consequence, the commercially available capacitor can be used, and moreover, 600V components can be used in the power stage for universal input applications.

- 2. Higher efficiency: In Fig. 4-12, the current flowing through  $D_1$  and the shadowed portion of  $D_2$  is directly delivered to the output through  $T_1$  and  $T_2$  without storing in  $C_1$  first. Therefore, a lion share power was transferred to the load without being processed twice. The overall conversion efficiency can be improved consequently. For the currently existing cascade two-stage or single-stage approaches, basically, the power is processed serially by PFC cell and DC-DC cell, and the overall efficiency is given by the product of two stage efficiencies,

i.e.,  $\eta = \eta_1 \eta_2$ , where  $\eta_1$  and  $\eta_2$  are the efficiencies of two stages respectively. In the proposed topology, supposing k is the ratio at which power is transferred to the output just through the PFC stage, then, the efficiency of the proposed structure can be expressed as  $\eta = k\eta_1 + (1-k)\eta_1\eta_2 > \eta_1\eta_2$ . Obviously the overall efficiency can be improved by minimizing the power process times. In addition, reduced current stress also brings about higher efficiency due to reduced turn off losses.

- 3. Reduced current stress: It can be shown from  $i_{D_1}$  in Fig. 4-12, that the existence of interval  $D_2$  will decrease the duty cycle when line voltage nears its peak value, and thus can effectively reduce the peak value of input current when transferring the same average input current. Therefore, the main switch can be turned OFF under reduced current stress.

- 4. Low turn off spikes: The snubber capacitor  $C_1$  can effectively suppress the turn off spikes of the main switch, and in each switching cycle, its stored energy can also be released to the output through the coupling winding at the moment of the main switch being turn ON.

- 5. High power application potential: Two Flyback transformer configuration has the potential to increase the power conversion rating and also release the thermal design difficulties due to distributed heat dissipation.

In addition, reduced cost and improved reliability due to least components are also preferred in practical applications.

## 4.5.4 Simulation and Experimental Results

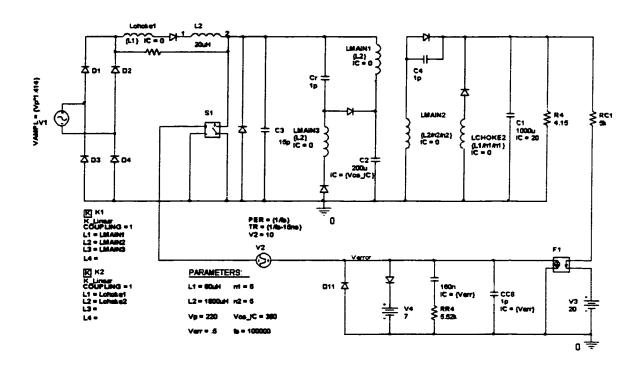

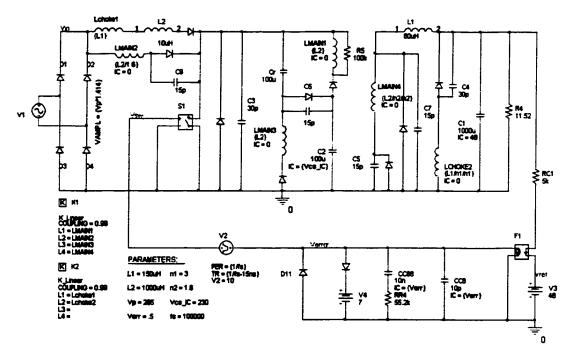

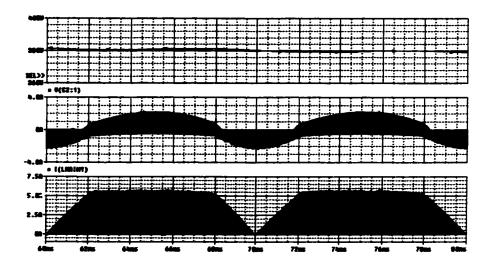

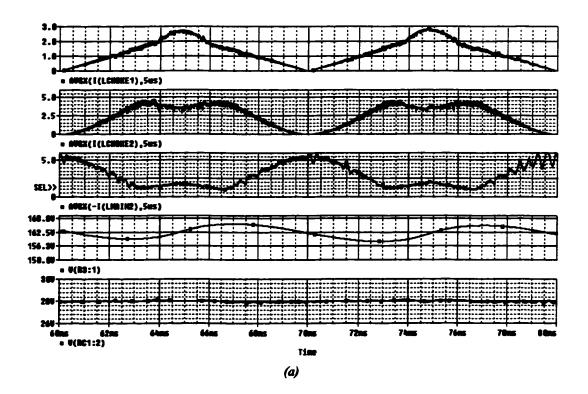

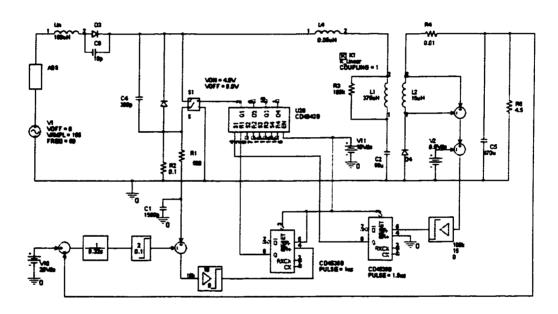

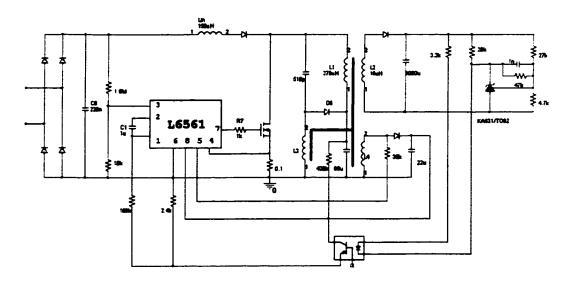

In order to verify the above analysis, a 20V@4.5A PSPICE closed loop simulation circuit is built up as shown as Fig. 4-14.

Fig. 4-14 Simulation Schematics

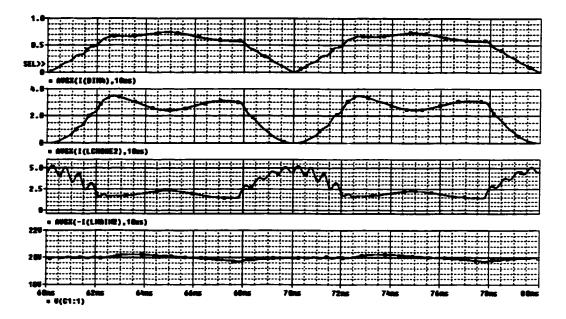

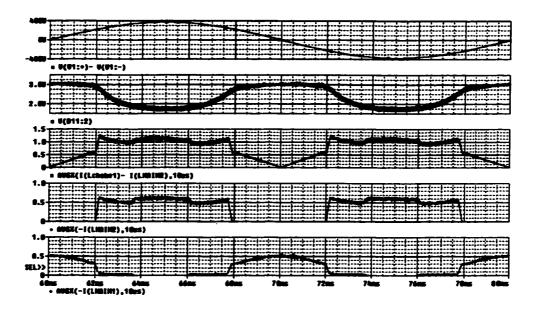

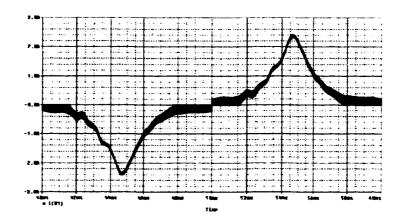

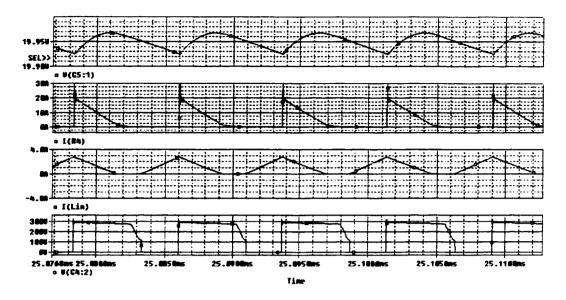

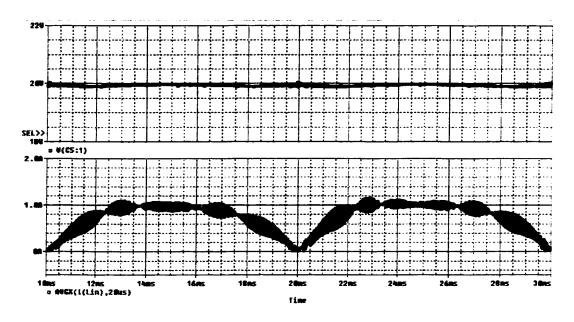

Figure 4-15 presents the simulation results for the proposed topology. Figure 4-15(a) gives the simulated key waveforms in one line cycle:

The first trace shows the rectified input current, which is nearly sinusoidal waveform with lower crest value. It should be noted here that the practical waveform would be better since the input filter has not been implemented in front of the presented simulation scheme.

The second trace indicates the current transferred to the output through T1, resulting in more than 50% energy delivered to the output directly without being processed twice, as previous approaches did.

The third trace indicates current transferred to the output through T2, which just fills the valley of the second current trace to pursue the trade-off between the high power factor and low output ripple; It also can be seen only a small output portion powered by the buffer capacitors.

The last trace gives the output voltage to indicate the proposed power conversion scheme can obtain pretty small output ripple with near unity power factor.

Figures 4-15(b) and (c) show the current flowing through the primary and secondary windings of two transformers in one switching cycle for the input line across zero and near peak value, respectively. It can be found that the waveforms agree well with the above analysis. For the bulk capacitor, in half a line cycle, it exhibits net discharge performance in one switching cycle around line voltage across zero, and net charge performance near line voltage near the peak.

- First trace: Rectified input current;

- Second trace: Current transferred to the output through T1;

- Third trace: Current transferred to the output through T2;

- Fourth trace: Output Voltage

- (a) Simulated waveforms over one line cycle

(b) Windings current around line voltage across zero

(c) Windings current around line voltage near the input peak value

Fig. 4-15 Simulation results

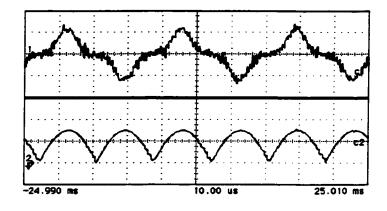

A 90~265V/60Hz input, 20V@4.5A output prototype was built to experimentally verify the proposed scheme, as shown in Fig. 4-16. The following key components were implemented in the experimental circuit: Flyback transformer T1: n2=4.1/L2=80uH/L1=23uH; DC-DC transformer T2: Np:Ns:Na = 4.1:1:4.1; Switches—S1: IRF9N65; Storage Capacitor — 100uF/450V; Clamp capacitor — 4.7n; Boost Diode — DSEI 806A; Secondary rectifier diode D1, D2 — 10CT150; Switching frequency — 100kHz.

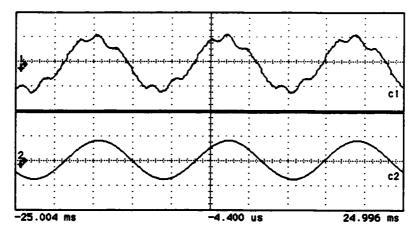

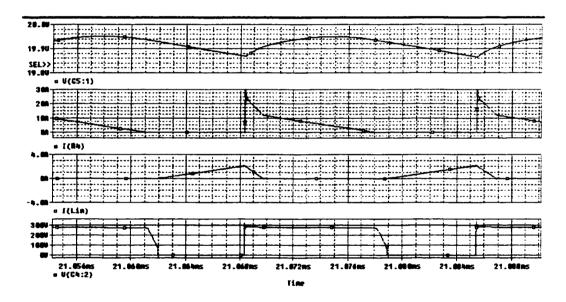

Figure 4-17 presents the waveforms under full load and nominal input (110V/60Hz) condition. The upper trace indicates the prototype achieved near sinusoidal input current waveform.

Fig. 4-16 Universal input 20V@4.5A Adapter prototype

Fig. 4-17 Measured line current and voltage

Figures 4-18 and 4-19 present the full load efficiency and power factor under different input voltage, respectively. The results indicate the efficiency stays above 81% and the Power Factor of the developed prototype stays above 0.95 through the entire

input range. Figure 4-20 indicates the DC bus voltage is well below 400V through the universal input range, which makes the commercial available capacitor practical in this adapter.

Fig. 4-18 Measured power factor vs. line voltage under full load

Fig. 4-19 Measured efficiency vs. line voltage under full load

Fig. 4-20 Maximum voltage vs. line voltage under full load

#### 4.5.5 Topology Derivation

The DC-DC transformer in the proposed topology can also be designed to have another forward winding, as shown in Fig. 4-21. The modified topology can reduce the secondary current stress and further improve the conversion efficiency, in addition to still keeping the inherent DC-bus voltage claming capability.

Fig. 4-21 Topology derivation

## 4.6 Summary

This chapter first analyzes the mechanism of high intermediate DC-bus voltage, and after briefing existing stress-alleviating approaches, a simple inherent voltage clamping scheme for S<sup>2</sup> PFC AC-DC conversion is introduced. A practical application topology was proposed, analyzed and used to experimentally validate the concept.

#### 5. CURRENT STRESS ALLEVIATING APPROACHES

#### 5.1 Introduction

The PFC stage in an S<sup>2</sup> PFC AC-DC converter normally operates in DCM mode to utilize its inherent current-shaping capability. Therefore, compared with cascading two-stage schemes, S<sup>2</sup> PFC AC-DC conversion has higher current stress. Current stress not only accompanies with increased switching losses and lower efficiency, but also brings about annoying EMI issues. Pursuing a current alleviating scheme will "kill two birds with one stone" to increase the power conversion efficiency, and help to release the pressure of the S<sup>2</sup> PFC AC-DC converter EMI filter design.

As stated in the first chapter, it is not necessary to achieve sinusoidal input current waveform to meet the regulations. Non-sinusoidal approach sometimes is a better choice in terms of performance and cost. In this chapter, three near sinusoidal input current approaches are introduced to alleviate current stress, thereafter to pursue the better trade-off quality-cost performance.

### 5.2 Peak Value Clamping Technique

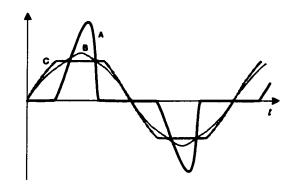

Figure 5-1 shows three different types of line current waveforms with various distortions. It is known that waveform A exists in traditional converters composed of a diode bridge and a filter capacitor. This waveform fails to meet the regulations due to its high harmonic current. Whereas, the sinusoidal waveform B represents the ideal case that