# Flyboost derived single stage power factor correction converter

*ProQuest Dissertations and Theses*; 2003; ProQuest Dissertations & Theses (PQDT) pg. n/a

# FLYBOOST DERIVED SINGLE STAGE POWER FACTOR CORRECTION CONVERTER

By

WEIHONG QIU

B.S. University of Xiangtan, 1991

M.S. University of Nanjing Aeronautics & Astronautics, 1994

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer science at the University of Central Florida

Orlando, Florida

Summer Term 2003

Major professor: Issa Batarseh

UMI Number: 3094814

## UMI Microform 3094814

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# **ABSTRACT**

Power Factor Correction (PFC) scheme is necessary for lots of electric equipment with AC input as power source to meet the harmonic requirement of several standards. By integrating a PFC cell with a DC-DC conversion cell, single stage PFC scheme is attractive to low power application because of its low component count and low cost. But, typical single stage PFC converters suffer from high voltage and high current stresses, which block their way to practical applications.

Flyboost-derived single stage PFC converter can transfer input power directly to output end with portion of input power proceeded by the active switch only once. And the intermediate bus voltage is also automatically limited to specific value determined by circuit parameters. So this scheme can reduce the voltage and current stresses on power components, and better performance can be achieved with low cost.

Lots of single-stage PFC converter schemes can be derived by integrating flyboost PFC circuit with basic DC-DC conversion circuits. Two good topologies were studies in detail to show advantages of this scheme. The operations of those topologies were discussed, and power flow analysis approach was implemented to obtain critical equations for practical design. Optimal design procedure was developed and verified by prototypes and experiments. Experimental results show their superiorities over counterpart single-stage PFC schemes. Low components count and good performance makes them suitable for low power low cost universal input application.

Considering the influence of leakage inductance of flyback transformer, the operation of non-ideal flyback circuit is very complex due to its several operational modes. Based on detailed operation analyses, one unified average Pspice model was developed for non-ideal flyback circuit, which is also suitable for flyboost PFC scheme. By combining this average model with average models of basic DC-DC converters, the average model for flyboost-derived single stage PFC converters were developed. This average model can reduce the total simulation time significantly. And one special simulation procedure was developed to perform AC small signal analysis for flyboost-derived PFC topologies. Simulation results show special characteristics of flyboost-derived topologies, which provide design guide for practical applications.

TO MY GRANDFATHER

iv

# **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to my advisor, Dr. Issa Batarseh, for his guidance, inspiration and support during the course of this work. I would not have been able to complete my research without his extensive knowledge and creative thoughts. Through his enthusiasm and personality, he also gained my most sincere admiration.

I also thank many of my collegues at UCF, Dr. Shiguo Luo, Dr. Wei Gu, and Dr. Wenkai Wu, Dr. Chris Iannello, Dr. Peter Kornetzky and Dr. Zaki Moussaoui for many enlightening discussions; Their invaluable suggestions were so helpful to my research.

My experience at UCF has been a great period in my life. I am grateful to have the chance to combine enjoyable education and productive research atmosphere through the dynamic group at UCF. I wish to thank my fellow researchers, Dr. Hong Mao, Khalid Krustom, Songquan Deng, Jia Luo, Jaber Abu Qahouq, Nattorn Pongratananukul, Enrique Tenicela, Joy Mazumdar and Duy Bui Quang for their help and cooperation.

And I would like to express my deep appreciation to Ms. Elizabeth Plaisted for her invaluable editing work of my dissertation.

Finally, my heartfelt appreciation goes to my parents and my wife for their love.

This work has been supported by an NSF grant, a NASA STTR research grant, and the University of Central Florida.

# **TABLE OF CONTENTS**

| LIS | ST O | F TABI     | LES X                                                          |  |

|-----|------|------------|----------------------------------------------------------------|--|

| LIS | ST O | F FIGU     | JRESXI                                                         |  |

| 1.  | INT  | RODUCTION1 |                                                                |  |

|     | 1.1  | Backgr     | round2                                                         |  |

|     |      | 1.1.1      | Conventional Power Factor Correction converter                 |  |

|     |      | 1.1.2      | Single stage Power Factor Correction converter                 |  |

|     |      | 1.1.3      | Key issues in single stage Power Factor Correction converter 7 |  |

|     |      | 1.1.4      | Intermediate bus voltage control8                              |  |

|     |      | 1.1.5      | Parallel power flow PFC converter                              |  |

|     |      | 1.1.6      | Average Model for switching mode power supply18                |  |

|     | 1.2  | Dissert    | tation Outline                                                 |  |

| 2.  | DIR  | ECT P      | OWER TRANSFER FLYBOOST PFC CELL21                              |  |

|     | 2.1  | Introdu    | action21                                                       |  |

|     | 2.2  | Flyboo     | ost-flyback single stage PFC                                   |  |

|     |      | 2.2.1      | Flyback Operational Mode Analysis25                            |  |

|     |      | 2.2.2      | Boost Operational Mode Analysis28                              |  |

|     | 2.3  | Power      | Flow Analysis                                                  |  |

|     |      | 2.3.1      | Flyback Mode Power Flow Analysis34                             |  |

|     |      | 2.3.2      | Boost Mode Power Flow Analysis                                 |  |

|    |     | 2.3.3 Final equation of Power Flow Analysis         | 37 |

|----|-----|-----------------------------------------------------|----|

|    |     | 2.3.4 Conditions fro DCM+CCM Operation              | 38 |

|    | 2.4 | Summary                                             | 41 |

| 3. | FLY | BOOST PARALLEL/SERIES FORWARD SINGLE STAGE PFC      |    |

|    | CO  | NVERTER                                             | 42 |

|    | 3.1 | Introduction                                        | 42 |

|    | 3.2 | Operation Description                               | 45 |

|    |     | 3.2.1 Flyback operation mode                        | 46 |

|    |     | 3.2.2 Boost operation mode                          | 49 |

|    | 3.3 | Steady-State Analysis                               | 50 |

|    |     | 3.3.1 Mode boundary                                 | 50 |

|    |     | 3.3.2 Condition for PFC cell under DCM              | 50 |

|    |     | 3.3.3 Intermediate bus voltage                      | 52 |

|    |     | 3.3.4 Features                                      | 62 |

|    | 3.4 | Practical Design Considerations                     | 63 |

|    |     | 3.4.1 Controller design                             | 63 |

|    |     | 3.4.2 Influence of transformers' leakage inductance | 65 |

|    |     | 3.4.3 Magnetizing inductance of T1 primary winding  | 68 |

|    |     | 3.4.4 Intermediate bus voltage                      | 69 |

|    |     | 3.4.5 DC/DC conversion cell                         | 69 |

|    | 3.5 | Design example                                      | 70 |

|    |     | 3.5.1 Determine the maximum duty cycle              | 70 |

|    |     | 3.5.2 Determine the minimum hus voltage at low line | 70 |

|          |               | 3.5.3 Design the parallel/Series forward DC-DC cell      | 71   |

|----------|---------------|----------------------------------------------------------|------|

|          |               | 3.5.4 Design the PFC transformer T1                      | 71   |

|          |               | 3.5.5 Check the maximum bus voltage at high line voltage | 73   |

|          | 3.6           | Experimental Verifications                               | 74   |

|          | 3.7           | Summary                                                  | 78   |

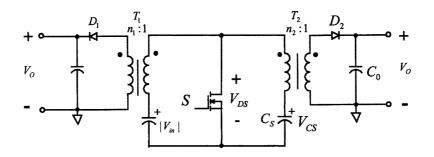

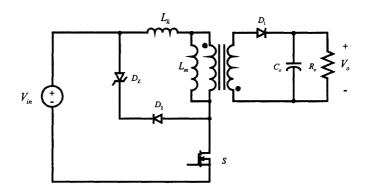

| 1.       | BI-I          | FLYBACK SINGLE STAGE PFC CONVERTER                       | 79   |

|          | 4.1           | Introduction                                             | 79   |

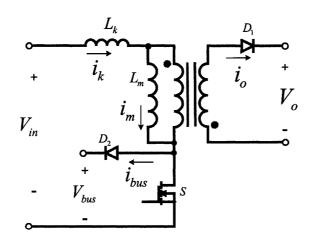

|          | 4.2           | Operation Descriptions                                   | 84   |

|          |               | 4.2.1 Flyback Mode Operation                             | 87   |

|          |               | 4.2.2 Boost Mode Operation                               | . 91 |

|          | 4.3           | Steady State Analyses                                    | 95   |

|          |               | 4.3.1 Mode Boundary                                      | . 95 |

|          |               | 4.3.2 Stead-State Equation for Intermediate Bus Voltage  | . 96 |

|          |               | 4.3.3 Condition for PFC cell in DCM                      | 109  |

|          |               | 4.3.4 Features of Bi-flyback topology                    | 110  |

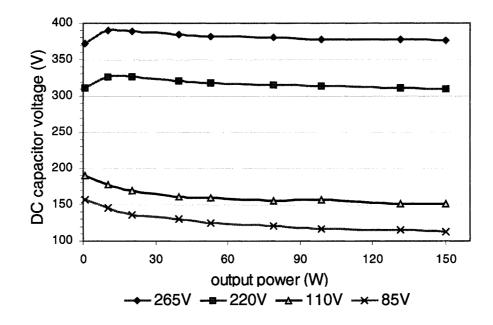

|          | 4.4           | Experimental results                                     | 111  |

|          | 4.5           | Summary                                                  | 117  |

| 5.       | CO            | NTROL APPROACHES FOR BI-FLYBACK CONVERTER                | 118  |

|          | 5.1           | Introduction                                             | 118  |

|          | 5.2           | Valley switching control approach                        | 122  |

|          | 5.3           | Experimental Verification                                | 130  |

|          | 5.4           | Summary                                                  | 133  |

| <b>`</b> | <b>Δ \</b> /1 | FRAGE MODEL OF ELVROOST PEC CIRCUIT                      | 134  |

|    | 6.1  | Introdu | ection                                                        |

|----|------|---------|---------------------------------------------------------------|

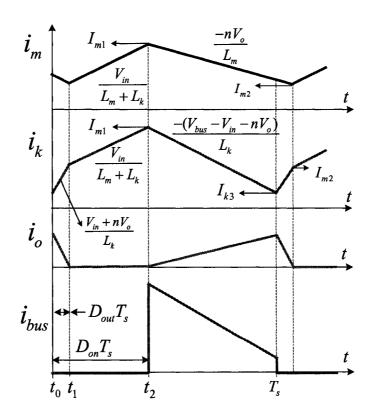

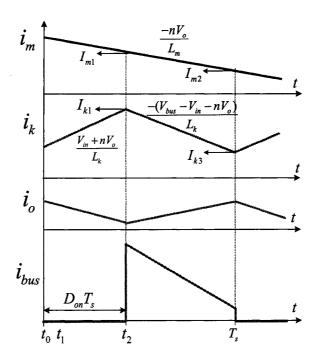

|    | 6.2  | Operati | ion analysis of non-ideal flyback circuit                     |

|    |      | 6.2.1 I | Flyback DCM+DCM                                               |

|    |      | 6.2.2 H | Flyback CCM+DCM141                                            |

|    |      | 6.2.3 H | Flyback CCM+CCM                                               |

|    |      | 6.2.4 H | Boost DCM+DCM                                                 |

|    |      | 6.2.5 H | Boost CCM+CCM                                                 |

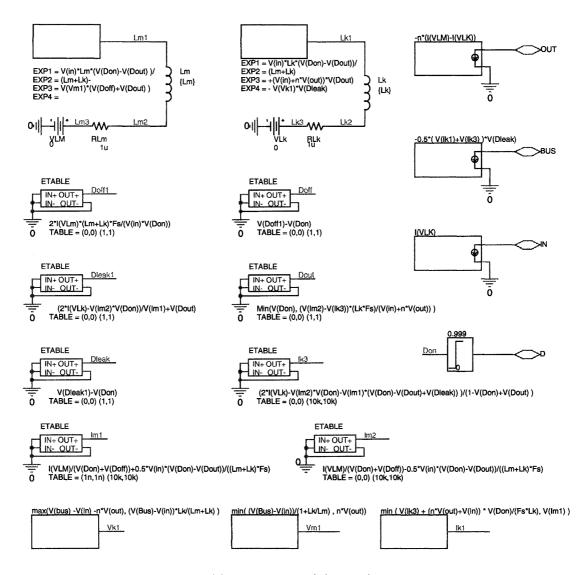

|    | 6.3  | Averag  | e model for non-ideal flyback circuit                         |

|    | 6.4  | Validat | ion of Average model for non-ideal flyback circuit            |

|    |      | 6.4.1 V | Verification of DC analysis by switching Pspice model 162     |

|    |      | 6.4.2 V | Verification of AC analysis by SIMPLIS166                     |

|    | 6.5  | Averag  | e model for Flyboost-parallel/series forward single stage PFC |

|    |      | convert | rer                                                           |

|    |      | 6.5.1 I | Derivation of the average model                               |

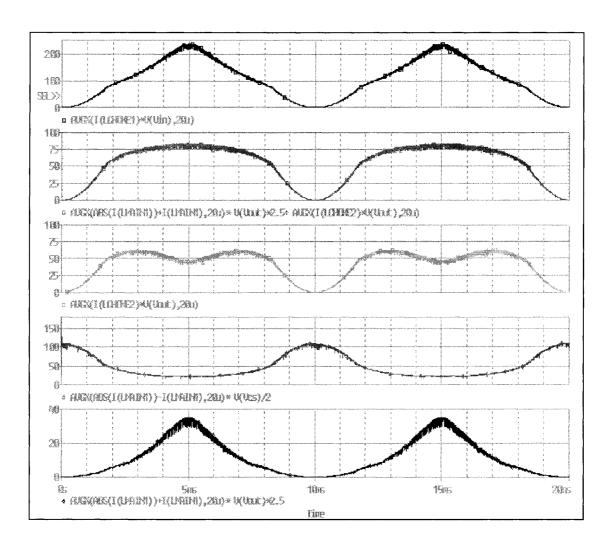

|    |      | 6.5.2 I | OC operation analysis by the average model                    |

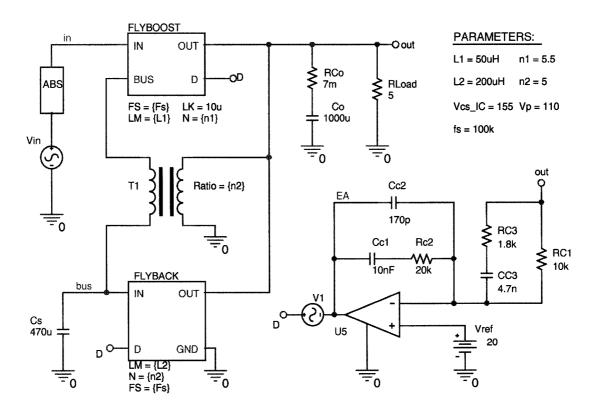

|    |      | 6.5.3 A | AC analysis by the average model                              |

|    | 6.6  | Averag  | e model for Bi-flyback single stage PFC converter 186         |

|    |      | 6.6.1 I | Derivation of the average model                               |

|    |      | 6.6.2 I | OC operation analysis by the average model                    |

|    |      | 6.6.3 A | AC analysis by the average model                              |

|    | 6.7  | Summa   | ry194                                                         |

| 7. | CO   | NCLUS!  | ION195                                                        |

| LI | ST O | F REFE  | RENCES                                                        |

# LIST OF TABLES

| Table 4.1 Measured bus voltage (Volts) at different operation condition116 |

|----------------------------------------------------------------------------|

| Table 4.2 Experimental results of Bi-flyback topology116                   |

# LIST OF FIGURES

| Fig. 1-1 | Two-stage PFC converter                                                  | .4         |

|----------|--------------------------------------------------------------------------|------------|

| Fig. 1-2 | Single stage PFC converter                                               | .4         |

| Fig. 1-3 | Current waveform at different mode                                       | .4         |

| Fig. 1-4 | Blocking cell in boost inductor path to reduce intermediate bus voltage1 | . 1        |

| Fig. 1-5 | Input power waveform for unity power factor                              | .4         |

| Fig. 1-6 | Power flow chart1                                                        | .6         |

| Fig. 2-1 | Flyboost PFC cell                                                        | :2         |

| Fig. 2-2 | An example of Flyboost PFC circuit                                       | 23         |

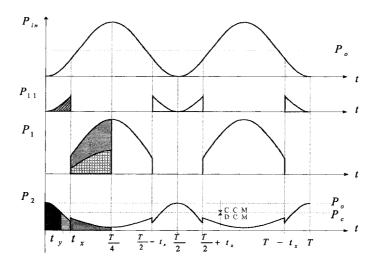

| Fig. 2-3 | Operation mode of Flyboost PFC cell in one line frequency cycle2         | <u>'</u> 4 |

| Fig. 2-4 | Operation of flyback mode                                                | 26         |

| Fig. 2-5 | Operation of flyback mode                                                | !9         |

| Fig. 2-6 | Operational waveform in one line cycle by simulation                     | 1          |

| Fig. 2-7 | Power flow map of flyback-flyback topology3                              | 3          |

| Fig. 3-1 | Russian single stage PFC converter4                                      | ŀ3         |

| Fig. 3-2 | Flyboost-parallel/series forward single stage PFC converter4             | l4         |

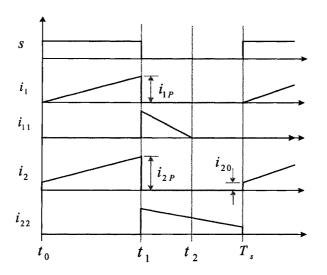

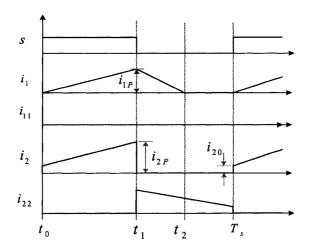

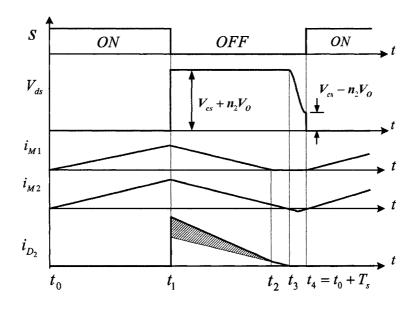

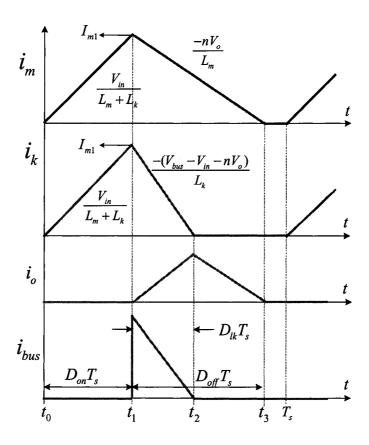

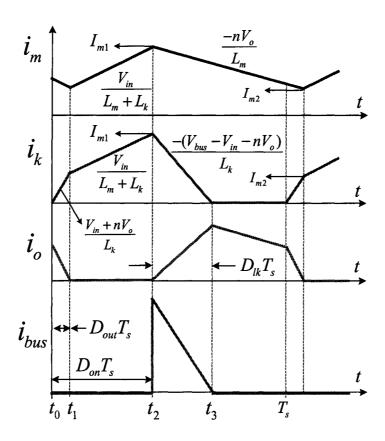

| Fig. 3-3 | Operation mode and waveforms4                                            | 18         |

| Fig. 3-4 | MathCAD sheet for intermediate bus voltage under CCM                     | 56         |

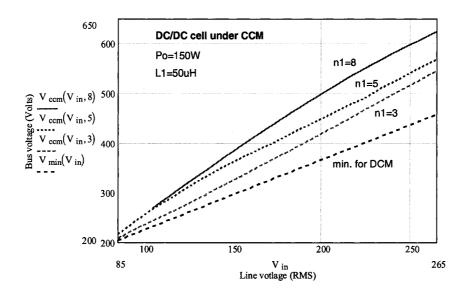

| Fig. 3-5 | Bus voltage Vs Line voltage with DC/DC cell under CCM5                   | 57         |

| Fig. 3-6 | MathCAD sheet for intermediate bus voltage under DCM                     | 58         |

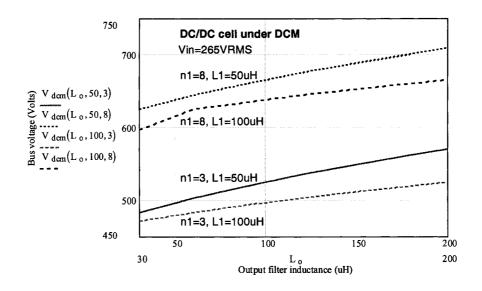

| Fig. 3-7  | Bus voltage Vs output inductance with DC/DC cell under DCM        | 59  |

|-----------|-------------------------------------------------------------------|-----|

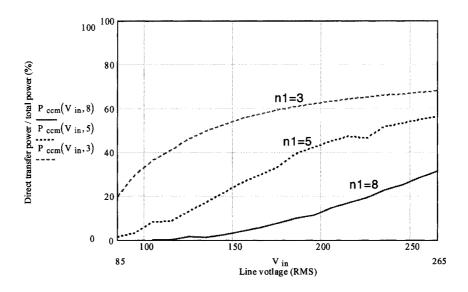

| Fig. 3-8  | MathCAD sheet for direct transferred power                        | 60  |

| Fig. 3-9  | Direct transferred power percentage over input voltage            | 61  |

| Fig. 3-10 | Parallel power transfer                                           | 64  |

| Fig. 3-11 | Influence of leakage inductance of PFC transformer T <sub>1</sub> | 66  |

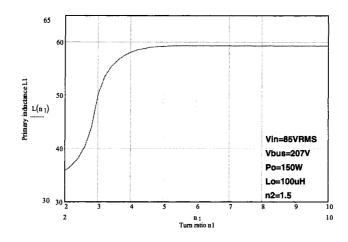

| Fig. 3-12 | MathCAD sheet for interrelationship between $L_1$ and $n_1$       | 72  |

| Fig. 3-13 | Interrelationship between $L_1$ and $n_1$                         | 73  |

| Fig. 3-14 | Prototype based on the flyboost parallel/series forward converter | 75  |

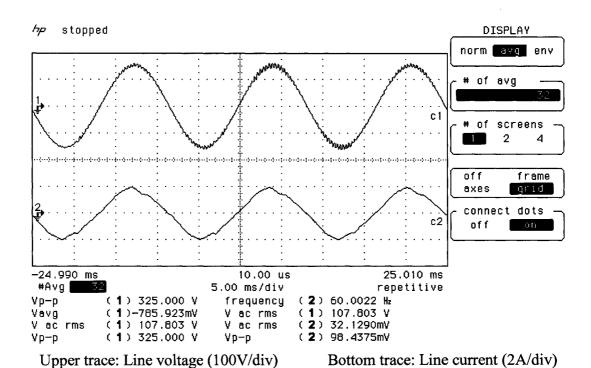

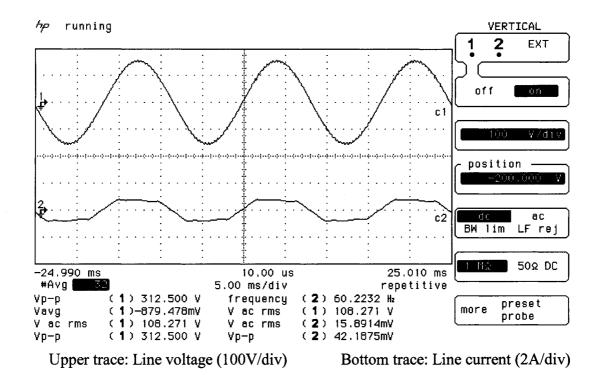

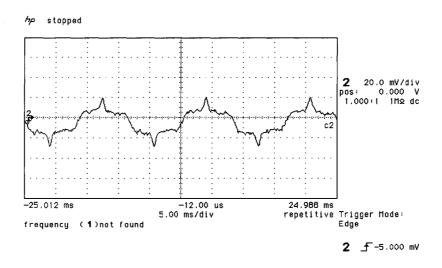

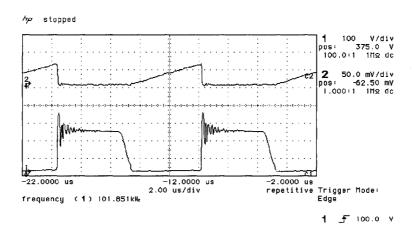

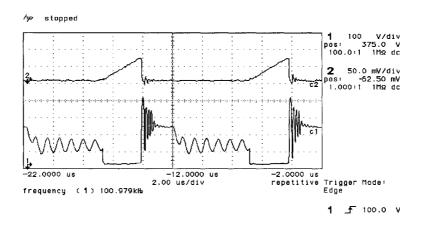

| Fig. 3-15 | Measured waveform at 110V AC input and 150W output                | 75  |

| Fig. 3-16 | Measured waveform at 110V AC input and 150W output                | 76  |

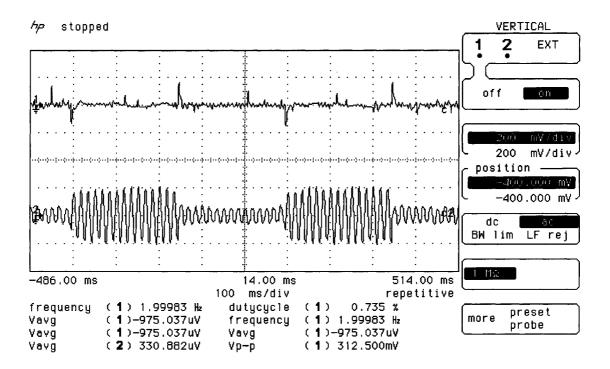

| Fig. 3-17 | Dynamic load testing                                              | 77  |

| Fig. 4-1  | Bifred topology for single stage PFC applications                 | 82  |

| Fig. 4-2  | Bi-flyback topology                                               | 83  |

| Fig. 4-3  | Operation mode in one line cycle                                  | 86  |

| Fig. 4-4  | Operation of flyback mode                                         | 88  |

| Fig. 4-5  | Operation of boost mode                                           | 93  |

| Fig. 4-6  | Power flow over a line period                                     | 97  |

| Fig. 4-7  | Power flow over a line period                                     | 104 |

| Fig. 4-8  | Input current waveform obtained by MathCAD and Pspice             | 106 |

| Fig. 4-9  | Power flow analysis result by OrCAD Pspice                        | 108 |

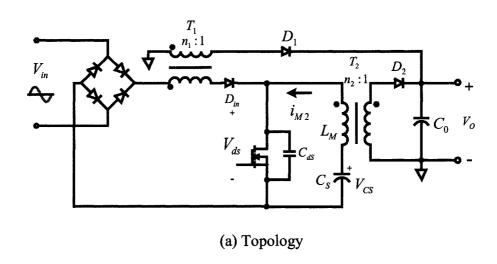

| Fig. 4-10 | Bi-flyback PFC converter with snubber circuit                     | 112 |

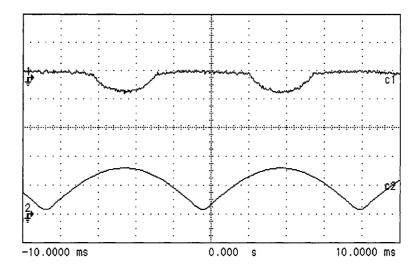

| Fig. 4-11 | Input current and input voltage at 100W output and 110V input     | 114 |

| Fig. 4-12 | Measured intermediate bus voltage versus output power             | 114 |

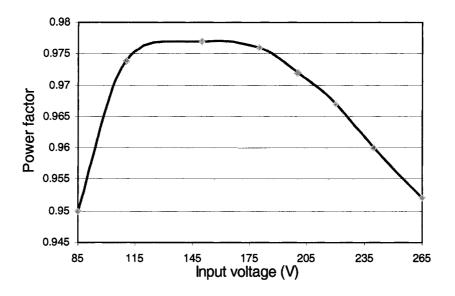

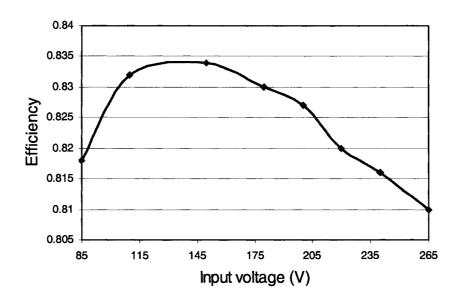

| Fig. 4-13 | Measured power factor at 150W load                                | .115 |

|-----------|-------------------------------------------------------------------|------|

| Fig. 4-14 | Measured efficiency at 150W load                                  | .115 |

| Fig. 5-1  | Duty cycle waveform for voltage mode control                      | .120 |

| Fig. 5.2  | Bi-flyback single-stage PFC converter                             | .124 |

| Fig. 5-3  | Equivalent circuit during free resonant interval                  | .125 |

| Fig. 5-4  | Simulated operational waveforms over switching cycle              | .128 |

| Fig. 5-5  | Operational waveforms over half line period                       | .129 |

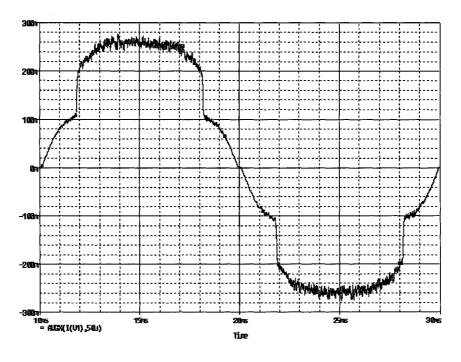

| Fig. 5-6  | Input current waveform                                            | .131 |

| Fig. 5-7  | Operational waveforms over switching cycle                        | .132 |

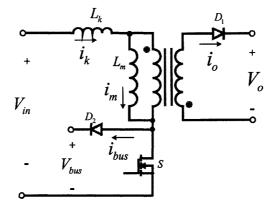

| Fig. 6-1  | Typical flyback circuit                                           | .137 |

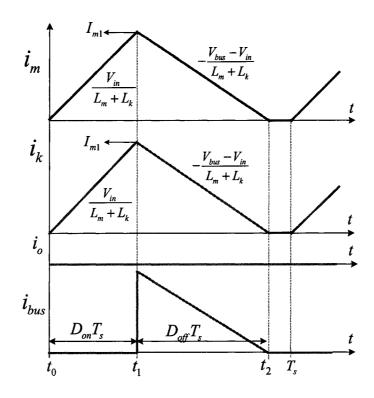

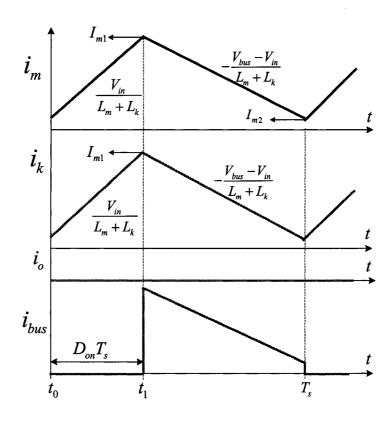

| Fig. 6-2  | Operation waveforms of flyback DCM+DCM mode                       | .140 |

| Fig. 6-3  | Operation waveforms of flyback CCM+DCM mode                       | .144 |

| Fig. 6-4  | Operation waveforms of flyback CCM+CCM mode                       | .147 |

| Fig. 6-5  | Special operation case for flyback CCM+CCM mode                   | .149 |

| Fig. 6-6  | Operation waveforms of Boost DCM+DCM mode                         | .151 |

| Fig. 6-7  | Operation waveforms of Boost CCM+CCM mode                         | .152 |

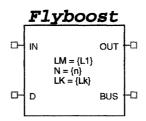

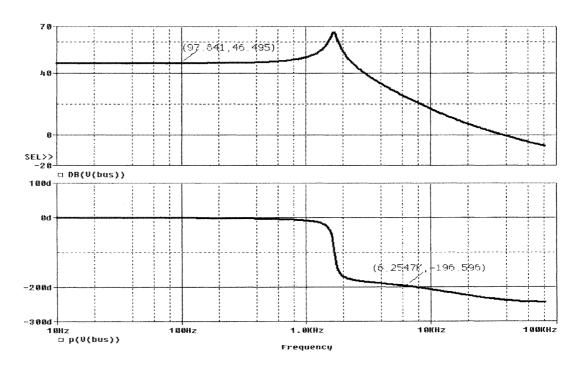

| Fig. 6-8  | Non-ideal flyback block circuit                                   | .160 |

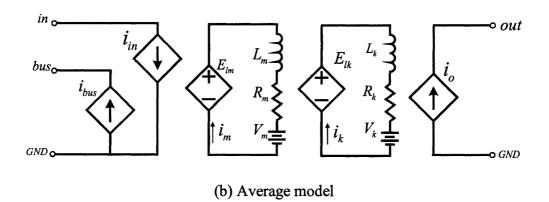

| Fig. 6-9  | Average model of non-ideal flyback block circuit in Pspice        | .161 |

| Fig. 6-10 | Netlist of the average model of non-ideal flyback block circuit   | .162 |

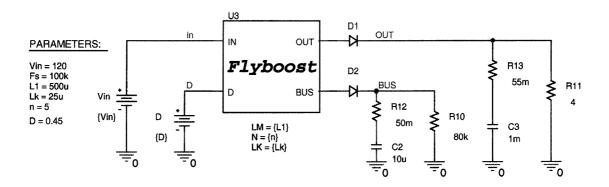

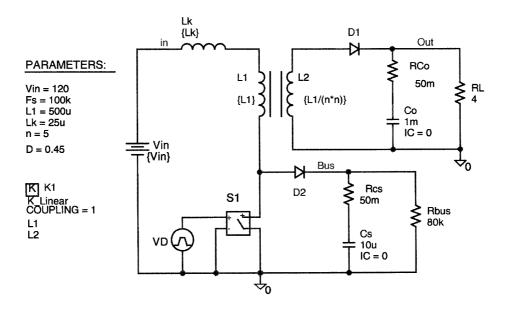

| Fig. 6-11 | Average model of non-ideal flyback converter                      | .164 |

| Fig. 6-12 | Switching model of non-ideal flyback converter                    | .164 |

| Fig. 6-13 | Simulation results comparison between average and switching model | .166 |

| Fig. 6-14 | Simulation circuit for non-ideal flyback by SIMPLIS               | .168 |

| Fig. 6-15 | Simulation results comparison for Flyback DCM+DCM operation170           |

|-----------|--------------------------------------------------------------------------|

| Fig. 6-16 | Simulation results comparison for Flyback CCM+DCM operation171           |

| Fig. 6-17 | Simulation results comparison for Boost CCM+CCM operation172             |

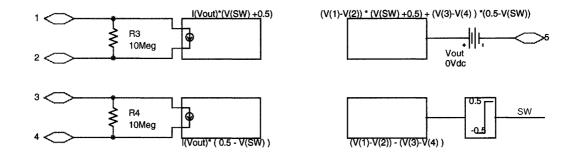

| Fig. 6-18 | Average model for parallel/series forward converter175                   |

| Fig. 6-19 | Average model of flyboost-parallel/series forward PFC converter176       |

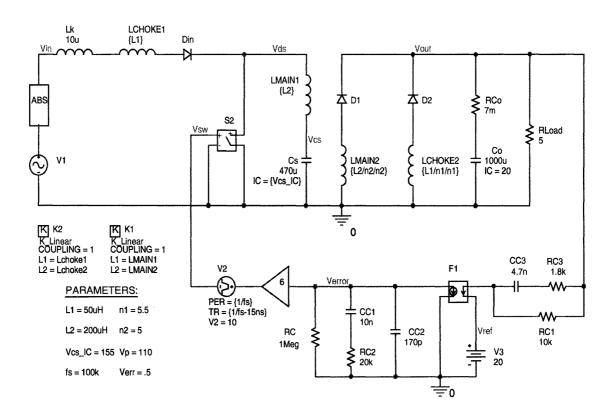

| Fig. 6-20 | Switching model of flyboost-parallel/series forward PFC converter177     |

| Fig. 6-20 | Comparison of simulation results from average and switching model178     |

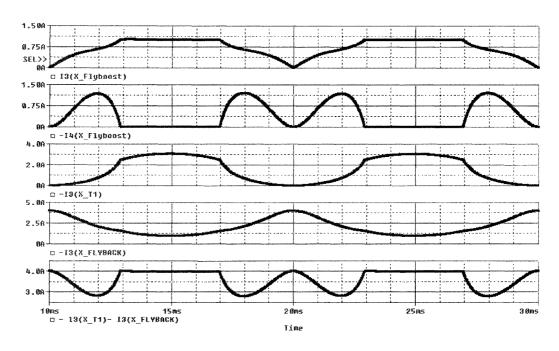

| Fig. 6-21 | Operational waveform in one line cycle180                                |

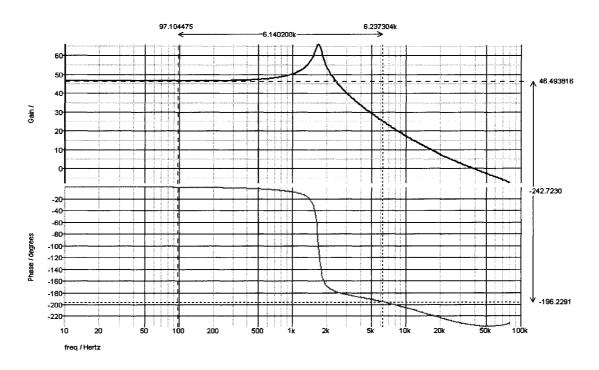

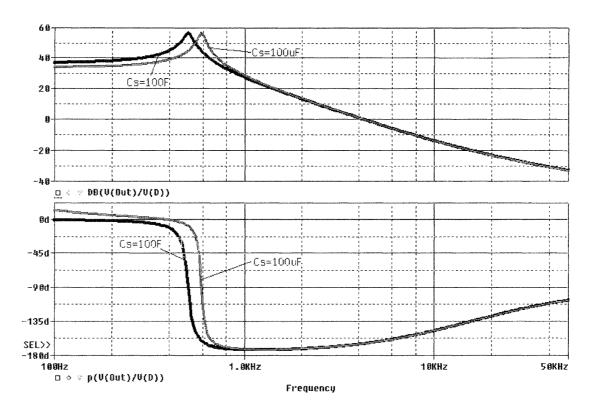

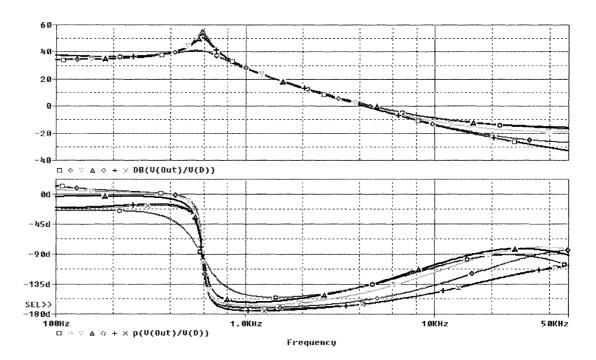

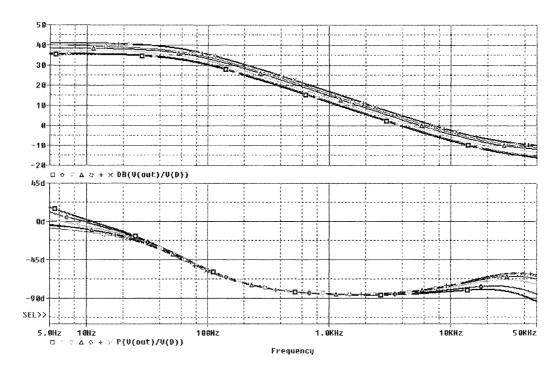

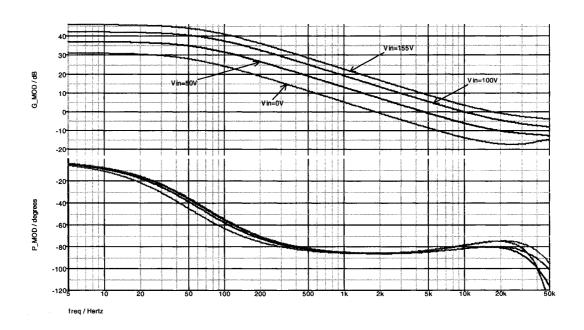

| Fig. 6-22 | Transfer function of Parallel-series forward with different capacitor183 |

| Fig. 6-23 | Transfer function of flyboost- Parallel/series forward PFC converter     |

|           | at different interval in one line period                                 |

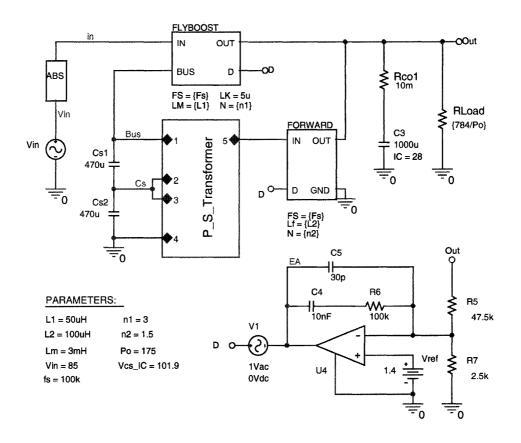

| Fig. 6-24 | Average model for Bi-flyback PFC converter                               |

| Fig. 6-25 | Switching model of Bi-flyback PFC converter                              |

| Fig. 6-26 | Comparison of simulation results from average and switching model192     |

| Fig. 6-27 | SIMPLIS model of Bi-flyback PFC converter193                             |

| Fig 6-28  | Transfer function of Ri-flyback PFC converter 194                        |

# **CHAPTER 1**

# INTRODUCTION

Power conversion system designs are becoming increasingly important in state-of-the-art electronics systems, especially in information system applications. Poor power quality in many power conversion systems has caused many problems as mentioned in recent surveys and industrial reports. Power factor correction techniques, which can improve the power quality of power conversion system, have become an attractive alternative due to several regulations that have been effected recently.

Many Power Factor Correction (PFC) AC/DC converters schemes have been proposed in recent years. Classified by the system configurations, these techniques can be divided into two categories, two-stage and single-stage schemes. For low power applications, including electronic ballasts for fluorescent lamps, the single stage approach is especially attractive due to its simple power stage and control circuit. But there are some issues existing in the single stage PFC converter, such as high DC bus voltage, high current stress and voltage stress over main switch components. A lot of topologies were proposed to solve one or some of those issues in order to achieve better performance. Those approaches are surveyed in this chapter.

1

## 1.1 Background

The power converter is a necessary part in lots of electronic equipment to convert utility line voltage to a voltage suitable for other parts in the electronic equipment. In conventional power conversion systems, a simple rectifier bridge directly connected with a bulky capacitor is used. But this kind of topology draws pulsed current from the utility line with poor power factor, typically 0.6. In order to limit the influence of the power conversion system on utility line, some standards, including IEC 555, have specified requirements for harmonic contents in the line current drawn by the electronic equipment.

There are two different approaches for meeting those requirements: the passive power filter and the active Power Factor Correction (PFC) circuit. Although they can achieve high efficiency, passive power filter are not commonly used due to their bulky size and weight. They can be found in some applications where there is a very strict EMI requirement. However, the active power factor correction circuit has drawn a lot of attention due to its high performance and compact size. Many products that use an active PFC circuit have appeared in the market recently.

In this chapter, conventional technologies of the active PFC converter are reviewed. Some common issues in single stage power factor correction circuit are discussed, and some available solutions are provided.

#### 1.1.1 Conventional Power Factor Correction converter

In the past several years, many topologies and control approaches have been presented in the active PFC area. According to its topology, the active PFC converter can be divided into categories:

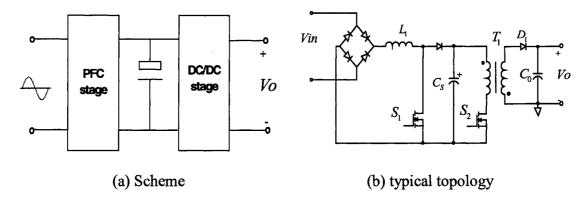

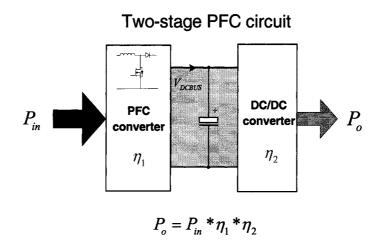

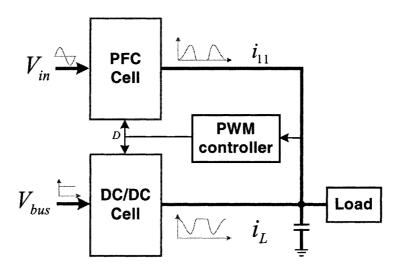

- a. <u>Two-stage PFC converter</u>: Consists of a PFC stage and a DC/DC conversion stage. The PFC stage will convert the utility line voltage to a constant DC voltage with a high power factor. The DC/DC conversion stage will convert that constant DC voltage to the desired voltage with tight output voltage regulation. These two stages can be optimally designed since they operate independently. This approach is commonly used in high power applications. The scheme and typical topology are shown in Fig. 1-1; its advantages include superior performance and flexible design configuration, but its cost is high due to its complex configuration.

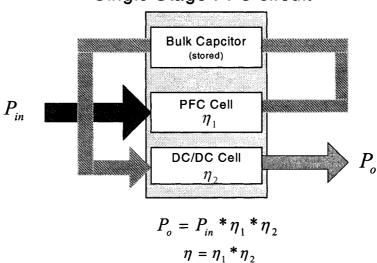

- b. <u>Single stage PFC converter</u>: The PFC stage and DC/DC conversion stage in this approach are integrated into one stage with single controller and shared active switches. Normally the controller is designed to achieve only the tight output regulation, while a high power factor is achieved through specified topologies with automatically waveform shaping function, such as boost topology with constant duty cycle control. The single stage PFC converter is more attractive for low power applications because of its simple configuration and low cost. Here some deep researches will be conducted on it. The scheme and typical topology are shown in Fig. 1-2.

Fig. 1-1 Two-stage PFC converter

Fig. 1-2 Single stage PFC converter

Fig. 1-3 Current waveform at different mode

PFC converter can be divided into three categories based on the conduction mode of PFC stage as shown in Fig. 1-3:

- a. <u>Continuous Conduction Mode (CCM):</u> In this mode, the PFC stage runs at CCM. This approach is typically used in high power two stage PFC converter, since the current stress on the active switches is lowest. With specifically designed IC chips, a very high power factor can be achieved easily. CCM operation can be applied to the single stage PFC circuit as mentioned in [1], but the configuration and control method are too complicated and too high cost.

- b. <u>Discontinuous Conduction Mode (DCM)</u>: In this mode, the PFC stage runs at DCM. This method is commonly used in a single stage PFC converter, since it is easy to get high power factor for some topologies when constant duty cycle control is implemented. Although the current stress on the active switch is much higher than its counterpart at CCM and intermediate bus voltage is out of active control, it draws a lot of attention due to its simplicity and low cost.

- c. <u>Boundary conduction mode</u>: This PFC stage runs at boundary conduction mode, the mode between CCM and DCM, which is when the new switching cycle begins once the line current reaches zero. With only a few components and simple control IC, this approach can achieve high performance without the diode reverse recovery problem that exists in CCM. This approach provides an excellent tradeoff between high performance and low cost, so it is common in low and medium power two stages PFC converters, such as in electronic ballast for fluorescent lamp applications.

# 1.1.2 Single stage Power Factor Correction converter

In this section, the research mainly focuses on the single stage PFC converter. The simplest single stage PFC converter uses the flyback converter directly. With simple configuration and control circuit, high power factor was achieved easily. Other familiar topologies, such as isolated Cuk and Sepic (without intermediate bulk capacitor), can also gain good power factor and the desired isolated output. Unfortunately, the main drawback of this kind of topology is the output voltage regulation. The high double-line-frequency ripple in output voltage limits the application of single stage converters.

In order to get tight regulation, an intermediate bus capacitor must be used since the input power will be pulsating when the power factor is unity. In [1], a family of single stage PFC topologies was achieved by integrating PFC cell and DC/DC cell with one controller and shared active switches. In this topology type, the PFC cell should have automatic waveform shaping function, which means that sinusoid input current waveform should be achieved without active control. As analyzed in [1], DCM boost topology under constant duty cycle control will generate sinusoid current waveform that follows the input voltage waveform. So the controller of this kind of topology will only need to be designed to maintain tight output regulation.

Many topologies, including DCM boost, buck-boost, and flyback, have the automatic waveform shaping function, as presented in [1-14]. All of those topologies can achieve high power factor under constant duty cycle control. Just integrated those PFC topologies with any other DC/DC topologies, many single stage power factor correction circuits can be achieved.

Although the previously mentioned approach is very simple and low cost, it is far from perfect: it suffers from high voltage stress, high current stress and high intermediate bus voltage. In order to relieve the circuit from those drawbacks, a lot of modified single stage topologies were presented with different features, as presented in [15], with different drawbacks. You have to make the tradeoff depending on your specified applications.

# 1.1.3 Key issues in single stage Power Factor Correction converter

The single stage PFC topologies are very simple and attractive for low cost application. However, this topology suffers from the following drawbacks:

- a. High intermediate bus voltage. As discussed in [15], the high intermediate bus voltage in the simple single stage PFC circuit is unavoidable because this voltage is out of active control. Although intermediate bus voltage can be independent from the load condition by running both PFC cell and DC/DC cell at DCM, it must change widely in order to get power balance between input and output for universal voltage applications. The high voltage rating capacitor will increase the converter cost largely. Some modified topologies or control methods can eliminate those problems at a price of lower power factor or higher complexity. Those options will be discussed in the following section.

- b. High voltage stress over active switch. High intermediate bus voltage brings high voltage stress on switch components. So high voltage rated components are required, resulting in high cost and low efficiency.

- c. High current stress. Since topologies with automatically waveform shaping function always run at DCM, the current stress on active switches is much higher. These active switches in a typical single stage PFC circuit need to process all output power twice, which results in increased current stress also. Although single stage PFC converter may save one or more active switches, the processed power is same as two-stage PFC circuit. It is difficult to get high efficiency.

- d. Complex configuration. Because PFC cell and DC/DC cell are integrated into one cell, it is difficult to get optimized design. It causes problems in the analysis of this kind of topology, as discussed in [15].

In next two sections, some solutions to above issues are discussed, and a family of PFC circuit with flyboost PFC cell is included also to show its features.

#### 1.1.4 Intermediate bus voltage control

In two-stage PFC circuit, there is a separate controller to keep the intermediate bus voltage constant. So the DC/DC stage design can be optimized. While in single stage PFC circuit, the only control is to obtain tight output voltage regulation. There is no active control over the intermediate bus voltage, since both PFC cell and DC/DC cell share active switches and single control loop. As discussed in [15-19], the intermediate bus voltage is an important issue in single stage PFC circuit, because it determines the voltage rating of bulk capacitor and switch components.

As presented in [15], the typical equation for intermediate bus voltage of flyback + flyback PFC converter operating under DCM+DCM was presented as:

$$V_{Bus} = V_{in} * \sqrt{\frac{L_2}{2 * L_1}} \tag{1.1}$$

While at DCM+CCM operation, it equals:

$$V_{Bus} = \frac{1}{n} \left( V_{in} \sqrt{\frac{V_o}{4} f_s L_1 I_o} - V_o \right)$$

(1.2)

From the above equations, we have found that the intermediate bus voltage depends on circuit parameters, input voltage and load condition when DC/DC conversion cell operates under CCM. While DC/DC conversion cell operates under DCM, the voltage will only depend on parameters and input voltage. A very high intermediate bus voltage will be expected when DC/DC conversion cell operates under CCM at light load. There are some approaches that may eliminate these problems, such as varied frequency control. But its complexity and EMI issue make it impractical. So, in order to keep this voltage in reasonable range, both PFC and DC/DC cell should operate at DCM in simple PFC circuit, although it increases current stress over switch components. Through this method, the intermediate bus voltage will be independent of the load condition.

From the DCM+DCM equation, we find that the intermediate bus voltage will change linearly according to the input voltage without any relationship with load condition. For universal line voltage applications, it may cause many problems for circuit design, since the line voltage will change from 85Vrms to 265Vrms. The reason for such a high intermediate bus voltage is that the circuit needs to balance the input power and output at any load and line voltage condition, and also keep input inductor operating under DCM.

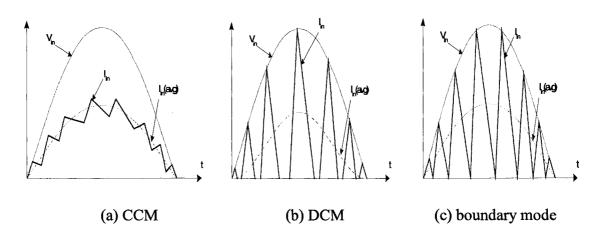

In order to limit the range of this voltage, several methods were presented in [14-19]. Good review of all methods was provided in [14]. The main concept of those approaches is to add a block cell in boost inductor charging or/and discharging path. Those blocks will transfer some power to output, reduce the effective charging voltage and/or increase effective discharging voltage across input inductor; so lower intermediate bus voltage can be expected.

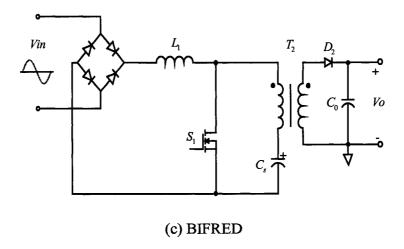

From Fig. 1-4, the effective charging voltage across boost inductor  $L_1$  during switch ON period is  $V_{in}(t) - V_{b1}$ , and discharging voltage during switch OFF period is  $V_{bus}+V_{b2}-V_{in}(t)$ . By adding two blocking voltage, the effective charging voltage reduces while effective discharging voltage increases. So lower intermediate bus voltage can keep PFC inductor under DCM. Bifred topology in [20-22] is also a good example of this concept, since there is a blocking cell located in boost inductor discharging path.

Typically, those blocking voltage is achieved by adding an extra winding to the main transformer, referred as magnetic switch or DC bus voltage feedback in [16-19]. Those windings will transfer some power directly to the output end and reduce the effective input power in one line cycle. So it breaks the original power balance across the intermediate bus capacitor and keeps the intermediate bus in a reasonable range. And another advantage of this concept is that the DC/DC cell can operate at CCM to reduce current stress on the switch component without punishment of high voltage stress at light load condition.

# (a) Voltage blocking scheme

# (b) Typical topology

Fig. 1-4 blocking cell in boost inductor path to reduce intermediate bus voltage

But its disadvantage is also obvious: when the input voltage is less than  $V_{b1}$ , there will be no input current. So it will deteriorate the input current waveform and reduce power factor. And complex transformer configuration is another drawback. So the improvement is achieved at a price of performance deterioration.

In [23], another effective method, referred to flyboost PFC scheme, was proposed to reduce the voltage and current stress. By adding a winding to PFC inductor, the intermediate bus voltage is limited less than V<sub>in</sub>+ n\*V<sub>o</sub>. And DC/DC cell also can operate at CCM to reduce current stress. Based on the flyboost PFC scheme, a family of single stage PFC converter can be derived, as discussed in [23-29]. And implementing this concept to Bifred topology, the so-called Bi-Flyback topology in [29] will have even lower intermediate bus voltage. In following chapters, two typical flyboost-derived single stage PGC topologies are studied in detail.

## 1.1.5 Parallel power flow PFC converter

In order to get low cost high performance topology, voltage stress and current stress on power components should be as low as possible. High current stress means high current rating components, high cost and low efficiency. For a good topology, the current stress should be as less as possible under the condition of meeting all other requirements. Here, some solutions to reduce the current stress are discussed.

Firstly, the influence of operation mode is studied. DCM operation always means higher RMS value than CCM operation when the average value is same. So the best choice is to let the circuit operate at CCM. But, as mentioned in last section, most of single stage PFC circuit needs to operate at DCM+DCM (both cells at DCM) in order to

get high power factor and reasonable bus voltage range. So the current stress is pretty high in most single stage PFC circuit.

For PFC cell, classic single stage PFC topologies with automatically waveform shaping function require the inductor to operate under DCM in order to get high power factor. Some topologies can run at CCM still with good power factor. But the circuit configurations or/and it control method were too complex. There is no other good choice for simple low cost single stage PFC circuit. So PFC cell has to operate at DCM for low cost and simple circuit.

As for the DC/DC cell, operation at DCM is required just to limit the intermediate bus voltage range under different load condition. If there is another good way to disconnect the relationship between the intermediate bus voltage and load condition, DC/DC cell can run at CCM to reduce the current stress.

So a good operation mode for single stage PFC circuit is DCM+CCM, with an effective method limiting the intermediate bus voltage. The topologies presented in next two chapters are under DCM+CCM.

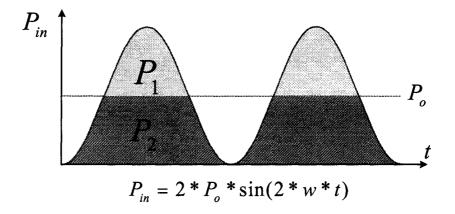

Secondarily, power flow in single stage PFC circuit is analyzed. Assume that both the input voltage and input current are sinusoid waveform and power factor is 1. Then the input power is equal to 2\*Po\*sin(2\*w\*t), as shown in Fig. 1-5. The input power is also sinusoid waveform. In order to get tight output voltage regulation, there should be a stored device to store energy of P1 in Fig. 1-5 when instantaneous Pin is higher than output power. Then the stored power is transferred to output when instantaneous input power is less than output power.

Fig. 1-5 input power waveform for unity power factor

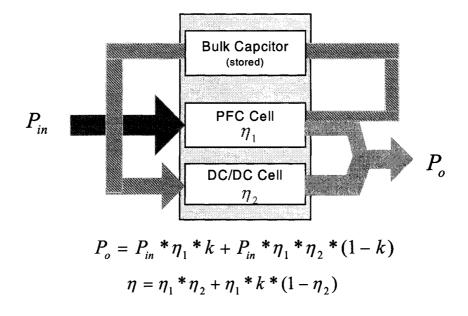

Classic since single stage PFC circuit is just an integration of PFC cell and DC/DC cell in corresponding two-stage PFC cell, so the active switch needs to process all output power separately in the PFC cell and in DC/DC cell like in two-stage PFC converter. It means that active switch needs to process all output power twice: first convert input power to stored DC power, and then convert stored DC power to output power. Fig. 1-6 (a) and (b) shows the power flow in two-stage PFC circuit and single stage PFC circuit. The equation of efficiency of those circuits is same:

$$\eta = \eta_1 * \eta_2 \tag{1.3}$$

In each power processing, there are some power losses dissipated as heat. So the efficiency of the conversion system is low. If some power can be transferred to output direct through PFC cell, the power processed by DC/DC cell will be less, which means that the power losses in DC/DC cell can be reduced. This concept is shown in Fig. 1-6(c). The equation of efficiency of this concept is:

$$\eta = \eta_1 * \eta_2 + \eta_1 * k * (1 - \eta_2)$$

(1.4)

K is the ratio of direct transferred power versus whole power.

It is clear that the efficiency of this method is higher than conventional method. And the current stress is also reduced since the power processed in DC/DC cell is reduced. Now the issue is how many power should be directly transferred to output without deterioration to input current waveform, and how to do it.

(a) Two-stage PFC

# Single Stage PFC circuit

(b) Single stage PFC

(c) Single stage PFC with direct power transfer

Fig. 1-6 Power flow chart

In order to keep tight output voltage regulation, power transferred to output end should always be equal to load power at any time. In order to get high efficiency, the best way is to transfer all input power direct to output end when instantaneous input power is less than output power, and transfer extra power to output from intermediate bus capacitor, and transfer exact output power to output end directly and store extra power in intermediate bus capacitor. According to this idea, P2, in Fig. 1-5, can be transferred to output directly without influence to output voltage regulation. And P1 needs to be stored in bulk capacitor and transferred to output when P2 is less than Po. It is easy to calculate that P2 is 68% of Po, and P1 is 32% of Po. It means that 68% of output power is processed by active switch only once, and only 32% of output power is handled twice. The output power is processed 1.32 times by active switches, instead of 2 times in

conventional single stage PFC circuit. This method is the best method for single stage PFC circuit, as far as power processing is considered.

Since there are two power flow paths in the abovementioned concept, it is referred to "parallel power transfer" in [30-35]. Based on its operation features, it also is called "direct power transfer" in [23].

Based on this concept, some topologies were presented recently. In [30], by using two separate cells in primary side, exact value of P1 and P2 were transferred to output end. Although high efficiency was achieved, its complicated configuration is its main drawback.

In [31], this concept was applied to secondary side. Another independent DC/DC converter is added to conventional PFC circuit to store and transfer P1. High power factor and efficiency were reported. But the disadvantage is its complexity and high cost.

In [32], some simple topologies based on parallel power transfer concept were proposed. By properly merging two conventional topologies, those topologies also achieve parallel power transfer. Simple circuit and control was their advantage. But those topologies brought high current harmonic content that reduced the power factor. Although the power factor still met the regulations, it is not a good choice.

Basically, a lot of topologies in [14] with extra winding in boost loop to block charging/discharging voltage also have this function. In [33], a lot of parallel power transfer topologies were reviewed in detail.

By the way, parallel power transfer also means that it breaks the power balance across intermediate bus capacitor. So some topologies with parallel power transfer can also limit the intermediate bus voltage.

# 1.1.6 Average Model for switching mode power supply

In switching mode power supply design, the transfer function of the converter is important. Based on the transfer function, optimal compensation circuit can be designed to achieve better transient response. Due to its switching characteristics, the circuit configuration changes when the switch is ON or OFF. The power supply system is the non-linear time-variant system. So conventional linear control theory cannot be implemented to switching mode power supply design.

In switching mode power supply, there is one important feature that makes it different to other non-linear time-variant system. The time constant of the inductor and capacitor is much longer than the switching period. The L-C works like lower frequency filter for the system. Based on this characteristic, the averaging modeling concept was proposed to model the switching mode power supply system in [34]. The basic concept of the average modeling is to find out the averaged characteristics of the system in one switching cycle. Then the linear equivalent system is obtained by the small signal perturbation is applied around the steady state operation point. This linear equivalent can be used for the AC analysis of the switching mode power supply.

The average modeling was discussed in a lot of papers for different topologies, such as in [34-42]. For different topologies, one average model had to be derived. Then the PWM switch model in [35-37] provided one unified model just for the non-linear time-variant part of the power supply: the switch and diode. The model then was put back to the original circuit with all other parts, such as inductor and capacitor in the same position untouched. The PWM switch model is good for simulation. The Switch Inductor Model (SIM) in [38-40] implements one block to replace the inductor, the switch and

diode. One feature of SIM is its automatic mode transition. By limiting the maximum diode conduction time to (1-D)\*Ts, the model works for CCM and DCM. It simplifies the simulation procedure.

The modeling for power factor correction converter is little different to the DC-DC converter. Average modeling concept can also applied here. In DC-DC converter, the averaging procedure is performed over one switching cycle. For PFC converter, the averaging procedure is over one line cycle, assumed that the control loop response very slow. In [41-45], the average modeling method for power factor correction converter was discussed.

Once the average model is developed, simulation software, such as Pspice, can be implemented to find the transfer function of the power supply. Pspice can perform bias point calculation to find out the steady state operation point, and then perform small signal AC analysis.

## 1.2 Dissertation Outline

The objective of dissertation is to study the flyboost derived single stage Power Factor Correction converters. By implementing direct power transfer, flyboost derived PFC schemes can achieve better performance comparing to other single stage PFC schemes. The operation and characteristics of this scheme was discussed in detail, and two typical examples were studies with experimental results. And practical design

procedure was proposed. The average model was developed and implemented to perform the AC small signal analysis of flyboost derived PFC converters.

The dissertation is organized into seven chapters as following:

Chapter 2 will discuss on the operation and features of the flyboost PFC cell by one simple example;

Chapter 3 focuses on the analysis and design of the flyboost-parallel/series forward single stage PFC converter;

Chapter 4 will discuss on the operation and characteristics of Bi-flyback single stage PFC converter;

Chapter 5 will focus on the control method for Bi-flyback PFC converter, and valley-switching control technique is discussed in detail;

Chapter 6 will discuss on the average modeling of the flyboost PFC cell and flyboost-derived single stage PFC converter;

Chapter 7 provides the conclusions of this dissertation.

# **CHAPTER 2**

# DIRECT POWER TRANSFER FLYBOOST PFC CELL

### 2.1 Introduction

One of common characteristics in conventional PFC cell topologies, such as Boost, buck-boost, and flyback topologies, is that there is only one power flow path. This means that the active switch must process all output power twice, as discussed in previous chapter. Some modified topologies can carry out direct power transfer function with higher efficiency and limited intermediate bus voltage, but input current waveform is deteriorated and power factor performance is lessened.

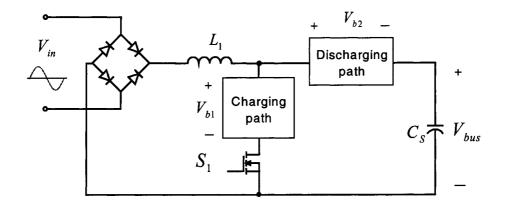

In [23], another approach was proposed to carry out this function with little influence on this current waveform. The main idea is to add an extra winding to input inductor to get another power flow path directly to output. Based on this concept, a PFC cell with direct power transfer was presented, called as flyboost in [23]. As shown in figure 2-1, Flyboost PFC cell consists of a boost converter with an additional winding added to the boost inductor.

Fig. 2-1 Flyboost PFC cell

Based on this PFC cell, a family of single stage Power Factor Correction topologies can be derived, as illustrated in [23]. All those topologies can transfer some input power directly to output, and limit maximum intermediate bus voltage. In this chapter, one simple example is implemented to discuss the operation of flyboost PFC cell, and power flow analysis approach is proposed to obtain the equation of the intermediate bus for practical design.

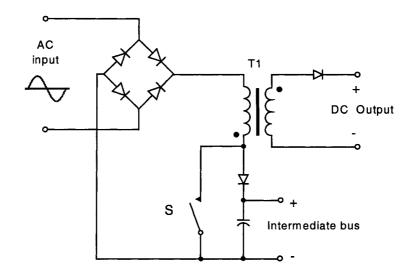

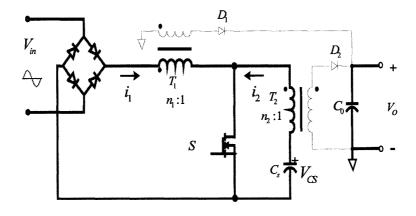

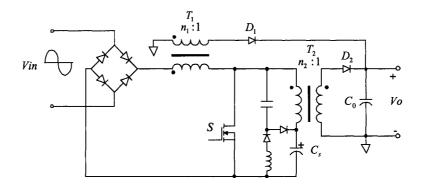

#### 2.2 Flyboost-flyback single stage PFC

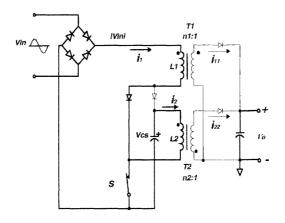

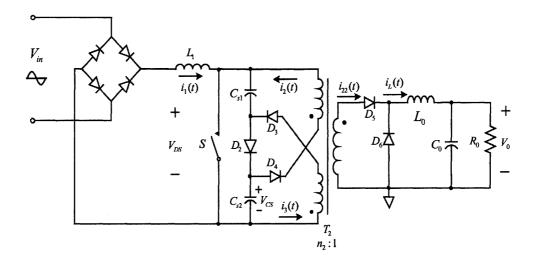

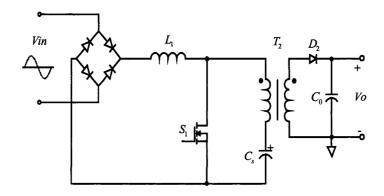

The simplest DC-DC converter is flyback. Here, flyback DC-DC cell is integrated with flyboost PFC cell to form a new single stage PFC converter. The topology is shown in Fig. 2-2, which consists of a flyboost PFC cell and a flyback converter cell. The flyboost PFC cell includes flyboost transformer T<sub>1</sub>, input bridge rectifier, diode D<sub>1</sub>, D<sub>2</sub>,

$D_3$  and main switch S. The flyback converter cell is comprised of flyback transformer  $T_2$ , diode  $D_4$  and main switch S. Both cells share only main switch and the controller.

Fig. 2-2 An example of Flyboost PFC circuit

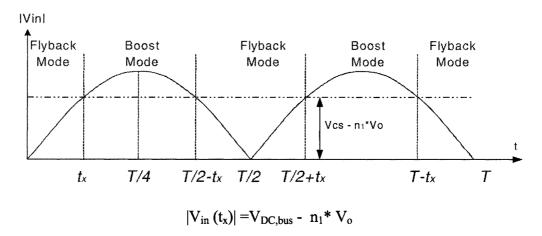

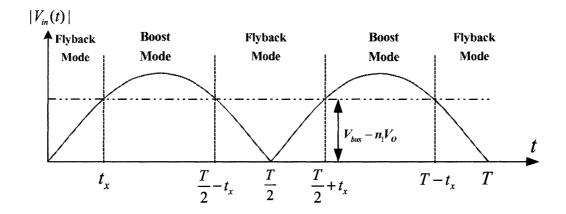

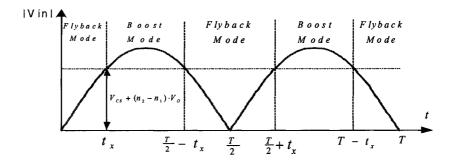

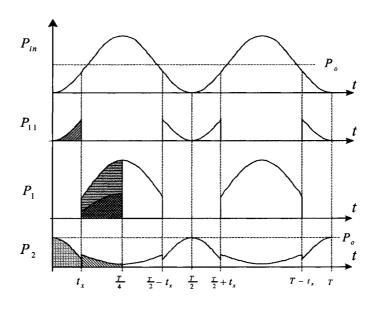

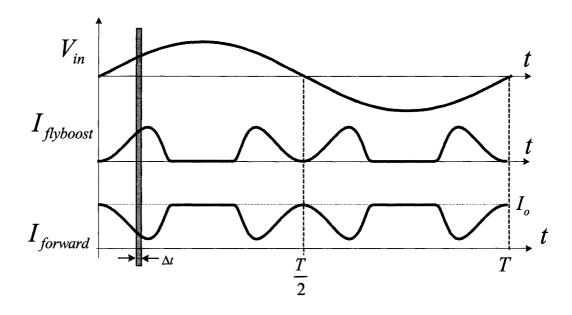

According to the operation of the flyboost transformer  $T_1$ , the proposed PFC cell operates in two different modes in one line cycle, as shown in Fig. 2-3. These two modes of operations are discussed as follows:

a). Flyback mode: When  $v_{in}(t) < V_{DC,bus} - n_1 * V_o$ ,  $(n_1: turn ratio of T_1)$ ,  $T_1$  operates as a flyback transformer. When main switch S is ON,  $T_1$  is charged by rectified line voltage linearly. When S is OFF,  $T_1$  will discharge all of its stored magnetizing power to output. So  $T_1$  magnetizing power stored during main switch ON period is directly transferred to output, resulting in this part of power being processed only once.

<u>b). Boost mode:</u> When  $v_{in}(t) >= V_{DC,bus} - n_1 * V_o$ ,  $T_1$  works as a boost inductor. When S is ON,  $T_1$  is charged by rectified line voltage linearly. When S is OFF,  $T_1$  will discharge all of its magnetizing power to DC bus capacitor. The power stored in DC bus

capacitor will be transferred to output by DC/DC conversion cell, with this part of power being processed twice.

Fig. 2-3 Operation mode of Flyboost PFC cell in one line frequency cycle

According above discussion, Flyboost PFC cell operates like boost PFC cell or flyback PFC cell at different period in one line cycle. Since high power factor can be achieved by both DCM flyback PFC cell and DCM boost PFC cells, high power factor can also be expected from flyboost PFC cell. Integrating flyboost PFC cell with a DC/DC conversion cell, tight output regulation will also be achieved.

Parameters in figure 2-2 are defined as:

- Flyboost transformer T<sub>1</sub>: Turn ratio n<sub>1</sub>:1; primary inductance L<sub>11</sub>, secondary inductance L<sub>12</sub>

- Flyback transformer T<sub>2</sub>: Turn ratio n<sub>2</sub>:1; primary inductance L<sub>21</sub>, secondary inductance L<sub>22</sub>

- |Vin(t)|: rectified instantaneous input voltage

- V<sub>cs</sub>: storage capacitor voltage on high voltage side

■ V<sub>o</sub>: output voltage

In the following analysis, we assume that:

- No leakage inductance in two transformers

- $V_{cs}$  (voltage across storage capacitor) and output  $V_o$  are constant

- All switch components are ideal

- Input voltage is constant during each switching cycle

- Flyboost operates at DCM, Flyback runs at CCM

#### 2.2.1 Flyback Operational Mode Analysis

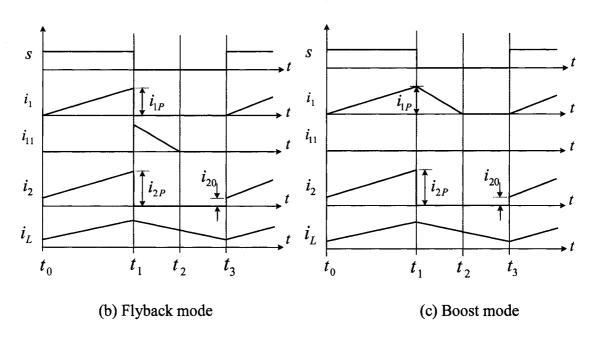

When the line voltage is low,  $|V_{in}(t)| < V_{cs} - V_o * n_l$ , the flyboost power factor correction cell works as flyback transformer. During the switch on period, the current in flyboost transformer will increase linearly and the energy is stored as magnetizing energy. During the switch off period, the stored magnetizing energy will be transferred to the load. Meanwhile, the flyback converter cell will deliver some power to load also in order to keep the total power transferred by PFC cell and flyback cell in one switching cycle equal to the output power. By this way, the output voltage ripple will be minimized. Operation waveforms and equivalent circuits during this mode are shown in figure 2-4.

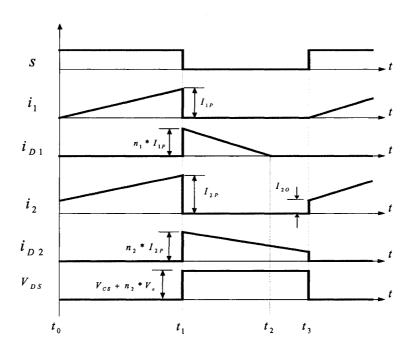

# a. Operation waveform

# b. Equivalent circuit during ON period

# c. Equivalent circuit during OFF period

Fig. 2-4 Operation of flyback mode

Interval 1 ( $t_0 \sim t_1$ ): the main switch is turned on at  $t_0$ , the rectified line voltage |Vin| is applied to  $L_{11}$ , the primary winding of flyboost transformer  $T_1$ . The current in  $L_{11}$ ,  $i_{L11}$  in Fig. 2-4, will increase linearly, and the energy is stored in flyboost transformer. And the voltage across storage capacitors is applied to flyback transformer,  $T_2$ , which will cause the current in output filter ( $i_2$  in Fig. 2-4) to increase linearly. Since PFC cell operates at DCM,  $i_{L11}$  will increase from zero.

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L11}) := \frac{|\mathrm{Vin}(\mathrm{t})|}{L11} \tag{2.1}$$

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L21}) := \frac{\mathrm{Vcs}}{L21} \tag{2.2}$$

Interval 2 ( $t_1 \sim t_2$ ): the main switch is turned off at  $t_1$ ,  $T_1$  will discharge through its secondary winding  $L_{12}$  and delivery stored magnetizing energy to the output. The current in the flyboost transformer secondary winding ( $i_{L12}$ ) will decrease linearly. And the current in  $T_2$  ( $i_{L22}$ ) will also decrease linearly.

At  $t_2$ , all magnetizing energy in flyboost transformer  $T_1$  is transferred to the load,  $i_{L12}$  reaches zero and the block diode  $D_3$  will prevent the current from becoming negative. And the current in flyback transformer  $L_{22}$  continues to decrease.

$$\frac{d}{dt}(i_{L12}) := -\frac{Vo}{L12}$$

(2.3)

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L22}) := -\frac{\mathrm{Vo}}{\mathrm{L}22} \tag{2.4}$$

Interval 3 ( $t_2 \sim Ts$ ):  $i_{L12}$  stays at zero. And the current in flyback transformer  $T_2$   $i_{L22}$  continues to decrease until the switch is turned on at  $T_s$  and a new cycle begins.

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L12}) := 0 \tag{2.5}$$

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L22}) := -\frac{\mathrm{Vo}}{L22} \tag{2.6}$$

#### 2.2.2 Boost Operational Mode Analysis

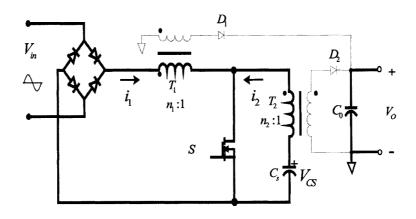

When line voltage is higher than  $V_{cs}$ -  $V_o$ \*  $n_l$ , flyboost transformer  $T_l$  works as boost inductor. During the switch ON period, the current in flyboost transformer  $T_l$  will increase linearly, then decrease and transfer power to storage capacitors during the switch off period. The flyback converter cell will deliver all required power to the load to minimize the output voltage ripple.

Interval 1 ( $t_0 \sim t_1$ ): the main switch is turned on at  $t_0$ , the line voltage is applied to flyboost transformer. The current in the primary winding of flyboost transformer,  $i_{L11}$  in Fig. 2-5, will increase linearly. And the voltage across storage capacitors will be applied to transformer,  $T_2$ , which will cause the current  $i_{L21}$  in Fig. 2-5 to increase linearly also. Under full load condition Flyboost transformer will runs as a boost inductor at DCM, while flyback converter cell will run at CCM to reduce current stress on main switch.

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}\,\,\mathrm{L}_{11}\,) := \frac{\left|\mathrm{Vin}\,(\mathrm{t})\right|}{\mathrm{L}_{11}}\tag{2.7}$$

$$\frac{\mathrm{d}}{\mathrm{dt}}(i_{L21}) := \frac{\mathrm{Vcs}}{L21} \tag{2.8}$$

Interval 2 ( $t_1 \sim t_2$ ): the main switch is turned off at  $t_1$ . The current in the flyboost ( $i_{L11}$ ) will decrease linearly and discharge energy to storage capacitors. And the current in flyback ( $i_{L22}$ ) will also decrease linearly. At  $t_2$ , the current in the flyboost ( $i_{L11}$ ) reaches zero.

# a. Operational waveform

# b. Equivalent circuit during ON period

# c. Equivalent circuit during OFF period

Fig. 2-5 Operation of flyback mode

$$\frac{d}{dt}(i_{L11}) := |Vin(t)| - Vcs$$

(2.9)

$$\frac{d}{dt}(i_{L22}) := -\frac{Vo}{L22}$$

(2.10)

Interval 3 ( $t_2 \sim t_3$ ):  $i_{L12}$  stays at zero. And the current in flyback transformer  $T_2$   $i_{L22}$  continues to decrease until the switch is turned on at  $t_3$ . Then a new switching cycle will begin.

$$\frac{\mathrm{d}}{\mathrm{dt}}(\mathrm{i}_{L12}) := 0 \tag{2.11}$$

$$\frac{d}{dt}(i_{L22}) := -\frac{Vo}{L22}$$

(2.12)

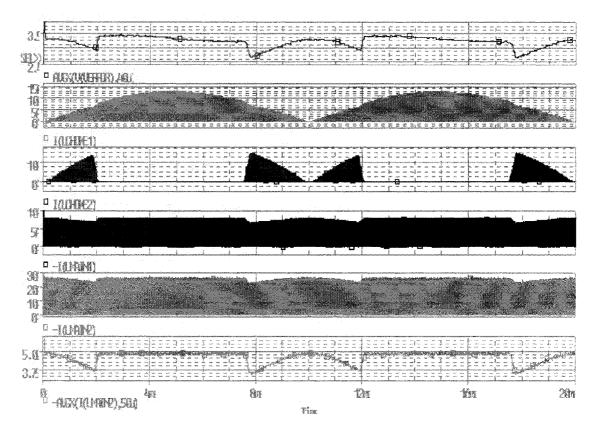

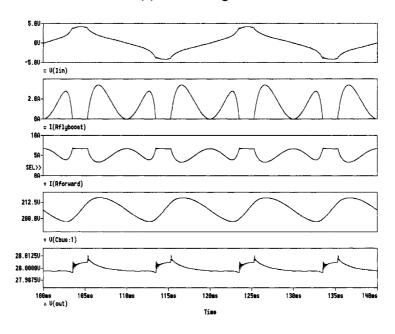

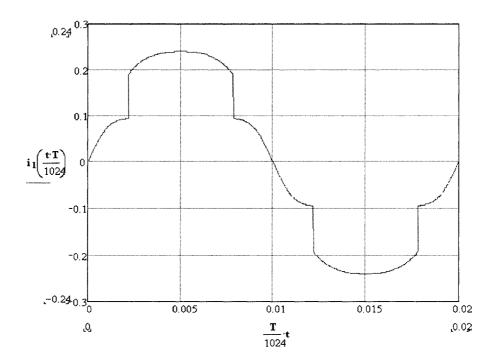

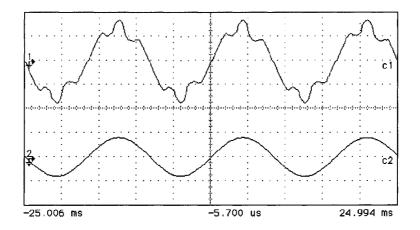

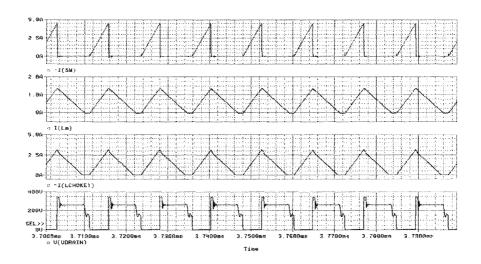

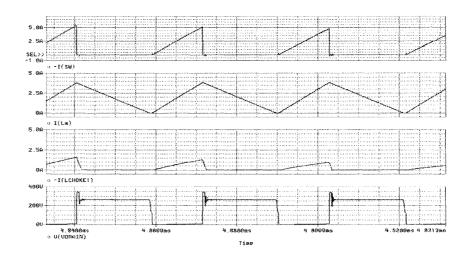

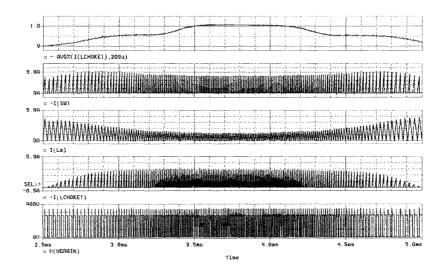

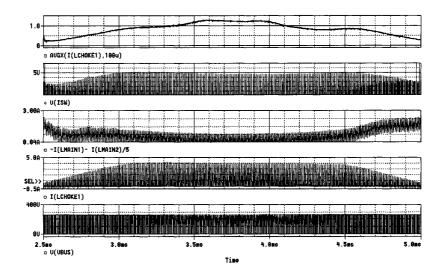

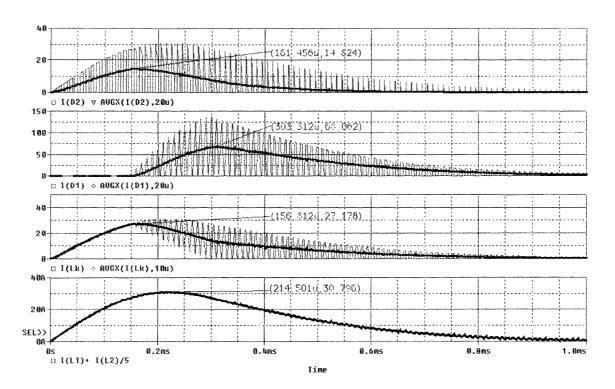

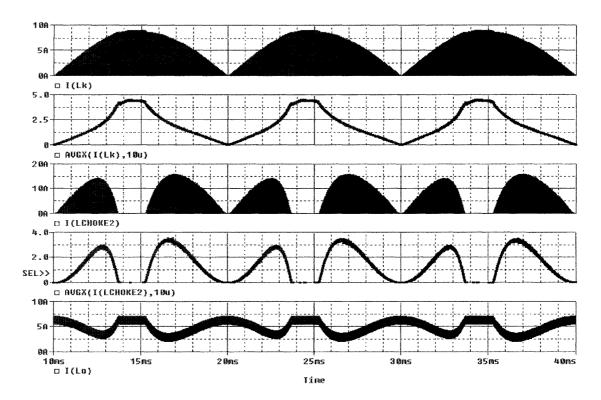

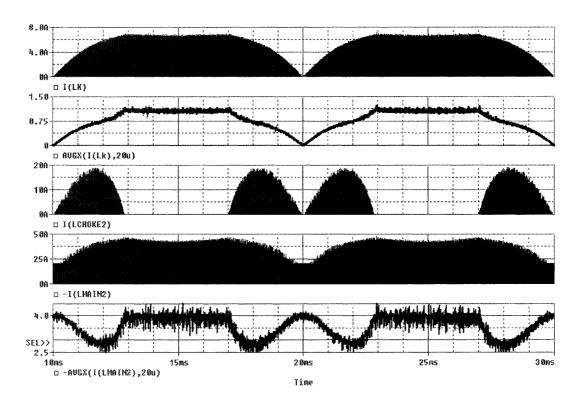

The operation of this topology in Fig. 2-2 was simulated in OrCAD Pspice<sup>®</sup>. Some simulation results are shown in Fig. 2-6. Those results verified the correction of above analysis. Some simulation results are shown in Fig. 2-6. In this simulation, simple output voltage feedback controller is used. The duty cycle (trace 1) is changing according to average  $i_{L22}$  value (trace 6) in order to keep the sum of  $i_{L12}$  and  $i_{L22}$  equal to output current.

In Fig. 2-6, we can clearly see there are two different operation modes in this topology. And the input current waveform still follows voltage change with little distortion, which means high power factor achieved at input end.

From top to bottom:

Trace 1: duty cycle (D)

Trace 2: T1 primary current (i<sub>L11</sub>)

Trace 3: T1 secondary current  $(i_{L12})$

Trace 4: T2 primary current (i<sub>L21</sub>)

Trace 5: T2 secondary current (i<sub>L22</sub>)

Trace 6: Average T2 secondary current (i<sub>L22</sub>) over each switching cycle

Fig. 2-6 Operational waveform in one line cycle by simulation

#### 2.3 Power Flow Analysis

Since there are two different operational modes in flyboost derived PFC topology, conventional analysis methods can be adopted directly. For large signal analysis, the parameters can be determined through power flow analysis. However, it is a challenge to find an effective analysis method for small signal analysis.

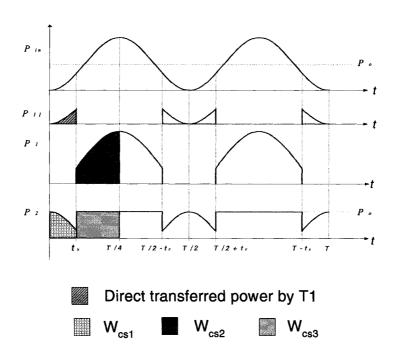

In the following section, power flow analysis method is applied to analyze the topology in Fig. 2-2. In this analysis, only DCM+CCM operation is analyzed. However, other combination operation modes, such as DCM+DCM and DCM+CCM/DCM can gained easily according to same analysis method. The power flow chart is shown in Fig. 2-7.

For simplicity, the following assumptions are given:

- Ideal components, without switching characteristics, leakage inductance, parasitic parameters, etc.

- Input voltage is constant during each switching cycle;

- Switching frequency is much higher than line frequency;

- Sum of value over switching cycle can be converted to integration over time;

- Vcs, DC bus voltage, is constant, meaning that the charging energy and discharging energy to DC bus capacitor should be equal for each <u>line cycle</u>;

- Tight output regulation. It means the charging energy and discharging energy to output capacitor should be equal for each <u>switching cycle</u>;

The main concepts in this method are:

- Calculate total power transferred by two paths, which should be equal to output power, and obtain instantaneous duty cycle for each switching cycle;

- Calculate the charging and discharging power of the intermediate bus capacitor. These power should remain equal to keep the intermediate bus voltage constant. This equation can be used to obtain the intermediate bus voltage under different circuit parameters.

Fig. 2-7 Power flow map of flyback-flyback topology

It is preferred to let DC-DC flyback cell operate under CCM, because the RMS current through power components is minimum. Here, we begin to analyze with DC-DC flyback cell operating under CCM. Other operation mode analysis will discuss later.

If DC-DC flyback cell operates under CCM for the whole line cycle and intermediate bus voltage is constant, the duty cycle should be constant also to achieve constant output voltage:

$$D = \frac{n_2 * V_o}{V_{cs} + n_2 * V_o} \tag{2.13}$$

Since operation mode is changing based on the instantaneous input line voltage, the power transfer path is also different in flyback and boost modes. We need to analyze the power flow separately in two modes.

#### 2.3.1 Flyback Mode Power Flow Analysis

During Flyback mode, two flyback transformers are charged during ON period, and T<sub>1</sub> is entirely discharged during OFF period in each switching cycle, but T<sub>2</sub> will not completely discharged since it operates at CCM. And all stored magnetizing energy in T<sub>1</sub> transformers are transferred to output end directly, and some of T<sub>2</sub> will be transferred to output also. So there are two power paths for output. And DC bus capacitor (intermediate bus capacitor) is only discharged, no charging energy in flyback mode.

The following equation shows the current in  $T_1$  primary winding when switch is turned off at  $t_1$

$$i_{lp} := \frac{V_g \cdot D \cdot T_s}{L_l} \tag{2.14}$$

The following equation shows stored magnetizing energy in  $T_1$  transformers when switch is turned off at  $t_1$ .

$$W_1 := \frac{L_1 \cdot i_{1p}^2}{2} \tag{2.15}$$

By combining Eqs. 2-14 and 2-15, we obtain:

$$W_{1} := \frac{V_{g}^{2} \cdot D^{2} \cdot T_{s}^{2}}{2 \cdot L_{1}}$$

(2.16)

All power processed in this mode is transferred to load. In order to keep tight output voltage regulation, i.e.  $V_0$  constant, the total power transferred by  $T_1$  and  $T_2$  should be equal to output power in each switching cycle. The power transferred by  $T_1$  is equal to:

$$P_{1} = \frac{W_{1}}{T_{S}} = \frac{V_{g}^{2} D^{2} T_{S}}{2L_{1}} \tag{2.17}$$

So the power processed by T<sub>2</sub> in one switching cycle is:

$$P_2 = P_o - P_1 = P_o - \frac{V_g^2 D^2 T_S}{2L_1}$$

(2.18)

In whole flyback mode, total energy transferred by flyback transformer  $T_2$  is from DC bus capacitor, and is equal to:

$$W_{cs1} := \sum_{t=0}^{t_x} P_2 \cdot T_s$$

(2.19)

When the switching period is much less than line period, the above sum equation can be converted to the following integration equation:

$$W_{cs1} := \int_{0}^{t_x} \left( P_o - \frac{V_g^2 \cdot D^2 \cdot T_s}{2 \cdot L_1} \right) dt$$

(2.20)

The input voltage can be described as:

$$V_{g} := V_{p} \cdot \sin(w \cdot t) \tag{2.21}$$

So the total discharging energy from intermediate bus capacitor during flyback mode is equal to:

$$W_{cs1} := P_o \cdot t_x - \frac{V_p^2 \cdot D^2 \cdot T_s}{2 \cdot L_1} \int_0^{t_x} \sin(w \cdot t)^2 dt$$

(2.22)

The above equation can be simplified as:

$$W_{cs1} := P_o \cdot t_x - \frac{V_p^2 \cdot D^2 \cdot T_s}{2 \cdot L_1} \left( \frac{t_x}{2} - \frac{\sin(2 \cdot w \cdot t_x)}{4 \cdot w} \right)$$

(2.23)

#### 2.3.2 Boost Mode Power Flow Analysis

Under boost mode, two flyback transformers are charged during ON period, and  $T_1$  entirely is discharged its magnetizing energy to DC bus capacitor during OFF period in each switching cycle. All output power is from DC bus capacitor through  $T_2$ . And DC bus capacitor is discharged by  $T_2$ , and charged by  $T_1$  at this mode.

The average input current in one switching cycle is

$$i_1(avg) := \frac{D^2 \cdot T_s}{2 \cdot L_1} \cdot \frac{V_{cs} \cdot V_g}{V_{cs} - V_g}$$

(2.24)

So the average input power in one switching cycle is

$$P_1 := V_g \cdot i_1(avg) \tag{2.25}$$

By combining Eq. 2.24 and 2.25, we obtain:

$$P_{1} := \frac{D^{2} \cdot T_{s}}{2 \cdot L_{1}} \cdot \frac{V_{cs} \cdot V_{g}^{2}}{V_{cs} - V_{g}}$$

(2.26)

The energy transferred by  $T_1$  from input is stored completely in DC bus capacitor in whole Boost mode, which is equal to:

$$W_{cs2} := \sum_{t=t_x}^{\frac{T}{4}} P_1 \cdot T_s$$

(2.27)

Based on the assumption, the above equation can be converted to integration equation. By combining Eqs. 2.21 and 2.26, it yields:

$$W_{cs2} := \int_{t_x}^{\frac{T}{4}} \frac{D^2 \cdot T_s}{2 \cdot L_1} \cdot \frac{V_{cs} \cdot V_p^2 \cdot \sin(w \cdot t)^2}{V_{cs} - V_p \cdot \sin(w \cdot t)} dt$$

(2.28)

All output power is transferred via  $T_2$ . So, for each switching cycle,  $P_2$  is equal to  $P_0$ . The energy transferred by  $T_2$  is totally from DC bus capacitor in whole boost mode, which is equal to:

$$W_{cs3} := \sum_{t=t_x}^{\frac{T}{4}} P_2 \cdot T_s$$

(2.29)

Since P2 is equal to output power Po, so,

$$W_{cs3} := P_o \cdot \left(\frac{T}{4} - t_x\right) \tag{2.30}$$

#### 2.3.3 Final equation of Power Flow Analysis

For each line cycle, the discharging and charging energy from and into DC bus capacitor should be balanced to keep  $V_{cs}$  constant. So:

37

$$W_{cs2} = W_{cs1} + W_{cs3}$$

(2.31)

Use above equation, we get:

$$\int_{t_{x}}^{\frac{T}{4}} \frac{T_{s}}{2 \cdot L_{1}} \cdot \frac{n_{2}^{2} \cdot V_{o}^{2}}{\left(V_{cs} + n_{2} \cdot V_{o}\right)^{2}} \cdot \frac{V_{cs} \cdot V_{p}^{2} \cdot \sin(w \cdot t)^{2}}{V_{cs} - V_{p} \cdot \sin(w \cdot t)} dt = P_{o} \cdot \frac{T}{4} - \frac{V_{p}^{2} \cdot T_{s}}{2 \cdot L_{1}} \cdot \frac{n_{2}^{2} \cdot V_{o}^{2}}{\left(V_{cs} + n_{2} \cdot V_{o}\right)^{2}} \cdot \left(\frac{t_{x}}{2} - \frac{\sin(2 \cdot w \cdot t_{x})}{4 \cdot w}\right)$$

(2.32)

In the above equation, tx is the boundary time for flyback mode and boost mode. In first quarter of line period, Vin(t) is equal to Vcs - Vo\*n1 at  $t_x$ . So the boundary time for two modes is given by:

$$t_{x} = \arcsin\left(\frac{V_{cs} - n_{l} \cdot V_{o}}{V_{p}}\right)$$

(2.33)

Since the operation of this circuit is symmetrical over the line period, it is easy to obtain all mode boundary point for this topology, as shown in Fig. 2-7.

#### 2.3.4 Conditions fro DCM+CCM Operation

The above analysis is based on this assumption:  $T_1$  always runs at DCM, while  $T_2$  operates at CCM. In order to use those equations, we need to make sure the operation mode is correct for the specified circuit parameters.

For PFC transformer  $T_1$ , the heavy load and high charging voltage happens at T/4, while  $V_{in}(t) = V_{peak}$ . The charging voltage for  $T_1$  is  $V_{in}$ , while the discharging voltage is Vcs-Vin, so we get:

$$V_p \cdot D = (V_{cs} - V_p) \cdot D1 \tag{2.34}$$

So,

$$D1 := \frac{V_p \cdot D}{V_{cs} - V_p} \tag{2.35}$$

In order to keep  $T_1$  under DCM,  $D_1$  should be less than 1-D, so:

$$D < \frac{V_{cs} - V_p}{V_{cs}} \tag{2.36}$$

And, the duty cycle depends on DC/DC cell, which is constant:

$$D = \frac{n_2 \cdot V_0}{V_{cs} + n_2 \cdot V_0}$$

(2.37)

Combining the above equations, the condition for T<sub>1</sub> under DCM is given by:

$$V_{CS}^{2} - V_{CS}V_{P} - n_{2}V_{P}V_{Q} > 0 (2.38)$$

According to power flow chart in Fig. 2-7, the lightest load of DC/DC transformer  $T_2$  happens at the mode boundary  $t_x$ . If  $T_2$  runs under CCM at  $t_x$ , it will operate under CCM at any time. According to current waveform at CCM, we found that:

$$i_{22}(avg) > \frac{1}{2} \cdot \Delta i_{22} \cdot (1 - D)$$

(2.39)

while, i22 is the current through T2 secondary winding current. And

$$\Delta i_{22} := n_2 \cdot \Delta i_2 \tag{2.40}$$

$\Delta i_{22}$  is the current ripple in  $T_2$  secondary winding, and  $\Delta i_2$  is the current ripple in  $T_2$  primary winding. The current ripple of  $T_2$  during switch ON period is given by:

$$\Delta i_2 = \frac{V_{CS}DT_S}{L_2} \tag{2.41}$$

The power transferred by  $T_2$  is equal to:

$$P_2 = V_0 i_{22}(avg) (2.42)$$

Combining Eqs. 2.37 and 2.39 - 2.42, we obtain the minimum power for  $T_2$  under CCM is:

$$P_{2} > \frac{n_{2}^{2} \cdot V_{cs}^{2} \cdot V_{o}^{2} \cdot T_{s}}{2L_{2} \cdot (V_{cs} + n_{2} \cdot V_{o})^{2}}$$

(2.43)

At mode boundary  $t_x$ , the direct transferred power by  $T_1$  is equal to:

$$P_{1}(t_{x}) = \frac{V_{g}^{2}(t_{x})D^{2}T_{S}}{2L_{1}}$$

(2.44)

Since power transferred by  $T_2$  is the difference between output power an direct power transferred by  $T_1$ , we obtain the equation for  $P_2$  as follows:

$$P_2(t_x) = P_0 - \frac{V_g(t_x)^2 \cdot D^2 \cdot T_s}{2 \cdot L_1}$$

(2.45)

At mode boundary  $t_x$ , the input voltage is equal to  $V_{cs}$ - $n_1V_o$ . direct transferred power by  $T_1$  is equal to:

$$P_{o} - \frac{\left(V_{cs} - n_{1} \cdot V_{o}\right)^{2} \cdot T_{s}}{2 \cdot L_{1}} \cdot \frac{n_{2}^{2} \cdot V_{o}^{2}}{\left(V_{cs} + n_{2} \cdot V_{o}\right)^{2}} > \frac{n_{2}^{2} \cdot V_{cs}^{2} \cdot V_{o}^{2} \cdot T_{s}}{2L_{2} \cdot \left(V_{cs} + n_{2} \cdot V_{o}\right)^{2}}$$

(2.46)

Finally we obtain the requirement for T<sub>2</sub> under CCM by combining above equations as follows:

$$2L_{1}L_{2}P_{o}\left(V_{CS}+n_{2}V_{O}\right)^{2}-L_{2}T_{s}\left(n_{2}V_{O}V_{CS}-n_{1}n_{2}V_{o}^{2}\right)^{2}-L_{1}T_{s}n_{2}^{2}V_{CS}^{2}V_{o}^{2}>0$$

(2.47)

Those equations describe the relationship between intermediate bus voltage and other circuit parameters. But they are transcendental equations and are difficult to solve. Next chapter we will discuss in detail about how to solve those equations numerically by math software, such as MathCAD.

#### 2.4 Summary

By adding one winding to boost inductor, flyboost PFC cell can transfer some input power directly to output end. So the total power proceeded by power stage is reduced. There are two operation modes in one line cycle: flyback mode and boost mode. The period length of each mode depends on the input voltage, output voltage, intermediate bus voltage, and turn ratio of flyboost transformer. When the intermediate bus voltage goes high, the period of flyback mode increases, resulting in more power to output and less power to the bus capacitor. So it can limit the maximum intermediate bus voltage. Through one simple example, the operation of flyboost PFC cell was discussed in detail in this chapter. And one special analysis method, power flow method, was implemented to obtain critical equations for this kind of topology.

#### **CHAPTER 3**

# FLYBOOST PARALLEL/SERIES FORWARD SINGLE STAGE PFC CONVERTER

#### 3.1 Introduction

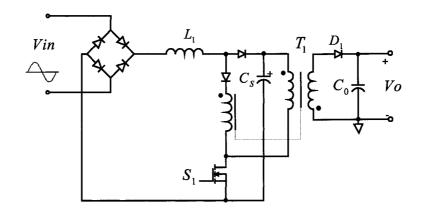

In previous chapter, Flyboost, the direct power transfer PFC cell, was introduced with one simple example. In actual application, that circuit suffers from very high voltage stress for universal application, even with the automatic voltage limit function. In this chapter, one practical topology is discussed in detail with design guide and experimental results.

The single stage Russian PFC topology in Fig. 3-1 shows some advantages due to its automatic voltage clamp function. When the main switch is on, two primary winding of DC-DC transformer T1 work in parallel to power the output inductor, like typical forward; while the main switch is turned off, two primary winding work in series to discharge the magnetizing energy back to intermediate bus caps, resulting in clamped voltage across main switch. The DC-DC circuit in Russian topology is called parallel/series forward converter. The maximum voltage stress should be always equal to the sum of two caps voltage, independent of the transformer leakage inductor. If we can control the intermediate bus voltage, then the voltage stress over the main switch is also

under control. In traditional Russian PFC topology, the voltage is controlled by letting the PFC cell and DC-DC cell operate under DCM. This method is simple and effective, but resulting in very high current stresses on main switch and secondary diodes. This disadvantage makes it impractical, especially for mediate power level, such as 200w.

Fig. 3-1. Russian single stage PFC converter

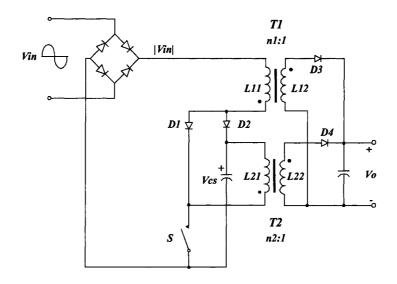

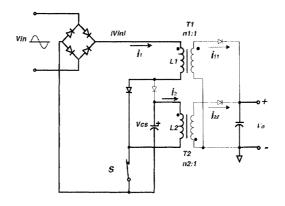

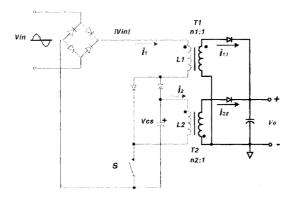

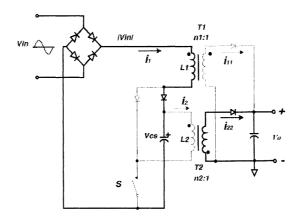

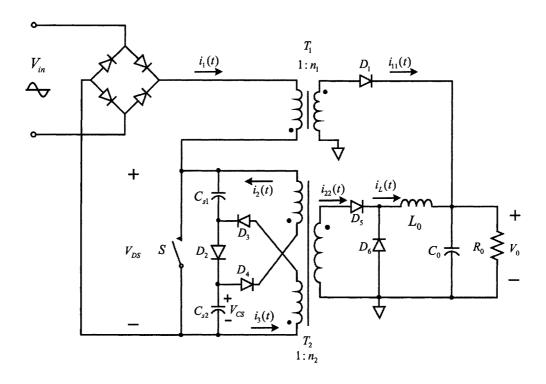

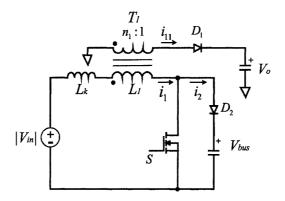

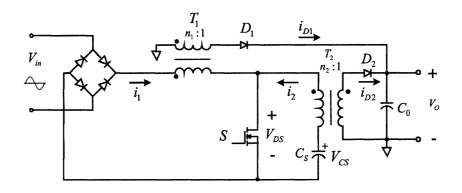

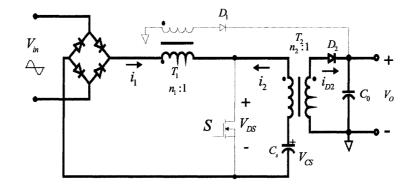

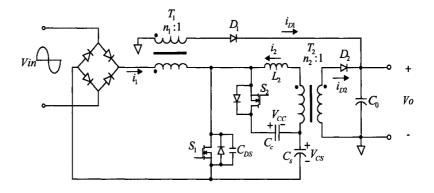

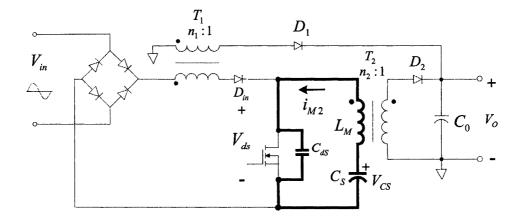

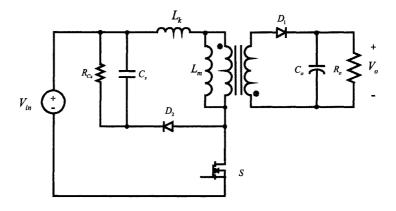

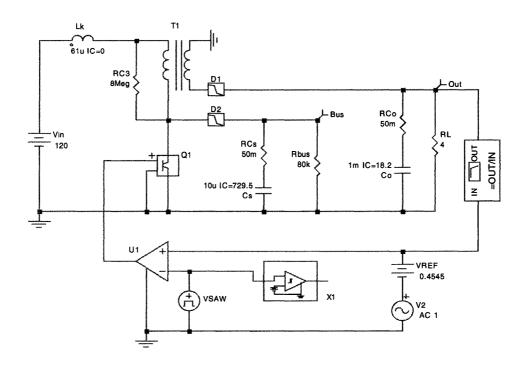

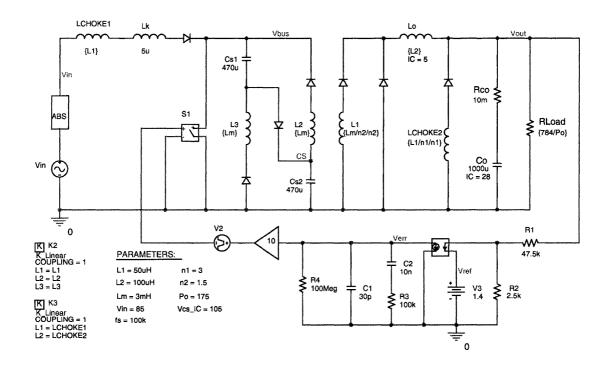

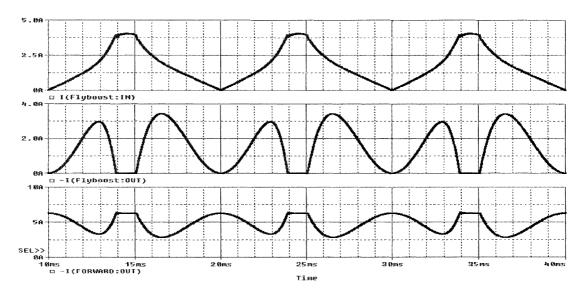

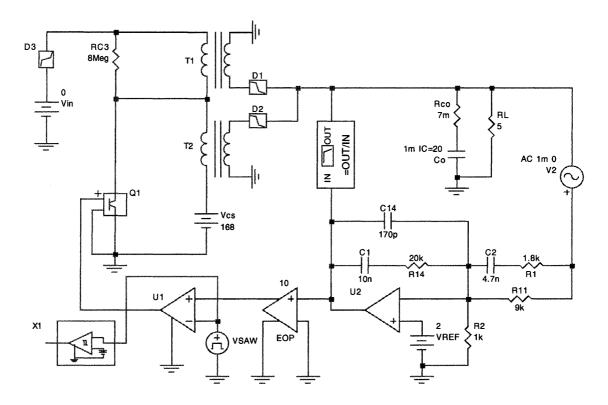

In this chapter, this topology is integrated with flyboost PFC cell to achieve better results. As discussed in previous chapter, flyboost PFC can let the DC-DC cell operate under CCM and limit the intermediate bus voltage at the same time. The flyboost-parallel/series forward single stage PFC topology, shown in Fig. 3-2, inherits the advantage from both ideas.

The topology shown in Fig. 3-2 is based on the flyboost PFC scheme and a parallel/series forward DC/DC conversion cell. The flyboost PFC cell, including transformer  $T_1$ , input bridge rectifier, two intermediate bus capacitors ( $C_{s1}$  and  $C_{s2}$ ), diode  $D_1$  and  $D_2$ , and active switch S, operates in DCM to achieve high power factor and

transfers some input power to the output directly. The parallel/series forward DC-DC conversion cell, which consists of bus capacitors ( $C_{s1}$  and  $C_{s2}$ ), forward transformer  $T_2$ , output inductor  $L_o$ , output capacitor  $C_o$ , diodes and switch S, converts the stored intermediate bus voltage to the output and achieves tight output voltage regulation. Both cells share bus capacitors, the only active switch S and controller.

Fig. 3-2. flyboost-parallel/series forward single stage PFC converter

The operation of this topology is discussed in detail below, and design procedure is provided with one example. And experimental results from the example prototype are given to verify the analysis and design.

#### 3.2 Operation Description

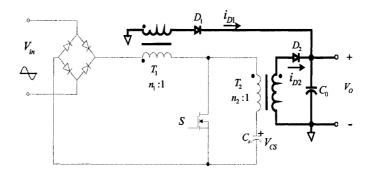

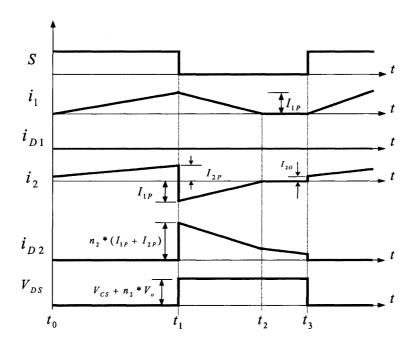

Just like typical single-stage PFC topologies, the flyboost PFC cell and DC-DC conversion cell in this topology operate independently, although both cells share the only one switch. But the operation of this topology differs from other typical schemes by its special operation modes and parallel power flow feature. There are two different modes in one line cycle, depending on the instantaneous input voltage and the bus voltage, as shown in Fig. 3-3(a). When input voltage is low, diode D<sub>1</sub> in transformer T<sub>1</sub> secondary side will conduct during switch OFF interval, and T<sub>1</sub> works like a flyback transformer. It is referred to flyback mode; while input voltage goes higher, T<sub>1</sub> will operate like a boost inductor to charge intermediate bus capacitors. It is called as boost mode.

In the following discussion, the DCM operation will be assumed for the PFC cell to achieve high power factor, and the CCM operation for the DC-DC conversion cell to reduce the current stress on the switches. To simplify the analysis, all components here are assumed to be ideal without parasitic parameters, and the ripple voltage across bulky capacitors is neglected.

Following are the detailed operation description of the above topology in one switching cycle for each different operation mode.

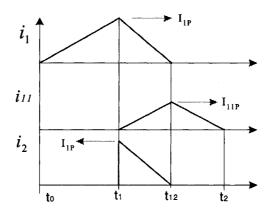

#### 3.2.1 Flyback operation mode

When rectified line voltage  $|V_{in}(t)|$  is less than  $V_{bus}$ - $n_1V_o$  ( $V_{bus}$ : bus voltage, equal to the sum of the voltage across two intermediate bus capacitors;  $n_1$ : the turn ratio of T1;  $V_o$ : output voltage), Transformer  $T_1$  works like a flyback transformer to discharge all stored input power directly to the load. And this portion of load power is processed by the active switch S only once. Meanwhile, DC-DC cell will deliver some power from bus capacitors to the load to keep tight output voltage regulation. The operational waveforms are shown in Fig. 3-3(b).

Interval 1 ( $t_0 \sim t_1$ ): Switch S is turned on at  $t_0$ . The rectified line voltage  $|V_{in}(t)|$  is applied to primary winding of  $T_1$ . The current in  $T_1$ ,  $i_1$  in Fig. 3-3(b), increases linearly. Since PFC cell operates in DCM,  $i_1$  starts increasing from zero. The bus capacitors voltage  $V_{CS}$  is applied to output inductor Lo through transformer  $T_2$ , causing its current  $i_L$  to linearly increase also. The special configuration of parallel/series forward conversion cell will automatically keep the voltage across two bus capacitors always balanced: since the higher voltage in one capacitor will keep another capacitor from discharging during interval, it will bring down the higher voltage to equal to another voltage. So we assume those capacitor voltages are same and equal to half of bus voltage. Based on above analysis, we have:

$$L_{1}\frac{di_{1}(t)}{dt} = |V_{in}(t)| \tag{3.1}$$

$$L_O \frac{di_L(t)}{dt} = \frac{V_{cs}}{n_2} - V_O = \frac{V_{bus}}{2n_2} - V_O$$

(3.2)

where  $L_1$  is the primary inductance of transformer  $T_1$ , Lo is output filter inductor, n2 is the turn ratio of  $T_2$ .

Interval 2  $(t_1 \sim t_2)$ : S is turned off at  $t_1$ .  $T_1$  discharges through its secondary winding and deliveries its stored magnetizing energy to the load, resulting in the voltage across  $T_1$  primary winding clamped to  $n_1V_0$ . The current in output inductor  $L_0$  will flow through freewheel diode  $D_6$ . Transformer  $T_2$  will reset its magnetizing energy to bus capacitors through diode  $D_2$ - $D_4$ , thanks to its special circuit configuration. And the voltage across switch S is clamped by two bus capacitors, resulting in switch S free of spike voltage caused by leakage inductance existing in other topologies. We have:

$$L_{11} \frac{di_{11}(t)}{dt} = -V_O \tag{3.3}$$

$$L_O \frac{di_L(t)}{dt} = -V_O \tag{3.4}$$

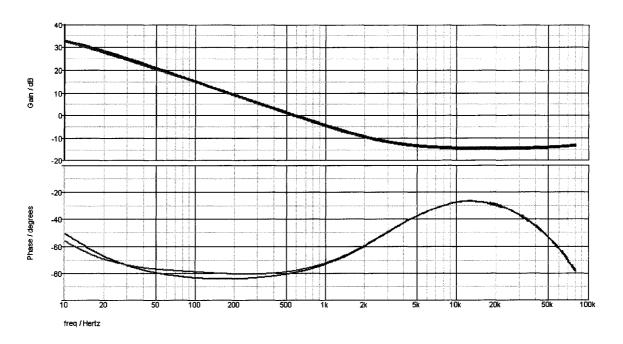

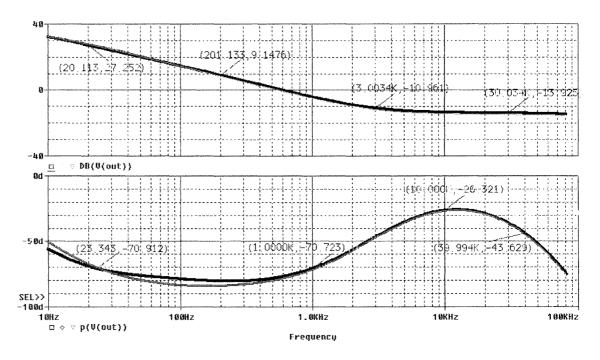

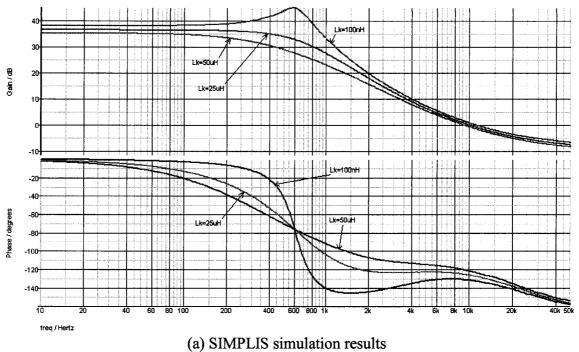

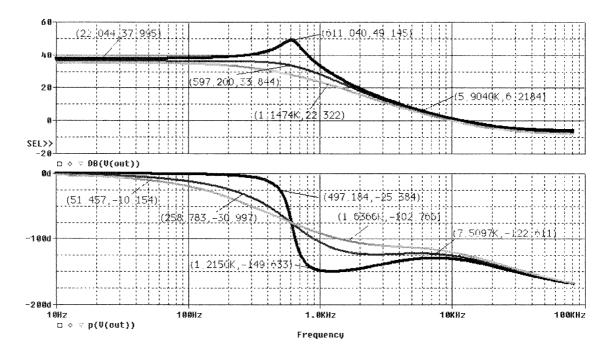

where  $L_{11}$  is the secondary inductance of transformer  $T_1$ .