## MODELING AND DESIGN OF MULTI-PORT DC/DC CONVERTERS

by

## ZHIJUN QIAN B.S. Zhejiang University, 2005 M.S. Zhejiang University, 2007

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2010

Major Professor: Issa Batarseh

$\odot$  2010 ZHIJUN QIAN

To my wife

#### **ABSTRACT**

In this dissertation, a new satellite platform power architecture based on paralleled three-port DC/DC converters is proposed to reduce the total satellite power system mass. Moreover, a four-port DC/DC converter is proposed for renewable energy applications where several renewable sources are employed. Compared to the traditional two-port converter, three-port or four-port converters are classified as multi-port converters. Multi-port converters have less component count and less conversion stage than the traditional power processing solution which adopts several independent two-port converters. Due to their advantages multi-port converters recently have attracted much attention in academia, resulting in many topologies for various applications. But all proposed topologies have at least one of the following disadvantages: 1) no bidirectional port; 2) lack of proper isolation; 3) too many active and passive components; 4) no softswitching. In addition, most existing research focuses on the topology investigation, but lacks study on the multi-port converter's control aspects, which are actually very challenging since it is a multi-input multi-output control system and has so many cross-coupled control loops.

A three-port converter is proposed and used for space applications. The topology features bidirectional capability, low component count and soft-switching for all active switches, and has one output port to meet certain isolating requirements. For the system level control strategy, the multi-functional central controller has to achieve maximal power harvesting for the solar panel, the battery charge control for the battery, and output voltage regulation for the dc bus. In order to design these various controllers, a good dynamic model of the control object should be obtained first. Therefore, a modeling procedure based on a traditional state-space averaging method is

proposed to characterize the dynamic behavior of such a multi-port converter. The proposed modeling method is clear and easy to follow, and can be extended for other multi-port converters.

In order to boost the power level of the multi-port converter system and allow redundancy, the three-port converters are paralleled together. The current sharing control for the multi-port converters has rarely been reported. A so called "dual loop" current sharing control structure is identified to be suitable for the paralleled multi-port converters, since its current loop and the voltage loop can be considered and designed independently, which simplifies the multi-port converter's loop analysis. The design criteria for that dual loop structure are also studied to achieve good current sharing dynamics while guaranteeing the system stability.

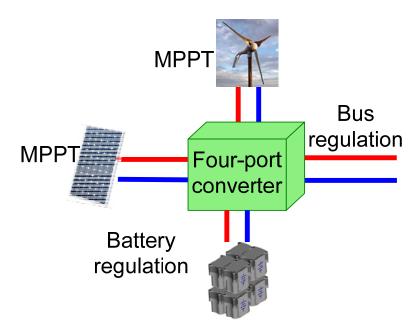

The renewable energy applications are continuously demanding the low cost solution, so that the renewable energy might have a more competitive dollar per kilowatt figure than the traditional fossil fuel power generation. For this reason, the multi-port converter is a good candidate for such applications due to the low component count and low cost. Especially when several renewable sources are combined to increase the power delivering certainty, the multi-port solution is more beneficial since it can replace more separate converters. A four-port converter is proposed to interface two different renewable sources, such as the wind turbine and the solar panel, one bidirectional battery device, and the galvanically isolated load. The four-port converter is based on the traditional half-bridge topology making it easy for the practicing power electronics engineer to follow the circuit design. Moreover, this topology can be extended into *n* input ports which allow more input renewable sources.

Finally, the work is summarized and concluded, and references are listed.

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to my advisor, Professor Issa Batarseh, for his efforts to plant the seeds of this work, his constant assistance and support, and whose personality, leadership experience and critical thinking provided an exemplary example for me to follow.

I would also like to thank Dr. Oasam Abdel-Rahman for his training and advising and the members of the ApECOR team: John Elmes, Rene Kersten, Keith Mansfield and Michael Pepper, for their support. In addition, I would like to express my appreciation to my colleagues at the Power Electronics Laboratory.

Special thanks are also extended to my dissertation approval committee members, Professor Issa Batarseh, Professor John Z. Shen, Professor Wasfy Mikhael, Professor Thomas X. Wu, Professor Louis Chow and Dr. Hussam J. Al-Atrash. I am grateful to the University of Central Florida faculty and staff for their cooperation and would like to thank Ms. Theresa Collins for her invaluable editing work on my dissertation.

Finally, I would like to express my undying love and gratitude to my mother, Yu Liping, my father, Qian Huixing, and last but not least, my lovely wife, Hu Ting, and her family, whose love, encouragement and support have been the root of my success.

This work is supported partially by several agencies and companies including NASA, Advanced Power Electronics Corporation, and the University of Central Florida.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                              | xi  |

|--------------------------------------------------------------|-----|

| LIST OF TABLES                                               | xix |

| CHAPTER 1: INTRODUCTION                                      | 1   |

| 1.1. Background for Satellite Applications                   | 1   |

| 1.2. Background for Renewable Energy Applications            | 7   |

| 1.3. Outline of Dissertation                                 | 11  |

| CHAPTER 2: LITERATURE REVIEW                                 | 15  |

| 2.1. Multi-input Converters                                  | 16  |

| 2.2. Multi-port Converters                                   | 20  |

| 2.3. Summary                                                 | 24  |

| CHAPTER 3: AN INTEGRATED THREE-PORT DC/DC CONVERTER: CIRCUIT | T   |

| ANALYSIS, MODELING AND CONTROL                               | 27  |

| 3.1. General Description                                     | 27  |

| 3.2. Circuit and Topology                                    | 27  |

| 3.2.1. Circuit Operation Principles                          | 28  |

| 3.2.2. ZVS Analysis                                          | 36  |

| 3.2.3. DC Analysis                                           | 37  |

| 3.3. Modeling and Control                                    | 38  |

| 3.3.1. Mode Definition.                                      | 38  |

| 3.3.2. Control Structure                                     | 41  |

| 3.3.3. Autonomous Mode Transitions                                | 43  |

|-------------------------------------------------------------------|-----|

| 3.3.4. Converter Modeling and Controller Design                   | 48  |

| 3.4. Experimental Results                                         | 62  |

| CHAPTER 4: PARALLEL OPERATION OF MULTIPLE THREE-PORT              |     |

| CONVERTERS                                                        | 77  |

| 4.1. General Description                                          | 77  |

| 4.2. Current Sharing for Two Paralleled Converters                | 77  |

| 4.2.1. Output Port Current Sharing for Two Paralleled Converters  | 78  |

| 4.2.2. Modeling of Dual-loop Current Sharing Structure            | 81  |

| 4.2.3. Battery Port Current Sharing for Two Paralleled Converters | 88  |

| 4.2.4. Input Port Current Sharing for Two Paralleled Converters   | 94  |

| 4.3. Experiments for Two Three-port Converters                    | 97  |

| 4.4. Multi-channel Paralleled Three-port Converters               | 103 |

| 4.4.1. Output Port Hybrid Current Sharing Method                  | 107 |

| 4.4.2. Synchronization Among Different Channels                   | 112 |

| 4.5. Experiments for Multiple Three-port Converters               | 115 |

| CHAPTER 5: AN INTEGRATED FOUR-PORT DC/DC CONVERTER                | 120 |

| 5.1. General Description                                          | 120 |

| 5.2. Topology                                                     | 121 |

| 5.2.1. Driving Scheme                                             | 123 |

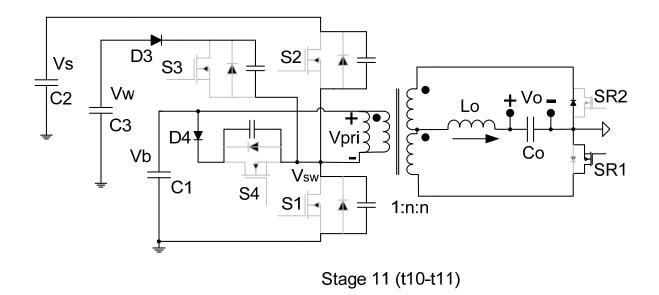

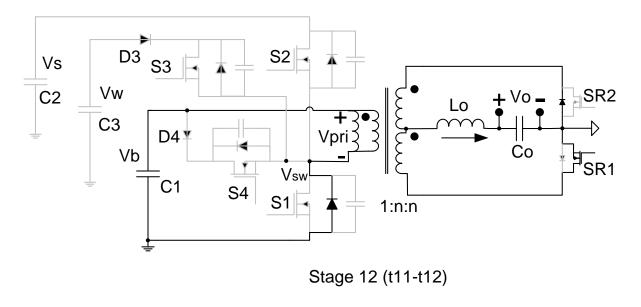

| 5.2.2. Circuit Operation Principles                               | 125 |

| 5.2.3. Steady State Analysis             | 134 |

|------------------------------------------|-----|

| 5.2.4. ZVS Analysis                      | 134 |

| 5.2.5. Circuit Design Considerations     | 136 |

| 5.2.6. Semiconductor Stresses            | 137 |

| 5.2.7. Transformer Turns Ratio           | 138 |

| 5.3. Modeling and Control                | 139 |

| 5.3.1. Various Modes of Operation        | 139 |

| 5.3.2. Control Structure                 | 142 |

| 5.3.3. Converter Modeling                | 143 |

| 5.3.4. Decoupling Method                 | 146 |

| 5.4. Experimental Results                | 147 |

| 5.5. Extension into Multi-port Converter | 155 |

| CHAPTER 6: CONCLUSIONS AND FUTURE WORK   | 157 |

| 6.1. Major Contributions                 | 157 |

| 6.2. Future Work                         | 159 |

| REFERENCES                               | 161 |

# LIST OF FIGURES

| Fig. 1. 1: Typical terminal characteristics of a solar array, (a) irradiance variations, (b) |    |

|----------------------------------------------------------------------------------------------|----|

| temperature variations.                                                                      | 4  |

| Fig. 1. 2: Multiple converter solutions for the satellite platform power system.             | 6  |

| Fig. 1. 3: Satellite power system includes platform power system sourcing by solar panels    |    |

| and batteries, and user power system sinking by various types of user loads                  | 6  |

| Fig. 1. 4: The wind turbine characteristics of power V <sub>s</sub> . rotor speed            | 10 |

| Fig. 1. 5: The wind turbine P-V characteristics.                                             | 11 |

|                                                                                              |    |

| Fig. 2. 1: Multi-input buck-boost converter                                                  | 16 |

| Fig. 2. 2: Multi-input flyback converter                                                     | 17 |

| Fig. 2. 3: Multi-input flyback converter with a multi-winding transformer                    | 18 |

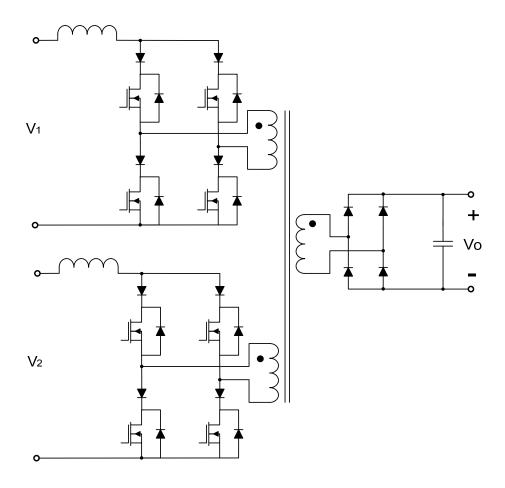

| Fig. 2. 4: Two-input current-fed full-bridge dc/dc converter                                 | 19 |

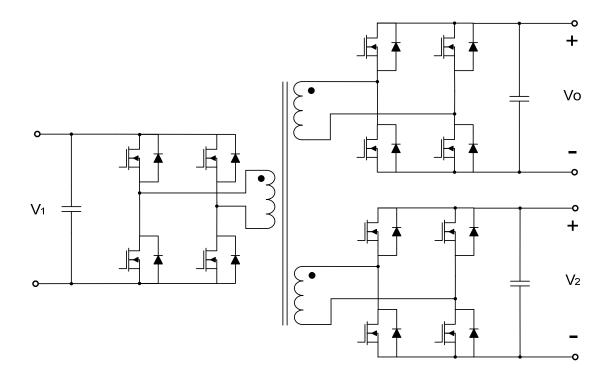

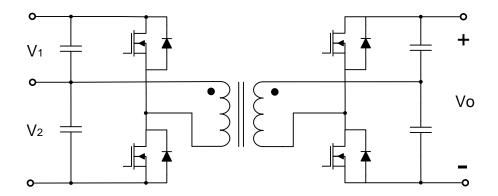

| Fig. 2. 5: Three-port full-bridge dc/dc converter                                            | 21 |

| Fig. 2. 6: Three-port half-bridge dc/dc converter                                            | 22 |

| Fig. 2. 7: Triple-half-bridge bidirectional dc/dc converter                                  | 23 |

| Fig. 2. 8: Reduced part, triple-half-bridge bidirectional dc/dc converter                    | 24 |

|                                                                                              |    |

| Fig 3. 1: Three-port modified half-bridge converter topology, which can achieve ZVS for      |    |

| all three main switches (S1, S2, S3) and adopt synchronous rectification for the             |    |

| secondary side to minimize conduction loss.                                                  | 28 |

| Fig 3. 2: Steady state waveforms of the three-port half-bridge converter                     | 30 |

| Fig 3. 3: Operation stages of the three-port half-bridge converter                                  | 35 |

|-----------------------------------------------------------------------------------------------------|----|

| Fig 3. 4: Different operational modes in satellite's one orbit cycle. Three-port converter          |    |

| can achieve MPPT, battery charge control and load regulation depending on                           |    |

| available solar power, battery state of charge and load profile. In stage I,                        |    |

| battery acts as the exclusive source during eclipse period. In stage II&III, solar                  |    |

| power is maximized to decrease battery state of discharge in stage II for initial                   |    |

| insolation period and then to increase battery state of charge in stage III for                     |    |

| increased insolation period. In stage IV, battery charge control is applied to                      |    |

| prevent battery over-charging and extend battery service life.                                      | 41 |

| Fig 3. 5: Three-port converter's control architecture to achieve MPPT for solar port,               |    |

| battery charge control for battery port and meanwhile always maintaining                            |    |

| voltage regulation for output port. OVR is to control d <sub>1</sub> , and the rest of control      |    |

| loops (BVR, BCR and IVR) are competing the minimum value to control d <sub>2</sub>                  | 42 |

| Fig 3. 6: (a) Conventional mode transition algorithm flow chart which is inclined to                |    |

| cause oscillation; (b) Oscillation between Mode 1 and Mode 2 because of                             |    |

| instant switching of duty cycle value                                                               | 45 |

| Fig 3. 7: (a) the proposed minimum function competitive method to allow smooth                      |    |

| transition of modes; (b) Mode 1 to Mode 2 transition with no oscillation; (c)                       |    |

| Mode 2 to Mode 1 transition with no oscillation.                                                    | 47 |

| Fig 3. 8: Basic waveforms of the three-port converter. $v_{pri}$ and $i_{Lo}$ represent transformer |    |

| primary side voltage and output inductor current respectively                                       | 49 |

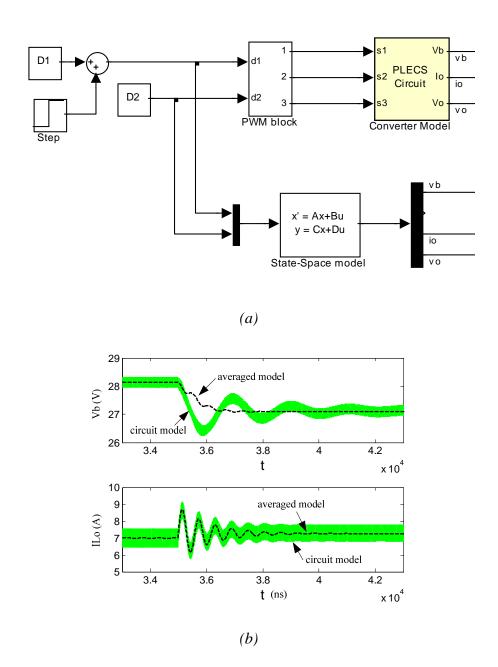

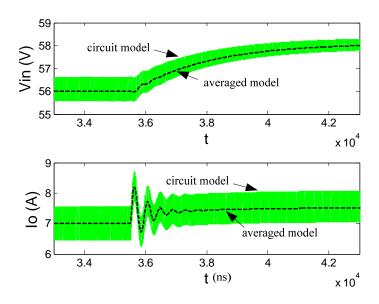

| Fig 3. 9: (a) Model comparison due to duty cycle step, (b) Averaged model and circuit                  |    |

|--------------------------------------------------------------------------------------------------------|----|

| model comparison for Battery-regulation Mode.                                                          | 54 |

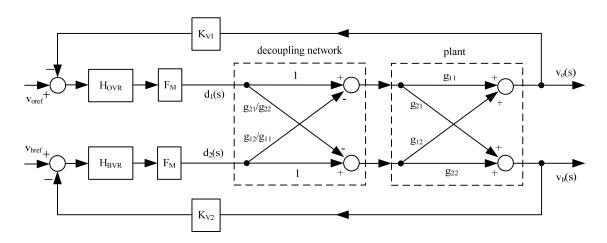

| Fig 3. 10: Small signal model of Battery-regulation Mode, control inputs and outputs are               |    |

| decoupled to enable separate controller design. $V_{\text{oref}}$ and $V_{\text{bref}}$ are the        |    |

| references for output voltage and battery voltage, respectively. $H_{\text{OVR}}$ and $H_{\text{BVR}}$ |    |

| are the compensators need to be designed.                                                              | 55 |

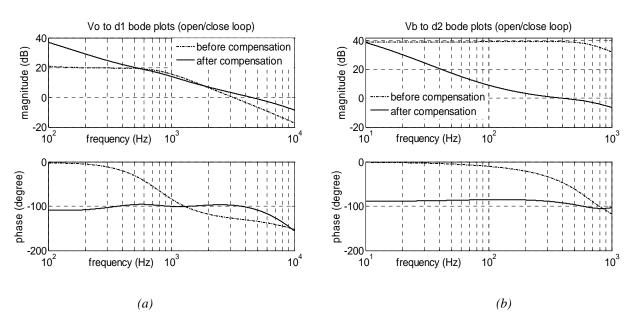

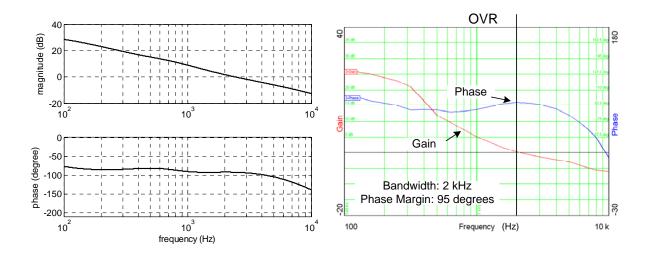

| Fig 3. 11: Simulated bode plots for Battery-regulation Mode, (a) $V_o(s)/d_1(s)$ ; (b) $V_b(s)/d_1(s)$ |    |

| d <sub>2</sub> (s). Dashed line denotes open loop plant transfer function before applying              |    |

| the compensator, solid line denotes close loop transfer function after applying                        |    |

| the compensator. BVR loop bandwidth is set to be one tenth of that of OVR                              | 58 |

| Fig 3. 12: Averaged model and circuit model comparison for Battery-balanced Mode                       | 60 |

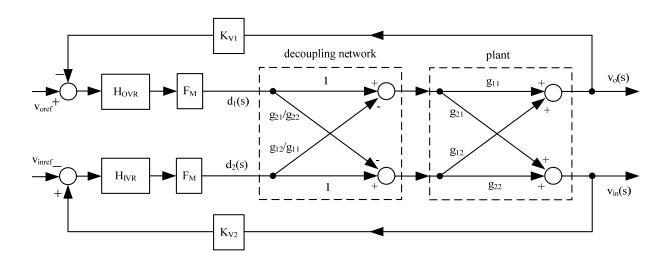

| Fig 3. 13: Small signal model of Battery-balanced Mode, control inputs and outputs are                 |    |

| decoupled to enable separate controller design. $V_{\text{oref}}$ and $V_{\text{inref}}$ are the       |    |

| references for output voltage and input voltage, respectively. $H_{\text{OVR}}$ and $H_{\text{IVR}}$   |    |

| are the compensators need to be designed.                                                              | 60 |

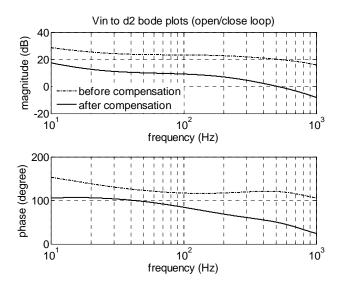

| Fig 3. 14: Simulated bode plots of $V_{in}(s)/\ d_2(s)$ . Dashed line denotes open loop plant          |    |

| transfer function before applying the compensator, solid line denotes close                            |    |

| loop transfer function after applying the compensator.                                                 | 62 |

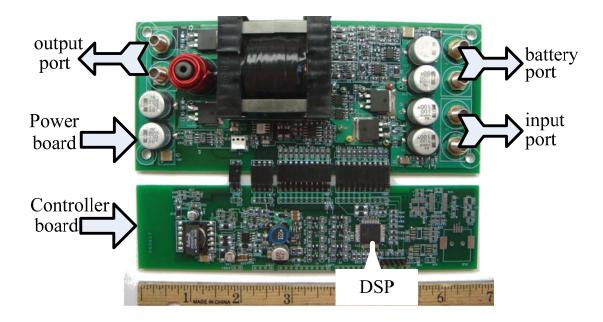

| Fig 3. 15: Prototype photo of three-port converter which consists of one controller board              |    |

| and one power board.                                                                                   | 63 |

| Fig 3. 16: Loading output port when the battery current is zero                                        | 64 |

| Fig 3. 17: Loading battery port when the output current is zero                                        | 64 |

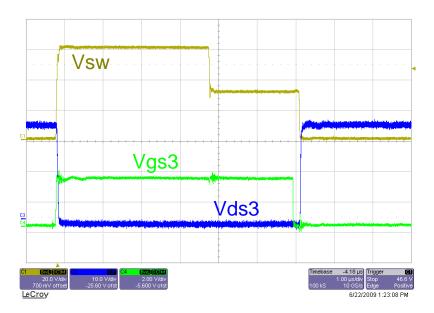

| Fig 3. 18: ZVS for S1                                                                                      | . 65 |

|------------------------------------------------------------------------------------------------------------|------|

| Fig 3. 19: ZVS for S2                                                                                      | . 65 |

| Fig 3. 20: ZVS for S3                                                                                      | . 66 |

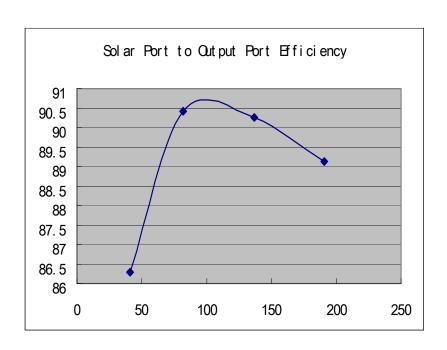

| Fig 3. 21: The efficiency when the power is transferred from solar port to output port                     | . 67 |

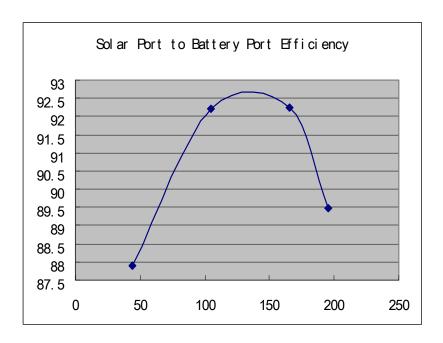

| Fig 3. 22: The efficiency when the power is transferred from solar port to battery port                    | . 67 |

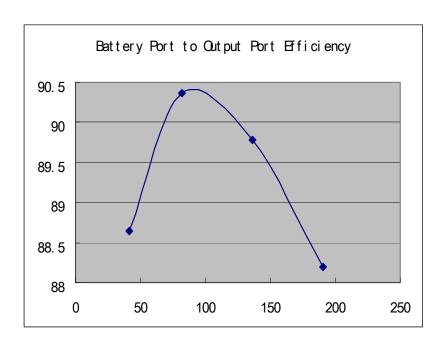

| Fig 3. 23: The efficiency when the power is transferred from battery port to output port                   | . 68 |

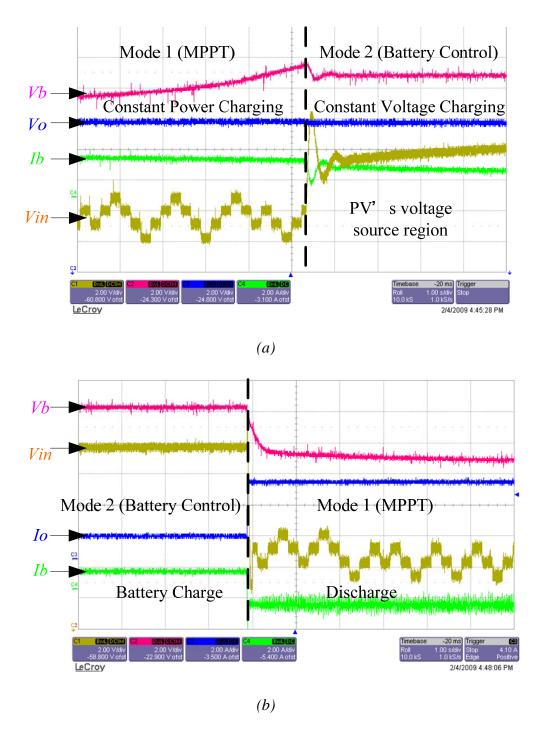

| Fig 3. 24: Autonomous mode transition, (a) Mode 1 to Mode 2; (b) Mode 2 to Mode 1                          | . 70 |

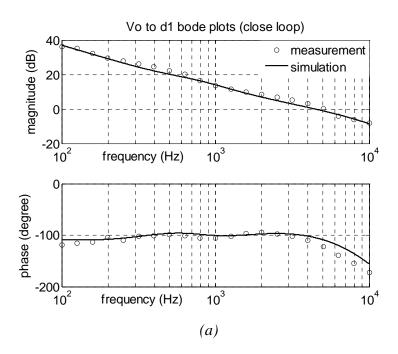

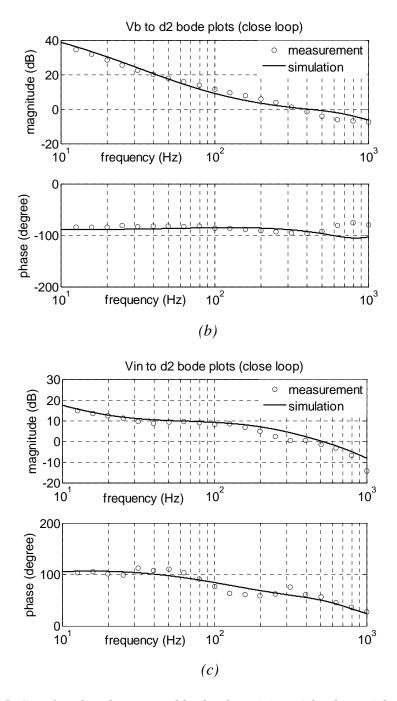

| Fig 3. 25: Simulated and measured bode plots, (a) $V_o$ / $d_1$ , (b) $V_b$ / $d_2$ , (c) $V_{in}$ / $d_2$ | . 72 |

| Fig 3. 26: (a) Battery-regulation Mode load step response, (b) Battery-balanced Mode                       |      |

| load step response.                                                                                        | . 74 |

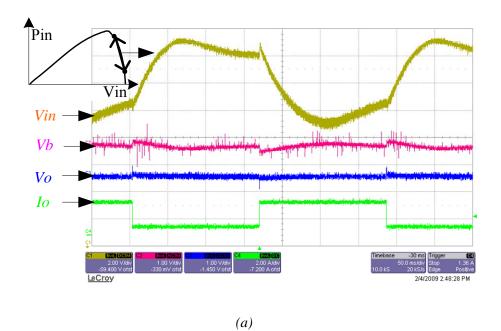

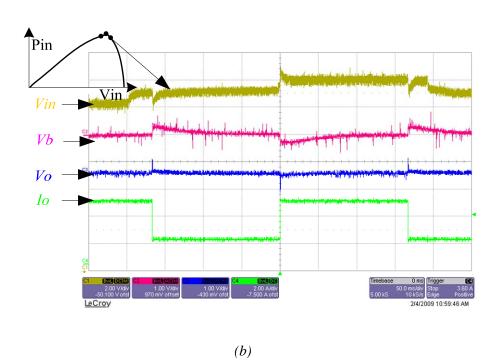

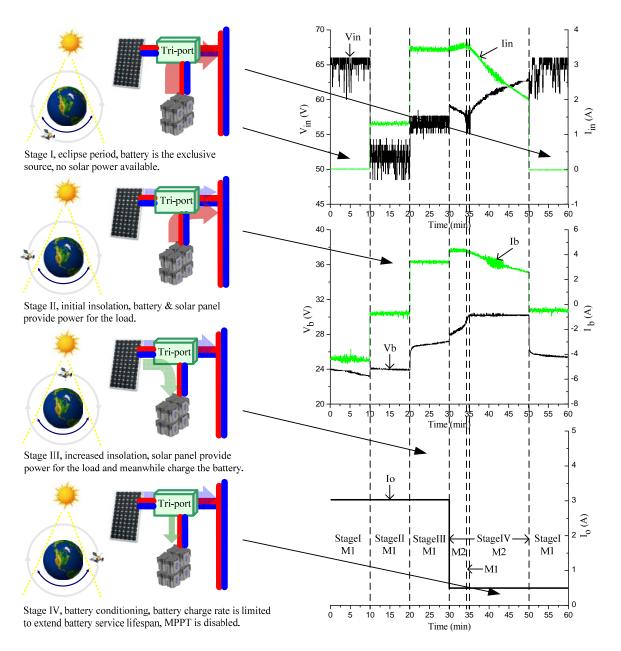

| Fig 3. 27: Different mode operations based on available solar power, battery state of                      |      |

| charge and load profile, left column shows four stages in satellite's one orbit                            |      |

| cycle; for the right column, top one shows input solar panel voltage and                                   |      |

| current, middle one represents battery voltage and current, bottom one shows                               |      |

| output port load level while its voltage is maintaining regulated all the time                             | . 76 |

|                                                                                                            |      |

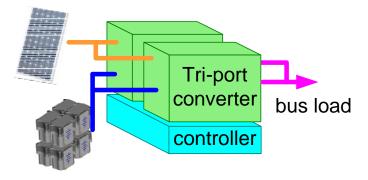

| Fig.4. 1: Paralleled three-port converter system interfacing solar panel, battery pack and                 |      |

| bus                                                                                                        | . 78 |

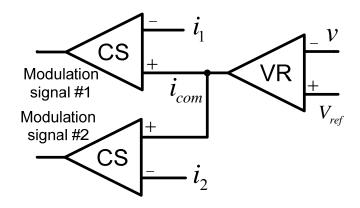

| Fig.4. 2: Dual loop CS control structure                                                                   | . 79 |

| Fig.4. 3: Outer voltage loop and inner CS loop control structure                                           | . 80 |

| Fig.4. 4: Inner voltage loop and outer CS loop control structure                                           | . 80 |

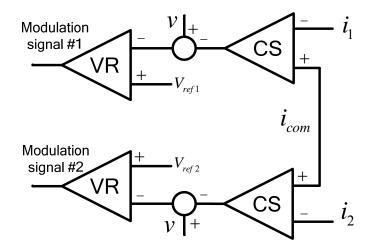

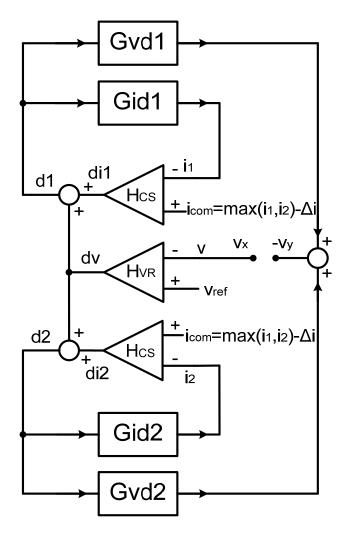

| Fig.4. 5: Loop analysis of output port with two paralleled converters, Gid and Gvd are    |    |

|-------------------------------------------------------------------------------------------|----|

| already obtained from section II (battery port control loop diagram is similar            |    |

| with output port)                                                                         | 84 |

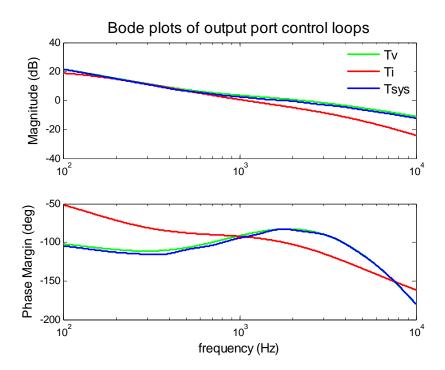

| Fig.4. 6: Calculated bode plots of output port control loops                              | 85 |

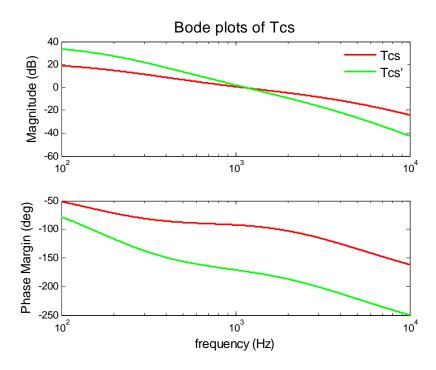

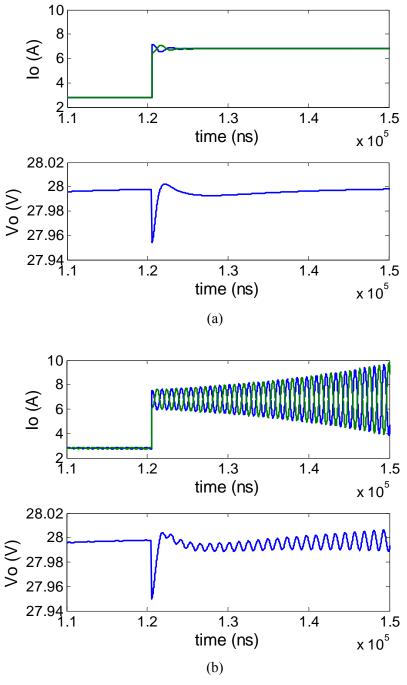

| Fig.4. 7: Bode plots of CS loop gain Tcs, stable and unstable                             | 86 |

| Fig.4. 8: Transient response to load steps from 40% to 100%, (a) stable CS loop gain Tcs; |    |

| (b) unstable CS loop gain Tcs'                                                            | 87 |

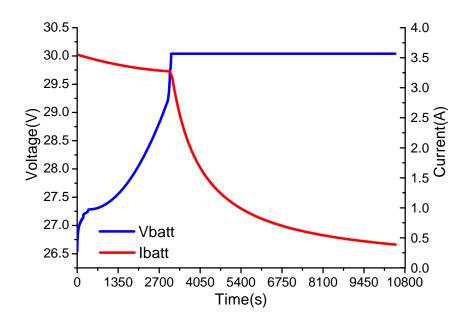

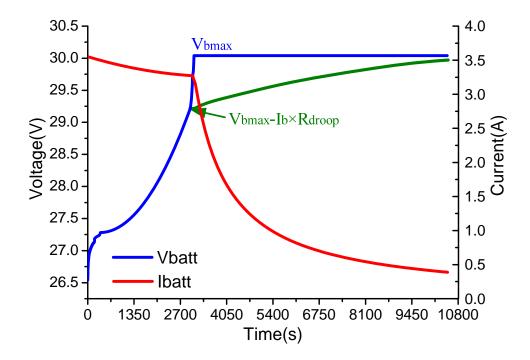

| Fig.4. 9: Battery two stage charging profile                                              | 89 |

| Fig.4. 10: Solar array irradiance changes, then battery charging power changes            |    |

| accordingly                                                                               | 89 |

| Fig.4. 11: Load level changes, then battery charging power changes accordingly            | 90 |

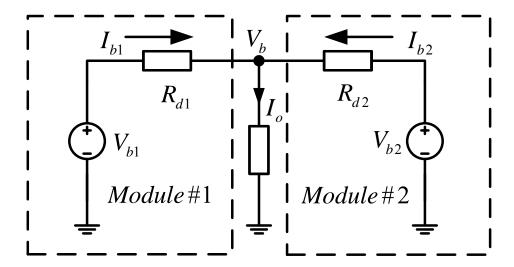

| Fig.4. 12: Battery output model with droop resistances                                    | 91 |

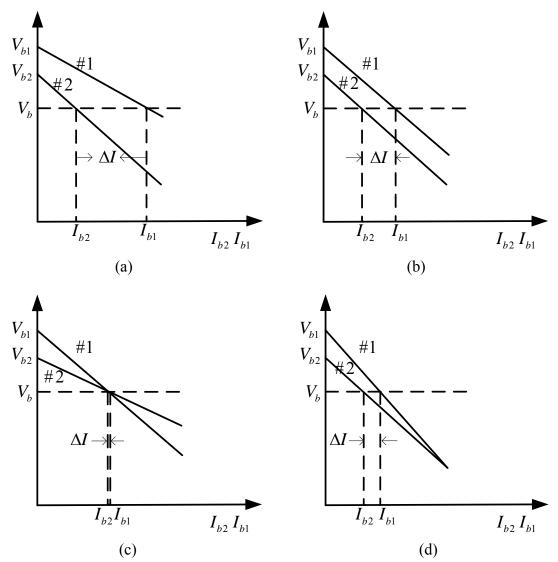

| Fig.4. 13: Effect of different droop rate on CS error (a) undesirable (b) acceptable (c)  |    |

| good, zero error at 50% (d) good, zero error at 100%                                      | 93 |

| Fig.4. 14: Battery charging algorithm with CS.                                            | 94 |

| Fig.4. 15: Input port current sharing diagram                                             | 95 |

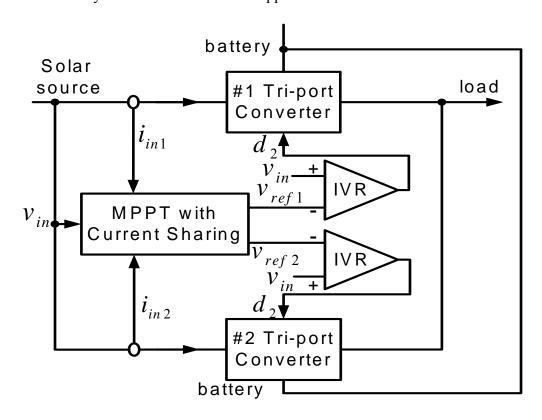

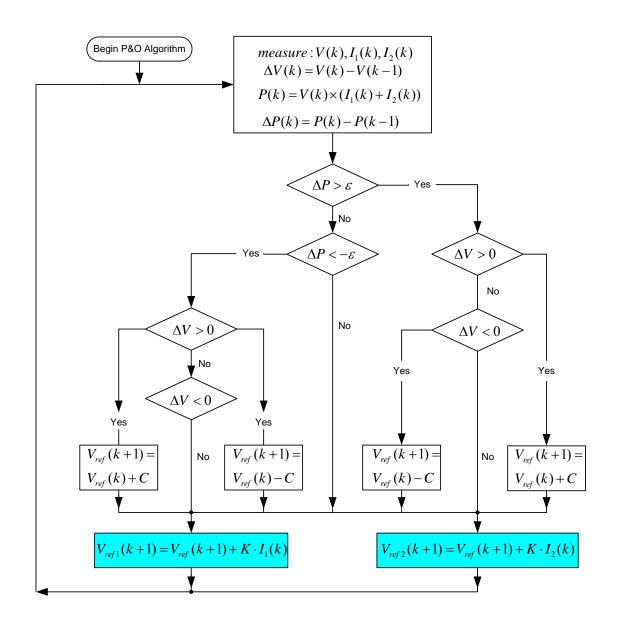

| Fig.4. 16: Perturb&Observe MPPT algorithm with CS                                         | 96 |

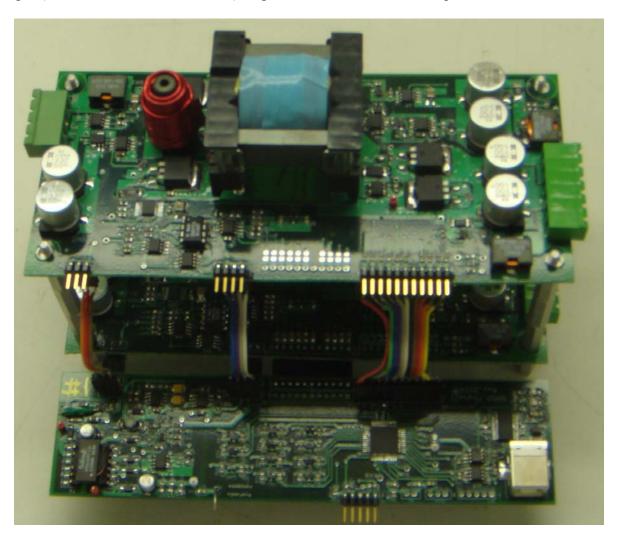

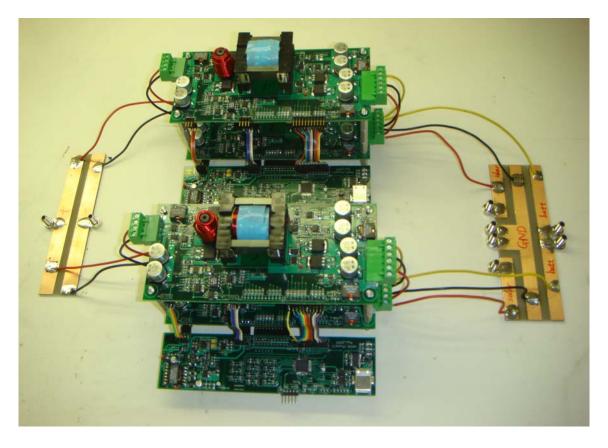

| Fig.4. 17: Prototype photo of two paralleled converters sharing with one DSP controller   |    |

| board, each power stage is rated at 200W, input port and battery port has the             |    |

| same ground while output port is isolated.                                                | 97 |

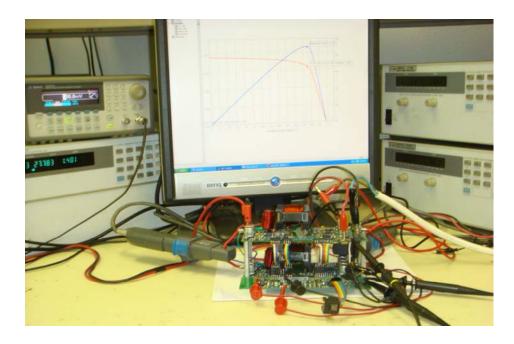

| Fig.4. 18: Test setup with two paralleled three-port converters                           | 98 |

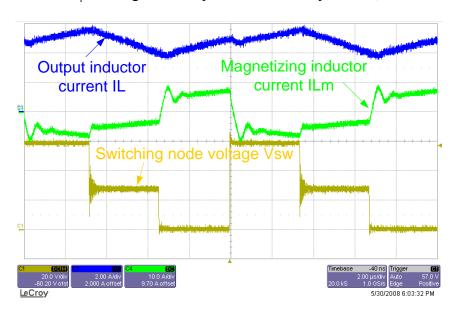

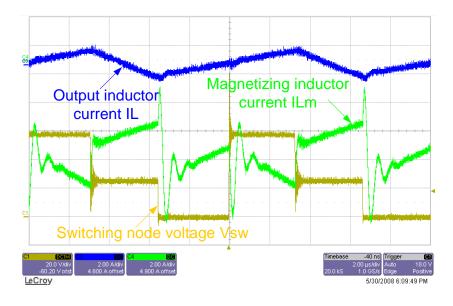

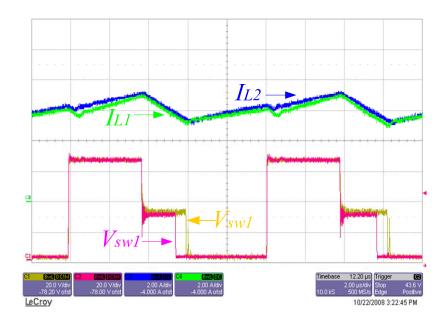

| Fig.4. 19: Steady state waveforms for output inductor current and switching node voltage  | 99 |

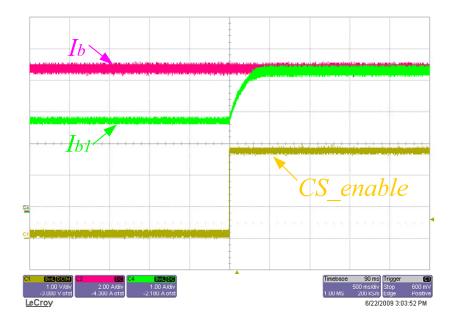

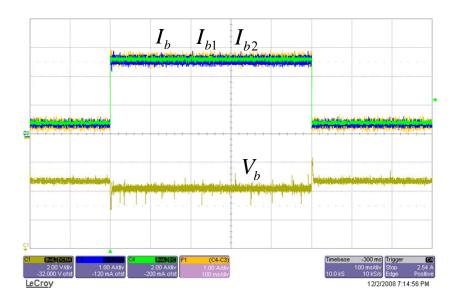

| Fig.4. 20: Current sharing performance before and after CS function enabled                               | 99  |

|-----------------------------------------------------------------------------------------------------------|-----|

| Fig.4. 21: Current sharing performance before and after CS function enabled                               | 100 |

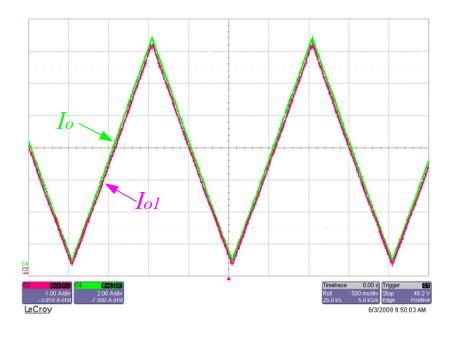

| Fig.4. 22: Output port load sweep (0.5-14A)                                                               | 100 |

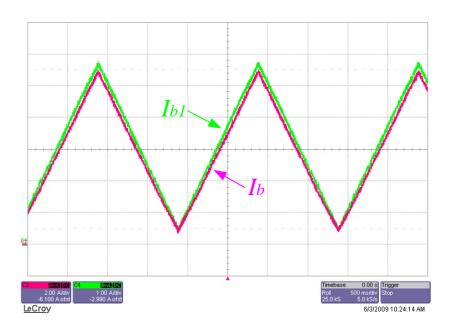

| Fig.4. 23: Battery port load sweep (0.5-11A)                                                              | 101 |

| Fig.4. 24: Battery load transient (1-5.5A)                                                                | 101 |

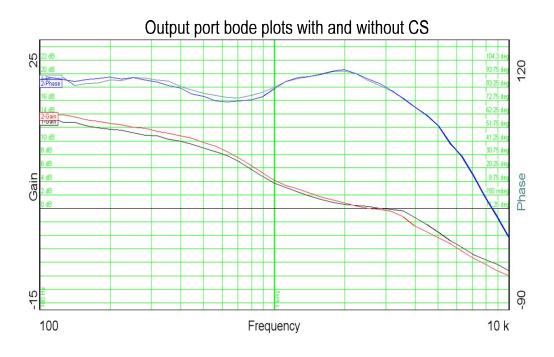

| Fig.4. 25: Measured bode plots of output port (T <sub>v</sub> and T <sub>sys</sub> agree with each other) | 102 |

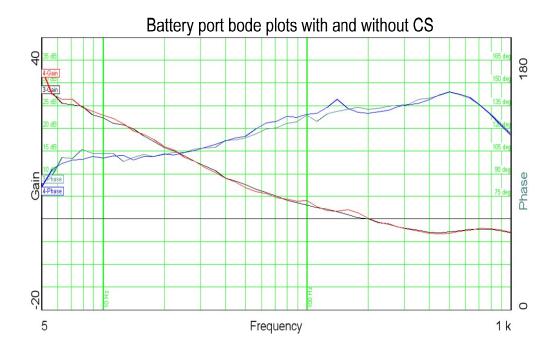

| Fig.4. 26: Measured bode plots of battery port, droop CS does not affect BVR loop                         | 103 |

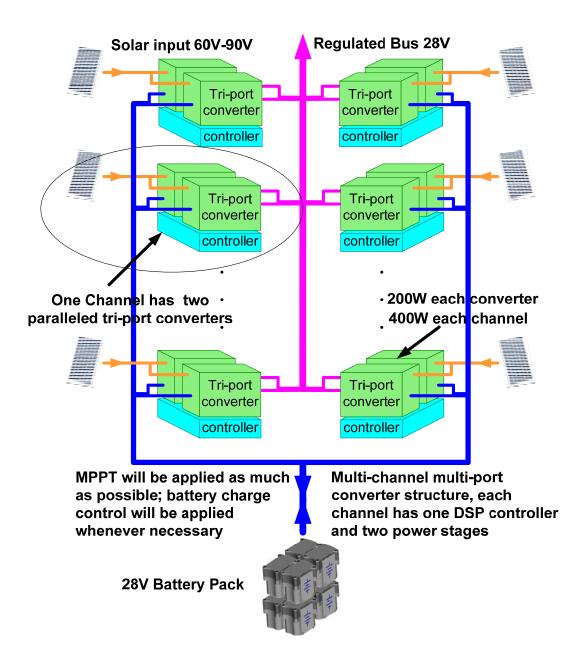

| Fig.4. 27: Multi-channel converter structure                                                              | 104 |

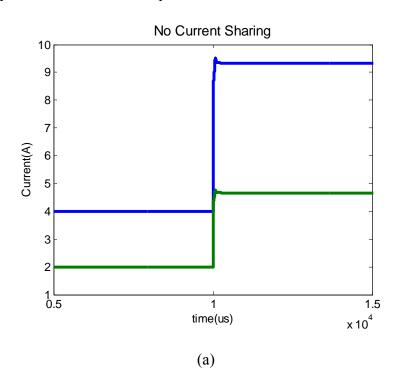

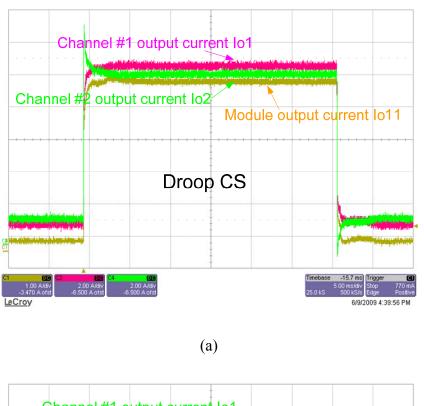

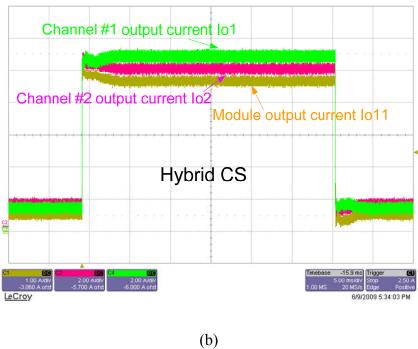

| Fig.4. 28: CS results with different approaches: (a) no current sharing, (b) active current               |     |

| sharing, (c) droop current sharing.                                                                       | 106 |

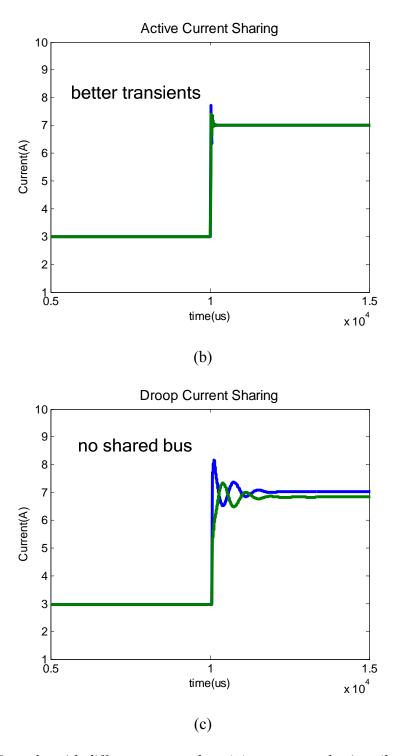

| Fig.4. 29: Output port hybrid CS structure                                                                | 107 |

| Fig.4. 30: Thevenin equivalent circuit                                                                    | 107 |

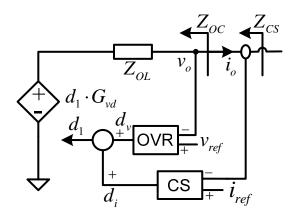

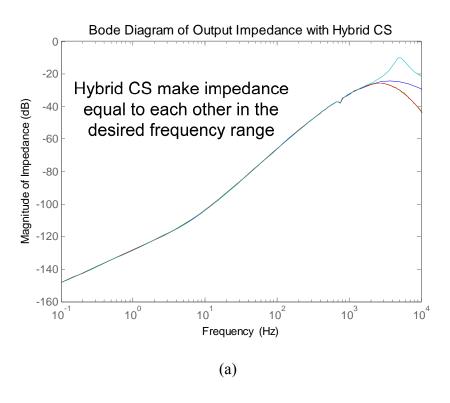

| Fig.4. 31: Output impedance with (a) hybrid CS and (b) droop CS method.                                   | 110 |

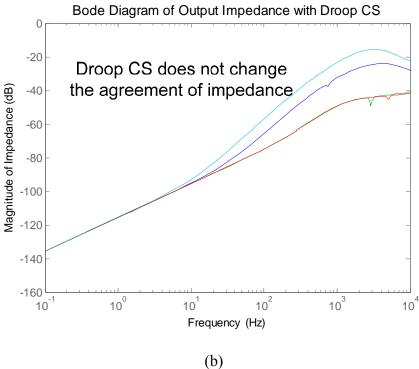

| Fig.4. 32: CS simulation results; (a) hybrid CS method, (b) droop CS method                               | 111 |

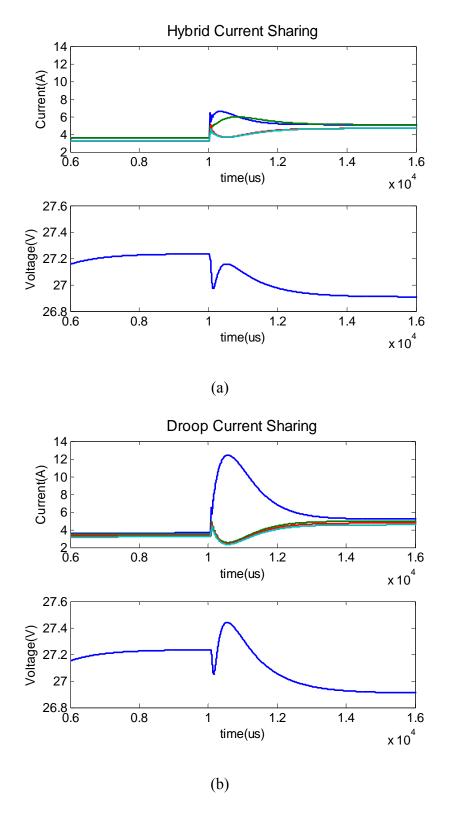

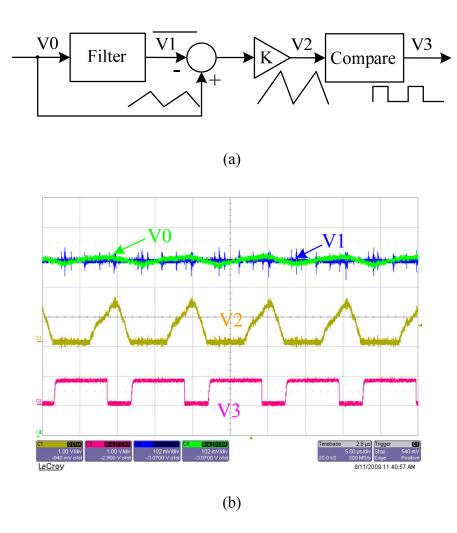

| Fig.4. 33: Implementation of synchronization with no wires: (a) circuit block diagram; (b)                |     |

| waveforms                                                                                                 | 113 |

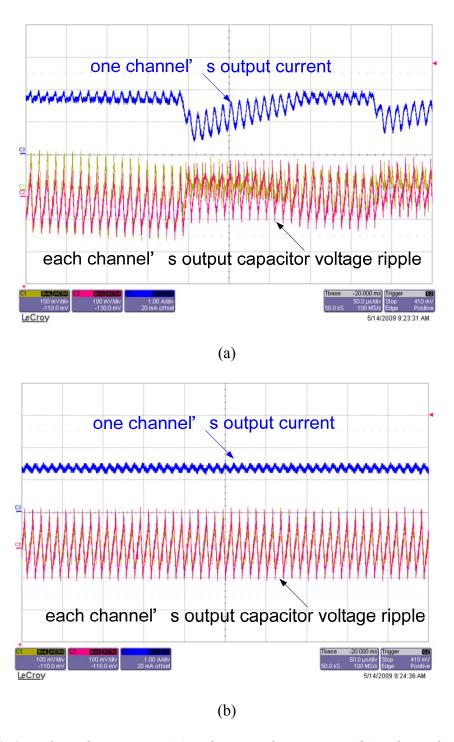

| Fig.4. 34: Signal synchronization, (a) without synchronization; (b) with synchronization                  | 114 |

| Fig.4. 35: Prototype photo of two converter channels                                                      | 115 |

| Fig.4. 36: Output port CS performance: (a) droop CS; (b) hybrid CS with better transients.                |     |

|                                                                                                           | 116 |

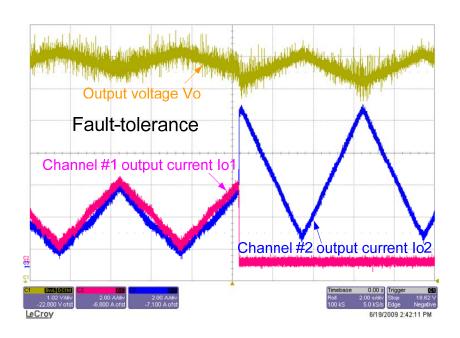

| Fig.4. 37: One channel fails while the other channel is not affected.                                     | 117 |

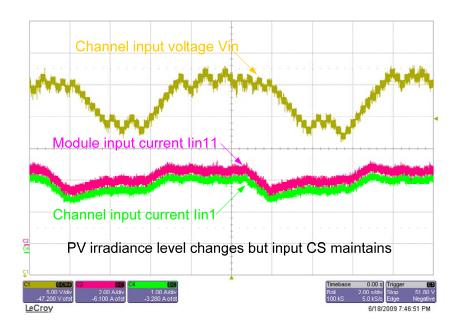

| Fig 4 38: Input Port CS with MPPT                                                                         | 118 |

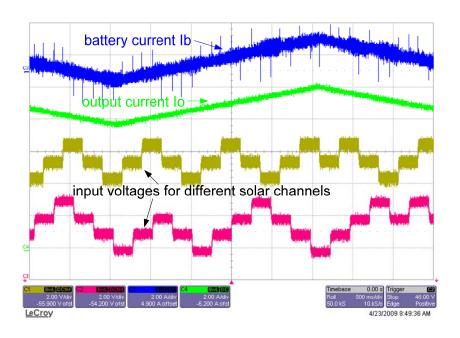

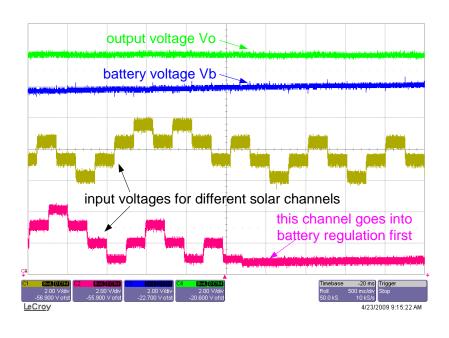

| Fig. 4. 39: Autonomous mode transitions: (a) both with MPP1; (b) transit from both with                                 |     |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| MPPT to one with MPPT; (c) transit from one with MPPT to both without                                                   |     |

| MPPT                                                                                                                    | 119 |

|                                                                                                                         |     |

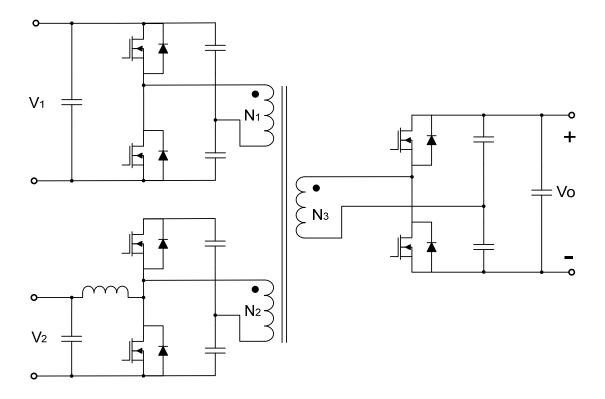

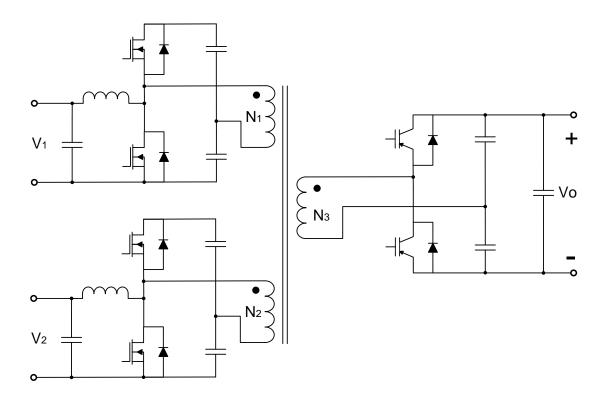

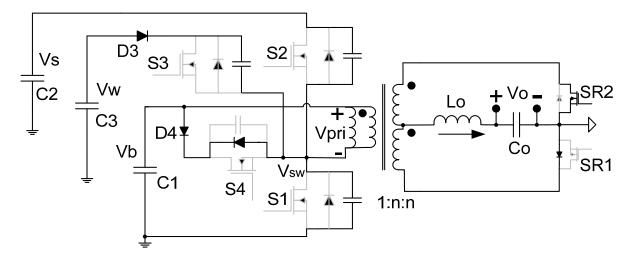

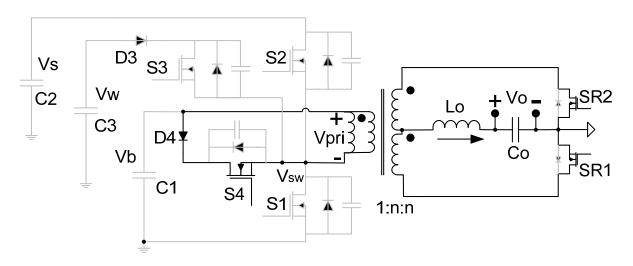

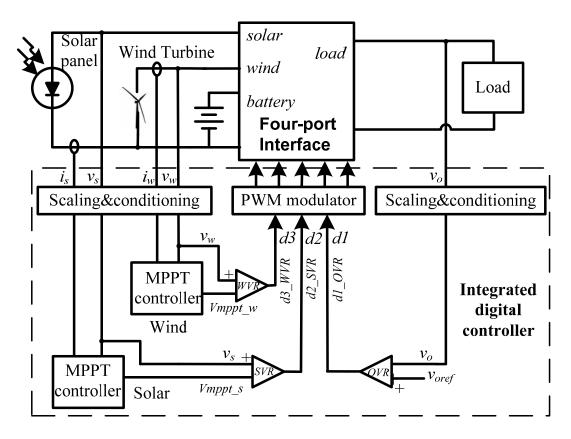

| Fig. 5. 1: Four-port converter concept                                                                                  | 121 |

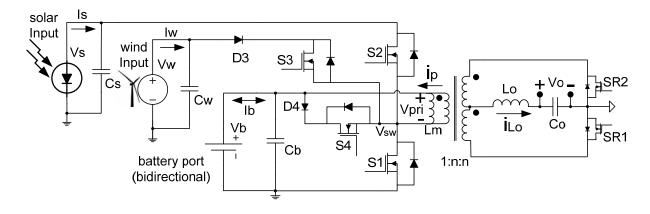

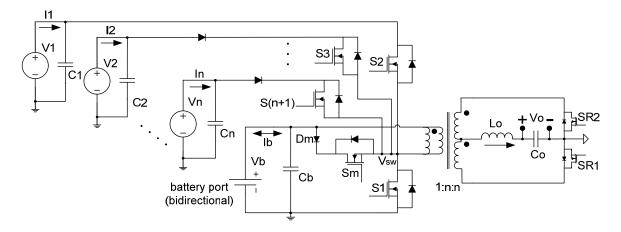

| Fig. 5. 2: The four-port half-bridge converter topology, which can achieve ZVS for all                                  |     |

| four main switches (S1, S2, S3 and S4) and adopts synchronous rectification                                             |     |

| for the secondary side to minimize conduction loss.                                                                     | 122 |

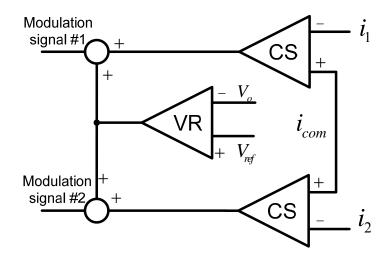

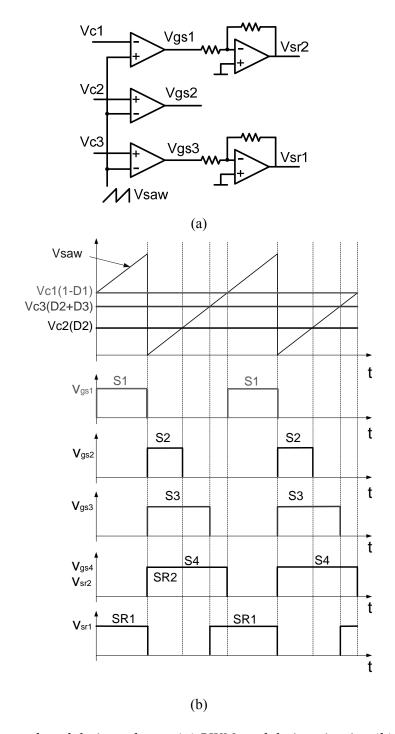

| Fig. 5. 3: The proposed modulation scheme: (a) PWM modulation circuits; (b) driving                                     |     |

| signal key waveforms.                                                                                                   | 124 |

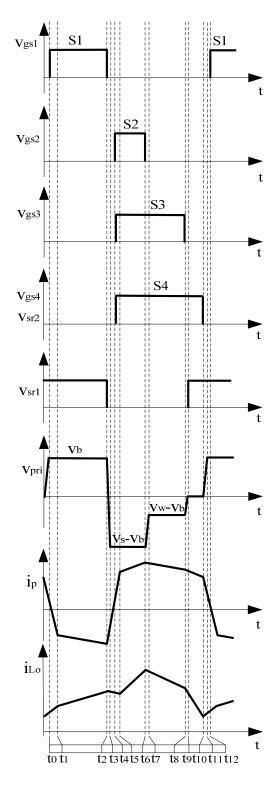

| Fig. 5. 4: Steady state waveforms of the four-port half-bridge converter                                                | 127 |

| Fig. 5. 5: Operation stages of the four-port half-bridge converter                                                      | 133 |

| Fig. 5. 6: A possible control structure to achieve MPPT for the PV panel and the wind                                   |     |

| turbine, meanwhile maintaining output voltage regulation. OVR, SVR and                                                  |     |

| WVR loops are to control d <sub>1</sub> , d <sub>2</sub> and d <sub>3</sub> , respectively.                             | 142 |

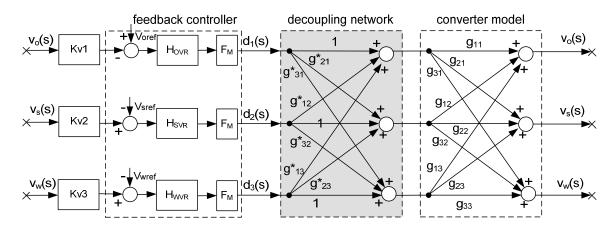

| Fig. 5. 7: Small signal model diagram, control inputs and outputs are decoupled to enable                               |     |

| separate controller design. The far right signals are routed to the far left ones in                                    |     |

| this diagram. $V_{\text{sref}}$ , $V_{\text{wref}}$ and $V_{\text{oref}}$ are the references for solar, wind and output |     |

| voltages, respectively. $H_{SVR}$ , $H_{WVR}$ and $H_{OVR}$ are the compensators need to be                             |     |

| designed.                                                                                                               | 145 |

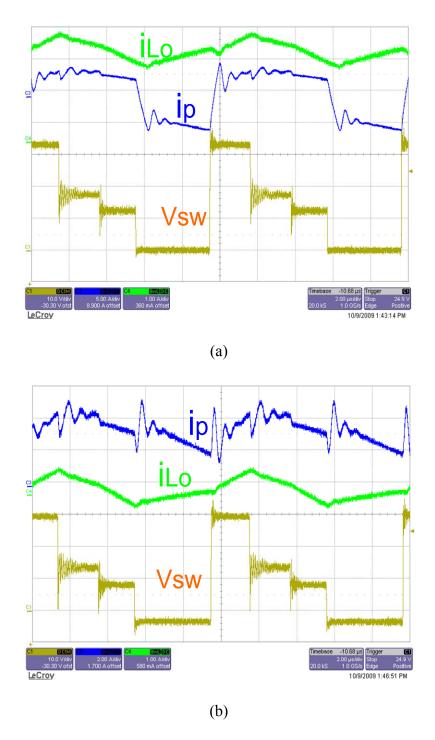

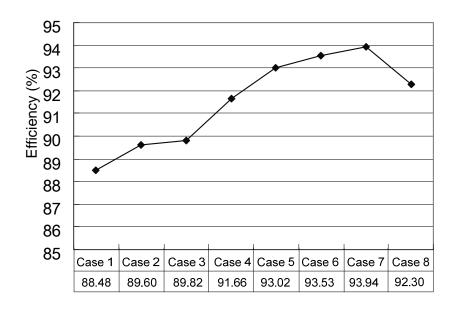

| Fig. 5. 8: Steady state waveforms: (a) Loading the output port when the battery current is                              |     |

| zero: (b) Loading the battery port when the output current is zero                                                      | 149 |

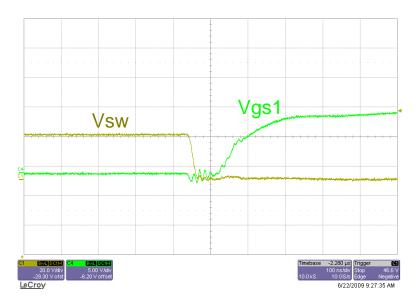

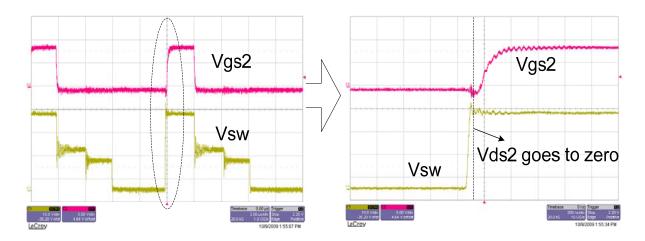

| Fig. 5. 9: V <sub>gs</sub> and V <sub>sw</sub> of the switch S1                     | 150 |

|-------------------------------------------------------------------------------------|-----|

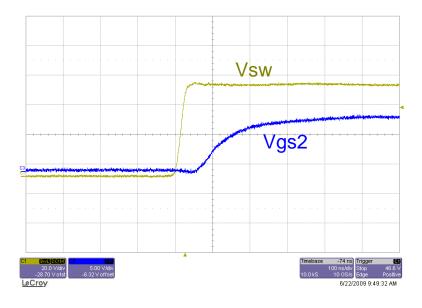

| Fig. 5. 10: V <sub>gs</sub> and V <sub>sw</sub> of the switch S2                    | 150 |

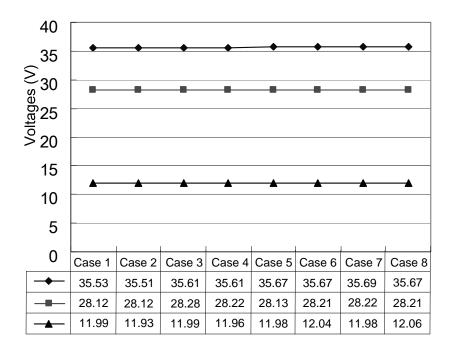

| Fig. 5. 11: Solar port, wind port, output port voltages under different load/source |     |

| conditions.                                                                         | 152 |

| Fig. 5. 12: Efficiency under different load/source conditions                       | 152 |

| Fig. 5. 13: Transient response of solar, wind and output voltages when the load is  |     |

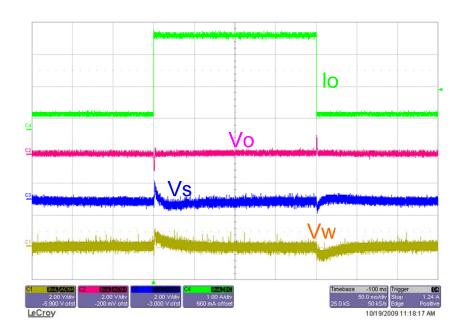

| perturbed by a step change between 10% and 90% rated output current                 | 154 |

| Fig. 5. 14: OVR loop bode plots: (a) prediction; (b) experiment.                    | 154 |

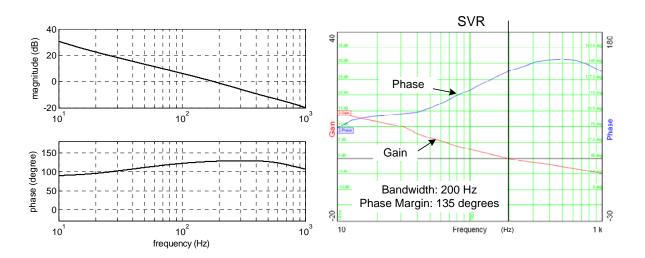

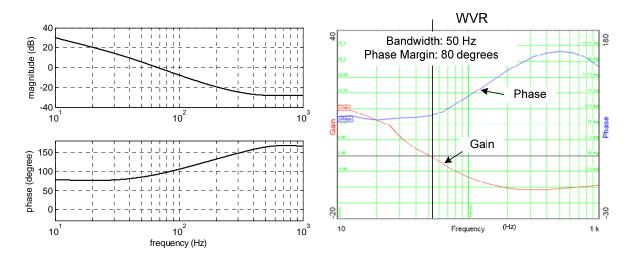

| Fig. 5. 15: SVR loop bode plots: (a) prediction; (b) experiment.                    | 155 |

| Fig. 5. 16: WVR loop bode plots: (a) prediction; (b) experiment                     | 155 |

| Fig. 5. 17: Extension of the proposed multi-port DC/DC converter                    | 156 |

# LIST OF TABLES

| Table 2.1 Comparison of Conventional Structure and Integrated Structure                          | 15  |  |

|--------------------------------------------------------------------------------------------------|-----|--|

| Table 3.1 Values of Circuit Parameters  Table 5.1 Operational Stages of the Four-port Converter. | 63  |  |

|                                                                                                  | 140 |  |

| Table 5.2 Different Load/Source Current Level Conditions                                         | 151 |  |

#### **CHAPTER 1: INTRODUCTION**

This chapter introduces the background information for the proposed multi-port converter to be used in satellite applications and renewable energy applications.

# 1.1. Background for Satellite Applications

The ever-increasing cost of launching a spacecraft into space, approximately \$100,000/kg, is a major driving force behind the efforts to minimize the volume and weight of its power system. Take the international space station as an example, the cost of the solar arrays per kilowatt is over \$3M/kW, assuming a mass of the solar array wing of 1000 kg and a beginning-of-life power of 32 kW[3]. In other words, the cost is heavily determined by the mass. Moreover, it is generally accepted that the satellite platform power system constitutes about 25% of its total dry mass, and reaches a figure of 35% when the user power system is included[1]. Therefore, mass is one of the most important design constraints for the space power system.

The satellite platform power system consists of solar arrays, batteries and an interface power conditioning unit (PCU). The PCU then connects the solar arrays and batteries to a distribution bus, normally 28V in low earth orbital (LEO) applications. The distribution bus then delivers the power to the user power system which includes various user loads such as propulsion, altitude control and data handling, etc.

The solar arrays generate the electrical power during periods of solar insolation throughout the operational life of the satellite, and deliver the sufficient power to supply normal satellite bus, which payloads the power demands. As mentioned above, the solar array is extremely heavy and expensive; therefore, one major issue is to efficiently convert this solar energy into a type of electrical energy that can be used by various loads.

Normally, there are two steps in the solar energy conversion.

The first step is to convert solar energy into an uncontrolled electrical power; its efficiency and mass is strongly dependent on the solar array materials and the efficiency improvement is relying on the development of material engineering, therefore it is beyond the scope of the power electronics research.

The second step is to use a power electronics circuit or interface to convert the uncontrolled power into a controlled and usable electrical power which can drive a distribution bus. The second conversion step relies on power electronics engineers to come up with smart solutions to achieve the power management control, with low mass and high efficiency.

The terminal voltage-current relationship of a PV cell can be described by the following equation.

$$I = I_{photo} - I_o \cdot (\exp[q / A \cdot K \cdot T \cdot (V + I \cdot R_{series})] - 1) - V / R_{shunt}$$

Eq. 1.1

Where  $I_{photo}$ : the photo current generated due to insolation

$I_o$ : the reverse saturation current of semiconductor material

$R_{series}$ : the series ohmic resistance of the cell

$R_{shunt}$ : the leakage current

*K*: the boltzman's constant

*T*: the absolute operating temperature

q: the charge of a single electron

A: the ideality factor of the p-n junction.

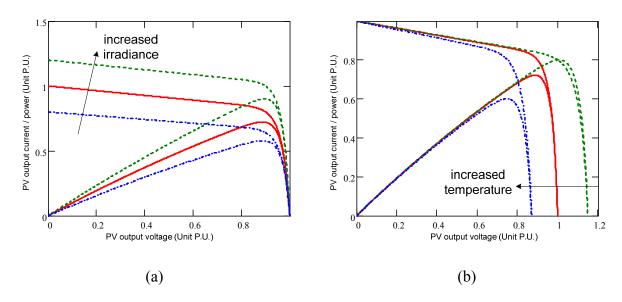

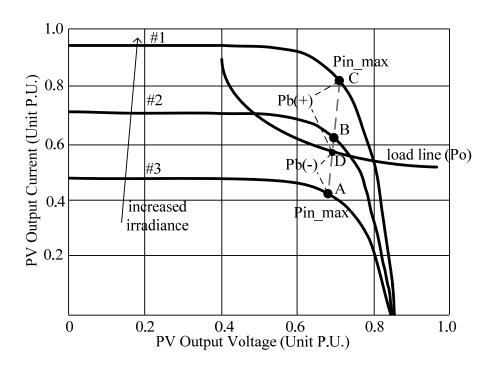

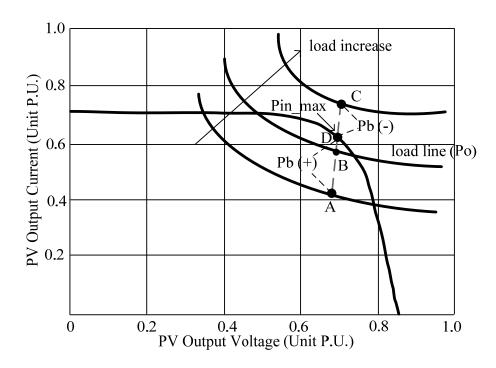

Figure 1.1 shows the typical nonlinear terminal characteristics of a solar array at different

operating conditions. For certain irradiance levels and temperatures, each PV curve has a point

that can deliver the maximal power. This point is defined as the maximum power point.

However, this point continuously moves following the variations in irradiance, temperature, and

other operating conditions. Therefore, a power electronics interface needs to be installed to

change the PV's load characteristics and to force the PV panel to follow this point which can

maximize the solar power harvesting.

3

Fig. 1. 1: Typical terminal characteristics of a solar array, (a) irradiance variations, (b) temperature variations.

Considering the satellite PCU, for the PV arrays, Maximum Power Point Tracking (MPPT) is very desirable in missions where the sun intensity varies drastically. Since for a given power budget requirement, MPPT will allow a smaller solar array to manage the same amount of load, therefore has the potential to lower overall mass of the power system. Another thing is that rather than an unregulated bus, a regulated bus will permit more efficient design of payload converters with less mass and volume by its impact on the filtering and derating of power components, thus may also save overall mass. Therefore, MPPT and bus regulation can potentially reduce the total satellite power system mass.

On the other hand, the battery will provide electrical energy to the satellite during pre-launch operations, the launch phase, eclipse periods, and during periods of peak power demand that exceeds solar array output capability. The battery needs to be protected from both over-charging and over-discharging in order to extend its service lifespan. So battery protection is always necessary for the satellite power system.

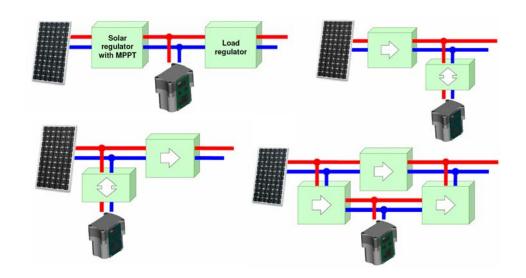

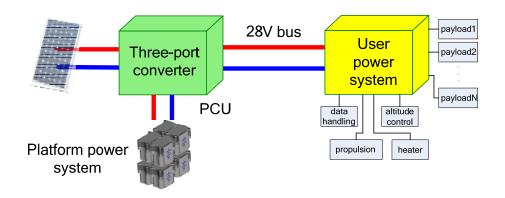

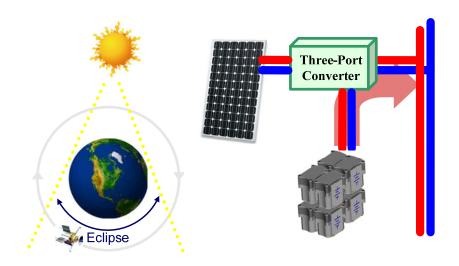

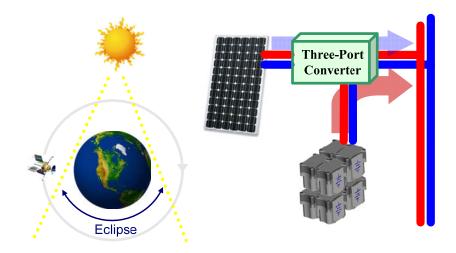

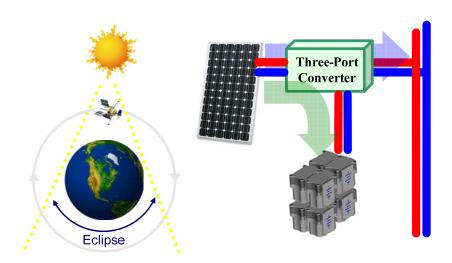

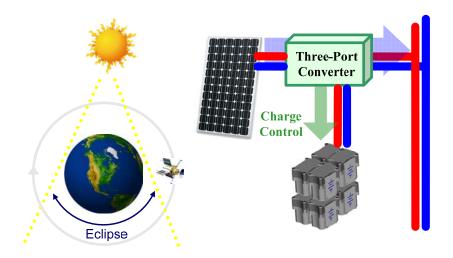

However, in the traditional satellite power system architectures as shown in Figure 1.2, normally several independent converters are used to achieve MPPT for the solar panel, battery charging/discharging control and bus regulation at the expense of increased conversion steps and control complexity. The added complexity, together with increased losses, size, weight, and cost, as well as decreased reliability, has impeded wide-spread adoption of such architectures for the satellite PCU. The potentially profitable MPPT technology has often been difficult to justify given the mass of MPPT regulator and control complexity overhead. Therefore, as in Figure 1.3, a single conversion stage is proposed in this dissertation to efficiently achieve MPPT and battery regulation while always maintaining a regulated distribution bus. The multi-functional utilization of power processing components and integration of control tasks reduces the size, weight, cost, and complexity, making the three-port converter a good candidate for the satellite platform power system.

Fig. 1. 2: Multiple converter solutions for the satellite platform power system.

Fig. 1. 3: Satellite power system includes platform power system sourcing by solar panels and batteries, and user power system sinking by various types of user loads.

### 1.2. Background for Renewable Energy Applications

Recently, renewable energy sources such as PV arrays, wind generators and fuel cells are gaining more and more attention due to their advantage of being abundant in nature and causing zero-emissions. For solar energy and wind energy, they are now the world's fastest growing energy resources. Today's PV arrays and wind turbines are state-of-the-art of modern technology, with modular design and quick installation. Since these renewable sources are intermittent in nature, combining more than one renewable source can increase the certainty of continuous load supplying compared with the individual source because of the renewable sources' complementary feature.

In order to accommodate different types of renewable sources, a multi-port converter interface will be desirable to achieve the power management control among different power sources and loads, and a storage device is necessary when the ac mains is not available. Otherwise, using several independent traditional converters will increase the total cost for the renewable system, because of high component count and increased control complexity. Therefore, the multi-port converter is a great fit for applications with hybrid renewable sources requiring low cost solutions.

For example, PV and wind power are complementary since sunny days are usually calm, and strong winds often occur on cloudy days or at night time. Moreover, the optimum combinations of PV array size and wind turbine capacity can be selected based on the solar and wind profile of the installation site to achieve the lowest cost per kilowatt of power. In order to keep supplying

power to the load in case no solar or wind power is available, a storage device has to be installed, which necessitates at least one bidirectional port from a multi-port interface. For the system level control strategy, in its normal operation, MPPT of both solar and wind will be desired while maintaining a regulated output, since MPPT can ensure maximum power harvesting. In addition, a battery will collect surplus power at light loading, and supply the deficit power at heavy

battery supplies power during peak load period. As a result, PV array and wind turbine

loading. Therefore, the solar and wind sources can be scaled to deliver the average load while the

requirement is low and the initial installing cost is reduced as well.

The PV array characteristics have been introduced in the above section; in this section we will

discuss the wind energy characteristics. A wind turbine can be defined as a machine that takes

kinetic energy from the wind and converts it to mechanical energy and transfers the motion to an

electric generator shaft. The fundamental equation governing the mechanical power capture of

the wind turbine rotor blades, which drives the electrical generator, is given by:

$$P = \frac{1}{2} \rho A C_p V^3$$

Eq. 1.2

Where P: Air density (kg/m3)

A: Area swept by the rotor blades

V: Velocity of air (m/sec)

$C_p$ : Power coefficient of the wind turbine.

8

The theoretical maximum value of the power coefficient  $C_p$  is 0.59 and it is often expressed as the function of the rotor tip-speed to wind-speed ratio TSR. TSR is defined as the linear speed of the rotor to the wind speed.

$$TSR = \frac{\omega R}{V}$$

Eq. 1.3

Where R and  $\omega$  are the turbine radius and the angular speed, respectively. In practical designs, the maximum achievable wind turbine efficiency  $C_p$  ranges between 0.4 and 0.5 for modern high speed turbines and between 0.2 and 0.4 for slow speed turbines.

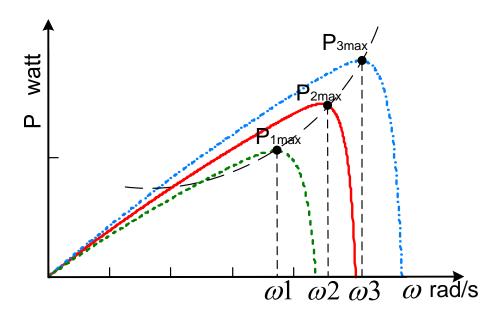

The typical power  $V_s$  rotor speed curve is plotted in Fig 1.4. As can be seen, there is a maximum power point at a certain rotor speed. For the wind turbine, the maximum power for different wind speeds is generated at different rotor speeds. Therefore, the turbine speed should be controlled to follow an optimal operating point which is different for every wind speed. For some designs, this is achieved by incorporating a speed control in the system design to run the rotor at high speed in high wind and at low speed in low wind, resulting in maximum electrical energy generation. Unfortunately, accurate wind speed measurement in the rotor of the turbine is difficult and requires the use of a relatively expensive anemometer if it is to be used for system control.

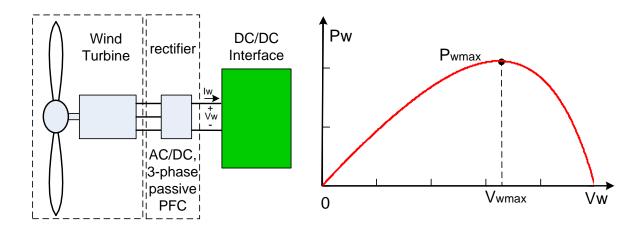

Fig. 1. 4: The wind turbine characteristics of power  $V_s$ . rotor speed.

Alternatively, a MPPT algorithm that does not need any external information like wind speed measurement can be utilized. As in Figure 1.5, almost every low to medium power wind turbine is designed to supply a three-phase AC where the frequency and magnitude varies with the speed of the wind. Additionally, a rectifier stage is often incorporated inside the wind turbine to condition the AC power into DC power. For the rectified voltage  $V_w$  and current  $I_w$ , the wind P-V curve resembles that of the solar power, in which one maximum power point exists to extract the peak power from the wind turbine. Adjusting the voltage on the dc rectifier will change the generator terminal voltage and thereby provide control over the current flowing out of the generator. Since the current is proportional to torque, the dc to dc converter will provide control over the speed of the turbine indirectly. As a result, MPPT of the wind turbine can be achieved with the similar control strategy for the PV panel.

Fig. 1. 5: The wind turbine P-V characteristics.

### 1.3. Outline of Dissertation

The outline of this dissertation will be as follows.

The first chapter introduces the background information of the multi-port converter to be used in applications like the satellite platform power system and the hybrid renewable energy power sources. For space applications, the most important design criteria is "minimum mass", and the multi-port converter can reduce the mass and increase the efficiency for its power system, since it has less component count and less conversion stage than traditional architectures with several independent converters. For renewable energy applications, the cost of the power electronics interface should be as low as possible. The low component count feature of the multi-port converter makes it the low cost choice for renewable energy applications.

The second chapter reviews the existing research for the multi-port converter, including both multi-input topologies and multi-port topologies. To date, most of the work is done in the power

stage design and topology investigation, with only a few reports focusing on the control aspects such as modeling and control strategies for the multi-port converter, which is actually very challenging for such kinds of multi-input multi-output systems. This dissertation is going to focus on not only the topology investigation, but also the control aspects.

The third chapter discusses the design of a three-port converter for space applications. First, the circuit operation and power stage design considerations are introduced, including the various circuit stages, ZVS analysis and DC analysis, etc. Then, the control aspects, such as various modes of operation and the autonomous mode transitions are discussed. This chapter also proposes a modeling procedure suitable for the multi-port converter based on the traditional state-space averaging method advocated by Dr. Middlebrook and Dr. Cuk [4], [5]. The major difference is that for the proposed method, different modes need to be identified first for the multi-port converter, and then the corresponding state variables need to be chosen to reveal the dynamic characteristics of the power ports that are of interest. Finally, the state-space equations in each main circuit stages are averaged to derive the converter model which follows the traditional state-space averaging method. Since control loops are coupled with each other due to the power stage integration issue, the proper decoupling method is suggested to allow separate controller design for each power port. The modeling procedure is general and is designed to be suitable for other multi-port topologies.

The fourth chapter talks about the interesting topic of paralleled multi-port converters. The main difficulty for designing current sharing controllers for multi-port converters is that there are so

many control loops involved, and the adding of the current sharing controller should not adversely affect the system stability and needs to achieve good current sharing performance, both in steady state and dynamics. Also, the added current sharing function should still preserve the attractive features like MPPT and battery charging. First, the current sharing for two three-port converters are introduced, and then followed by the current sharing for multiple three-port converter channels. A dual loop current sharing control structure is identified to be suitable for such a multi-input multi-output system, because the voltage loop and current loop can be assumed to be decoupled to simplify the control loop design. A hybrid current sharing strategy combining the active and passive control methods is proposed to achieve good current sharing dynamic performance and avoid the current sharing bus that would be present for the active current sharing method.

The fifth chapter proposes a novel four-port half-bridge converter for renewable energy applications. The four-port topology is constructed by simply adding two switches and diodes to the traditional half-bridge topology. Moreover, zero-voltage switching (ZVS) can be achieved for all main switches to allow higher efficiency at higher switching frequency, which will lead to more compact design of this multi-port converter. The circuit operation and topology is introduced first, including the driving scheme, ZVS analysis, steady state analysis, semiconductor stress consideration, etc. Three of the four ports can be tightly regulated by adjusting their independent duty cycle values, while the forth port is left unregulated to maintain the power balance for the system. The control structure targeting the hybrid solar wind application is proposed to allow MPPT of both the PV panel and the wind turbine simultaneously

or individually and then its small-signal model is derived by the modeling procedure proposed in the third chapter. Finally, a prototype is built to verify the proposed topology and confirm its ability to achieve tight independent control over three power processing paths.

The sixth chapter gives the conclusion and the scope of future work.

#### **CHAPTER 2: LITERATURE REVIEW**

Advantages of the integrated multi-port converter instead of several independent converters such as less component count and conversion stage can be obtained because resources of switching devices and storage elements are shared in each switching period. As a result, the integrated system will have a lower overall mass and more compact packaging. In addition, some other advantages of integrated power converters are lower cost, improved reliability, and enhanced dynamic performance due to power stage integration and centralized control. Additionally, it requires no communication capabilities that would be necessary for multiple converters. Therefore, the communication delay and error can be avoided with the centralized control structure. Instead of one control input for traditional two-port converter, N-port converter has N-1 control inputs, which makes the multi-port converter difficult to be modeled. Moreover, since the multi-port converter has an integrated power stage and thus the Multi-Input Multi-Output (MIMO) feature, it necessitates proper decoupling for various control loops design. Table 1 gives a comparison of the two different system structures.

Table 2.1 Comparison of Conventional Structure and Integrated Structure

|                         | Conventional multi-converter structure | Integrated multi-port structure |

|-------------------------|----------------------------------------|---------------------------------|

| Conversion stage        | more than one                          | One                             |

| Component count         | high                                   | Low                             |

| Overall mass            | high                                   | Low                             |

| Control design          | conventional and well-known            | complicated and little-reported |

| Control structure       | separated (require communication)      | centralized (no communication)  |

| Control input           | one                                    | N-1                             |

| Control loop decoupling | not required                           | Necessary                       |

<sup>\*</sup> N denotes the port numbers of N-port integrated converter.

Since most of the existing researches are conducted in the area of the topology investigation, the following literature review will focus on the features of different topologies.

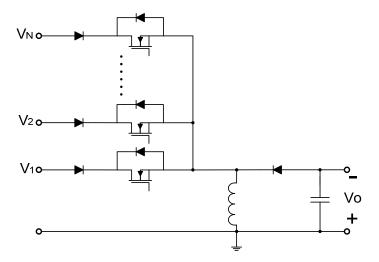

## 2.1. Multi-input Converters

As shown in Figure 2.1, a multi-input integrated buck-boost topology is proposed in [10] to allow multiple input sources. The topology is capable of interfacing sources of different voltage-current characteristics to a common load, while achieving a low component count. The open-loop circuit operation has been investigated to prove that the output port can be regulated based on the duty cycle value control of the active unidirectional switches. The operation modes of both continuous conduction mode (CCM) and discontinuous conduction mode (DCM) have been analyzed to obtain voltage gain relations. However, the output voltage is reversed with regard to input, and it is a non-isolated topology, which can not meet the isolation requirement for certain critical applications.

Fig. 2. 1: Multi-input buck-boost converter

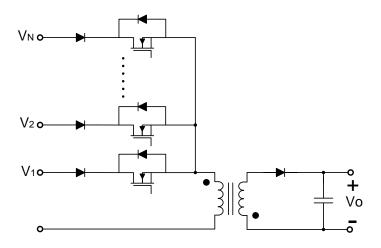

Hence, an isolated version of the above-mentioned topology named as multi-input flyback converter has been proposed in [11], which is illustrated in Figure 2.2. The output voltage polarity is the same as input, and output isolation is achieved. It is shown mathematically that the idealized converter can accommodate arbitrary power commands for each input source while maintaining a prescribed output voltage. Power budgeting is demonstrated experimentally for a real converter under various circumstances, including a two-input (solar and line-powered) system. A closed-loop control example involving simultaneous tracking of output voltage and set-point tracking of the solar array shows that an autonomous system is realizable.

Fig. 2. 2: Multi-input flyback converter

This simple winded transformer in [11] can be replaced by a multi-winding transformer in [20] to allow more flexible input voltage range. This topology as shown in Figure 2.3 is used for a zero-emission electric power generation system that has two input sources: one solar source and one ac mains input. The steady state and dynamic characteristics of this converter has been

investigated. The boundaries of stability are clarified based on the dynamic characteristics. It is proved that if circuit parameters are designed adequately, the proposed converter is sufficiently stable and useful.

Fig. 2. 3: Multi-input flyback converter with a multi-winding transformer

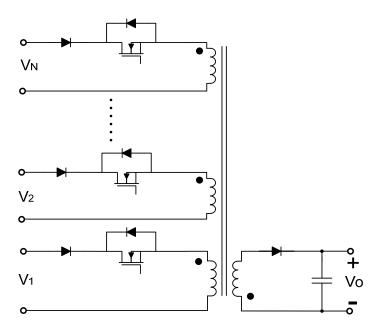

As in Figure 2.4, a multi-input dc/dc converter based on the flux additivity by using a multi-winding transformer is proposed in [18]. With the phase-shifted pulse width modulation (PWM) control, this converter can draw power from two different dc sources and deliver it to the load individually or simultaneously. The major drawback of this configuration is that it uses too many active switches and the associated driving circuitry, which may not justify the advantage of low component count and compact structure for the integrated converter.

Fig. 2. 4: Two-input current-fed full-bridge dc/dc converter

In summary, the main switches in these multi-input converters mentioned above can not achieve zero voltage switching (ZVS), which may impede their applications for high switching frequency designs to further shrink the converter size and weight. But most importantly, for the power harvesting applications, when the ac mains is not available, a battery has to be installed to provide the deficit power when the renewable sources can not generate enough power. In order to interface the battery, at least one bidirectional port is required from the multi-port interface. All above-mentioned multi-input converters can not achieve this goal within one topology.

Therefore, multi-port converters having the bidirectional port are necessary to interface the storage device.

## 2.2. Multi-port Converters

As shown in Figure 2.5, a three-port dc-dc converter has been proposed in [25] to have bidirectional and also ZVS capabilities. It is based on full bridge cells that allow bidirectional power flow in each port. Such a configuration facilitates the matching of different voltage levels in the overall system by the multi-winding transformer. The transformer design was optimally performed in order to incorporate the leakage inductances as required by the topology to affect the phase shift control. Furthermore, for the three-port converter, a dual-PI-loop based control strategy is proposed to achieve constant output voltage and power flow management. This topology has been verified through a hybrid fuel cell and super-capacitor system to improve the slow transient response of a fuel cell stack.

A similar work has been done in [24] taking the same topology to interface 14V and 42V bus to the high voltage bus for hybrid electric vehicles (HEVs). Besides the phase shift control managing the power flow between the ports, utilization of the duty cycle control for optimizing the system behavior is discussed. The dynamic analysis and associated control design are presented. A control-oriented converter model is developed and the bode plots of the control-output transfer functions are given. A control strategy with the decoupled power flow management is implemented to obtain fast dynamic response.

Fig. 2. 5: Three-port full-bridge dc/dc converter

As shown in Figure 2.6, a half-bridge version of this multi-port converter has been proposed in [17] for a fuel cell and super-capacitor generation system. The topology comprises a high-frequency three-winding transformer and three half-bridge cells, one of which is a boost half-bridge. The converter is controlled by phase shift, which achieves the primary power flow control, in combination with pulse width modulation (PWM). With the PWM control it is possible to reduce the rms loss and to extend the zero-voltage switching operating range to the entire phase shift region. A control scheme based on multiple PI regulators manages the power flow, regulates the output, and adjusts the duty cycle in response to the varying voltage on the port. Compared with full-bridge based topology, it applies half input voltage to the transformer

and adopts fewer switches to process the power. Therefore, the half-bridge based multi-port topology is more suitable for low to medium power applications.

Fig. 2. 6: Three-port half-bridge dc/dc converter

As shown in Figure 2.7, a similar topology has been used in [23] to interface hybrid energy storage as the battery and ultra-capacitor to achieve high overall performance. It can interface current source input, and can achieve ZVS for all six main switches by the phase shift control. This paper also discusses the power topology operation and the control aspects of dynamic characteristics analysis and the control strategy.

Fig. 2. 7: Triple-half-bridge bidirectional dc/dc converter

The above-mentioned topologies adopt a multi-winding transformer to couple different power ports. Therefore, all ports are fully isolated with each other. However, some applications do not require all ports to be fully isolated, and the share of some grounds may allow less component and fewer transformer windings. As shown in Figure 2.8, a topology in [15] is intended for future hybrid and fuel cell vehicles which may have three voltage nets: 14V, 42V and high voltage (>200V) buses. A soft-switched dc-dc converter using four switches has been proposed to interconnect these three nets. Its power flow management is based on a combined duty ratio and phase shift control, but soft-switching range is limited when the phase shifts between two very different voltage levels to have large current swing.

Fig. 2. 8: Reduced part, triple-half-bridge bidirectional dc/dc converter

To sum up, these multi-port topologies can be classified as two categories: non-isolated topologies [6]-[14] and isolated topologies [15]-[28]. Non-isolated multi-port converters usually take the form of buck, boost, buck-boost, etc, featuring compact design and high power density; isolated multi-port converters using bridge topologies have the advantages of flexible voltage levels and high efficiency since high frequency transformer and soft-switching techniques are used. As well, isolation may be required for certain critical applications.

#### 2.3. Summary

From the above literature review, all of the reported multi-port solutions suffer from at least one of the following drawbacks:

- 1. Lack of bidirectional capability to interface the battery;

- 2. No isolation capability or having too many isolating power ports with a bulky multiwinding transformer;

- 3. Using too many active switches and passive components which can not justify the multiport features like low component count and compact structure;

- 4. Lack of soft-switching capability to allow high frequency design to further shrink the converter size;

- 5. The power among different power ports can not be transferred individually or simultaneously.

For our applications, it requires at least one bidirectional port and only one isolated output port. The topologies with all ports isolated are over-qualified and unnecessary for our application. Therefore, the topologies with only one isolated port are sufficient. From this point of view, the topology as shown in Figure 2.8 is a good candidate. But as mentioned above, it has four main switches and its soft-switching range is limited when ports' voltage change largely. Therefore the main switches can still be reduced. Besides, our topology needs to have multiple input ports, but all above-mentioned multi-input topologies do not have ZVS soft-switching capability to allow high frequency designs. To sum up, the proposed topologies in this dissertation have the following features:

- 1. Have bidirectional capability;

- 2. Have one isolation port;

- 3. Low component count: have N switches for the N-port converter, that is three switches for a three-port converter;

- 4. ZVS for all main switches to allow high switching frequency designs;

- 5. The power among different power ports can be transferred individually or simultaneously.

For space applications in Chapter 3 and Chapter 4, the proposed three-port topology will have only three main switches, and it can achieve soft-switching for all the main switches for a wide input voltage range. Its main components are only three main switches, one clamping diode, one transformer, two rectification diodes and one inductor. For renewable energy applications in Chapter 5, based on the three-port converter, the proposed four-port topology adds one switch and diode to incorporate one more input port while still achieving ZVS for all four main switches. The power from both input ports can be transferred to the output port or battery port individually or simultaneously. If only one input source is available, the four-port topology reduces into the three-port operation which is almost the same as the topology proposed in Chapter 3. In Chapter 5, the proposed topology is extended into interface N power ports while still achieving ZVS for all main switches and still having very low component count. Therefore, this topology is a valuable choice for both space applications requiring minimum mass and renewable energy applications requiring minimum cost.

# CHAPTER 3: AN INTEGRATED THREE-PORT DC/DC CONVERTER: CIRCUIT ANALYSIS, MODELING AND CONTROL

#### 3.1. General Description

This chapter discusses the circuit operation, the modeling and the control of an integrated three-port converter for space applications. From topology point of view, this new three-port topology is derived by adding a diode and a switch across the transformer primary side, which provides one more control freedom and ensures a clamping path for the leakage energy to create ZVS condition for all the main switches. Since it is a new three-port converter, the small signal model will be desired to achieve the close loop controller design. Especially for such kind of multi-input multi-output (MIMO) control system, a precise model is critical to provide guidance through the whole control design process. Moreover, since various control loops are cross coupled with each other, a decoupling method suitable for such a MIMO system is proposed to allow separate controller design for each power port's feedback loop. The modeling procedure is based on the traditional state-space averaging method, and is suitable to be applied for other multi-port converters.

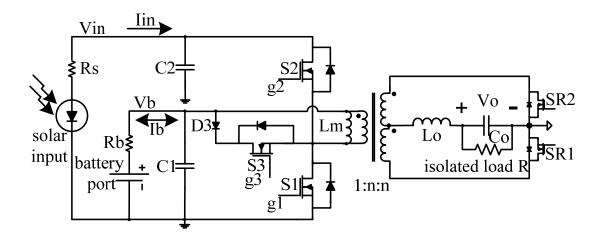

## 3.2. Circuit and Topology

This section introduces the three-port topology. As shown in Figure 3.1, it is a modified version of PWM half bridge converter which includes three basic circuit stages within a constant-frequency switching cycle to provide two independent control variables, namely duty-cycles  $d_1$

and  $d_2$  which are to control S1 and S2, respectively. This allows tight control over two of the converter ports, while the third port provides the power balance in the system. The switching sequence ensures a clamping path for the energy of the leakage inductance of the transformer at all times. This energy is further utilized to achieve zero-voltage switching (ZVS) for all primary switches for a wide range of source and load conditions. The circuit operation, the ZVS analysis and the DC analysis will be discussed as follows.

Fig 3. 1: Three-port modified half-bridge converter topology, which can achieve ZVS for all three main switches (S1, S2, S3) and adopt synchronous rectification for the secondary side to minimize conduction loss.

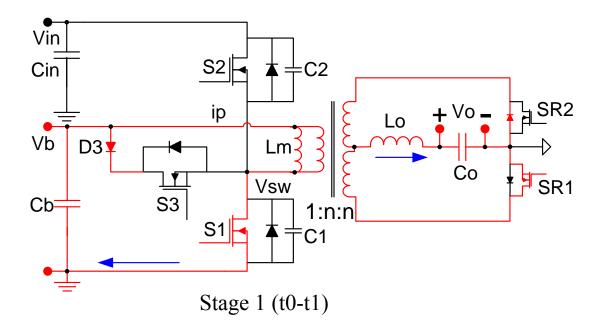

#### 3.2.1. Circuit Operation Principles

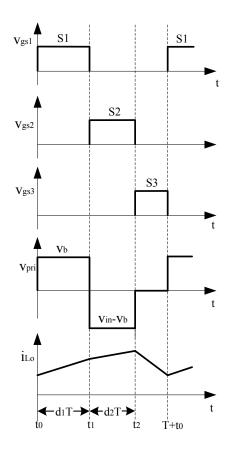

The steady-state waveforms of the three-port converter are shown in Figure 3.2, and the operation stages in one switching cycle are shown in Figure 3.3.

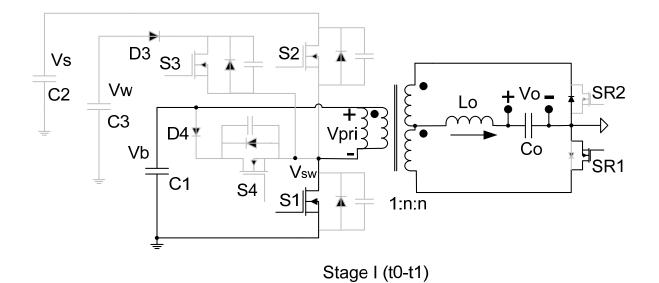

Stage 1 (t0-t1): Before this stage begins, the body diode of S1 is forced on to recycle the energy in the transformer leakage inductor, and the output is freewheeling. At time t0, S1 is gated on with ZVS, and then the leakage inductor is reset to zero and reverse-charged.

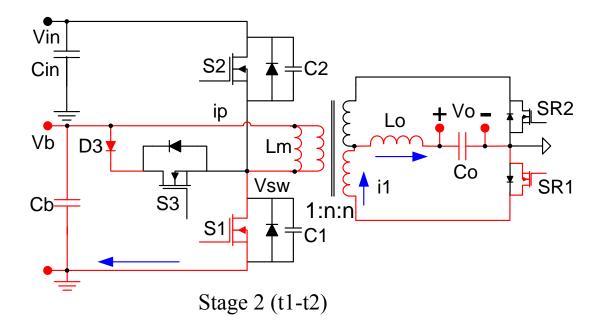

Stage 2 (t1-t2): At time t1, the transformer primary current increases to reflected current of io, the body diode of SR2 is blocked, and the converter starts to deliver power to output.

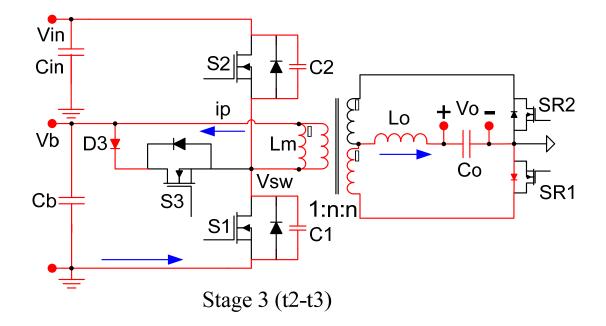

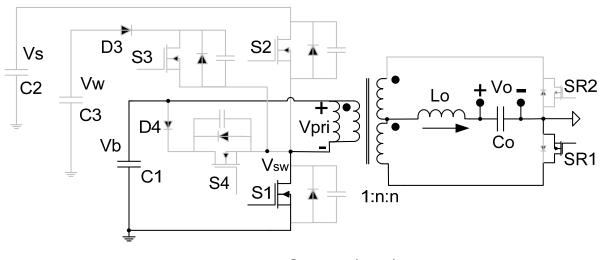

Stage 3 (t2-t3): At time t2, S1 is gated off, causing the leakage current ip to charge C1 and discharge C2.

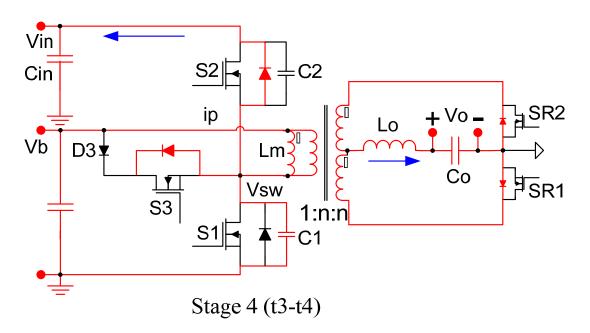

Stage 4 (t3-t4): At time t3, the voltage across C2 is discharged to zero, and D2 conducts to carry the current, which provides ZVS condition for S2. During this interval, the output is freewheeling.

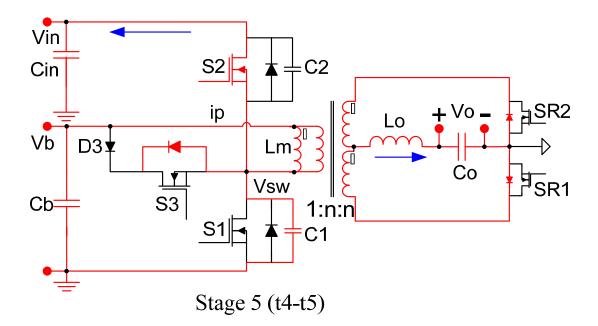

Stage 5 (t4-t5): At time t4, S2 is gated on with ZVS, and then the leakage inductor is reset to zero and reverse-charged. Output inductor current drop between t2 and t5 is due to the leakage inductor discharge/charge.

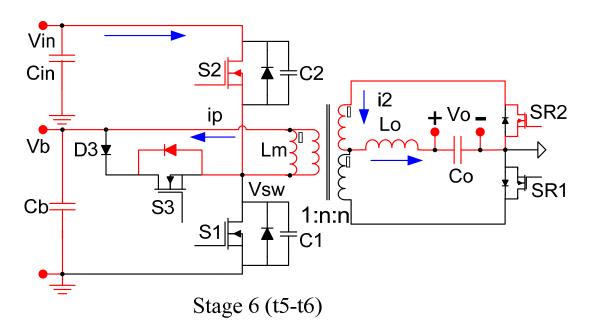

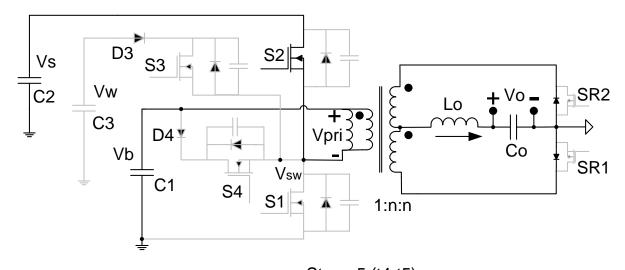

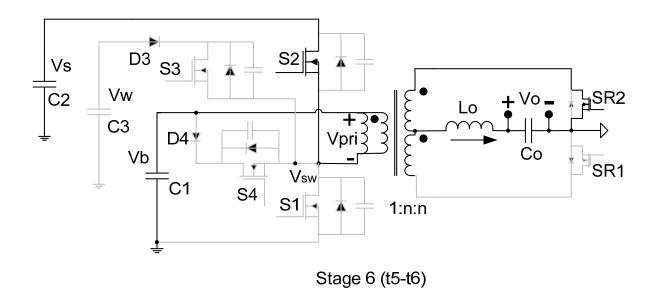

Stage 6 (t5-t6): At time t5, the transformer primary current increases to reflected current of i2, the body diode of SR1 is blocked, and the converter starts to deliver power to output.

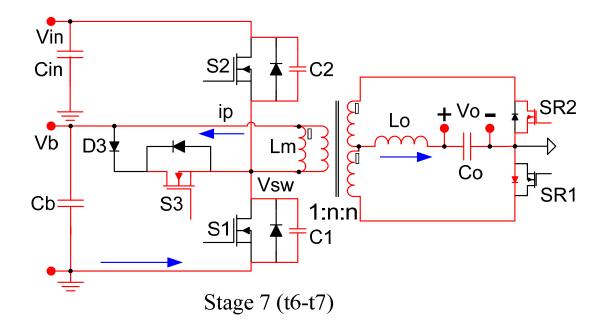

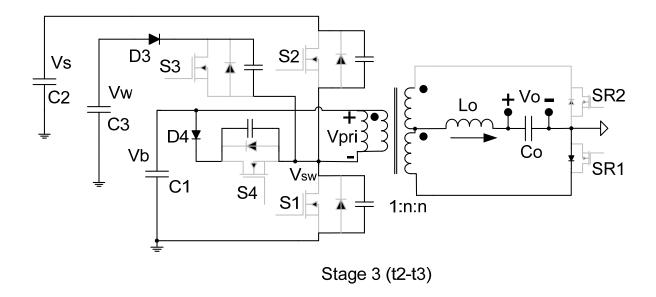

Stage 7 (t6-t7): At time t6, S2 is gated off, causing the leakage current ip to charge C2 and discharge C1.

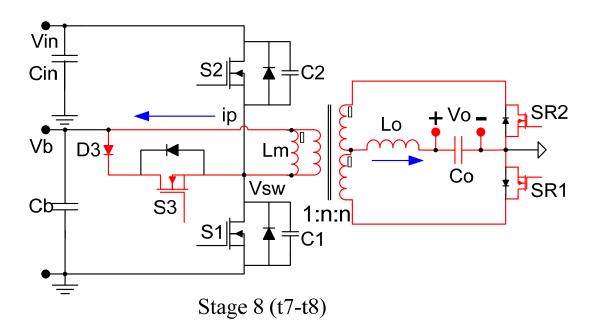

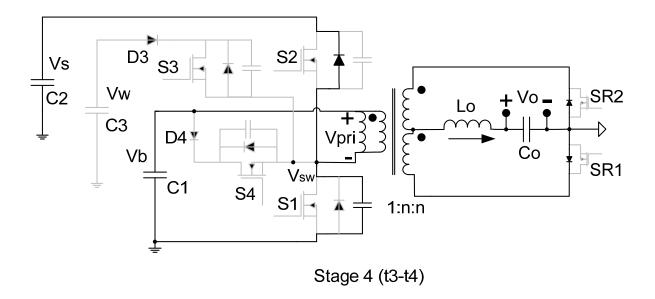

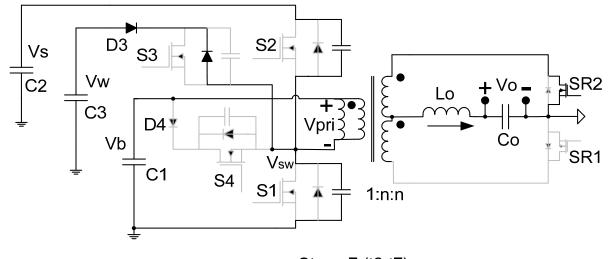

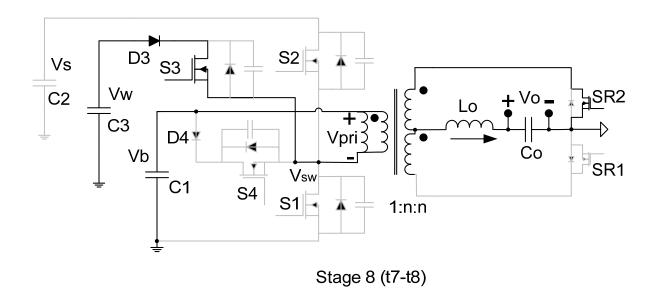

Stage 8 (t7-t8): At time t7, the voltage across D3 is discharged to zero, and D3 conducts. Since S3 is gated on before this time, the leakage current freewheels through D3 and S3 so that the leakage energy is trapped. On the secondary side, output inductor current freewheels through SR1 and SR2.

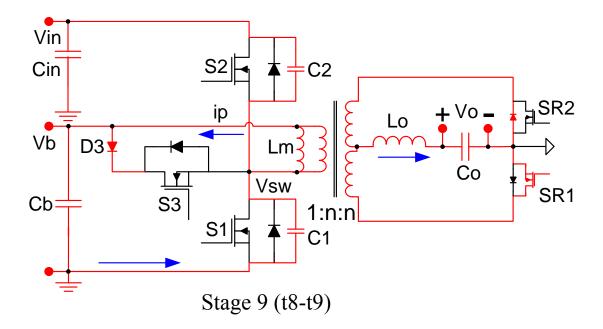

Stage 9 (t8-t9): At time t8, S3 is gated off, causing the trapped leakage energy to discharge C1 and charge C2.

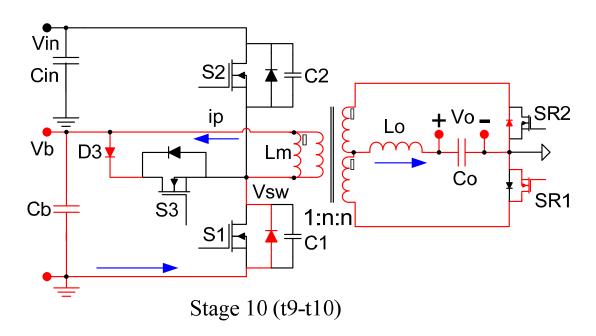

Stage 10 (t9-t10): At time t9, the voltage across S1 is discharged to zero, and D1 conducts to carry the current, which provides ZVS condition for S1. During this interval, the output is freewheeling.

This is the end of the switching cycle.

Fig 3. 2: Steady state waveforms of the three-port half-bridge converter

(a). Stage 1 operation

(b). Stage 2 operation

(c). Stage 3 operation

(d). Stage 4 operation

(e). Stage 5 operation

(f). Stage 6 operation

(g). Stage 7 operation

(h). Stage 8 operation

(i). Stage 9 operation

(j). Stage 10 operation

Fig 3. 3: Operation stages of the three-port half-bridge converter

#### 3.2.2. ZVS Analysis

When loading the output port, ZVS of the switches S1 and S2 can be realized through the energy stored in the transformer leakage inductor, while ZVS of S3 is always maintained because D3 will be forced on when the switching node voltage  $V_{sw}$  is connected to the input voltage  $V_{in}$ .

After S3 is turned off, the leakage energy is released to discharge C1 and charge C2 and S3's parasitic capacitance C3. The following condition should be satisfied to achieve ZVS for S1:

$$\frac{1}{2} \cdot L_k \cdot (I_M + n \cdot I_o)^2 > \frac{1}{2} \cdot C_{oss} \cdot (V_{in}^2 + V_{bi}^2), \quad I_M + n \cdot I_o > 0$$

Eq. 3.1

Where  $L_k$  is the transformer leakage inductance,  $C_{oss}$  is the MOSFET parasitic capacitance of S1, S2 and S3,  $V_{in}$  is the input voltage,  $I_o$  is the output load current,  $I_M$  is the transformer magnetizing current which is determined by the following equation.

$$I_{M} = \frac{I_{bi} + (D_{1} - D_{2})nI_{o}}{D_{1} + D_{2}}$$

Eq. 3.2

After S1 is turned, the leakage energy may charge C1 and discharge C2 and S3's parasitic capacitance C3 to achieve ZVS for S2:

$$\frac{1}{2} \cdot L_k \cdot (I_M - n \cdot I_o)^2 > C_{oss} \cdot V_{in}^2 + \frac{1}{2} \cdot C_{oss} \cdot V_{bi}^2, \quad I_M - n \cdot I_o < 0$$

Eq. 3.3

Where  $I_{bi}$  is the battery current. Therefore, when  $I_o$  is small and  $I_M$  is large,  $I_M - n \cdot I_o < 0$  can not be met, and ZVS of S2 is lost. Worst case scenario would be when loading the battery port and leaving output port open,  $I_M > 0$ , so ZVS of S2 can not be achieved.

#### 3.2.3. DC Analysis

Assuming an ideal lossless converter, the steady-state voltage governing relations between different port voltages can be determined by equating the voltage-second product across the converter's two main inductors to zero. First, using volt-second balance across the primary transformer magnetizing inductance, when operating in continuous conduction mode (CCM), we have:

$$V_{bi} \cdot D_1 = (V_{in} - V_{bi}) \cdot D_2$$

Eq. 3.4

With  $V_{in} = V_{C1} + V_{C2}$ , and  $V_{bi} = V_{C1}$ , the voltage at the bidirectional port,  $V_{bi}$ , may be given by:

$$V_{bi} = \frac{D_2}{D_1 + D_2} V_{in}$$

Eq. 3.5

Where  $V_{in}$  is the voltage of the input port,  $D_1$  and  $D_2$  are the duty-cycles of S1 and S2, respectively, and T is the duration of the switching cycle. Assuming CCM operation, the volt-second balance across the load filter inductor yields:

$$D_1T(nV_{bi}-V_{o})+D_2T(nV_{in}-nV_{bi}-V_{o})-(1-D_1-D_2)TV_{o}=0$$

$$V_o = 2\frac{D_1 D_2}{D_1 + D_2} n V_{in}$$

Eq. 3.6

Where n is the turns ratio of the transformer, and  $V_o$  is the load-port voltage. Using Equation 3.5, this can also be re-written as:

$$V_o = 2D_1 n V_{bi}$$

Eq. 3.7

Assuming a lossless converter, steady-state port currents can be related by applying the power conservation principle as follows:

$$V_{in}I_{in} = V_{bi}I_{bi} + V_{o}I_{o}$$

Eq. 3.8

Where  $I_{in}$ ,  $I_{bi}$ ,  $I_o$  are the average input, bidirectional battery, and load currents, respectively.

## 3.3. Modeling and Control

This section introduces a modeling method specially tailored for deriving multi-port converter's small signal models under different modes of operation. A decoupling network is then introduced to allow separate controller designs. Since there are various modes of operation, it is challenging to define different modes and further to implement autonomous mode transition based on the energy state of the three power ports. Various modes of operation are defined. And a competitive method is used to realize smooth and seamless mode transition.

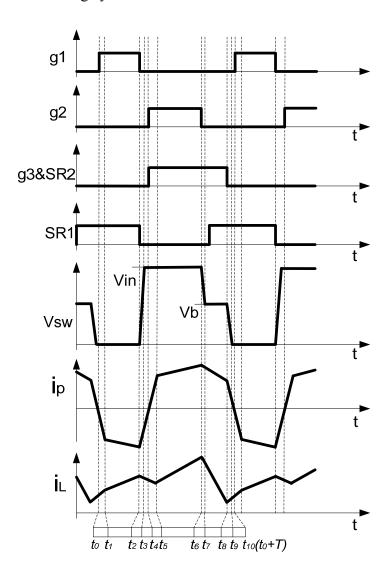

#### 3.3.1. Mode Definition

Having different operational modes is one of the unique features for multi-port converters. As illustrated in Figure 3.4, orbital satellite's power platform experiences periods of insolation and eclipse during each orbit cycle, with insolation period being longer. Since Maximum Power Point Tracking (MPPT) can notably boost solar energy extraction of a photovoltaic (PV) system, the longer insolation period means that MPPT is more often operated to allow a smaller solar array while managing the same amount of load. Two assumptions are made to simplify analysis:

1) Load power is assumed to be constant; 2) Battery over-discharge is ignored because PV arrays

and batteries are typically over-sized in satellites to provide some safety margins. Four stages in satellite's one orbit cycle yield two basic operational modes as follows.

In Battery-balanced Mode (Mode 1), the load voltage is tightly regulated, and the solar panel operates under MPPT control to provide maximum power. The battery preserves the power balance for the system by storing unconsumed solar power, or providing the deficit during high load intervals. Therefore, the solar array can be scaled to provide average load power while the battery provides the deficit during peak power of load, which is attracting to reduce solar array mass.

In Battery-regulation Mode (Mode 2), the load is regulated and sinks less power than is available, while the battery charge rate is controlled to prevent overcharging. This mode stops to start Mode 1 when the load increases beyond available solar power. That is, battery parameter falls below either maximum voltage setting or maximum current setting.

(a). Stage I operation (eclipse period)

(b). Stage II operation (initial insolation)

(c). Stage III operation (increased insolation)

d). Stage IV operation (battery charge control)

Fig 3. 4: Different operational modes in satellite's one orbit cycle. Three-port converter can achieve MPPT, battery charge control and load regulation depending on available solar power, battery state of charge and load profile. In stage I, battery acts as the exclusive source during eclipse period. In stage II&III, solar power is maximized to decrease battery state of discharge in stage II for initial insolation period and then to increase battery state of charge in stage III for increased insolation period. In stage IV, battery charge control is applied to prevent battery over-charging and extend battery service life.

#### 3.3.2. Control Structure

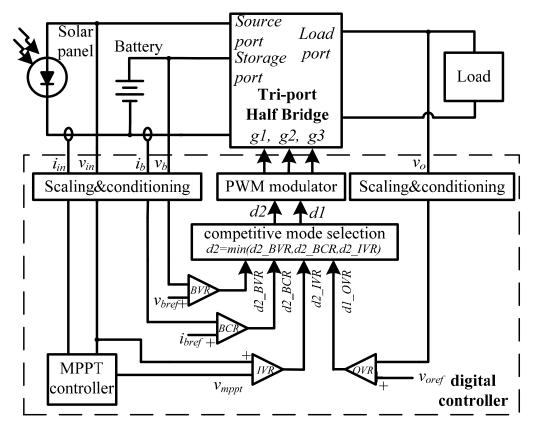

The multi-objective control architecture which aims to regulate different power ports is shown in Figure 3.5, control loops are named as follows: input voltage regulation (IVR), output voltage regulation (OVR), battery voltage regulation (BVR), and battery current regulation (BCR).

Fig 3. 5: Three-port converter's control architecture to achieve MPPT for solar port, battery charge control for battery port and meanwhile always maintaining voltage regulation for output port. OVR is to control  $d_1$ , and the rest of control loops (BVR, BCR and IVR) are competing the minimum value to control  $d_2$ .

The output port loop is simply a voltage-mode control loop, closed around the load voltage, and duty cycle  $d_I$  is used as its control input. According to the DC circuit equation  $V_o = 2V_b \cdot D_1 \cdot n$ , output voltage  $V_o$  can only be controlled by  $d_I$ , since battery voltage  $V_b$  is almost constant and transformer turn's ratio n is fixed. As a result,  $d_2$  is assigned to control either input port or battery port.

The IVR loop is used to regulate the solar panel voltage to its reference value. The reference is provided by an MPPT controller [34] using perturb and observe algorithm, and represents an estimate of the optimal operating voltage, duty cycle  $d_2$  is used as the control input when realizing the IVR loop. Otherwise,  $d_2$  can be decided by battery control loop which has two controllers, BVR and BCR. It should be mentioned that BCR is to prevent battery over-current, so it can be considered a protection function. Under normal operation, only one of two loops (IVR or BVR) will be active depending on the battery state of charge. Therefore, whether  $d_2$  is commanded by IVR, BVR or BCR depends on which mode it is in.

#### 3.3.3. Autonomous Mode Transitions

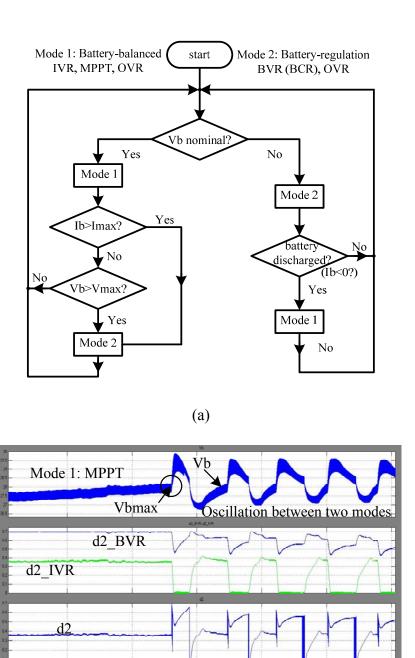

The mode of operation is determined according to the present operating conditions such as available solar power, battery state of charge and load profile. Figure 3.6(a) gives the flow chart for traditional mode transition algorithm. Mode 1 will be the default mode, where the converter will spend most of the time. Mode 1 is desirable because it enables maximum solar power input. When the converter is in Mode 1, the controller will continually check the battery parameter, and then switch to Mode 2 if the maximum setting voltage or current is reached. Once the converter is in Mode 2, it stays there until the load increases beyond available power. Although this algorithm is straightforward, without careful design of mode transitions, system oscillation will occur due to duty cycle's instant change. In a simulation as shown in Figure 3.6(b), when battery voltage reaches its maximum setting  $V_{bmax}$ , it switches to Mode 2 suddenly, that is,  $d_2$  is switched

from a nominal value to  $d_{2\_BVR}$  which is saturating at that moment, causing a battery voltage spike. But when the spike of  $V_b$  reduces below  $V_{bmax}$ , it will force the converter to switch back to Mode 1 and cause  $d_2$  another step change to introduce another voltage spike. And thus this process continues for a long time. Besides, small battery voltage spike can cause huge current spike which is usually large enough to break the circuit because of small battery internal resistance.

Fig 3. 6: (a) Conventional mode transition algorithm flow chart which is inclined to cause oscillation; (b) Oscillation between Mode 1 and Mode 2 because of instant switching of duty cycle value

(b)

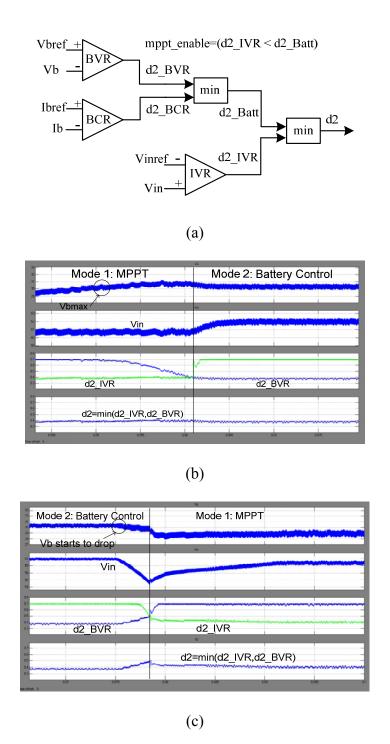

In order to avoid the sudden transition between modes, the autonomous mode transition is proposed in a competitive manor as shown in Figure 3.7(a). BVR, BCR and IVR are run in parallel to compete for minimum value in order to win control over  $d_2$ . Again, BCR will not be active during normal operation. So battery control is mainly BVR loop operation. For example, when converter is in Mode 1 with MPPT to maximize solar power,  $d_2$  will be determined by IVR loop, while BVR output is saturated at its upper limit because battery voltage does not reach its maximum setting. BVR will start to take control over  $d_2$  when battery maximum setting  $V_{bmax}$  is reached and BVR output goes down to win the minimum function. It should be noted that if IVR loop loses control, MPPT function needs to be disabled accordingly because of MPPT algorithm's inherent noise issue [33]. For example, in Figure 3.7(b), when converters are run in MPPT to maximize solar power,  $d_2$  will be determined by IVR loop, while BVR output is saturated at its upper limit because battery maximum voltage value is not reached. BVR will start to take control when  $V_{bmax}$  is reached and BVR output goes down to win the minimum function. Figure 3.7(c) shows Mode 2 to Mode 1 transition when the battery starts to discharge for sudden increase of load demand or decrease of solar power. This method simplifies the algorithm.

Fig 3. 7: (a) the proposed minimum function competitive method to allow smooth transition of modes; (b) Mode 1 to Mode 2 transition with no oscillation; (c) Mode 2 to Mode 1 transition with no oscillation.

## 3.3.4. Converter Modeling and Controller Design

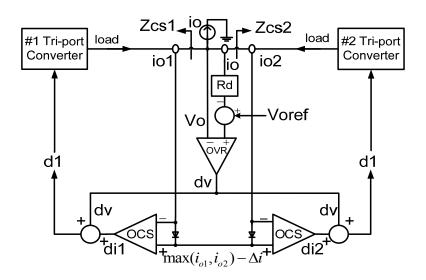

Small signal model is the basis for optimized controller design. Especially for such a complicated MIMO system of three-port converter, an effective model will be helpful to realize closed loop control and furthermore to optimize the converter dynamics. Since there are two modes of operation for the three-port converter, small signal models in both modes need to be obtained separately. Unlike conventional two-port converter, multi-port converter is high-order system, and the symbolic derivation of these plant transfer functions is fairly tedious, so it is difficult to obtain values of poles and zeros for analysis. Alternatively, the dynamics of the plant can be described in a matrix form, therefore computer software is used to plot the bode graph of different transfer functions. A common problem about MIMO system is the existence of various interacting control loops which complicate compensator designs; therefore a decoupling network is introduced to allow separate controller designs for each of the three power port.

### 3.3.4.1 Three-port Converter Modeling during Battery-Regulation Mode