# TOPOLOGY AND CONTROL INVESTIGATION FOR LOW-VOLTAGE HIGH-CURRENT ISOLATED DC-DC CONVERTERS

By

### HONG MAO

B.S. Sichuan University of Technology, 1992 M.S. Chongqing University, 1997 Ph.D Zhejiang University, 2000

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Major Professor: Issa Batarseh

Spring Term 2004

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 3134683

Copyright 2004 by Mao, Hong

All rights reserved.

### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

### UMI Microform 3134683

Copyright 2004 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### UNIVERSITY OF CENTRAL FLORIDA DISSERTATION APPROVAL

The members of the Committee approve the dissertation entitled **Topology and Control Investigation for Low-voltage High–Current Isolated DC-DC converters** by Hong Mao, defended on April 06, 2004.

Issa Batarseh, Chairman

Geof Potter

Louis Chow

in march

Thomas Wu

Washer Mills

Wasfy Mikheal

Christopher Iannello

Takis Kasparis

It is recommended that this dissertation be used in partial fulfillment of the requirements for the degree of Doctor of Philosophy from the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science.

Issa Batarseh, Department Jamal Nayfeh, Associate Dean for Graduate Studies

Louis Chow, Interim Dean

Patricia J. Bishop Vice Provost and Dean of Graduate Studies

The committee, the college, and the University of Central Florida are not liable for any use of the materials presented in this study.

## ABSTRACT

#### (Advisor: Dr. Issa Batarseh)

High conversion efficiency and fast transient response at high switching frequency are the two main challenges for low-voltage high-current DC-DC converters, which are the motivations of the dissertation work.

To reduce the switching power loss, soft switching is a desirable technique to keep power loss under control at high switching frequencies. A Duty-Cycle-Shift (DCS) concept is proposed for half-bridge DC-DC converters to reduce switching loss. The concept of this new control scheme is shifting one of the two symmetric PWM driving signals close to the other, such that ZVS can be achieved for the lagging switch due to the shortened resonant interval.

By applying a basic DCS concept to a conventional half-bridge DC-DC converter, Zero-Voltage-Switching is achieved for one of the two primary switches. To achieve ZVS for the other switch, a ZVS half-bridge topology is proposed. Basically, by adding an active branch to the conventional half-bridge topology, the leakage inductance energy is trapped during the freewheeling time, and the energy is released to achieve ZVS for the other switch. In addition, a modified ZVS half-bridge topology is proposed to ground the auxiliary switch, and thus, a simple drive circuitry can be applied to the auxiliary switch.

Leakage inductance leads to ringing issue in a half-bridge DC-DC converter. An active-clamp snubber topology is presented in the half-bridge DC-DC converters to recycle the leakage inductance energy and attenuate the ringing. Since dissipative snubbers are removed, a converter can operate more efficiently.

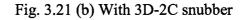

Body-diode reverse-recovery-related loss in SRs increases with the switching frequency. To reduce this reverse-recovery loss, two passive snubber circuits are proposed for SR rectifiers in a current dubler rectifier. The proposed snubbers attenuate reverse recovery ringing and higher efficiencies are achieved.

A unified DC model is derived based on the state-space average equation, which is suited for both symmetric and asymmetric half-bridge DC-DC converters. Furthermore, the DC analysis is conducted based on the unified DC model for symmetric and asymmetric half-bridge DC-DC converters with current-doubler rectifier. The AC model of isolated DC-DC converters is also established, and output impedance is analyzed for the purpose of transient response investigation.

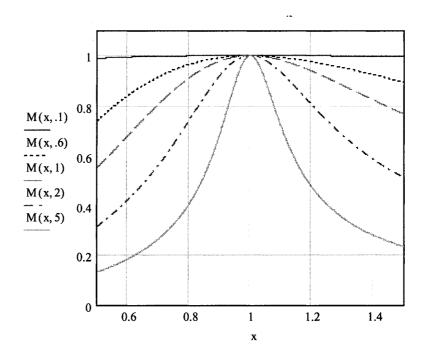

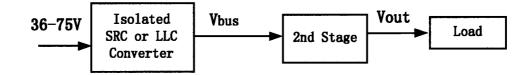

A two-stage approach is a trade-off between conversion efficiency and fast transient response. Full-Duty-Cycle (FDC) two-stage architecture is proposed to achieve desirable open-loop output impedance and fast transient response. Class-D resonant converters are investigated and recognized as potential topologies to reduce switching loss and SR conduction loss. Considering the limited regulation capability of class-D resonant converters, low-Q SRC and LLC resonant converters are proposed as candidate topologies in two-stage approaches.

iii

### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to my advisor, Dr. Issa Batarseh, for his guidance, encouragement and support. Dr. Batarseh's extensive vision and creative thinking have been the source of inspiration for me throughout this work. His personality and management experience are examples for me.

This work is supported and funded by ASTEC Power. I would like to thank Mr. Geof Potter, Vice President of ASTEC Power, for his valuable insight, technical guidance and encouragement. I would like to thank Mr. Brad Huggins for his valuable suggestions and technical support.

I am grateful to my committee members, Dr. Louis Chow, Mr. Goef Potter, Dr. Wasfy Mihkael, Dr. Christopher Iannello, Dr. Takis Kasparis and Dr. Thomas Wu. for their valuable suggestions and abundant help.

It has been a great pleasure to work in the Florida Power Electronics Center at the University of Central Florida. I would like to thank our alumni members, Dr. Shiguo Luo, Dr. Weihong Qiu, Dr. Weikai Wu and Dr. Christopher Iannello, for the valuable discussions and suggestions. I would like to acknowledge my coworkers Mr. Songquan Deng, Dr. Jaber A. Abu Qahouq, Ms. Yangyang Wen and Mr. Liangbin Yao for their useful discussion and support. I would like to thank all other Emerson team members, Dr. Louis Chow, Thomas Wu, Mr. Xiangcheng Wang, Dr. K. Ngo, Mr. Shangyang Xiao, Ms. Hua Zhou, Dr. Lei Zhou and Mr. Yeong Ren Lin. I would like to thank other members in the Power Electronics Laboratory, including Mr. Nattorn Pongratananukul, Ms. Yufang Jin and Mr. Khalid Rustom.

iv

I would like to express my special appreciation to my former advisors Prof. Zhengcheng Hou and Prof. Zhaolin Wu. Ten years ago, Prof. Hou guided me to the field of Power Electronics. From both of them, I learned not only extensive knowledge, but also from their excellent research attitudes and personalities.

I would like to express my appreciation to Ms. Michelle Jordan for her invaluable editing work on my dissertation.

Finally, I feel much indebted to my parents — they are always there to encourage and pray for me. With much love, I would like to thank my wife, Yangyang, for her encouragement and self-giving support.

Hong Mao

March 2004

To my wife - Yangyang

To my parents – Taichun Mao Xueqin Hou

# **TABLE OF CONTENTS**

|    | 510                | PF TABLESxi                                                       |  |

|----|--------------------|-------------------------------------------------------------------|--|

| LI | LIST OF FIGURESxii |                                                                   |  |

| 1. | INT                | RODUCTION1                                                        |  |

|    | 1.1                | Research Background and Motivation1                               |  |

|    | 1.2                | Review of Non-Isolated Multiphase VRM Technologies                |  |

|    | 1.3                | Review of Technologies in Isolated DC-DC Converters               |  |

|    |                    | 1.3.1 State-of-the-Art Rectifiers                                 |  |

|    |                    | 1.3.2 State-of-the-Art PWM DC-DC Converters                       |  |

|    | 1.4                | Dissertation Outline                                              |  |

| 2. | DU                 | TY-CYCLE-SHIFT (DCS) CONCEPT AND DERIVATIVE HALF-BRIDGE           |  |

|    | DC                 | -DC CONVERTERS                                                    |  |

|    | 2.1                | Introduction                                                      |  |

|    |                    |                                                                   |  |

|    | 2.2                | Duty-Cycle-Shift Concept                                          |  |

|    | 2.2                | Duty-Cycle-Shift Concept322.2.1 Proposed DCS PWM Control Scheme33 |  |

|    | 2.2                |                                                                   |  |

|    | 2.2                | 2.2.1 Proposed DCS PWM Control Scheme                             |  |

|    | 2.2                | <ul><li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>           |  |

|    | 2.2                | <ul> <li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>          |  |

|    | 2.2                | <ul> <li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>          |  |

|    | 2.2                | <ul> <li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>          |  |

|    |                    | <ul> <li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>          |  |

|    |                    | <ul> <li>2.2.1 Proposed DCS PWM Control Scheme</li></ul>          |  |

|    |     | 2.3.3        | Features of the Proposed Topology57                               |

|----|-----|--------------|-------------------------------------------------------------------|

|    |     | 2.3.4        | Experimental Verification of the Proposed Topology                |

|    |     | 2.3.5        | Test Results of the Developed Industry Demo Prototype             |

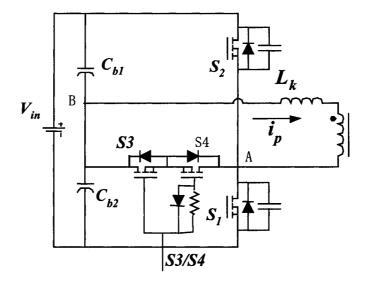

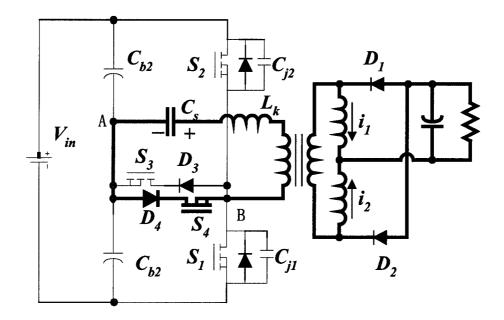

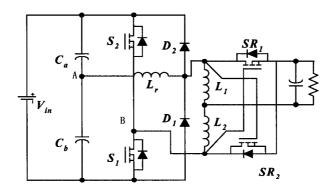

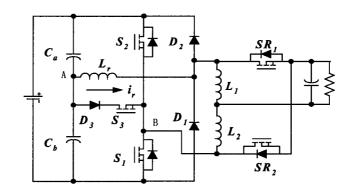

|    | 2.4 | Modi         | fied ZVS Half-Bridge DC-DC Topology Based on DCS Concept 71       |

|    |     | 2.4.1        | Introduction                                                      |

|    |     | 2.4.2        | Principle of Operation                                            |

|    |     | 2.4.3        | Experimental Verification                                         |

|    |     | 2.4.4        | Summary                                                           |

|    | 2.5 | Synch        | pronous Rectifier to Reduce Primary Circulating Conduction Loss81 |

| 3. | INV | <b>ESTIC</b> | GATION OF SNUBBER CIRCUITS FOR ISOLATED DC-DC                     |

|    | CO  | NVER         | TERS                                                              |

|    | 3.1 | An A         | ctive-Clamp Snubber for Half-Bridge DC-DC Converters              |

|    |     | 3.1.1        | Background                                                        |

|    |     | 3.1.2        | Principle of the Proposed Snubber Circuit                         |

|    |     | 3.1.3        | Main Features and Design Considerations                           |

|    |     | 3.1.4        | Simulation and Experimental Verification                          |

|    |     | 3.1.5        | Summary 104                                                       |

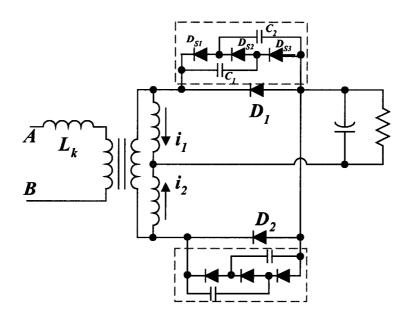

|    | 3.2 | Lossl        | ess Snubber Topologies for Current Doubler Rectifier 105          |

|    |     | 3.2.1        | Background 105                                                    |

|    |     | 3.2.2        | Review of State-of-the-Art Snubber Techniques for Current Doubler |

|    |     |              | Rectifiers 107                                                    |

|    |     | 3.2.3        | Passive Lossless 2D-1C Snubber Topology 111                       |

|    |     | 3.2.4        | Passive Lossless 3D-2C Snubber Topology114                        |

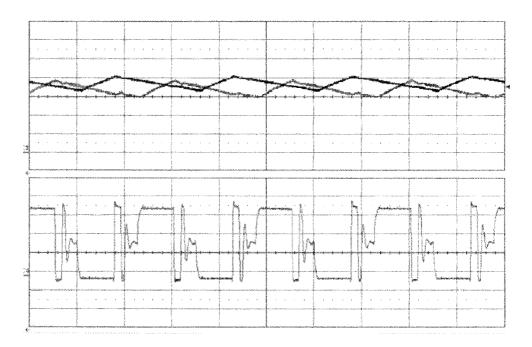

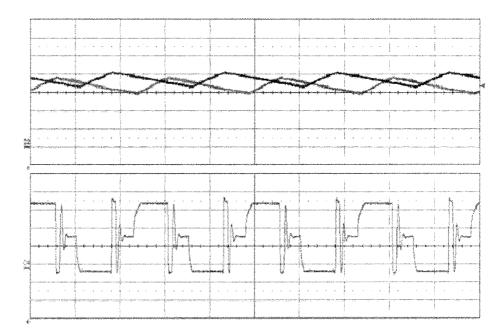

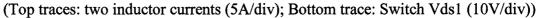

|    |     | 3.2.5  | Experimental Comparison118                                       |

|----|-----|--------|------------------------------------------------------------------|

|    |     | 3.2.6  | Summary 122                                                      |

| 4. | MO  | DELR   | NG OF ISOLATED DC-DC CONVERTERS 123                              |

|    | 4.1 | Unifie | d Steady-State DC Model for Half-bridge DC-DC Converters 123     |

|    |     | 4.1.1  | Introduction 123                                                 |

|    |     | 4.1.2  | DC Modeling of Half-Bridge DC-DC Converters 125                  |

|    |     | 4.1.3  | DC Analysis of Symmetric Half-Bridge DC-DC Converter 129         |

|    |     | 4.1.4  | DC Analysis of Asymmetric Half-Bridge DC-DC Converter 132        |

|    |     | 4.1.5  | Experimental and Simulation Verification                         |

|    |     | 4.1.6  | Summary 140                                                      |

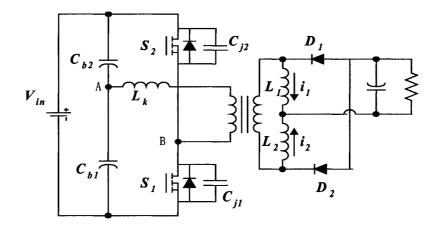

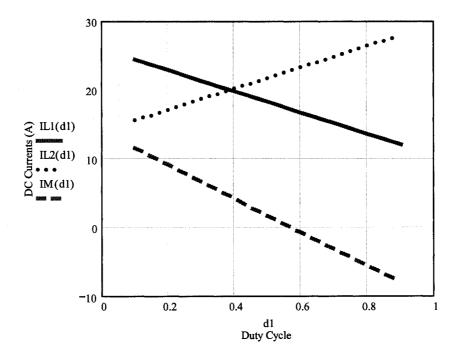

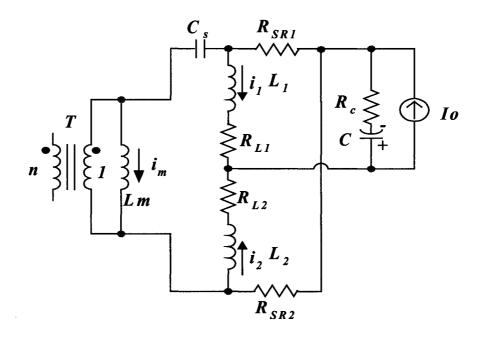

|    | 4.2 | An In  | proved Half-Bridge DC-DC Converter to Achieve Current Sharing140 |

|    |     | 4.2.1  | Modified Half-Bridge DC-DC Converters                            |

|    |     | 4.2.2  | DC Modeling of the Proposed Half-Bridge DC-DC Converter 141      |

|    |     | 4.2.3  | DC Analysis of the Proposed Half-Bridge DC-DC converter 145      |

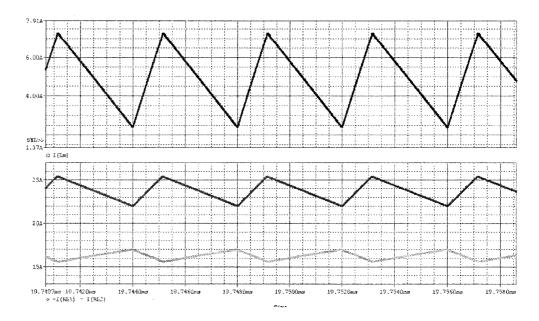

|    |     | 4.2.4  | Simulation Verification                                          |

|    |     | 4.2.5  | Summary 148                                                      |

|    | 4.3 | AC M   | Iodeling and Analysis of Isolated DC-DC Converters 149           |

|    |     | 4.3.1  | Closed-Loop System Modeling149                                   |

|    |     | 4.3.2  | Output Impedance Analysis 151                                    |

| 5. | ΤW  | O-STA  | AGE APPROACHES FOR DC-DC CONVERTSION 156                         |

|    | 5.1 | Revie  | w of Two-Stage Architectures of Voltage Regulator (VR)           |

|    | 5.2 | Revie  | w of Architecture of Point-of-Load (POL) Converters              |

|    | 5.3 | Two-   | Stage Approaches of Standard Brick Converters                    |

|    |            | 5.3.1 | Buck-Type Full-Duty-Cycle Converter Approach                  |

|----|------------|-------|---------------------------------------------------------------|

|    |            | 5.3.2 | Boost-Type Full-Duty-Cycle Converter Approach                 |

|    |            | 5.3.3 | Transient Response Analysis of Full-Duty-Cycle Converters 170 |

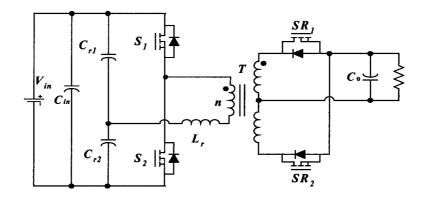

|    | 5.4        | Resor | nant Converters and Two-Stage Approaches                      |

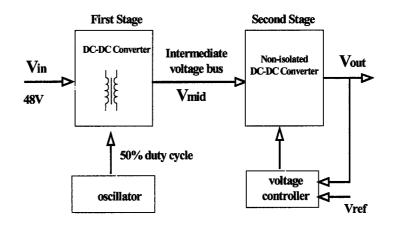

|    | 5.5        | A Tw  | ro-Stage Approach to 48V Input DC-DC Converter                |

|    |            | 5.5.1 | Introduction                                                  |

|    |            | 5.5.2 | Proposed Two-Stage Approaches for 48V DC-DC Converters 186    |

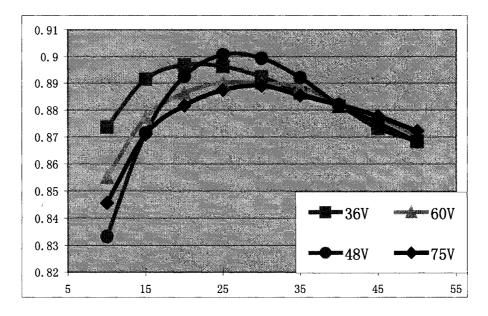

|    |            | 5.5.3 | Experimental Results                                          |

|    |            | 5.5.4 | Summary 198                                                   |

| 6. | CO         | NCLU  | SION 199                                                      |

| RE | REFERENCES |       |                                                               |

# LIST OF TABLES

Table 2.1 Comparisons of half bridge converters under several control schemes...43

# **LIST OF FIGURES**

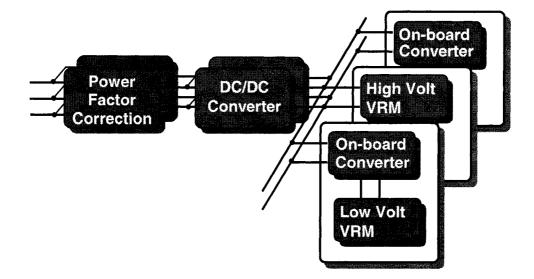

| Fig. 1.1  | Architecture of distributed power system (DPS)                   | 2 |

|-----------|------------------------------------------------------------------|---|

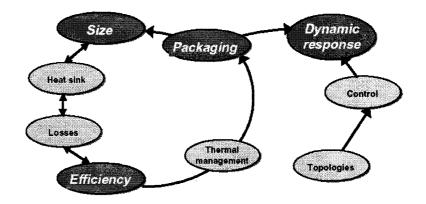

| Fig. 1.2  | Main factors affecting the design of low output voltage OBCs     | 4 |

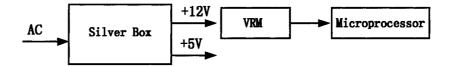

| Fig. 1.3  | Power delivery architecture for low-end computer systems         | 6 |

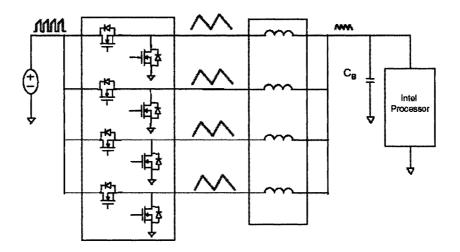

| Fig. 1.4  | Interleaved multi-channel architecture                           | 7 |

| Fig. 1.5  | Architecture of conventional PWM isolated DC-DC converters1      | 0 |

| Fig. 1.6  | Voltage-driven rectifiers                                        | 2 |

| Fig. 1.7  | Current-driven rectifiers1                                       | 3 |

| Fig. 1.8  | An application of center-tapped current-driven rectifier14       | 4 |

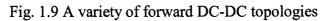

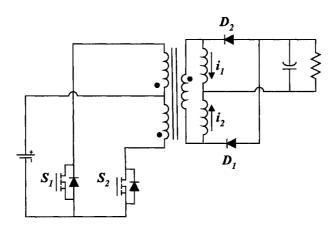

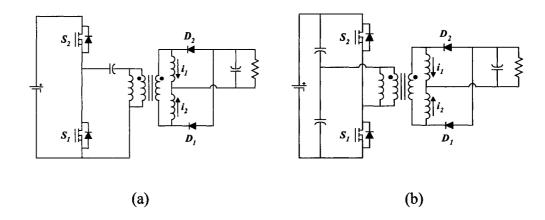

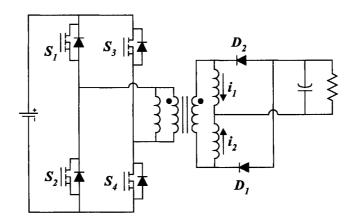

| Fig. 1.9  | A variety of forward DC-DC topologies Current-driven rectifiers1 | 8 |

| Fig. 1.10 | Push-pull DC-DC converter                                        | 0 |

| Fig. 1.11 | Half-bridge DC-DC converters                                     | 2 |

| Fig. 1.12 | Full-bridge DC-DC converters                                     | 3 |

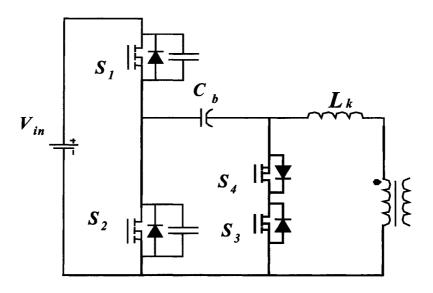

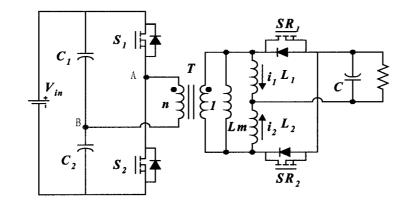

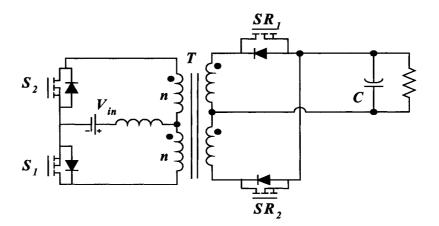

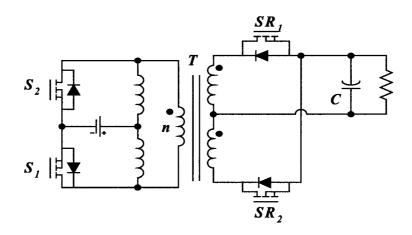

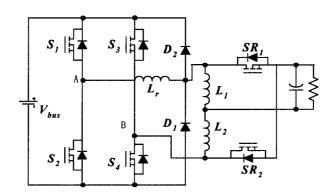

| Fig. 2.1  | Half-bridge DC-DC converter with current doubler rectifier       | 3 |

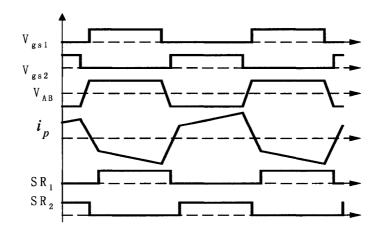

| Fig. 2.2  | Waveforms of half-bridge DC-DC converters                        | 5 |

| Fig. 2.3  | A DCS PWM modulation scheme                                      | 6 |

| Fig. 2.4  | Operation Modes Analysis                                         | 8 |

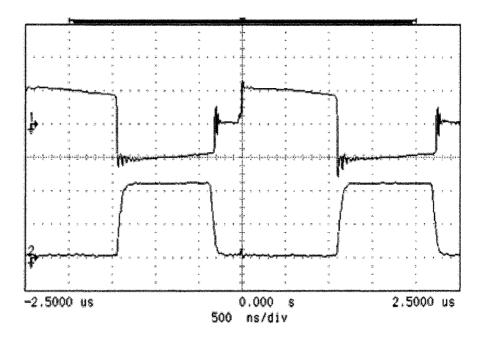

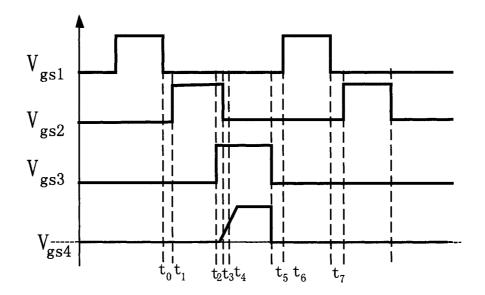

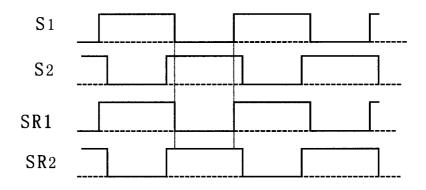

| Fig. 2.5  | Gate signals of S <sub>1</sub> , S <sub>2</sub> 4                | 5 |

| Fig. 2.6  | Zero-Voltage-Switching of switch S <sub>2</sub> 4                | 5 |

| Fig. 2.7  | Transformer waveforms of conventional symmetric control4         | 6 |

| Fig. 2.8  | Transformer waveforms of duty-cycle-shift control4               | 6 |

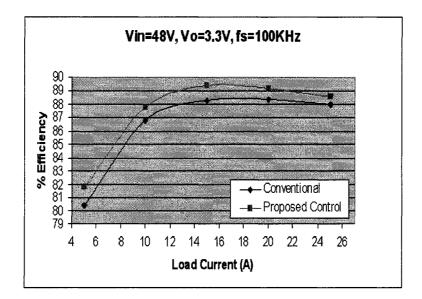

| Fig. 2.9  | Efficiency Comparison at 100 KHz4                                | 7 |

| Fig. 2.10 Efficiency Comparison at 200 KHz47                            |

|-------------------------------------------------------------------------|

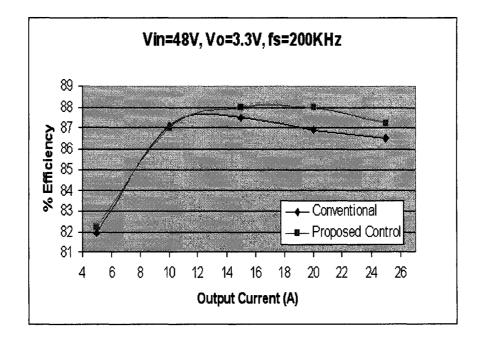

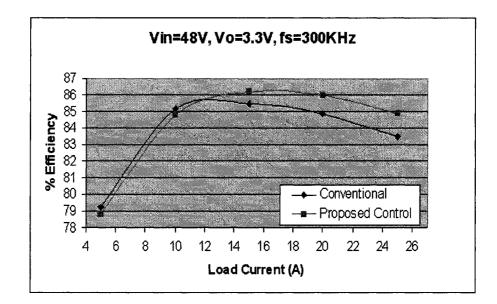

| Fig. 2.11 Efficiency Comparison at 300 KHz48                            |

| Fig. 2.12 Efficiency Comparison at 400 KHz48                            |

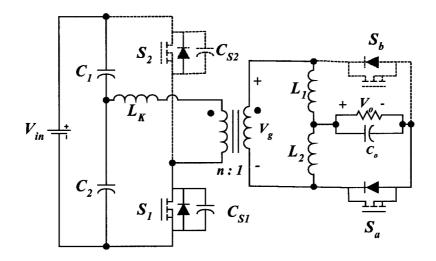

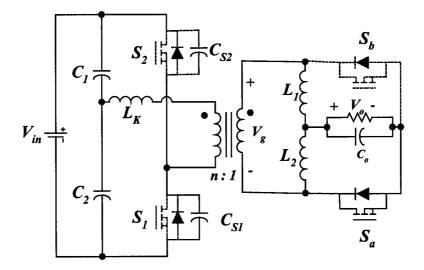

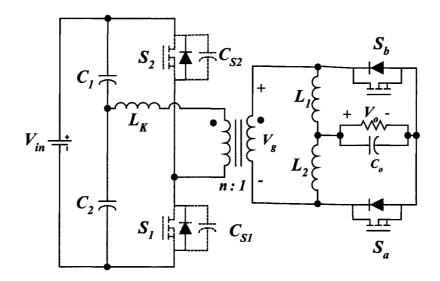

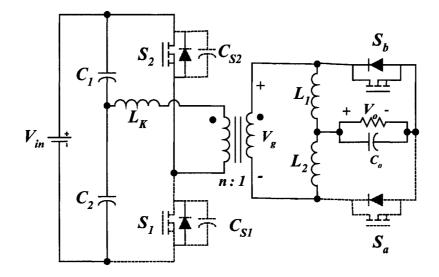

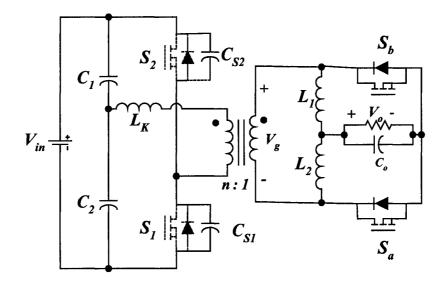

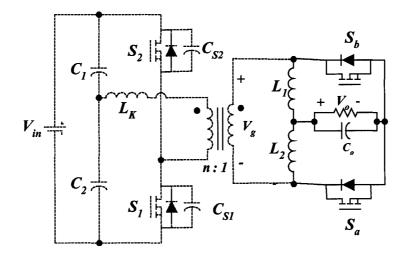

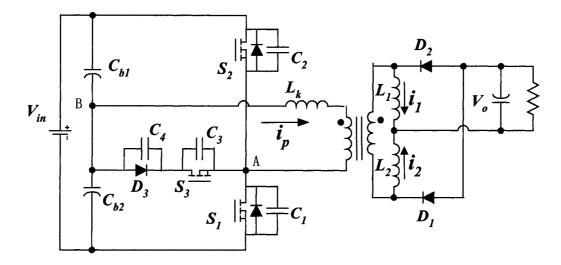

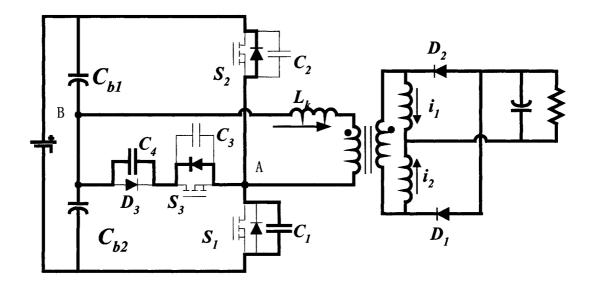

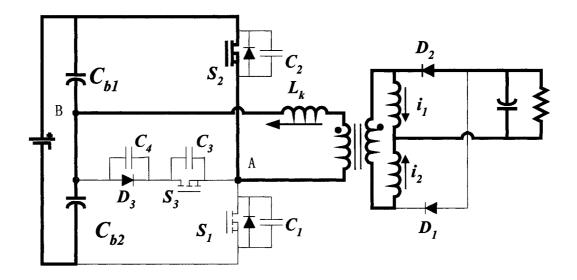

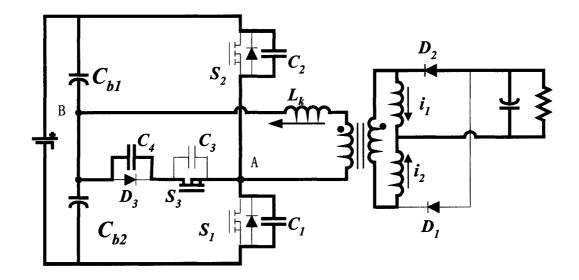

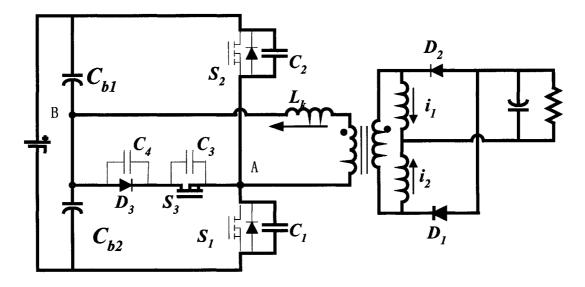

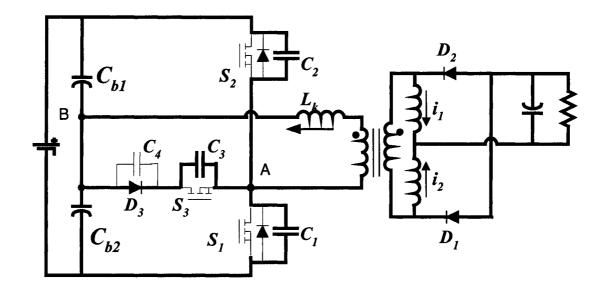

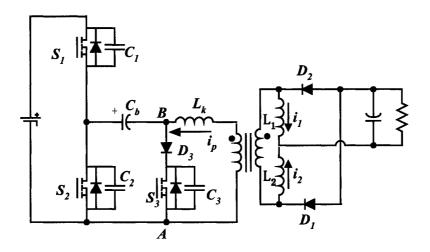

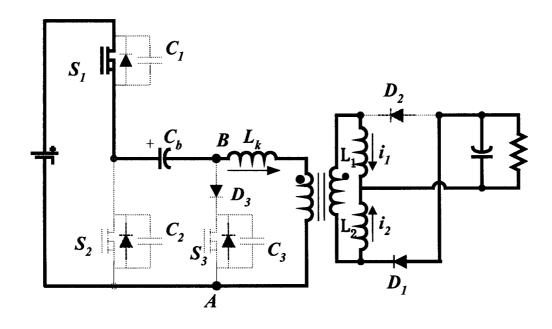

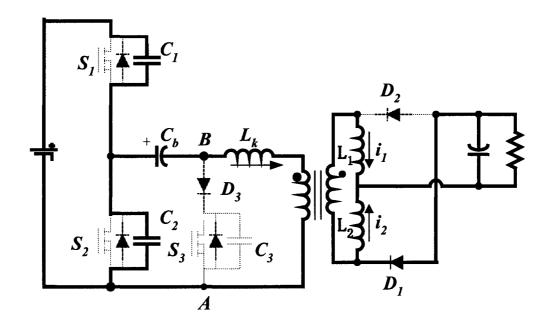

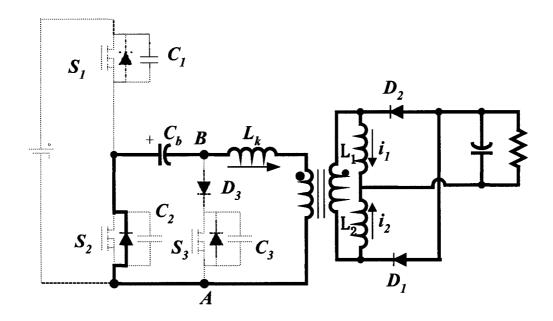

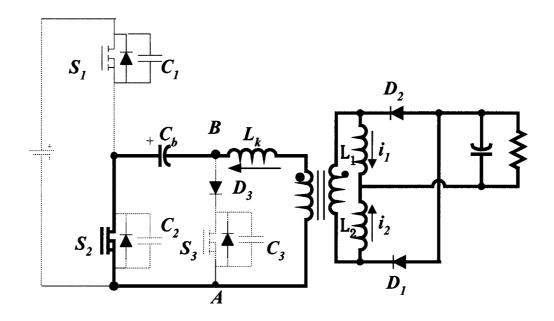

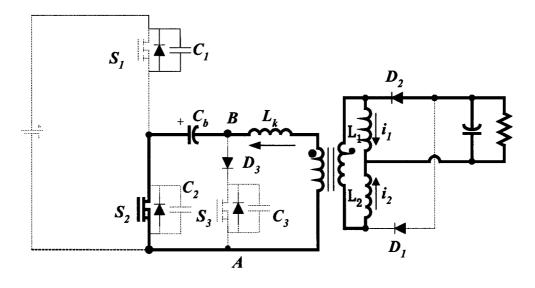

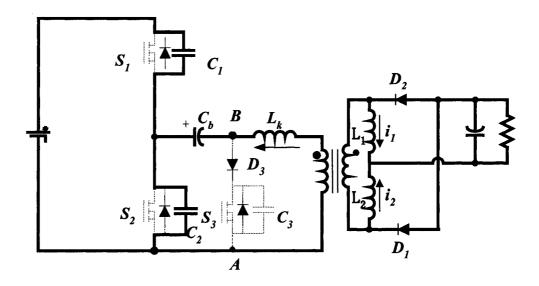

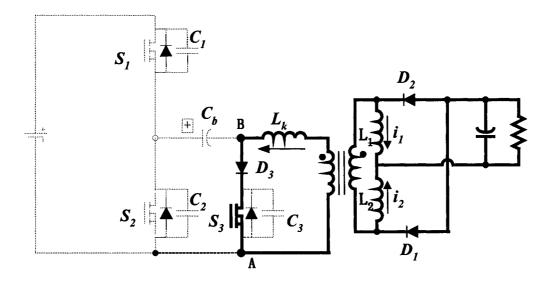

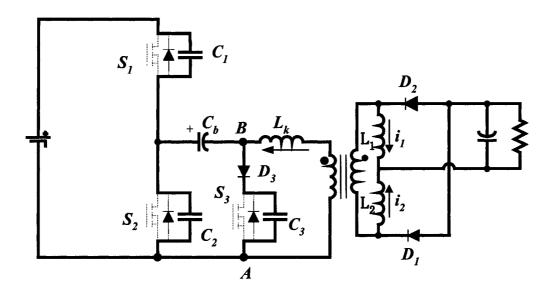

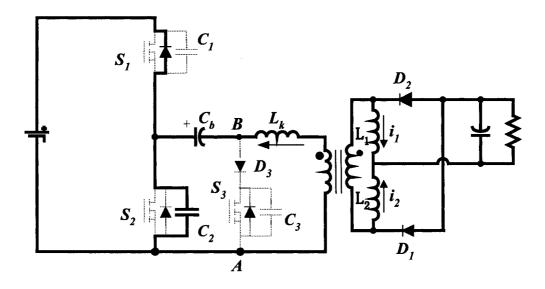

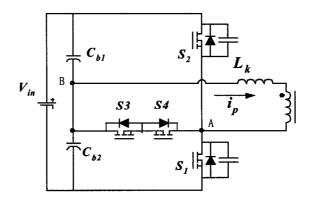

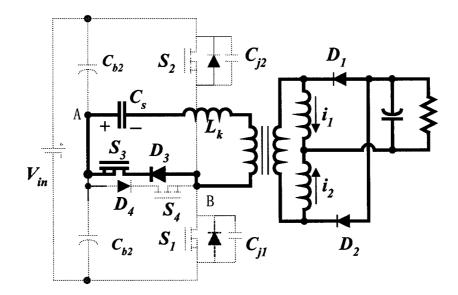

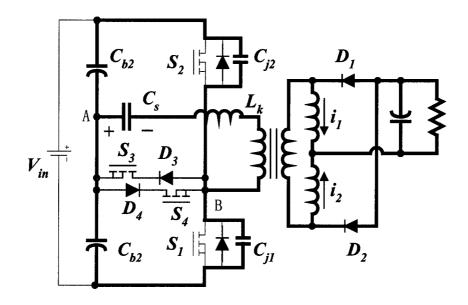

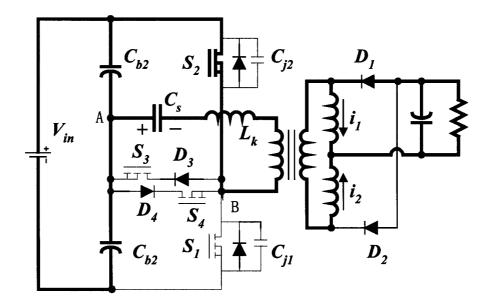

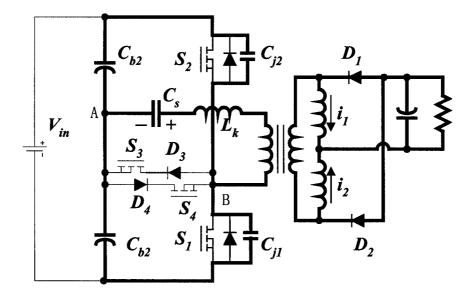

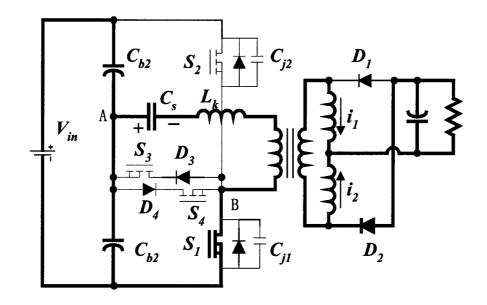

| Fig. 2.13 Proposed DCS controlled ZVS half bridge converter             |

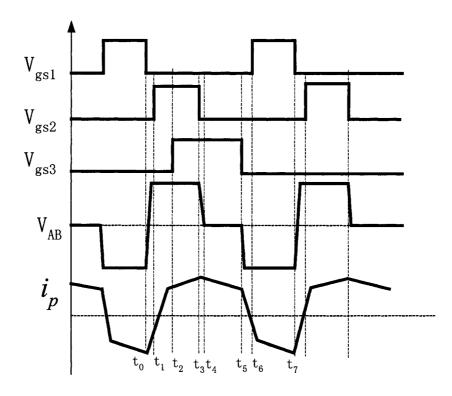

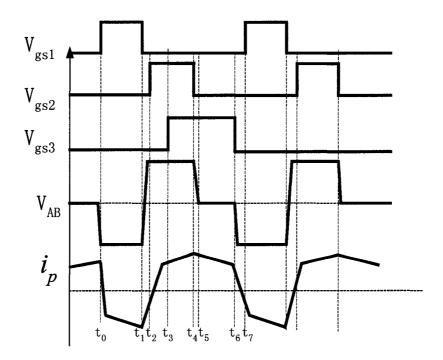

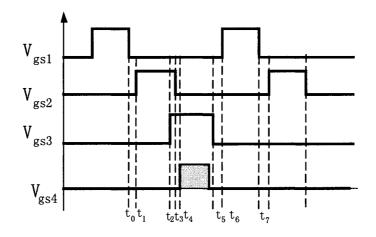

| Fig. 2.14 Key waveforms of the proposed ZVS half bridge converter       |

| Fig. 2.15 Operation Modes Analysis                                      |

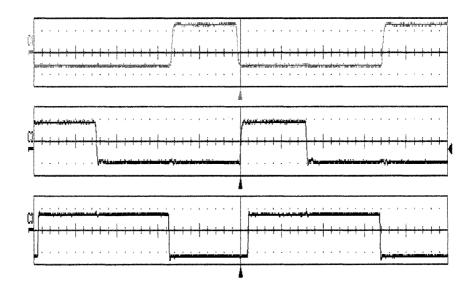

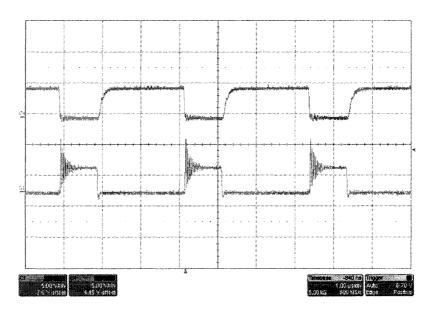

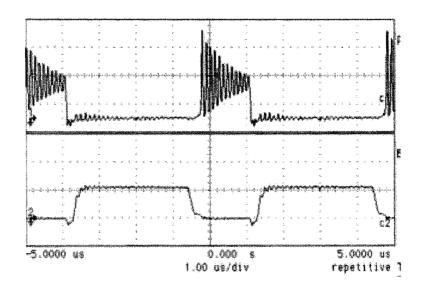

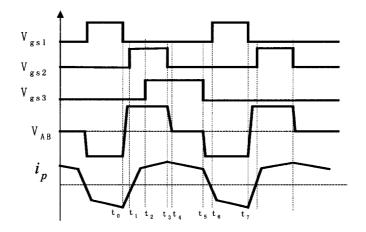

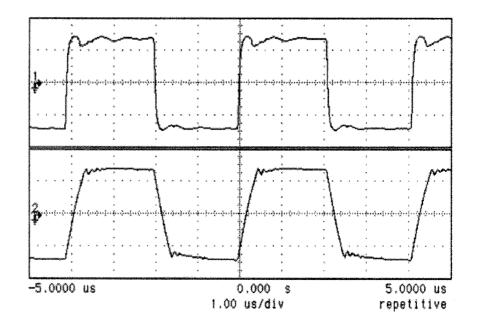

| Fig. 2.16 Gate drive signals of switch $S_1$ , $S_2$ and $S_3$          |

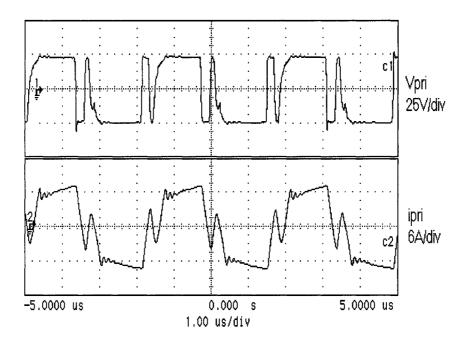

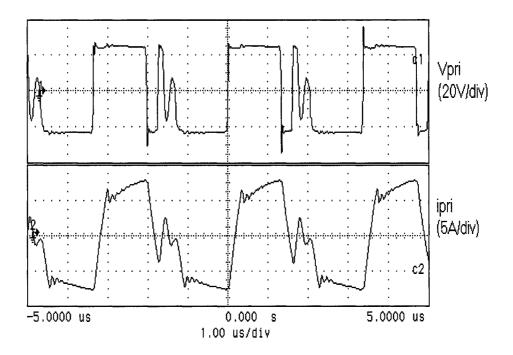

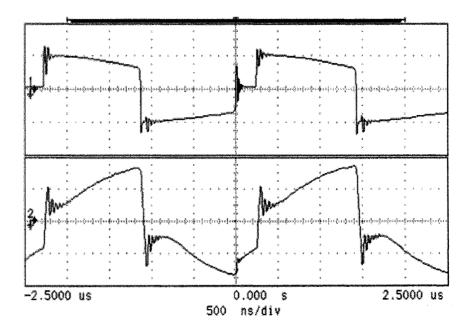

| Fig. 2.17 Transformer voltage and current                               |

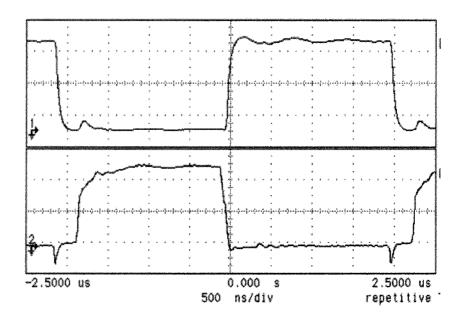

| Fig. 2.18 ZVS waveforms of the switch S <sub>1</sub> 63                 |

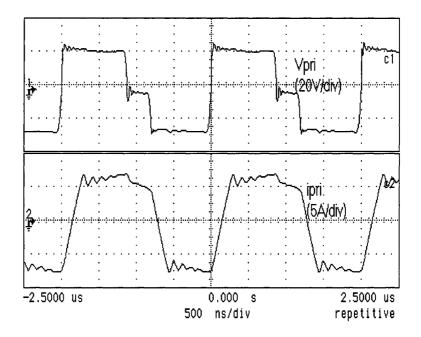

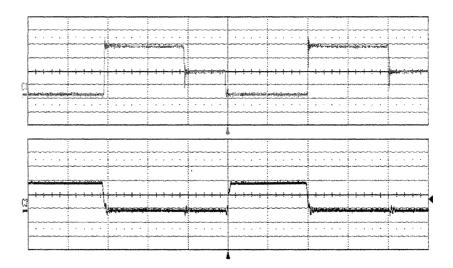

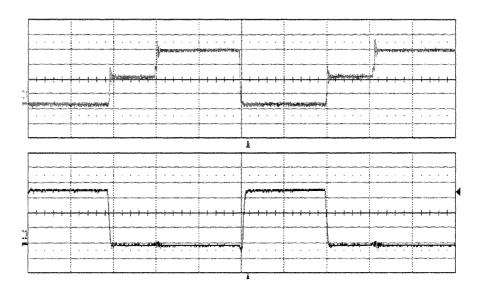

| Fig. 2.19 ZVS waveforms of switch S <sub>2</sub> 64                     |

| Fig. 2.20 ZVS waveforms of switch S <sub>3</sub> 64                     |

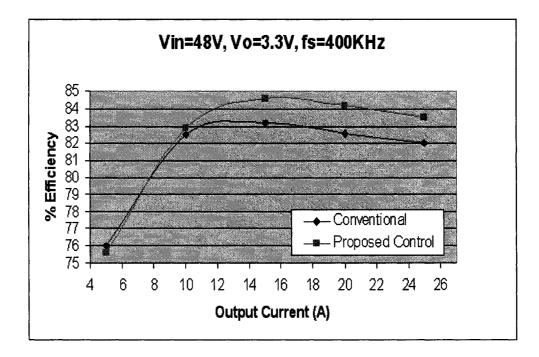

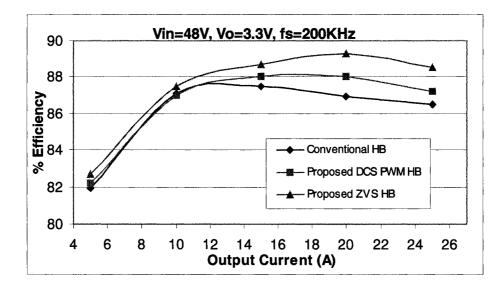

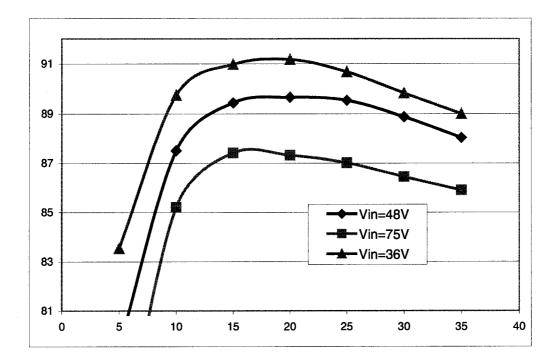

| Fig. 2.21 Efficiency Comparison at the switching frequency of 200 kHz65 |

| Fig. 2.22 Efficiency comparison at the switching frequency of 400 kHz66 |

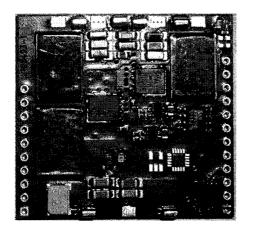

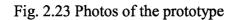

| Fig. 2.23 Photos of the prototype                                       |

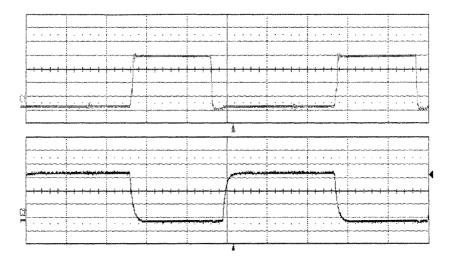

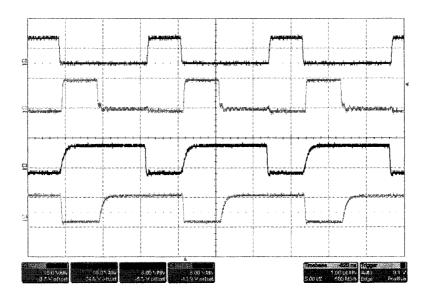

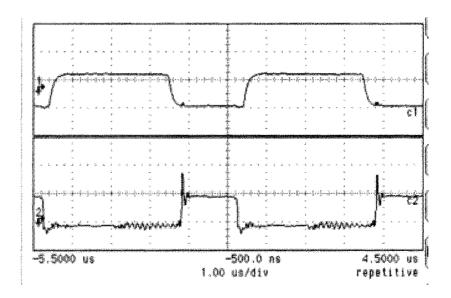

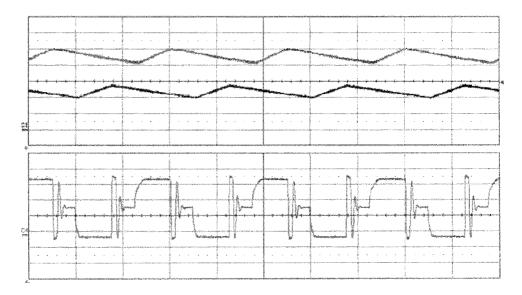

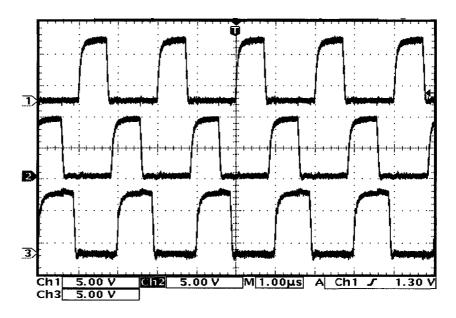

| Fig. 2.24 Gate drive voltage waveforms of primary switches              |

| Fig. 2.25 Waveforms of SR gate and V <sub>ds</sub>                      |

| Fig. 2.26 Waveforms of primary and secondary switch gate voltages       |

| Fig. 2.27 ZVS waveforms of a primary switches69                         |

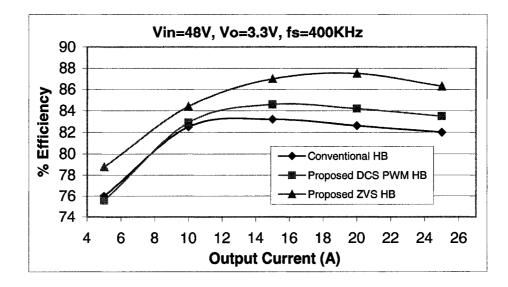

| Fig. 2.28 Prototype efficiency                                          |

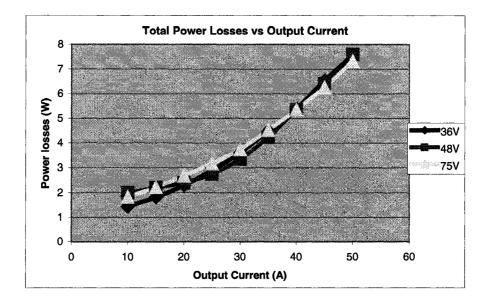

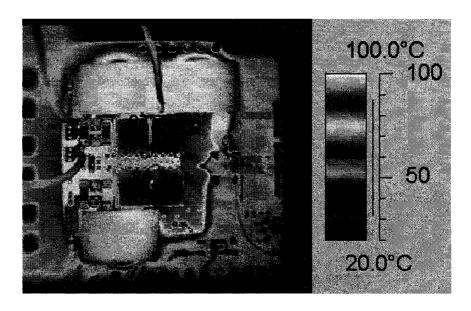

| Fig. 2.29 Prototype total power loss70                                  |

| Fig. 2.30 Prototype thermal picture70                                   |

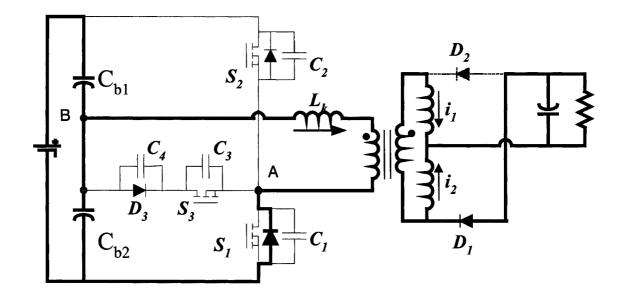

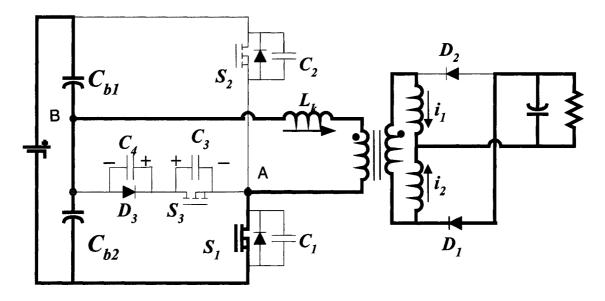

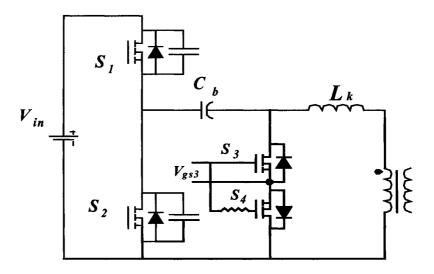

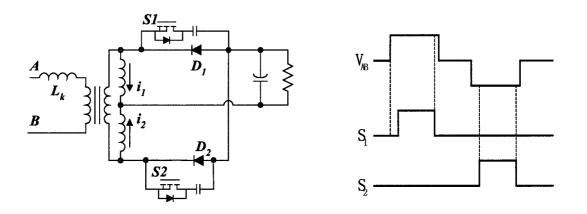

| Fig. 2.31 Modified ZVS DC-DC HB converter                               |

| Fig. 2.32 Waveforms of the Modified ZVS DC-DC HB converter73            |

| Fig. 2.33 Operational Modes                                               |

|---------------------------------------------------------------------------|

| Fig. 2.34 Prototype photo79                                               |

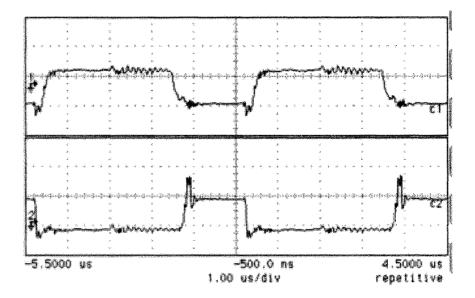

| Fig. 2.35 Waveforms of the Prototype80                                    |

| Fig. 2.36 Measured Efficiency of the prototype                            |

| Fig. 2.37 DCS HB converter with synchronous rectification                 |

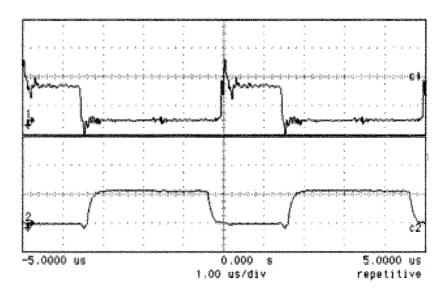

| Fig. 2.38 Gate drive waveforms                                            |

| Fig. 2.39 DCS HB converter with tied-gate SR                              |

| Fig. 2.40 Waveforms of DCS HB converter with tied-gate SR                 |

| Fig. 2.41 Modified DCS HB converter85                                     |

| Fig. 2.42 Modified DCS HB converter with tied-gate SR85                   |

| Fig. 3.1 Half-bridge isolated DC-DC converter90                           |

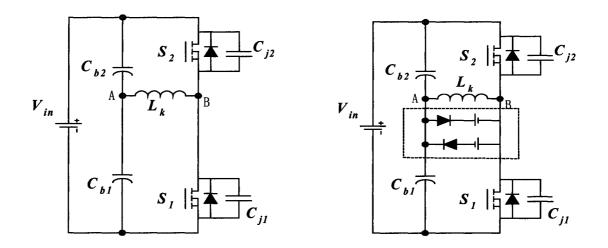

| Fig. 3.2 Equivalent oscillation circuits during the freewheeling period91 |

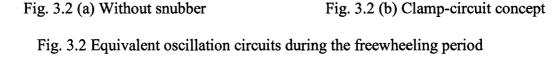

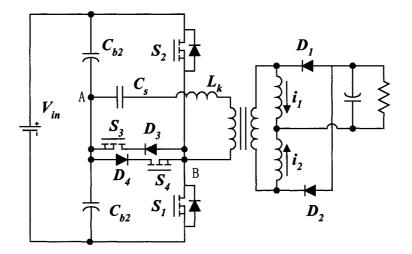

| Fig. 3.3 Active-clamp Half-bridge DC-DC converter                         |

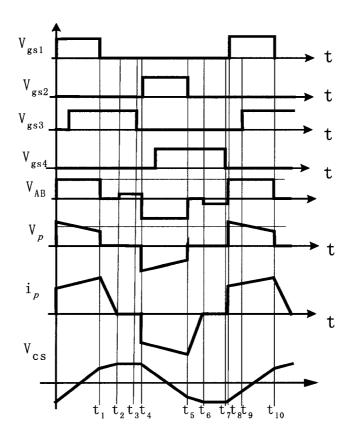

| Fig. 3.4 Key waveforms of the proposed topology94                         |

| Fig. 3.5 Operation modes analysis94                                       |

| Fig. 3.6 Two operation manners for the proposed converter                 |

| Fig. 3.7 Comparison between R/C snubber and the active-clamp snubber101   |

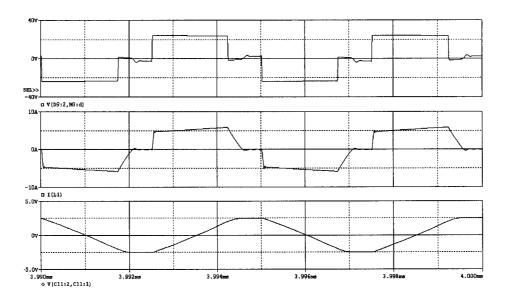

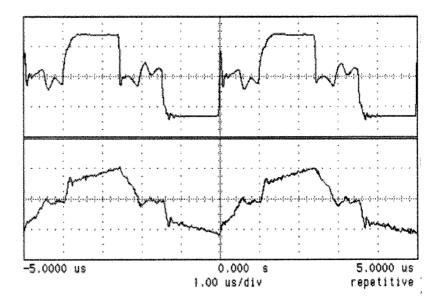

| Fig. 3.8 Transformer voltage and current waveforms (D=0.37)102            |

| Fig. 3.9 Transformer voltage and current waveforms (D=0.28)103            |

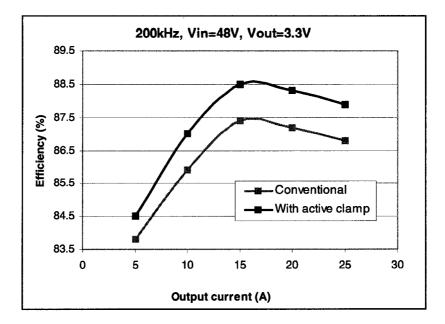

| Fig. 3.10 Efficiency comparison for the two snubbers104                   |

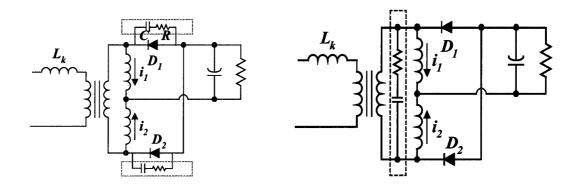

| Fig. 3.11 RC snubber circuits for a current doubler rectifier108          |

| Fig. 3.12 RCD snubber Circuits                                            |

| Fig. 3.13 Active-Clamp lossless Snubber                                   |

| Fig. 3.14 Reactor snubber circuits                                                |

|-----------------------------------------------------------------------------------|

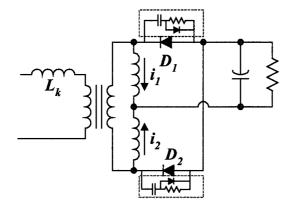

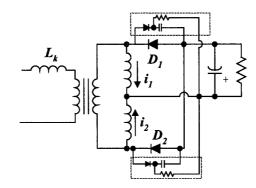

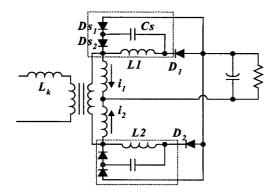

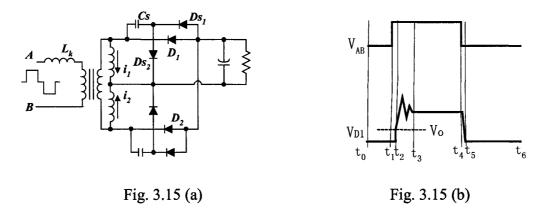

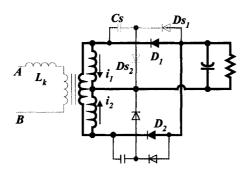

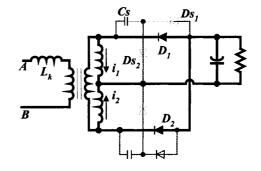

| Fig. 3.15 2D-1C snubber circuits                                                  |

| Fig. 3.16 Operational modes of the 2D-1C snubber topology113                      |

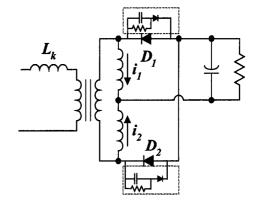

| Fig. 3.17 3D-2C snubber circuit116                                                |

| Fig. 3.18 Two key modes of operation117                                           |

| Fig. 3.19 Experimental Half-bridge DC-DC converter118                             |

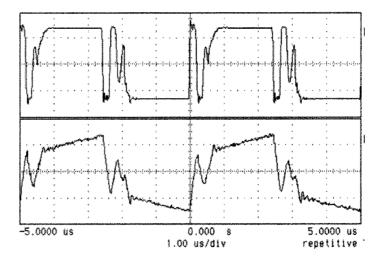

| Fig. 3.20 Waveforms of the RC and RCD snubbers119                                 |

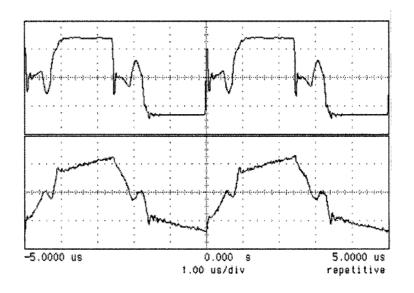

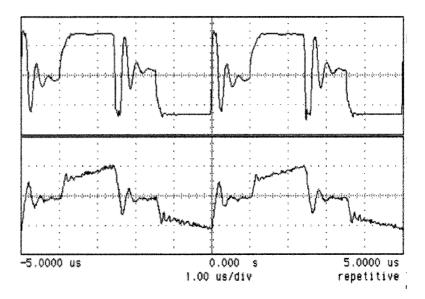

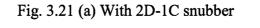

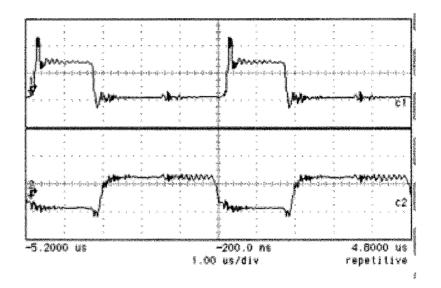

| Fig. 3.21 Waveforms of the proposed snubbers121                                   |

| Fig. 3.22 Efficiency comparison of snubbers (fs=200 kHz)122                       |

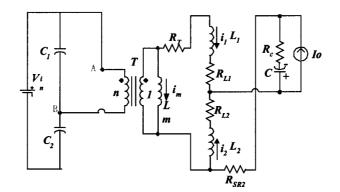

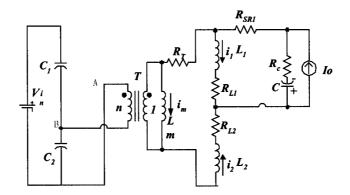

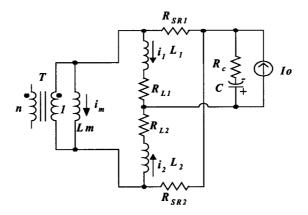

| Fig. 4.1 CDR Half-bridge DC-DC converter                                          |

| Fig. 4.2 Mode 1, S1 is on                                                         |

| Fig. 4.3 Mode 2: S2 is on127                                                      |

| Fig. 4.4 Mode 3: Both S1 and S2 are off128                                        |

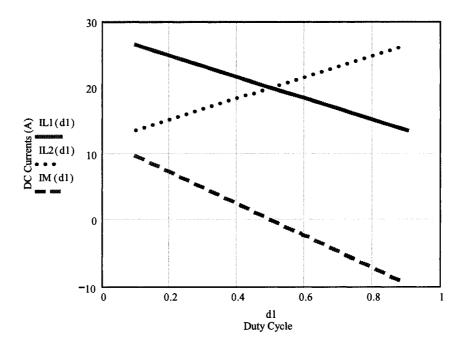

| Fig. 4.5 Transformer and inductor DC currents vs. duty cycle134                   |

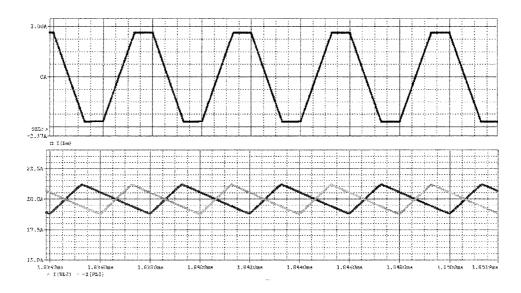

| Fig. 4.6 Waveforms of symmetric HB converter under symmetric duty cycles and      |

| inductor DCR values137                                                            |

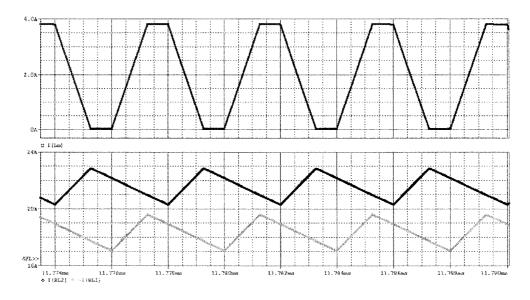

| Fig. 4.7 Waveforms of the symmetric HB converter under asymmetric inductor DCR    |

| values137                                                                         |

| Fig. 4.8 Waveforms of asymmetric HB converter with asymmetric duty cycles and     |

| symmetric inductors DCR138                                                        |

| Fig. 4.9 HB DC-DC converter under symmetric conditions                            |

| Fig. 4.10 Symmetric HB DC-DC converter under asymmetric SR channel resistance and |

| symmetric inductor DCR values139                                                  |

| Fig. 4.11 Symmetric HB converter under asymmetric inductor DCR values and       |

|---------------------------------------------------------------------------------|

| symmetric SR channel resistance139                                              |

| Fig. 4.12 Modified Half-bridge DC-DC converter141                               |

| Fig. 4.13 Mode 1: S <sub>1</sub> is on142                                       |

| Fig. 4.14 Mode 2: S <sub>2</sub> is on143                                       |

| Fig. 4.15 Mode 3: Both $S_1$ and $S_2$ are off143                               |

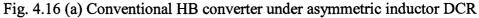

| Fig. 4.16 Current sharing comparison between conventional and modified HB DC-DC |

| converter147                                                                    |

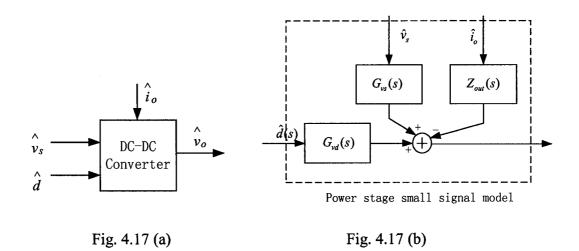

| Fig. 4.17 Power stage block of DC-DC converters                                 |

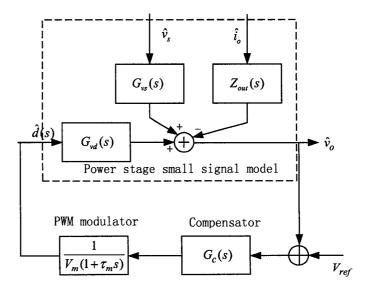

| Fig. 4.18 Closed-loop controlled DC-DC converter                                |

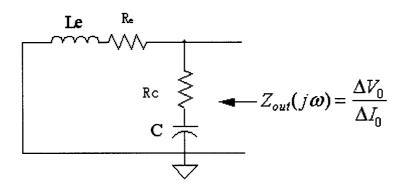

| Fig. 4.19 Open-loop output impedance equivalent circuit                         |

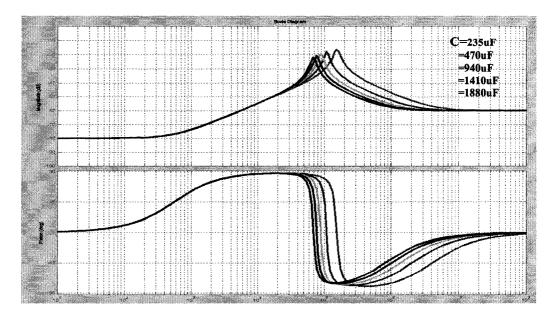

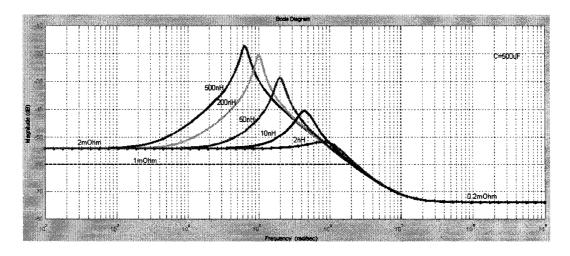

| Fig. 4.20 Open-loop output impedance (dB) and phase curve154                    |

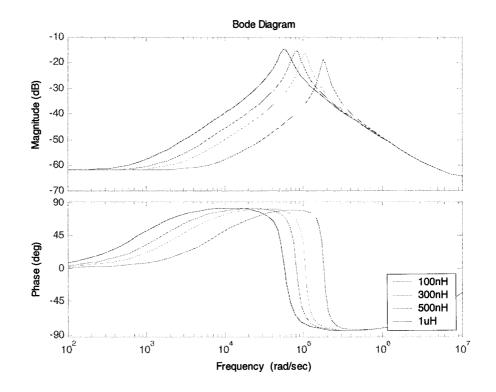

| Fig. 4.21 Open-loop output impedance with a variety of filter inductance        |

| Fig. 4.22 A closed-loop design and output impedances                            |

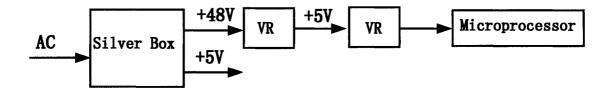

| Fig. 5.1 Conventional desktop power architecture159                             |

| Fig. 5.2 A desktop power management architecture159                             |

| Fig. 5.3 A alternative power management architecture                            |

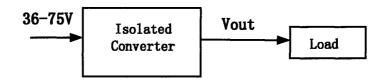

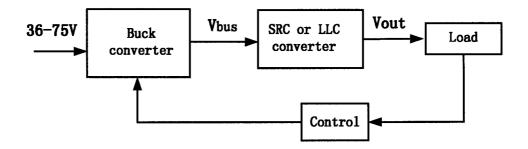

| Fig. 5.4 Telecom isolated DC-DC conversion architecture                         |

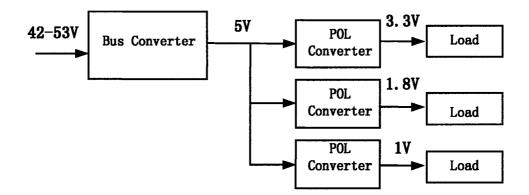

| Fig. 5.5 IBA architecture164                                                    |

| Fig. 5.6 A two-stage approach of brick converter166                             |

| Fig. 5.7 Half-bridge DC-DC converter167                                         |

| Fig. 5.8 Full-bridge DC-DC converter                                            |

| Fig. 5.9 Push-pull DC-DC converter                                              |

| Fig. 5.10 Waveforms of full-duty-cycle bridge DC-DC converters                         |

|----------------------------------------------------------------------------------------|

| Fig. 5.11 Boost-type push-pull DC-DC converter169                                      |

| Fig. 5.12 Boost-type current-divider DC-DC converter                                   |

| Fig. 5.13 Boost-type current-divider DC-DC converter                                   |

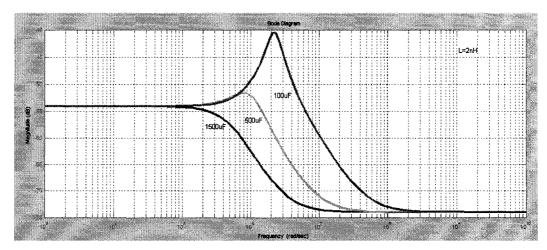

| Fig. 5.14 Open-loop-output impedance with varied filter inductance                     |

| Fig. 5.15 I Open-loop-output impedance with varied filter capacitance                  |

| Fig. 5.16 Output voltage response to load change with 1A/1nS current slew rate173      |

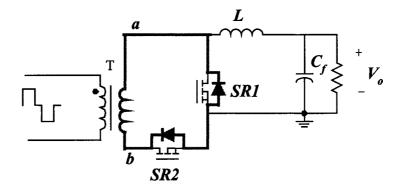

| Fig. 5.17 Half-wave rectifier topology174                                              |

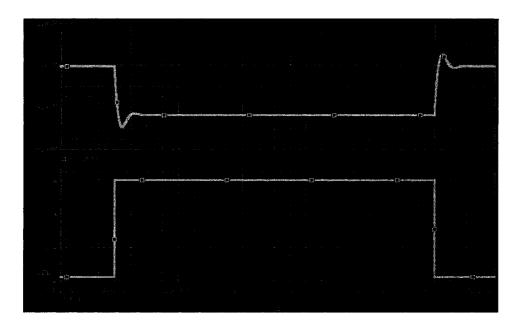

| Fig. 5.18 SR <sub>1</sub> reverse-recovery waveforms175                                |

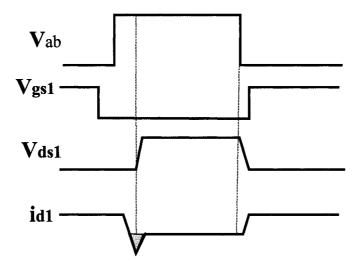

| Fig. 5.19 Waveforms of the synchronous rectifier176                                    |

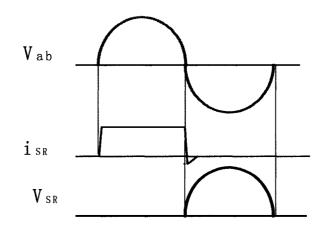

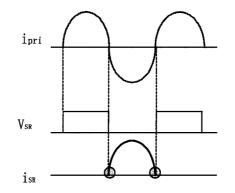

| Fig. 5.20 Class-D Half-bridge series parallel resonant converter (SPRC)177             |

| Fig. 5.21 Waveforms of the synchronous rectifier178                                    |

| Fig. 5.22 Class-D Half-bridge series resonant DC-DC converter                          |

| Fig. 5.23 S Class-D Half-bridge LLC resonant DC-DC converter                           |

| Fig. 5.24 Class-D full-bridge LLC resonant DC-DC converter179                          |

| Fig. 5.25 DC voltage gain characteristics vs. normalized switching frequencies181      |

| Fig. 5.26 Two-stage approach with SRC or LLC converter in the 1 <sup>st</sup> stage    |

| Fig. 5.27 Two-stage approach with SRC or LLC converter in the 2 <sup>nd</sup> stage182 |

| Fig. 5.28 Capacitance boost architecture                                               |

| Fig. 5.29 Two-stage approach for high step-down converter                              |

| Fig. 5.30 Asymmetric HB ZVS DC-DC converter                                            |

| Fig. 5.31 Waveforms of Asymmetric HB DC-DC converter                                   |

| Fig. 5.32 A family of non-isolated ZVS DC-DC converter                                 |

| Fig. 5.33 Non-isolated DCS topology                                    | 194         |

|------------------------------------------------------------------------|-------------|

| Fig. 5.34 Key waveforms                                                | 194         |

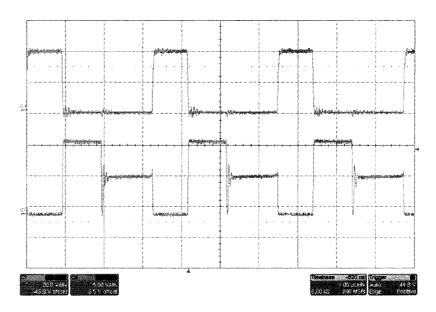

| Fig. 5.35 Experimental results of the first-stage converter            | 195         |

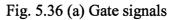

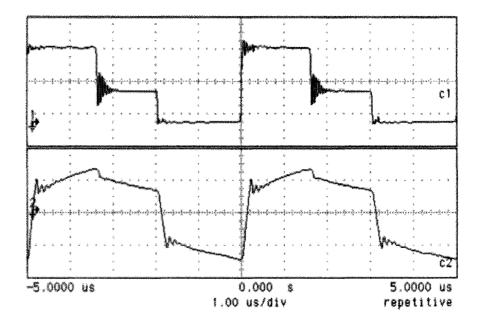

| Fig. 5.36 Experimental results of the non-isolated DCS ZVS HB DC-DC co | nverters197 |

### **1. INTRODUCTION**

### 1.1 Research Background and Motivation

The advances in VLSI (very large scale integration) technologies impose a new challenge for delivering high-quality power to digital ICs. As more and more transistors are integrated into the integrated circuit chip, and with the transistors operating at higher switching frequencies, the power level to supply the chip is significantly increasing [A1-A3].

Recently, solutions based on distributed power system (DPS) architectures [A4-A6] are becoming very popular, especially in multi-board electronic equipment. This technique divides the power conversion scheme from the input source to the load in two stages. The first stage generates an intermediate voltage bus from the AC mains. This DC bus supplies power to the load through different DC-DC converters, located on the same board where the supplied circuits are connected. These DC-DC converters are normally referred to as On Board Converters (OBC).

A typical scheme showing a distributed architecture is shown in Fig. 1.1 [A4]. Distributed architectures present many advantages compared with centralized solutions. These advantages could be summarized as follows [A7]:

- Improved quality of output voltage

- Easier thermal management

- Easier partial redundancy

- Higher power density

- Simpler and cheaper wiring

- Improved reliability

Fig. 1.1 Architecture of distributed power system (DPS)

In distributed power architecture, there is a very important converter that is the last one in the power chain — it is the On Board Converter (OBC). The OBCs supply power directly to the load (IC and microprocessor) and is mounted on the same PCB. Generally, the input voltage bus of OBCs range from 36V~75V with nominal 48V input.

Size is the main concern in the design of on board converters for distributed power supplies. These converters should be as small as possible in order to use them as another component in the design of the load PCB. One idea to reduce the size of a DC-DC converter is to increase switching frequency, because this way the value of reactive components is lower. Transformers, inductors and capacitors become smaller as the switching frequency increases if their size is dependent on their reactive value. However, this trend is reversed when their size depends on their power losses. The main trend in the design of on-board DC-DC converters in the last years was aimed at very high switching frequencies and at modifying the power circuits to keep switching losses under control.

Lower power consumption implies higher functional integration, hence the voltage supplying integrated circuits gradually decreased because power consumption in an integrated circuit decreases significantly with the reduction of supply voltage. This way, the density of integration circuits keeps increasing and the ICs may operate at higher speed [A1-A3]. However, lower-voltage and higher-current powering requirements pose challenges for the power management designer. For example, according to the Intel roadmap, microprocessors requiring 1V and 100~130A will be available in the market in the next two to four years [A1]. This increase of load current and reduction of its voltage are also accompanied by an increased transient current slew rate at the processor power bus.

With lower voltage, the performance of electronic circuits will improve, but the design of low voltage power converters will be much more difficult, mainly due to the lower efficiency of the low voltage solution. Lower efficiency leads to thermal management difficulties, which prevent size reduction of OBCs.

Some manufactures offer small OBCs featuring very high power densities. However, these converters usually need a large heat sink to obtain high reliability. In most applications, the size of both the converter and the heat sink should be taken into account. These losses are the main constraint in the design if small OBCs are working at high switching frequencies. Efficiency is a key parameter, including view of how good the power conversion is and also the quality of the thermal management. Through advanced technologies, OBCs can achieve high efficiency such that the heat sink can be removed and the converter size is significantly reduced. Fig. 1.2 illustrates the main topics that affect the size of On Board Converters [A7].

Fig. 1.2 Main factors affecting the design of low output voltage OBCs

With lower output voltage, the conduction loss in the output stage rectifiers becomes more significant and results in considerably reduced efficiency. The efficiency improvement of on-board low-voltage DC-DC converters mainly depends on the components, especially semiconductors [A8-A10]. However, topology and control design is very important for the converter performance based on a specific level of components [A11-A20]. Especially, power stage topologies based on soft-switching/resonant approaches have been recently investigated for high-power density high-efficiency applications [A11-A20]. Advanced topology technology is one of the main approaches to reduce DC-DC converter size and increase power density [A23-A30]. Moreover, with higher switching frequencies, passive components value (such as L and C) can be used

under certain current and voltage ripples. Thus, the related filter phase delay is reduced and better transient response can be achieved.

A low voltage may be achieved through two on-board DC-DC converters in a series. As shown in Fig. 1.1, following the first on-board DC-DC converter, a low voltage Voltage Regulator Module (VRM) is utilized to further step down the voltage. Usually, the second-stage VRM is non-isolated [A2]. Generally, high-density low-voltage on-board DC-DC converters can be divided into two categories: isolated DC-DC converters and non-isolated DC-DC converters. Non-isolated topologies are usually used for 5V~12V input bus applications while isolated topologies are suited for high-input voltage applications such as 48V nominal input, wherein the isolation transformer provides electrical isolation between inputs and outputs. Moreover, the transformer helps to step down the input voltages to output with increased duty cycle. In this way, converter switching and conduction losses are reduced, and higher efficiency can be achieved [A14-A15].

### 1.2 <u>Review of Non-Isolated Multiphase VRM Technology</u>

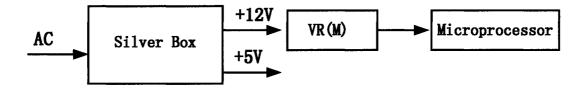

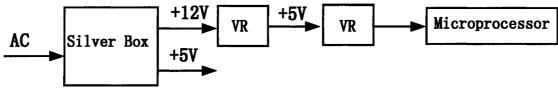

A typical example of non-isolated on-board DC-DC converters is the Voltage Regulator Module (VRM) for computer microprocessors. The centralized silver box is a typical power source in computer systems. However, with lower voltage and higher current demands, the parasitic resistance and inductance between the centralized silver box and the microprocessor have a severe, negative impact on power quality. It is not practical to use the centralized silver box to provide power directly to the microprocessor [A12]. The power supply architecture must be changed. The point-of-load regulation system is used to deliver highly accurate voltage to the microprocessor, where a dedicated DC-DC converter, the VRM, is placed close to the microprocessor in order to minimize the parasitic impedance between the VRM and microprocessors. Fig. 1.3 shows the power delivery architecture for low-end computer systems, where the on-board VRM is supplied by 5V or 12V input voltage.

Fig. 1.3 Power delivery architecture for low-end computer systems

Most of today's VRMs draw power from the 12V output of a silver box due to the voltage drop through 5V voltage bus. To achieve fast transient response and better thermal management, the multi-phase buck converter techniques are widely employed in industry. Conventional multi-phase VRMs employ PI controllers for voltage regulation. However, PI compensators limit the transient response of the control loop and the system. Hysteretic voltage control can improve the transient response owing to the bang-bang control concept [A30].

Non-isolated DC-DC converters are generally buck-derived type. To reduce the output current ripple and for better thermal management, interleaved multi-channels are employed [A12, A14]. An interleaved multi-channel buck converter is shown in Fig. 1.4, which consists of N identical buck converters with interconnected inputs and outputs.

The duty cycle of adjacent channels have a phase shift of  $360^{\circ}/N$ . The main benefit of multiphase technology is the ripple cancellation effect, which enables the use of small inductance to both improve transient response and minimize the output capacitance [A12].

Multiphase converters interleave the inductor currents in individual channels and therefore greatly reduce the total current ripples flowing into the output capacitance. With the current ripple reduction, the output voltage ripples are greatly reduced, which enables the use of very small inductance to improvement response. Therefore small output capacitance can be used to meet the transient requirements. The reduced output voltage ripples also allow more tolerance for voltage variations during the load transient, because the voltage ripple will consume a smaller part of the total voltage tolerance budget and output capacitance.

Fig. 1.4 Interleaved multi-channel architecture

Recently, multiphase converters have been widely used for 12V-input VRMs as a standard practice. Correspondingly, many semiconductor companies, such as Intersil, Semitech, National Semiconductor, on Semiconductor, Analog Devices and Voltera, have produced dedicated control chips for multiphase VRMs.

### 1.3 <u>Review of Technology in Isolated DC-DC Converters</u>

The non-isolated 12V input buck converters are required to have high step-down ratios when their output voltage is very low, which makes the converters to operate at small duty cycles and asymmetric transient responses [A14]. With the increase of the required power levels, the 12V input bus voltage may not be able to satisfy the requirements any longer, because the increased distribution loss degrades efficiency. In this case, 48V input-voltage isolated converters are more efficient than 12V input non-isolated VRs, especially for "server" and "workstation" computer systems [A15]. With the isolation transformer, the duty cycle can be optimized and better efficiency is expected [A15]. More importantly, the 48V voltage bus reduces the distribution conduction losses due to the low voltage drop than 12V voltage bus. Generally, for data power systems, the on-board DC-DC converter has a relatively stable input voltage of 48V; for telecom power systems, the input voltage isolated for point-of-load, on-board DC-DC converters. From this point of view, higher-input-voltage isolated DC-DC converters are prevailing in telecom and datacom applications.

### 1.3.1 State-of-the-Art Rectifiers

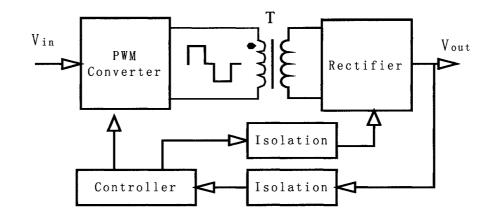

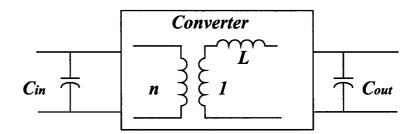

Without exception, isolation transformers are indispensable parts in isolated DC-DC converters. The conversional isolated Pulse-Width-Modulation (PWM) DC-DC converter structure is shown in Fig. 1.5, which consists of three parts: PWM converter, isolated transformer and rectifier. PWM converter behaves as an inverter to generate AC voltage or current that is applied to transformer primary winding. The transformer delivers AC voltage or current from the primary side to the secondary side and provides electrical isolation. With a transformer turns ratio, the converter may work at a desirable duty cycle and achieve good efficiency. AC voltages or currents are delivered to the transformer secondary side, and through the rectifier, a DC voltage can be obtained from the output. Hence, the energy processing in a DC-DC converter is DC-AC-transformer-AC-DC.

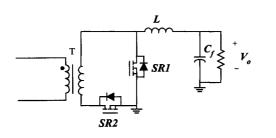

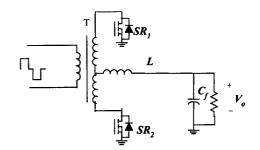

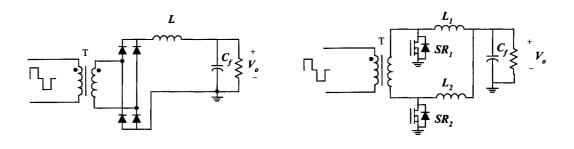

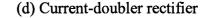

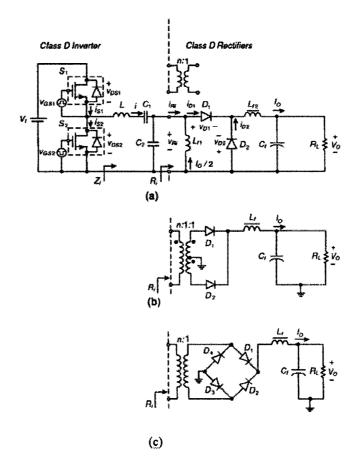

Conventional voltage-driven rectifiers are shown in Fig. 1.6, where inductor(s) are added to the transformer secondary side because a voltage source cannot be applied to a capacitor directly. Forward rectifier is a "half-wave" rectification type, which means the transformer output current is asymmetric with unidirectional DC current with AC components; thus transformer windings and rectifier utilization are limited. All other rectifiers and transformers are symmetric with bi-directional current, and transformer magnetics resets itself without external winding or circuitry.

Fig. 1.5 Architecture of conventional PWM isolated DC-DC converters

PWM converters in Fig. 1.5 can be a variety of state-of-the-art topologies, such as forward, flyback, two-switch forward, push pull, half bridge and full bridge. Those topologies can be buck type or boost type according to the fact that filter inductor(s) are located at inputs or output. Correspondingly, they can be called current-fed or voltage-fed DC-DC converters. In general, a current-fed PWM converter generates an AC current feeding to a transformer. Likewise, a voltage-fed PWM converter generates an AC voltage feeding to a transformer. Correspondingly, voltage-driven rectifiers are connected with the transformer secondary side for voltage-fed (buck-derived) converters; current-driven rectifiers are connected with the transformer secondary side for current-fed (buck-derived) converters.

Among those secondary-side rectification topologies, the forward topology [A13, A18, A24, A25, A26, A34] has the simplest structure. However, it is the least suitable for low-voltage high-current applications. Namely, the forward topology requires a larger filter inductance and exhibits larger rectification losses than a center-tapped or current-

doubler rectifier [A41]. In fact, in the center-tapped topology, the frequency of the output-filter-inductor voltage waveforms is twice the switching frequency, while in the forward topology it is equal to the switching frequency. As a result, the required value of the filter inductance in the center-tapped topology is significantly smaller than that in the forward rectifier. A center-tapped rectifier is a popular rectification topology and is a kind of "full-wave" rectifier. The drawback of the center-tapped rectifier is that the transformer is tapped and two secondary windings carry output currents alternatively. In other words, the transformer windings are not fully utilized [A32].

Compared to center-tapped topology, a full-bridge rectifier reduces secondary-side windings to one. Also, the winding carries AC current, and it increases transformer utilization [A32, A33]. However, since output current goes through two rectifier diodes (or synchronous rectifiers), the rectifier conduction loss is significant at low-voltage-output applications due to the increased forward voltage drop across rectifiers. The full-bridge rectifier is usually used for higher output voltage applications.

For low-voltage and high current applications, the current-doubler rectifier is widely used in industry and recognized as a good rectification topology [A32-A34, A41]. Since the current through the transformer secondary winding is half the output current, the current-doubler rectifier minimizes the secondary-winding *rms* current and conduction losses. Since two filter inductors share the output current, easier design and better thermal management for output inductors is achieved [A41]. Moreover, the current-doubler scheme minimizes the number of high-current interconnections to simplify the secondary layout and further reduce the layout-related losses.

11

(a) Forward rectifier

(b) Center-tapped rectifier

(c) Full-bridge rectifier

Fig. 1.6 Voltage-driven rectifiers

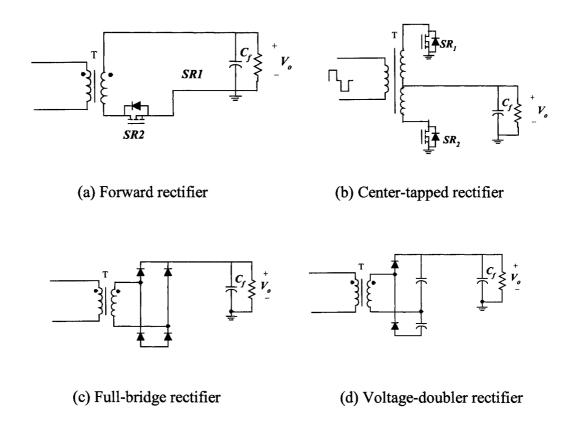

As mentioned above, if an AC current source is connected to a transformer primary winding, a current-driven transformer and corresponding rectifier should be applied to this kind of PWM converter. Fig. 1.7 shows four types of conventional current-driven rectifiers. Similar to the voltage-driven rectifier, there are four typical rectification types, wherein forward rectifier is asymmetric, and others are symmetric. In forward rectifier, a reset scheme has to be applied to the transformer.

In current-driven rectifiers, because transformers work as current sources, the secondary filter inductors in voltage-driven rectifiers can be removed. In fact, the filter

inductor is moved to the transformer primary side. Because the DC-DC converter input is a voltage source, to form a current source input, an inductor has to be placed in the primary side. The inductor is actually a filter inductor. It should be noted that for lowvoltage high-current output applications, putting inductor in the primary is good, because primary circuitry has higher voltage and lower current stresses, which means smaller current flows through the primary filter inductor. In that case, low-current inductors are easier to design than high-current inductors. However, compared with PWM voltagedriven rectifiers, the filter inductor in the PWM current-driven rectifiers freewheels on the primary side. Therefore, during switch-off periods, no power supplies the output capacitors, which results in discontinuous output currents and larger output voltage ripples. Actually, the flyback converter falls into this category of current-fed rectifiers.

Fig. 1.7 Current-driven rectifiers

To achieve a continuous power-supplying output capacitor and load, full duty cycle can be applied to primary switches. In other words, the freewheeling period of the primary inductors is eliminated [A42-A43]. An example of this is shown in Fig.1.8 [A42], where two DC-DC converter stages are in series to provide a step-down lowvoltage conversion. Secondary stage is a current-fed push-pull topology with a centertapped current-driven rectifier on the secondary side. Push pull topology operates at 50 percent duty cycle, thus the first-stage buck converter is responsible for voltage regulation. A control loop is closed through the first stage. Actually, an output filter capacitor and load can be reflected to the transformer primary side as a capacitor paralleled with a resistor. The secondary stage is just like a DC transformer.

Fig. 1.8 An application of a center-tapped current-driven rectifier

#### 1.3.2 State-of-the-Art PWM DC-DC Converters

In low-voltage applications, buck-derived DC-DC topologies prevail in commercially available products. Those topologies include flyback, forward, push pull, half bridge and full bridge.

Flyback topology is an isolated buck-boost topology. The advantages of this topology are simple structure and low cost. The transformer magnetizing inductance is charged and stores energy when the primary switch is turned on, and the stored energy is transferred to the output capacitor when the primary switch is turned off. Because there is no power supplying output capacitor and load, the output current is discontinuous, which results in large output current and voltage ripple. For low-voltage high-current applications, this feature could be a disaster, because the energy stored in the output capacitor is proportional to the square of output voltage value and a discontinuous current results in large output voltage ripple [A38]. Generally speaking, flyback topology is not suitable for low-voltage high-current applications.

Forward topology is the simplest among buck-derived topologies [A24, A25, A26, A34, A35]. It requires a single switch and therefore finds applications at lower power levels than those commonly encountered in the half-bridge and full-bridge configurations. The main disadvantage of the forward topology is its unidirectional core utilization and rectifier configuration, which leads to higher current ripples and bulky core size. However, as mentioned, forward topology is still widely utilized in industry because of its simplicity, especially in lower power levels.

Forward topology is obtained by adding an isolation transformer in the basic buck DC-DC converter. The steady-state voltage across any transformer or inductor must be

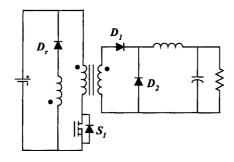

zero, otherwise the core will saturate. In the push-pull, half-bridge and full-bridge systems, this volt-second balance naturally occurs because of the symmetry of the alternating positive and negative waveforms applied to the windings. In a single ended forward converter, this volt-second balance doesn't happen naturally. Specific provision must be made to reset the core by allowing the voltage across the windings to back-swing during the switch "off" time so that the reverse volt-seconds equal and cancel the volt-seconds applied during the "on" time. With a variety of magnetics reset provisions [A21-25], there are many derivative forward converters as shown in Fig 1.9.

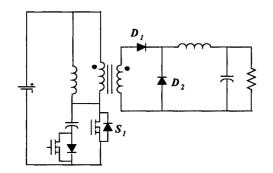

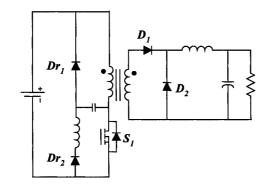

In Fig. 1.9(a), an additional winding and a diode Dr in series are added to reset the transformer core by recycling the transformer magnetizing energy. Diode  $D_1$  is used to block the reverse voltage when the transformer back swings. If the turns ratio between the primary wining and reset winding is 1:1, the forward converter must operate at a duty cycle below 50 percent to avoid transformer saturation. In this case, the primary switch withstands twice the input voltage. In Fig. 1.9(b), a passive RCD voltage clamp snubber circuit is applied to reset the transformer, where all magnetizing energy is transferred in the snubber capacitor and dissipated in the snubber resistor. Obviously, a RCD clamp circuit has lower efficiency than a reset-winding forward converter. However, the transformer design is much easier because the third winding and corresponding coupling requirement are eliminated.

Replacing the RCD snubber with an active clamp snubber circuit, an active-clamp forward converter is formed as shown in Fig. 1.9(c) [A26, A35]. It should be noted that a grounded P-channel MOSFET is used as an active switch to simplify the driving circuitry. In the active-clamp forward, the auxiliary switch can recycle magnetizing energy back to

input voltage bus. Most importantly, main switch can achieve zero-voltage-switching by utilizing magnetizing and leakage inductance energy. Therefore, the topology can be used in higher switching frequency than conventional forward topologies. Fig. 1.9(d) shows a derivative active-clamp forward converter: flyback-forward converter [A13], where the energy transfer becomes bi-directional, and transformer utilization is improved. It should be noted that a DC current bias exists in the magnetizing inductance in this topology, thus the transformer should be carefully designed.

As discussed above, in active-clamp forward topologies some kinds of lossless snubbers are used to reset and recycle magnetizing energy. The only disadvantage is that an additional switch complicates the power stage and driving circuitry. Fig. 1.9(e) shows a lossless passive LCD snubber forward converter, where the magnetizing energy is transferred into the capacitor when the switch is off; when the switch is on, the capacitor energy is transferred into the snubber inductor. Later on, when the switch is off, the energy is recycled back to the input voltage source through the diode  $D_{rl}$ . Theoretically, the snubber is lossless and the converter may achieve high efficiency.

In the passive and active clamp snubber circuitry discussed above, main switch voltage stress exceeds input voltage. Higher voltage stress means higher on-resistance and conduction loss. Fig. 1.9(f) shows a two-switch forward converter, where the transformer core is reset by clamping the transformer primary winding to the input voltage bus using two diodes. Since the voltage across two main switches is less than the input voltage, when compared with active-clamp converters, this two-switch forward topology is more reliable [A11].

17

$\begin{bmatrix} D_1 \\ D_2 \\ S_1 \\ S_1 \end{bmatrix}$

(a) Forward topology with a reset winding

(b) RCD clamp forward topology

(c) Active-clamp forward topology

(d) Flyback-forward DC-DC topology

(e) LCD clamp forward topology

(f) Two-switch forward converter

In the topologies of forward converters previously discussed, the converters operate at asymmetric conditions; the energy delivery in the transformer is unidirectional. In other words, voltage and current stresses are unevenly distributed between the main switch and the active-clamp switch, which results in higher stress on switches and rectifiers compared to symmetric half-bridge and full-bridge converters. The voltages across the switches are higher than the input DC voltage, which increase the on-state resistance of switches.

Unlike flyback and forward topologies, push-pull, symmetric half-bridge and fullbridge DC-DC topologies [A15, A27, A33] have symmetric architectures on both the primary side and the secondary side, and therefore they are found in higher power level applications. For low voltage and high current applications, both center-tapped and current-doubler rectifiers are widely employed in the secondary side.

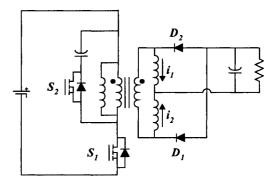

Push-pull topology is shown in Fig. 1.10. Push-pull topology almost has the same complexity as the half-bridge topology. However, in the half-bridge topology, capacitor(s) are needed in addition to the two main switches, while in the push-pull topology, center-tapped transformer winding is needed. Push-pull topology is suitable for low input voltage, and it tends to exhibit low primary-side conduction losses, since at any given instant only one switch is connected in series with the DC source. The push-pull configuration is prone to transformer saturation problems, since it cannot be guaranteed that the forward voltage drops and conduction time of two switches are exactly equal. For wide input voltage applications, push-pull topology has to operate at hard switching, and the ringing related to leakage inductance is a problem. In addition, higher voltage-rating

MOSFETs have to be selected for switches, because the theoretical minimum drain-tosource voltages seen by primary MOSFETs are twice the DC input voltage.

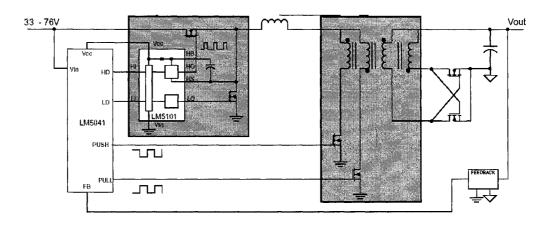

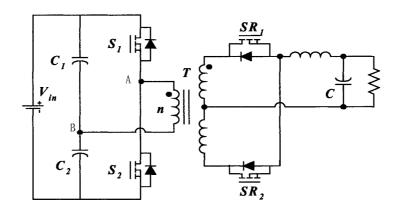

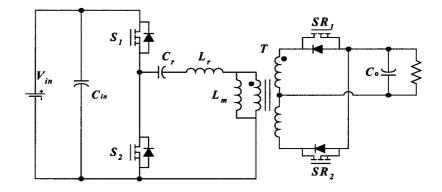

The half-bridge converter is also a push-pull version of the buck regulator. As shown in Fig.1.11, there are two configurations with a current-doubler rectifier. In fact, the center-tapped rectifier also can be applied to the transformer secondary winding. The key advantage of the half-bridge topology against the push-pull center-tap configuration is that the switch voltage ratings are cut in half (although the current is doubled). Moreover, the voltage applied to the transformer primary winding is cut in half, and less transformer primary turns are needed to step-down to the same output voltage level. For low output voltage applications, this is a desirable advantage since transformer secondary winding is single turn. In addition, current doubler rectification is good for stepping voltage down because the duty cycle is always less than 0.5.

Fig. 1.10 Push-pull DC-DC converter

There are two conventional control schemes for the half-bridge converter, which are symmetric control and asymmetric (complimentary) control. The main drawback of the conventional symmetric control is that both primary switches in the converter operate at hard switching condition. Moreover, during the off-time period of two switches, the oscillation between the transformer leakage inductance and junction capacitance of the switches results in energy dissipation and EMI emissions due to the MOSFETs body diodes reverse recovery [A44~A46]. To suppress the ringing, resistive snubbers are usually added. As a result, energy in the transformer leakage inductance is significantly dissipated in snubbers. Therefore, the symmetric-controlled half bridge is not a good candidate for high-switching frequency power conversion [A45].

The asymmetric (complementary) control was proposed to soften switching behavior of the half-bridge switches [A47, A48]. Two driving signals are complementarily generated and are applied to high-side and low-side switches. Thus, two switches may turn on at ZVS conditions owing to the fact that the transformer primary current charges and discharges the junction capacitance. However, asymmetric stress distribution on the corresponding components may occur due to the asymmetric duty cycle distribution for the primary two switches [A49]. In other words, current stresses in two primary switches are not identical; voltage and current stresses on secondary rectifiers are not equal. As a result, diodes or synchronous rectifiers with higher withstanding voltage are needed at the penalty of degrading the performance and efficiency of the rectifier stage [A45, A46, A49]. Furthermore, the DC gain ratio of the converter is nonlinear, thus higher duty cycle variation is needed for the same input voltage variation in comparison with the symmetric control scheme, which makes the

converter operate further beyond optimum operating point at high input voltage [A49]. Therefore, the complementary (asymmetric) PWM control is more suitable for applications where input voltage is fixed. As a solution to reduce the duty cycle variation for wide input voltage range, an asymmetric transformer turns ratio — together with integrated-magnetic structure — is proposed in [A49], such that rectifiers with lower withstanding voltage may be used to improve the performance. However, the power delivery for the transformer and current stresses in the switches and rectifiers is still uneven [A49].

Fig. 1.11 Half-bridge DC-DC converters

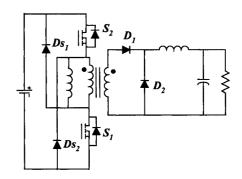

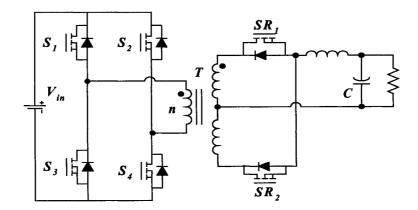

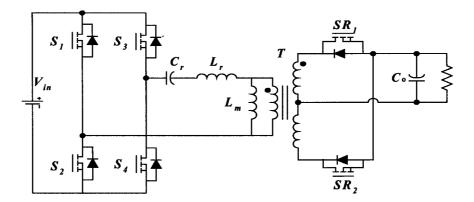

Full-bridge topology is a good candidate for higher power levels, because the current stresses are evenly distributed between four switches, and the transformer core and rectifiers are bi-directional and well utilized [A15, A33, A50]. A full-bridge converter is shown in Fig. 1.12. The voltage stress applied to four main switches is equal to input voltage, while the current stress through switches is half the current in a half-

bridge converter for the same output power level and same input voltage. Therefore, the full bridge has the voltage stress of half bridge and the current stress of the push-pull converter.

Phase-shifted full bridge [A15, A33, A50] is one of the most attractive zerovoltage-switching techniques since it allows all switches to operate at Zero-Voltage-Switching (ZVS) by utilizing transformer leakage inductance and junction capacitance of MOSFETs without adding an auxiliary switch. Actually, in a phase-shifted full-bridge converter, the leakage inductance energy is trapped by two up-switches or down-switches to achieve ZVS for lagging leg switches. Basically, four primary switches can achieve ZVS. At light load, the ZVS switching is always lost. That is not a big issue because the soft switching is not dispensable at a light load. It should be noted that when a full-bridge converter operates at a wide range of input voltage at high line input, the effective duty cycle becomes so small that the recycling interval increases leading to more conduction loss.

Fig. 1.12 Full-bridge DC-DC converters

23

In all topologies discussed above, the complexity of the full bridge is highest due to its large switch count and complicated control and driving [A44~A45]. Half-bridge topology is an attractive topology for middle power levels owing to its simplicity compared with the full-bridge topology. Although the full-bridge topology offers both the current stress of the push-pull topology and the low voltage stress of the half-bridge topology, the half-bridge topology is a preferred choice because of its lower component count and overall simplicity. However, in [A42], phase-shift controlled full-bridge topology is recognized as the best choice at high frequencies where soft switching of the primary switches is required to maintain efficiency.

### 1.4 Dissertation Outline

This dissertation consists of five chapters. They are organized as follows.

Chapter 1 is the background review of the existing on-board DC-DC converter technologies and the technical challenges for low-voltage high-current DC-DC converter designs. Size is the main concern in the design of on-board converters for distributed power supplies. One idea to reduce the size of a DC-DC converter is to increase switching frequency, because the value of reactive components is lower. Transformers, inductors and capacitors become smaller as switching frequency increases if their size is dependent on their reactive value. However, switching loss increases with switching frequency. When the switching frequency is increased to a certain level, the converter size depends on the power losses. These losses are the main constraint in the design of small OBCs working at high switching frequencies. The main trend in the DC-DC converter design in the last years was aimed at very high switching frequencies and at modifying the power circuits to keep switching losses under control. To reduce the switching power loss, soft switching is a desirable technique to reduce power loss and increase converter power density.

For non-isolated OBC converters, multiphase converters interleave the inductor currents in individual channels and therefore greatly reduce the total current ripples flowing into the output capacitance. With the current ripple reduction, the output voltage ripples are greatly reduced, which enables the use of very small inductance to improve response. Therefore, small output capacitance can be used to meet the transient requirements.

For low-voltage and high-current isolated DC-DC converters, secondary power loss dominates overall power losses. In the dissertation, a variety of rectification architectures are reviewed for low-voltage and high-current applications. Current-doubler and centertapped rectifiers are recognized as the suitable topologies for low-voltage and highcurrent rectifiers. In addition, state-of-the-art topologies such as flyback, forward, halfbridge, full-bridge and push pull — associated with as their derivative topologies — are reviewed.

Soft-switching techniques are the prevailing solution to reduce switching losses, which have been intensively investigated in the last two decades. In Chapter 2, a Duty-Cycle-Shift (DCS) concept is proposed for half-bridge DC-DC converters to reduce switching loss. The concept of this new control scheme is shifting one of the two symmetric PWM driving signals close to the other, such that ZVS may be achieved for the lagging switch due to the shortened resonant interval.

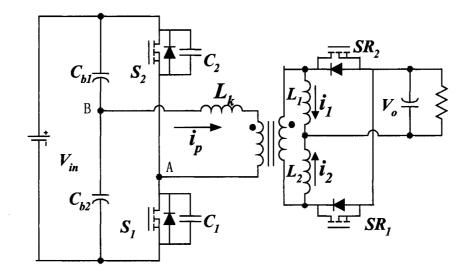

By applying a basic DCS concept to a conventional half-bridge DC-DC converter, Zero-Voltage-Switching is achieved for one of the two primary switches. To achieve ZVS for the other switch, a ZVS half-bridge topology is proposed in the dissertation. By adding an active branch to the conventional half-bridge topology, the leakage inductance energy is trapped during the freewheeling time, and the energy is released to achieve ZVS for the other switch. In addition, all auxiliary switches can achieve soft switching. With proposed techniques, converter efficiency is improved, and it allows the converter to operate at a higher switching frequency.

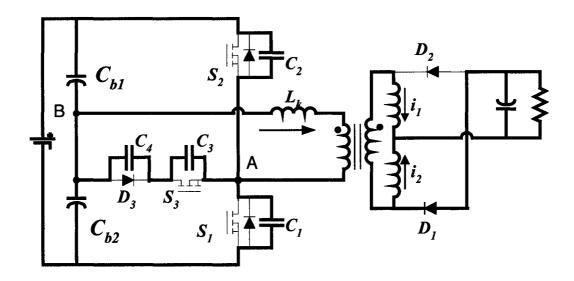

In the proposed ZVS half-bridge topology, the auxiliary switch is floating to the ground. A modified ZVS half-bridge topology is proposed to ground the auxiliary switch, and thus a simple drive circuitry can be applied to the auxiliary switch. For low voltage applications, to reduce the freewheeling conduction in the diode of the auxiliary branch, a synchronous rectifier is presented with simplified driving circuitry.

All topologies based on a DCS concept are verified by experimental results. The DCS concept is successfully demonstrated in an industry demo prototype.

In Chapter 3, two snubber topologies are proposed. For conventional half-bridge DC-DC converters, the leakage inductance results in ringing issues during the off-time interval. To dampen the ringing, dissipative snubbers such as RC and RCD snubbers are widely utilized. In the dissertation, an active-clamp snubber topology is presented in half-bridge DC-DC converters to recycle the leakage inductance energy and attenuate the ringing. Since dissipative snubbers are removed, a converter can operate more efficiently.

For low-output-voltage applications, SR losses account for a high portion of overall conversion losses. Body-diode reverse-recovery-related loss in SRs increases with the

switching frequency. To reduce this reverse-recovery loss, two passive snubber circuits are proposed for SR rectifiers. The proposed snubbers attenuate reverse recovery ringing, and higher efficiencies are achieved.

Chapter 4 mainly focuses on the modeling of the half-bridge DC-DC converter. A unified DC model is derived based on the state-space average equation, which is suited for both symmetric and asymmetric half-bridge DC-DC converters.

A half-bridge DC-DC converter with current-doubler rectifier is actually a twochannel isolated buck converter. Because peak-current-mode control cannot be directly applied to half-bridge DC-DC converter, the current sharing between two inductors is an issue. By solving the DC model, the DC current solution is obtained. The solution shows that the DC current sharing in the two inductors mainly depends on duty cycles and inductor DCRs in the converter, and SR on-resistances have no impact on the current sharing. The analysis also shows that a DC magnetizing current exists in the transformer of the asymmetric half-bridge DC-DC converter, and that the inductor currents are unbalanced if two inductor DCR values are asymmetric.

To solve the DC imbalance issue of the inductor currents, a simple modification is applied to the half-bridge DC-DC converter. Simulation and an established DC model verify that the current sharing between the two inductors can be achieved even under asymmetric DCR values, and the DC bias of transformer magnetizing current is eliminated.

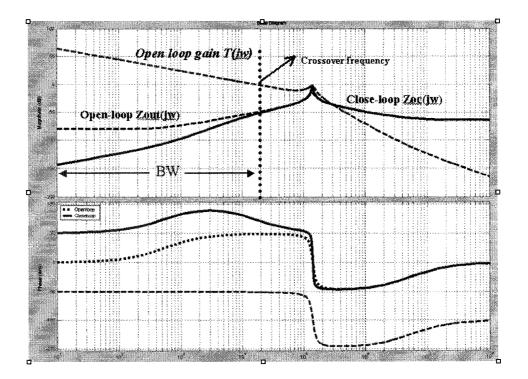

The AC model is established based on a closed-loop controlled system. For a current change disturbance, the closed-loop output impedance determines output voltage

overshoots and undershoots. Closed-loop output impedance is analyzed based on the AC model, and some important conclusions are given, which are the base of Chapter 5.

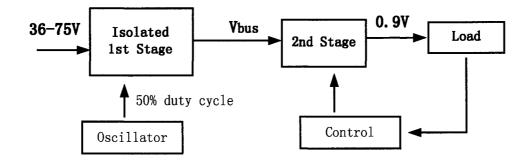

For one-stage approaches of DC-DC conversion, a converter has functions of regulation and isolation. In the two-stage approaches, regulation and isolation are separated from the other. In Chapter 5, two-stage Voltage Regulator (VR) architecture and Intermediate Bus Architecture (IBA) for datacom applications are reviewed.

Full-Duty-Cycle (FDC) two-stage architecture is proposed to achieve desirable open-loop output impedance. Since the filter inductance can be minimized in the FDC converter, the open-loop output impedance is becoming first-order, and it may compete with closed-loop controlled converters. FDC converters are potential candidate topologies for two-stage approaches.

High-switching frequency reduces magnetic and passive filter size. In Chapter 5, some resonant converters are investigated and recognized as potential topologies for twostage approaches. SRC and LLC resonant converters can reduce the body diode crossover conduction loss of synchronous rectifiers. PRC and LCC converters can soften the reverse recovery of body diodes in SR rectifiers.

The conclusion is given in Chapter 6.

# 2. HALF-BRIDGE DC-DC CONVERTERS BASED ON THE DUTY-CYCLE-SHIFT (DCS) CONCEPT

## 2.1 Introduction

To further increase the processing speed and decrease the power consumption in VLSI (Very Large Scale Integration) Integrated Circuits, the operating voltages of ICs keep decreasing. Lower power consumption implies higher functional integration, better thermal management and more reliability. However, increased processing speed and transistor integration density keeps increasing the power level instead of decreasing it with reduced operating voltage. These factors pose big challenges to power management. One of the challenges is the low operating voltage. Lower operating voltage means lower conversion efficiency for DC-DC converters due to semiconductor voltage drop. The second challenge is that the estate budgeted for power management doesn't increase with the raised power level of power converters. Therefore, power density of power supplies is strongly demanded. To achieve this goal, reduced sizes of passive components and high efficiency power conversion are the solutions. To reduce the volume of passive components, such as magnetics cores and capacitors, switching frequency has to be pushed higher. However, switching-related losses have significant impact on conversion efficiency.

Soft-switching techniques are the prevailing solution to reduce switching losses, which has been intensely investigated in the last two decades. Some of the invented techniques in recent years, such as active-clamp forward converter and full-bridge phase-shifted converter, have been widely applied to isolated DC-DC conversion products. Several techniques for high-frequency DC-DC conversion have been proposed to reduce

component stresses and switching losses while achieving high-power density and improved performance [B1-B11]. Among them, the phase-shifted zero-voltage-switching (ZVS) full bridge [B1~B3] is one of the most attractive techniques, since it allows all switches to operate at ZVS by utilizing transformer leakage inductance and MOSFETs' junction capacitance without adding an auxiliary switch. However, the complexity of the full bridge technique is among the highest of the conventional topologies due to its large switch count and complicated control and driving. Active-clamp forward topology [B4~B6] is another typical way to successfully realize ZVS for the switches by utilizing the leakage inductance, magnetizing inductance and junction capacitance. However, the topology of the converter is asymmetric and the energy delivery is unidirectional. In other words, voltage and current stresses are unevenly distributed, resulting in the individual switch and rectifier stresses being higher compared with symmetric half-bridge and fullbridge converters. This disadvantage limits the power level of the active-clamp forward topology applications. In addition, DC bias of magnetizing current may exist in the transformer [B5].

The half-bridge (HB) DC-DC converter is an attractive topology for middle power level applications, attributing to its simplicity. There are two conventional control schemes for the HB DC-DC converter, namely symmetric control and asymmetric (complimentary) control. The main drawback of the conventional symmetric control is that both primary switches in the converter operate at hard switching condition. Moreover, during the off-time period of two switches, the oscillation between the transformer leakage inductance and junction capacitance of the switches results in energy dissipation and EMI emissions due to the reverse recovery of MOSFETs body diodes. To suppress the ringing, resistive snubbers are usually added. As a result, energy in the transformer leakage inductance is significantly dissipated in snubbers. Therefore, the symmetric-control half bridge is not a good candidate for high-switching frequency power conversion.

The asymmetric (complementary) control was proposed to achieve ZVS operation for HB switches [B7~B11]. Two drive signals are complementarily generated and applied to high-side and low-side switches. Thus, the two HB switches may be turned on at ZVS conditions, attributing to the fact that the transformer primary current charges and discharges the junction capacitance. However, asymmetric stress distribution on the corresponding components may occur due to the asymmetric duty cycle distribution for the two primary switches. In other words, current stresses in the two primary switches are not identical, and voltage and current stresses on secondary rectifiers are not equal. As a result, diodes or synchronous rectifiers with higher voltage rating are needed at the penalty of degrading the performance and efficiency of the rectifier stage [B10]. Furthermore, the DC gain ratio of the converter is nonlinear, thus higher duty cycle variation is needed for the same input voltage variation in comparison with symmetric PWM control scheme. This makes the converter operate further beyond the optimum operating point at high input voltage [B10]. Therefore, the complementary (asymmetric) PWM control is more suitable for applications where the input voltage is fixed. As a solution to reduce the duty cycle variation for wide input voltage range, an asymmetric transformer turns ratio together with integrated-magnetic structure, was proposed in [B10], such that rectifiers with lower withstanding voltage may be used to improve the performance. However, the power delivery of the transformer and current stresses in the switches and rectifiers are still uneven [B10].

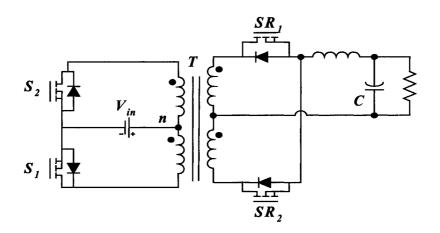

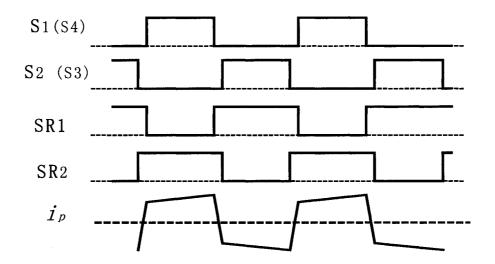

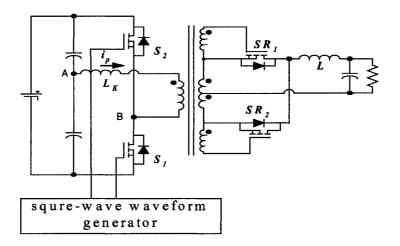

In this chapter, a new control concept, known as "Duty-Cycle-Shift PWM" (DCS PWM) control, is proposed and applied to the conventional HB DC-DC converters to achieve ZVS for one of the two switches without adding extra components or asymmetric penalties of the complementary control. The concept of this new control scheme shifts one of the two symmetric PWM driving signals close to the other, such that ZVS may be achieved for the lagging switch due to the shortened resonant interval. Unlike the asymmetric control, the width of the duty cycle for the two switches is kept equal, such that all corresponding components work at the conditions with even stresses, as is the case with the symmetric control scheme. Moreover, based on the DCS PWM control, two half-bridge DC-DC converter topologies are proposed to achieve ZVS for the other switch and auxiliary switch by adding an auxiliary switch and diode in the conventional half bridge. ZVS for the other switch is achieved by utilizing the energy trapped in the leakage inductance. In addition, the proposed topology with DCS PWM control eliminates the ringing resulting from the oscillation between the transformer leakage inductance and the switches junction capacitance during the off-time period. Therefore, the proposed converter has a potential to operte at higher efficiencies and switching frequencies.

#### 2.2 Duty-Cycle-Shift Concept

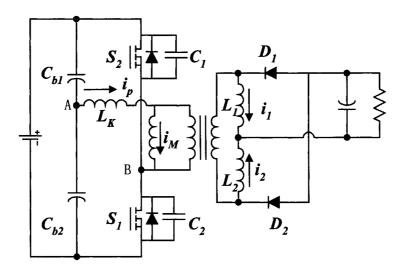

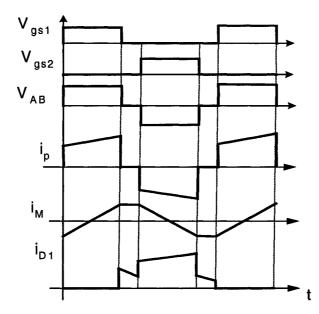

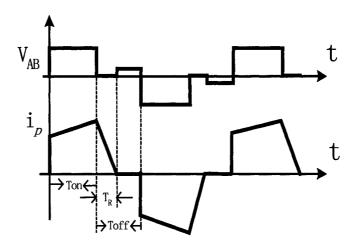

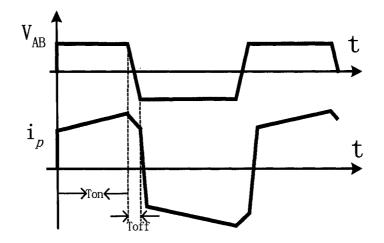

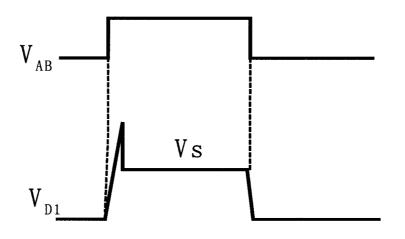

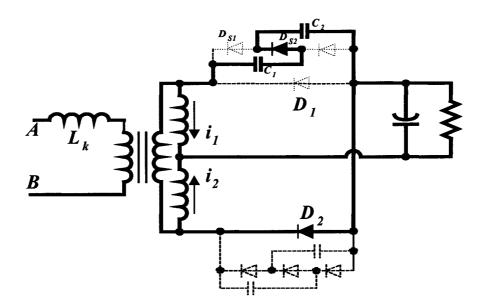

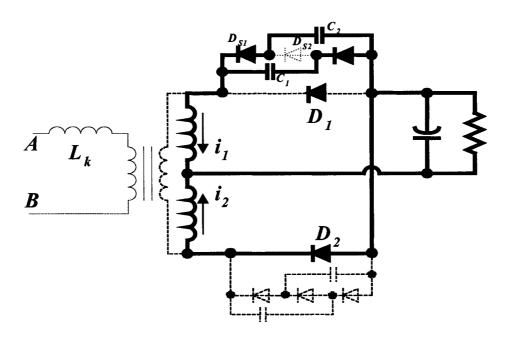

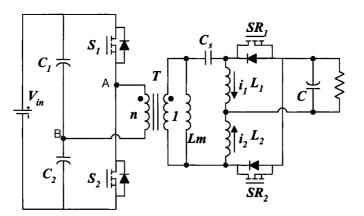

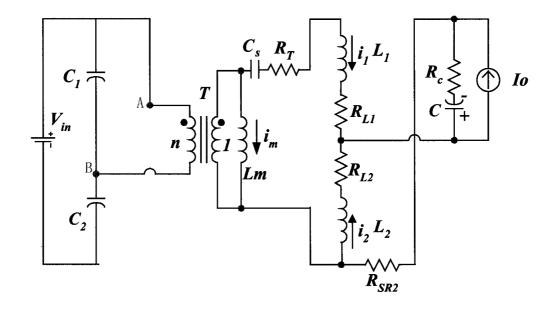

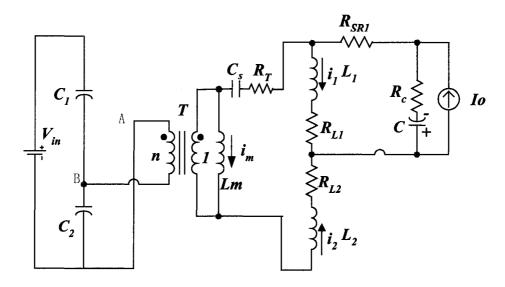

Fig. 2.1 shows the half-bridge DC-DC converter with current doubler rectifier. The ideal waveforms for the symmetric PWM control is sketched in Fig. 2.2 (a), where  $L_{k}$  is

the leakage inductance, ip and  $i_M$  are the transformer primary-side input and magnetizing currents, respectively and  $i_{D1}$  is the forward current through rectifier diode  $D_1$ . Besides the hard switching, conventional symmetric PWM control has transformer-leakage-inductance related disadvantages. During the off-time period when both switches are off, the energy stored in the transformer leakage inductance may be recycled to primary DC bus through the body diodes of MOSFETs. However, because of the reverse recovery current of the body diodes, the oscillation between the transformer leakage inductance and the MOSFETs junction capacitance is significant on the primary side. To suppress the ringing, snubber circuits usually are necessary to add, but losses dissipated in the snubber become dramatically large, especially at high input current and high switching frequencies.

Fig. 2.1 Half-bridge DC-DC converter with current doubler rectifier

### 2.2.1 Proposed DCS PWM Control Scheme

Fig. 2.2 (b) shows the key waveforms of the half-bridge converter with the proposed DCS PWM control. Based on symmetric PWM control,  $S_2$  driving signal  $V_{gs2}$  is shifted

left such that the  $V_{gs2}$  rising edge is close to the falling edge of  $S_1$  driving signal  $V_{gs1}$ . When  $S_1$  is turned off, the transformer primary current charges the junction capacitance of switch  $S_1$  and discharges the junction capacitance of switch  $S_2$ . After the voltage across drain-to-source of  $S_2$  drops to zero, the body diode of  $S_2$  conducts to carry the current. During the body diode conduction period,  $S_2$  may be turned on at zero-voltage switching. No ringing occurs during the transition period.

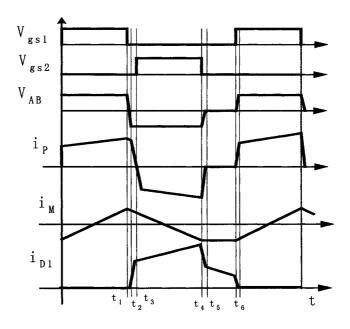

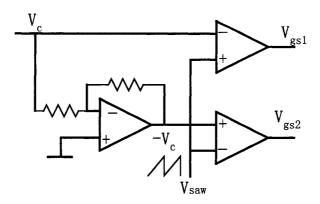

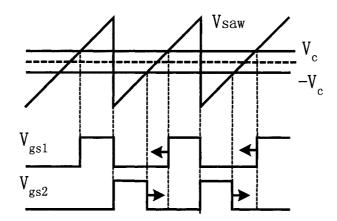

Fig. 2.3 shows a possible modulation approach for realization of DCS PWM control scheme. Where, Vsaw is the SAW carrier waveform for modulation and Vc and –Vc are control voltages derived from the front voltage or current controller. By modulating Vc and –Vc, driving signals for  $S_1$  and  $S_2$  can be generated, respectively. Because the falling time of the SAW waveform is short, the falling edge of  $S_1$  is always close to the rising edge of  $S_2$ , which provide a possibility of ZVS for  $S_2$ .

This modulation method differs from the conventional symmetric PWM method in that the direction of variation of the two duty cycles is opposite as shown in Fig. 2.3(b) by the arrows on the driving signals' waveforms. In other words, since Vc and –Vc are symmetrically centered around zero, the duty cycle of  $S_1$  is regulated by moving its rising edge left and right, while the duty cycle of  $S_2$  is regulated by moving its falling edge right and left, keeping  $S_1$  and  $S_2$  with the same duty cycle.

Fig. 2.2 (a) Waveforms of conventional HB DC-DC converters

Fig. 2.2 (b) Waveforms of DCS HB DC-DC converters

Fig. 2.3 (a) Modulation circuits

Fig. 2.3 (b) Key waveforms

Fig. 2.3 A DCS PWM modulation scheme

# 2.2.2 Principle of Operation