Front-end converter design and system integration techniques in distributed power systems

Luo, Shi

ProQuest Dissertations and Theses; 2001; ProQuest Dissertations & Theses (PQDT)

pg. n/a

### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 806-521-0600

## **NOTE TO USERS**

Page(s) not included in the original manuscript and are unavailable from the author or university. The manuscript was microfilmed as received.

248

This reproduction is the best copy available.

**UMI**°

# FRONT-END CONVERTER DESIGN AND SYSTEM INTEGRATION TECHNIQUES IN DISTRIBUTED POWER SYSTEMS

by

SHIGUO LUO

B.E. Southwest Institute of Technology, 1985

Ph. D. Chongqing University, 1993

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2001

Major Professor: Dr. Issa Batarseh

UMI Number: 3013894

### UMI Microform 3013894

Copyright 2001 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346 © 2001 Shiguo Luo

#### **Disclaimer**

Potential users of the methods and schematics described in this dissertation are advised that such use could potentially violate patent rights of one or more third parties. Author disclaims any liability which may arise from applying the methods and schematics that users should consult their own legal advisors.

### **ABSTRACT**

Power conversion system design issues are becoming increasingly important in state-of-the-art electronic systems, especially in computing and information system applications. These issues include not only improving power conversion efficiency, but also increased concerns regarding the cost and complexity of the power converters and systems utilized to satisfy the host system's total performance requirements. Further, system integration techniques, which can be used in "building blocks" to implement a wide range of power electronic circuits and systems, will be taking a critical role to innovate conventional designs and also bring profound effects into practical applications.

This dissertation explores front-end converter design and system integration techniques in distributed power systems (DPS), with the objective of achieving improvements in converter topology, system performance, system configuration and cost-effectiveness over conventional approaches. Key issues of single-stage (S<sup>2</sup>) power-factor-correction (PFC) converters are addressed and the solutions to these issues are investigated. An optimization design procedure of a family of S<sup>2</sup> converters, which is based on the averaging circuit model and MathCAD tool, is developed and verified by both simulation and experiment. A new PFC cell is presented with the direct-power-transfer (DPT) concept, and a new family of S<sup>2</sup> converters is derived and experimentally verified, which has excellent characteristics that help push S<sup>2</sup> converters into medium power applications. A comparison study of high power down converters is conducted, and in particular, experimental comparison of high power level for secondary-side

topologies is completed in this dissertation, which demonstrates that the current doubler rectification topology is a viable choice for high-efficiency converters. The dissertation also investigates system level techniques such as interleaving, paralleling and configuration simplification. New interleaving method for high power converters is presented and simulated results demonstrate its potentials in decreasing filter size and increasing power density. New paralleling methods for power converters have been obtained based on the comprehensive classification and evaluation of paralleling approaches of power supply modules. The dissertation also describes the operation principle, design considerations, and experimental results of an AC-DPS with multiple PWM-wave buses. Finally, a redundant AC-DPS with trapezoidal waveform bus is proposed.

To my grandparents and parents

#### ACKNOWLEDGMENTS

My four year stay in the U.S. has created an important literary piece of not only my research life but also my ideological reformation shaped through experiencing unnumbered horrific nights, but fantastic years, also through hardships and triumphs of study and research.

I sincerely thank my advisor, Dr. Issa Batarseh, for giving me the opportunity and confidence to work towards my Ph.D. degree at UCF, and providing me with a pleasant and productive research environment. In particular, his warm personality and friendship made my experience at this university one of the most cherished experiences of my life. Although my graduate study at UCF had experienced the hardest years and unexpected developments, his strong encouragement and wholehearted support have become my original power and pushed me to achieve my dream. Without his great help and supervision, this dissertation would never be born.

I wish to express my sincere appreciation to Dr. Fred C. Lee, who gave me the opportunity to enter the states, working as a visiting professor in Center of Power Electronics Systems (CPES, former VPEC) at Virginia Tech., from middle 1997 to end 1998, with which I had chance to know so many power electronics folks. I also thank the following CPES peers, Profs. Dan Y. Chen and Alex Huang, Drs. Hengchun Mao, Xuening Li, Xiaogang Feng, Zhihong Ye, Wei Chen, Lizhi Zhu, Liang Wang, Xunwei Zhou, and Mr. Xinsheng Zhou, Bo Zhang, Mr. Heping Dai, Dayu Qu, Yuhui Chen, Yongxuan Hu, Qun Zhao and Jianwen Shao for their constant care and friendship.

I also wish to take this opportunity to thank my former advisor, Prof. Zhencheng Hou, for bringing me into the wonderful field of power electronics.

I would like to express my gratitude to my research buddies Drs. Huai Wei Guangyong Zhu, and Chris Iannello, for sharing with me for many of valuable technical discussions, and unforgettable time we spent together.

I would also like to express my particular appreciation to Mr. Weihong Qiu, Mr. Lei Hua and Dr. Peter Kernetzky, who provided the help needed in implementing experimental verifications. Special thanks are also expanded to my close study fellow Dr. Wei Gu, as well as my old colleagues Drs. Zhixiang Liang and Jun Chen for beneficial technical arguments.

I gratefully thank FloridaPEC's faculty member, Dr. Thomas X. Wu, who gave me much encouragement toward my Ph. D. degree. To my other advisory committee members, Dr. Xin Li, Dr. Wasfy B Mikhael and Dr. Louis C. Chow, thanks for the patient, the passion, and their feedbacks.

Thanks are due to the many UCF staff who made the program and work possible, particularly for Ms. Mickey Gravois.

I am indebted to all my fellow students at UCF. Their friendship has made my stay in study & research program enjoyable. Especially, I thank FloridaPEC's members, Dr. Wenkai Wu, Jabber A. Abu Qahouq, Manasi Soundalgekar, Jia Luo, Yaomin Yang, Enrique Tenicela, Abdelhalim M. Alsharqawi, Khalid Rustom and Shailesh Anthony and Joy Mazumdar, for the valuable technical discussions.

Above all, I would like to express my deepest gratitude to my wife and son, Huaiying and Maozhe, who have been standing by me with their honest follow and also with their determined courage together sharing the life stress and struggling fruits.

This work was supported by NASA, NSF and the University of Central Florida.

### **TABLE OF CONTENTS**

| 1. INTRODUCTION                                       |                                |

|-------------------------------------------------------|--------------------------------|

| 1.1. Background and Motivations                       |                                |

| 1.2. Dissertation Outline and Major Results           | 8                              |

| 2. REVIEW OF DISTRIBUTED POWER SYSTEMS (DPS           | 5) 14                          |

| 2.1. Introduction                                     | 14                             |

| 2.2. Characteristics of Distributed Power             | 16                             |

| 2.3. Basic Distributed Structures                     | 19                             |

| 2.4. DC Distributed Power Systems                     | 23                             |

| 2.4.1. System Design Considerations                   | 24                             |

| 2.4.2. Investigation of Current Techniques            | 31                             |

| 2.4.3. Issues and Challenges                          | 38                             |

| 2.5. High Frequency (HF) AC-Distributed Power Systems | 40                             |

| 2.5.1. System Design Considerations                   | 41                             |

| 2.5.2. Investigation of Current Techniques            | 43                             |

| 2.5.3. Issues and Challenges                          | 46                             |

| 2.6. Summary                                          | 49                             |

| 3. KEY ISSUES AND SOLUTIONS FOR SINGLE-STAGE          | C (S <sup>2</sup> ) CONVERTERS |

|                                                       | 51                             |

| 3.1. Introduction                                     | 51                             |

| 3.2. Intermediate Bus Voltage Stress and Solutions    | 53                             |

| 3.2.1. Reason for High Bus Voltage Stress             | 53                             |

| 3.2.2. Schemes to Alleviate Bus Voltage               | 56                             |

| 3.2.3. Comparative Conclusions                        | 68                             |

| 3.3. Optimization Design of S <sup>2</sup> Converters | 69                             |

| 3.3.1. Operation Principle of Example Converter       | 69                             |

| 3.3.2. Circuit Equations and Averaging Model          | 72                             |

| 3.3.2.1 Circuit Equations                             | 72                             |

| 3.3.2.2 Averaging Model                               | 75                             |

| 3.3.3. Optimization Design Methodology                                      | 78         |

|-----------------------------------------------------------------------------|------------|

| 3.3.4. Design Example-A 150W S <sup>2</sup> Converter                       | 82         |

| 3.3.4.1 Power Stage Design                                                  | 82         |

| 3.3.4.2 Controller Design.                                                  | <b>8</b> 9 |

| 3.3.5. Simulated and Experimental Results                                   | 94         |

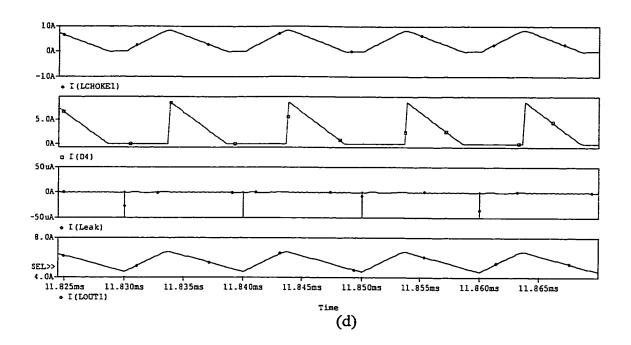

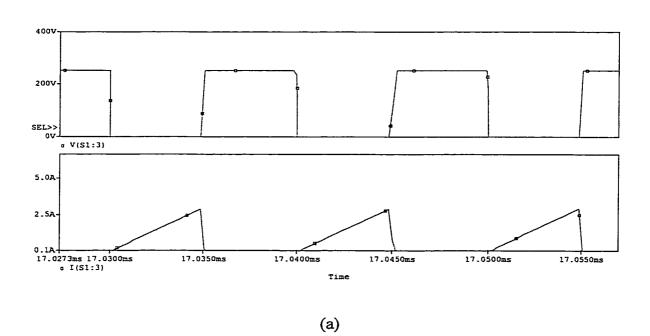

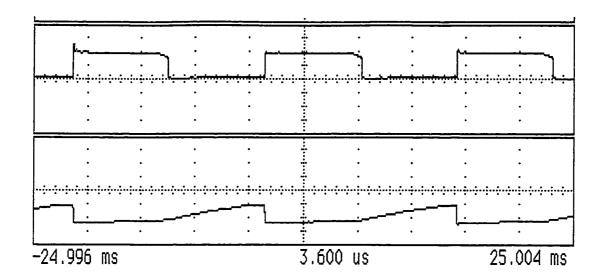

| 3.3.5.1 Simulated Results                                                   | 94         |

| 3.3.5.2 Experimental Results                                                | 98         |

| 3.4. Summary                                                                | 102        |

| 4. A FAMILY OF S <sup>2</sup> ISOLATED FRONT-END CONVERTERS                 | 104        |

| 4.1. Introduction                                                           | 104        |

| 4.2. Direct Power Transfer Concept for High Efficiency Converters           | 105        |

| 4.3. Development of Topologies                                              | 110        |

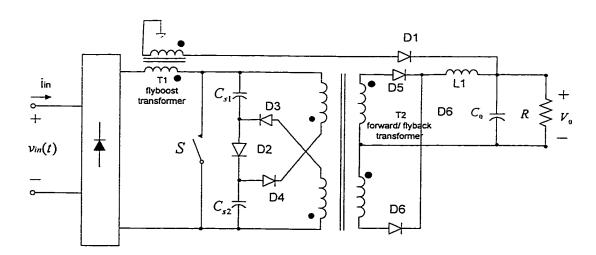

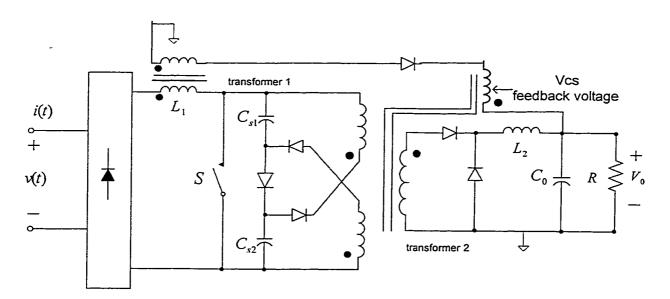

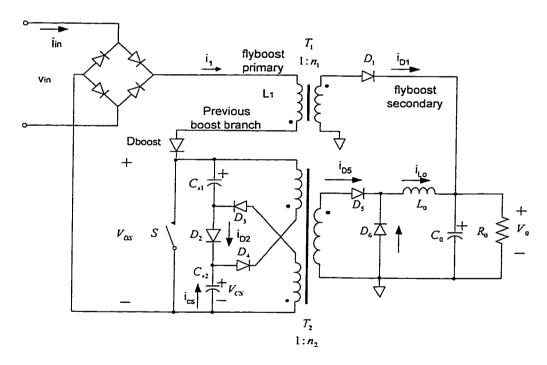

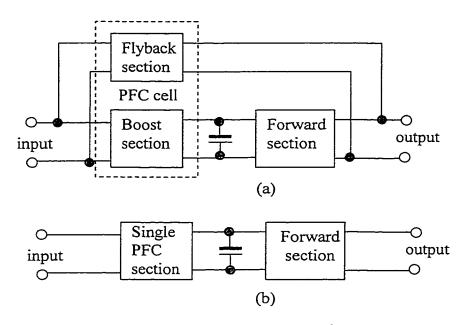

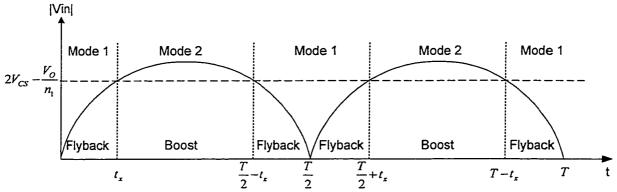

| 4.3.1. "Flyboost" PFC Cell                                                  | 110        |

| 4.3.2. A Family of S <sup>2</sup> Topologies Based on the Flyboost PFC Cell | 113        |

| 4.3.3. Extended Topologies                                                  | 118        |

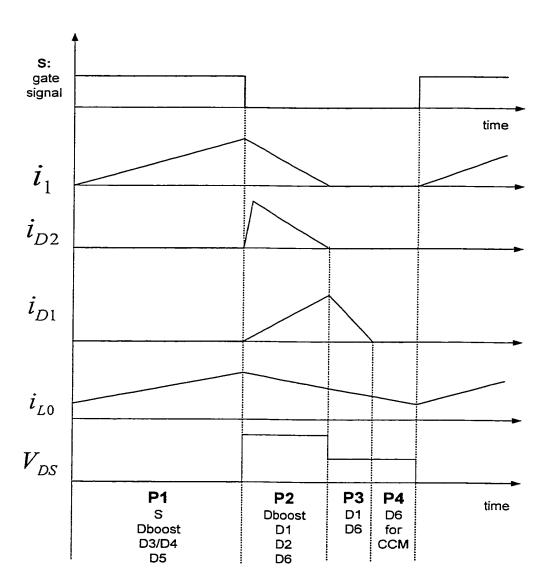

| 4.4. Example Circuit Operation and Basic Design Considerations              | 121        |

| 4.4.1. Circuit Operation                                                    | 121        |

| 4.4.2. Basic Design Considerations                                          | 126        |

| 4.5. Simulated and Experimental Results                                     | 130        |

| 4.5.1. Simulation Verification for Circuit Operation                        | 130        |

| 4.5.2. Verification for (DCM+CCM) Operation                                 | 133        |

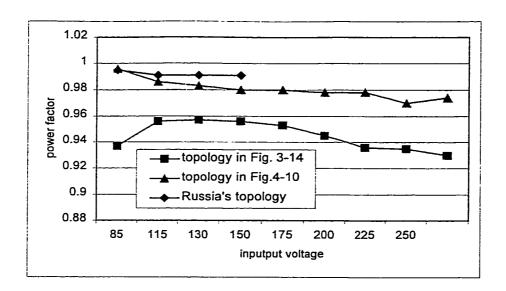

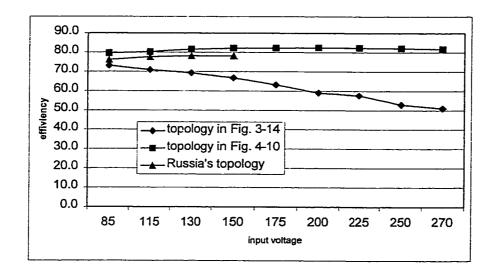

| 4.5.3. Verification and Comparison for DCM+DCM Operation                    | 137        |

| 4.6. Summary                                                                | 142        |

| 5. COMPARISON STUDY OF HIGH POWER DOWN CONVERTERS                           | 144        |

| 5.1. Introduction                                                           | 144        |

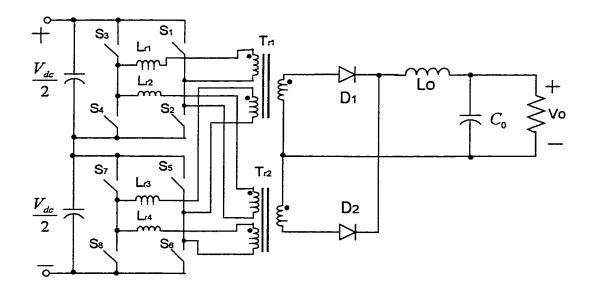

| 5.2. Comparison Analysis of Primary-Side Topologies                         | 146        |

| 5.2.1. Topologies under Medium DC Input Voltage                             | 146        |

| 5.2.2. Topologies under High DC Input Voltage                               | 148        |

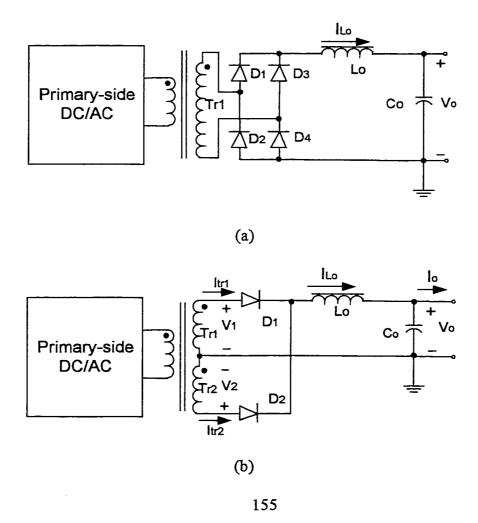

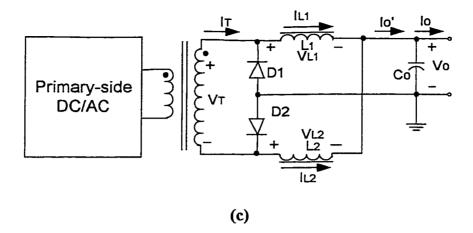

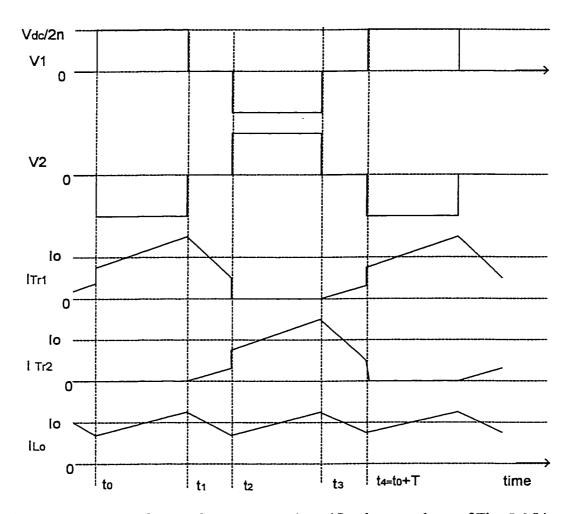

| 5.3. Comparison study of Secondary-Side Topologies                          | 154        |

| 5.3.1. Principle of Operation                                               | 156        |

| 5.3.2. Comparison Analysis                                                  | 159        |

| 5.3.3. Experimental Verifications                                           | 164        |

| 5 A Summary                                                                 | 160        |

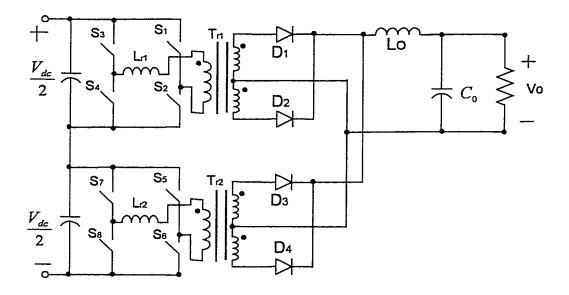

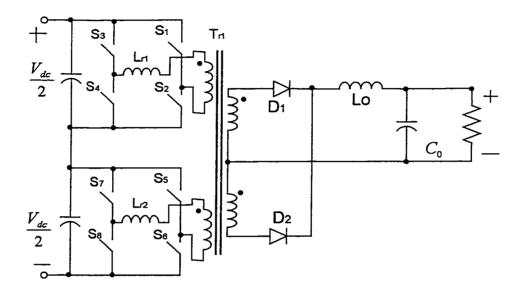

| 6. SYSTEM INTEGRATION TECHNIQUE — INTERLEAVING        | 171      |

|-------------------------------------------------------|----------|

| 6.1. Introduction                                     | 171      |

| 6.2. Conceptual Overview                              | 172      |

| 6.3. Limit of Conventional Interleaving Techniques    | 174      |

| 6.4. An Interleaving Method for High Power Topologies | 176      |

| 6.5. Comparison Analysis                              |          |

| 6.6. Simulated Results                                | 183      |

| 6.7. Summary                                          | 187      |

| 7. SYSTEM INTEGRATION TECHNIQUE — PARALLELING         | 189      |

| 7.1. Introduction                                     |          |

| 7.2. Conceptual Overview                              | 189      |

| 7.3. Classification of Paralleling Schemes            | 191      |

| 7.4. Assessment of Paralleling Schemes                |          |

| 7.4.1. Droop Schemes                                  | 193      |

| 7.4.2. Active Current-Sharing Schemes                 | 197      |

| 7.5. Simulation Examples of New Paralleling Methods   | 208      |

| 7.6. Summary                                          | 211      |

| 8. SYSTEM INTEGRATION TECHNIQUE — SIMPLIFYING BY H    | F AC BUS |

| •••••••••••••••••••••••••••••••••••••••               |          |

| 8.1. Introduction                                     | 213      |

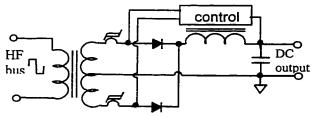

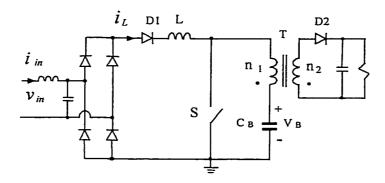

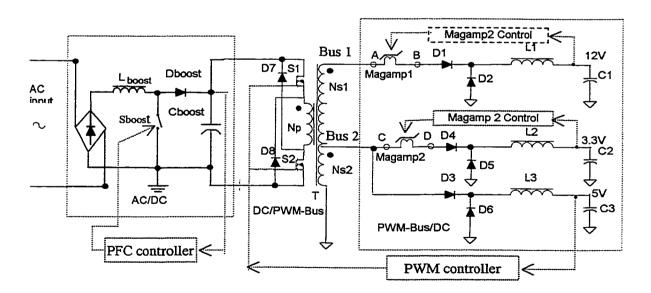

| 8.2. A HF AC-DPS with Multiple PWM-Buses              |          |

| 8.2.1. System Configuration                           | 214      |

| 8.2.2. Principle of Operation                         | 216      |

| 8.2.3. Basic Design Considerations                    | 220      |

| 8.2.4. Experimental Results                           | 224      |

| 8.3. A Redundant AC-DPS with Trapezoidal Waveform Bus | 227      |

| 8.4. Summary                                          | 230      |

| 9. CONCLUSIONS AND FUTURE WORK                        | 231      |

| 9.1. Conclusions.                                     | 231      |

| 9.2. Future Work                                      | 235      |

| DEPENDENCE                                            | 220      |

### LIST OF TABLES

| Table 2-1 Performance comparison of three PFC approaches                | 34  |

|-------------------------------------------------------------------------|-----|

| Table 3-1 Four operation periods                                        | 71  |

| Table 4-1 Conduction status of power components                         | 125 |

| Table 5-1 Comparison of center-tapped and current doubler rectifiers    | 163 |

| Table 6-1 Comparison of single power stage and interleaved power stages | 182 |

| Table 7-1 Combined active current-sharing schemes                       | 193 |

### LIST OF FIGURES

| Fig. 1-1.  | Power processing combination scheme using silver box and VRMs for               | •    |

|------------|---------------------------------------------------------------------------------|------|

|            | future generation of computers                                                  | 2    |

| Fig. 1-2.  | A typical architecture of DC distributed power system                           | 4    |

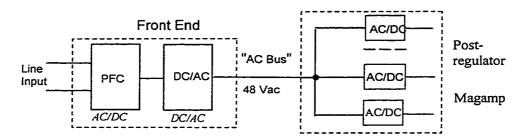

| Fig. 1-3.  | A typical architecture of AC distributed power system                           | 5    |

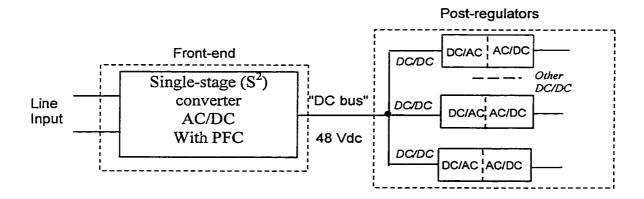

| Fig. 1-4.  | Simplified DC distributed power system                                          | 6    |

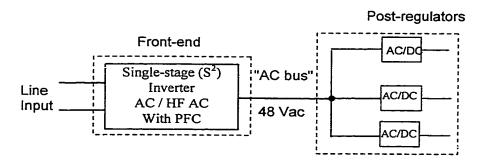

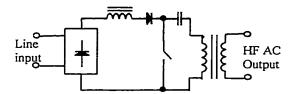

| Fig. 1-5.  | Simplified AC distributed power system                                          | 7    |

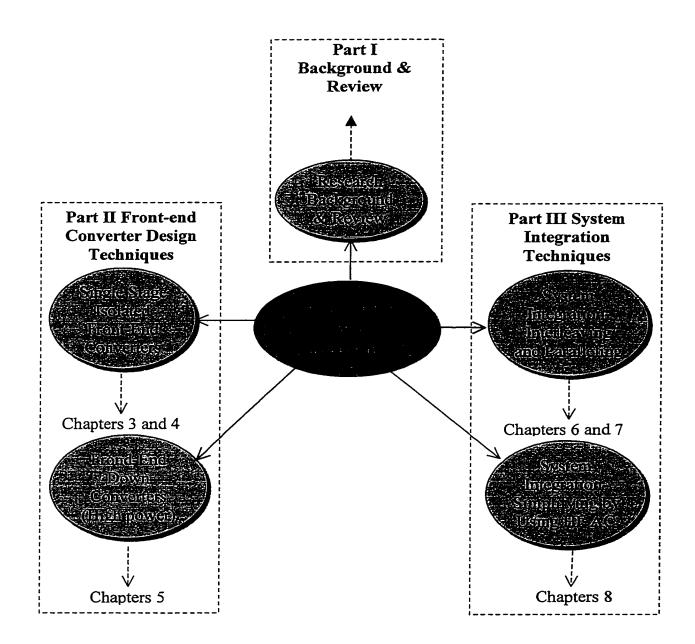

| Fig. 1-6.  | Framework description of dissertation coverage                                  | 9    |

| Fig. 2-1.  | Three types of "power supply" architectures                                     | 14   |

| Fig. 2-2.  | Basic distribution structures (a) paralleling, (b) cascading, (c) stacking, (d) |      |

|            | source splitting, and (e) load splitting.                                       | 20   |

| Fig. 2-3.  | A typical example for distributed power system                                  | 24   |

| Fig. 2-4.  | Prediction of stability for cascaded impedances                                 | 29   |

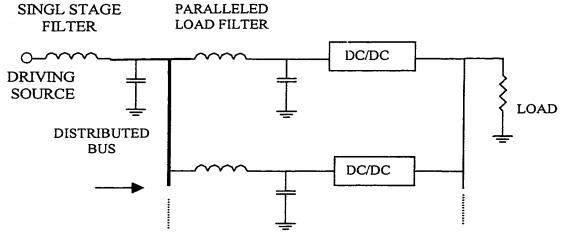

| Fig. 2-5.  | Stability enhanced with single source filter driving paralleled input filters   | .30  |

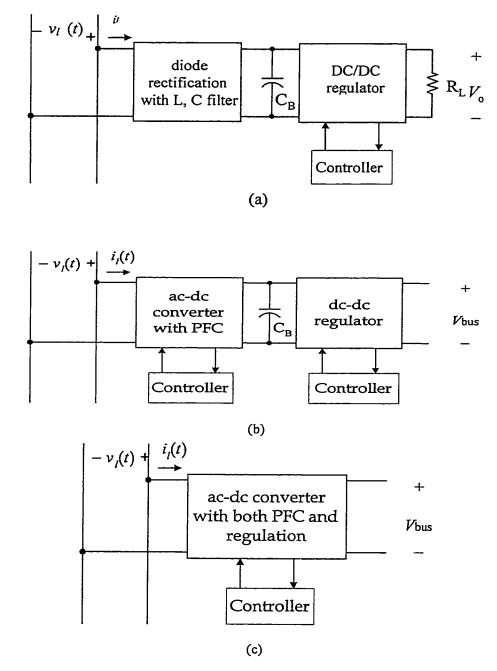

| Fig. 2-6.  | Three PFC approaches (a) passive PFC converter, (b) active two-stage PFC        |      |

|            | converter, and (c) active single-stage (S <sup>2</sup> ) PFC converter.         | .33  |

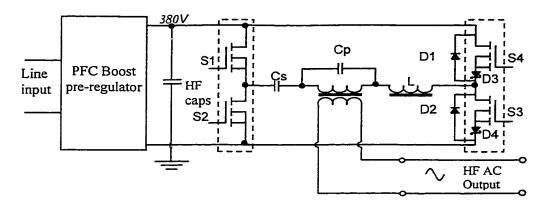

| Fig. 2-7.  | An example of front-end inverter with sine wave bus                             | .45  |

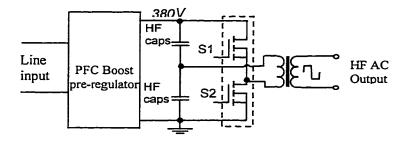

| Fig. 2-8.  | An example of front-end inverter with square wave bus                           | .45  |

| Fig. 2-9.  | An example of single stage front-end inverter                                   | .45  |

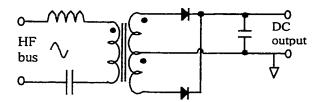

| Fig. 2-10. | A post-regulator using SRR with sine wave bus                                   | .46  |

| Fig. 2-11. | A post-regulator using magamp with square wave bus                              | .46  |

| Fig. 3-1.  | General block diagram of S <sup>2</sup> PFC converters                          | . 54 |

| Fig. 3-2.  | Functional block diagram of S <sup>2</sup> PFC converters                       | . 54 |

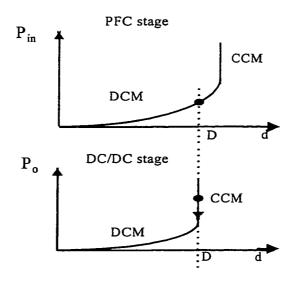

| Fig. 3-3.  | Relationship between the input power, output power, and duty-cycle              | .55  |

| Fig. 3-4.  | S <sup>2</sup> converter consisting of two flyback converters                   | . 58 |

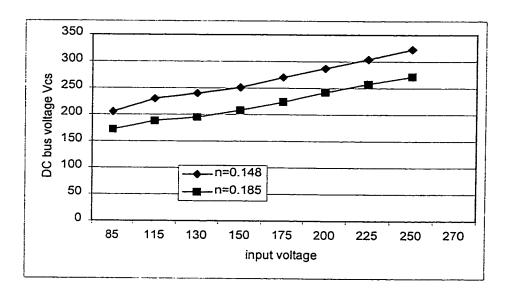

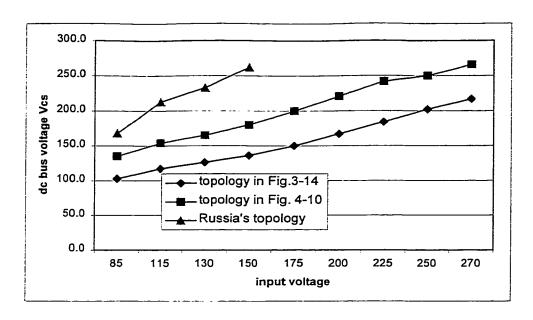

| Fig. 3-5.  | Bus voltage stress comparison under two combinations                            | .62  |

| Fig. 3-6.  | A S <sup>2</sup> converter with low capacitor voltage                           | .63  |

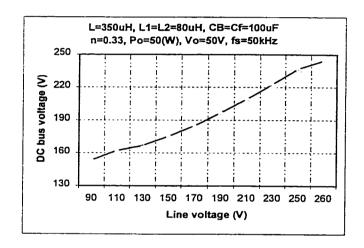

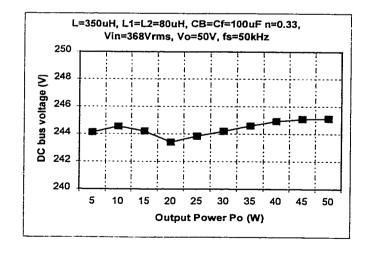

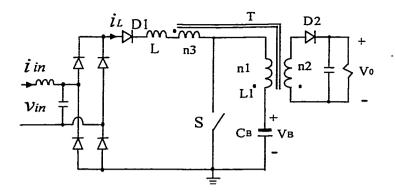

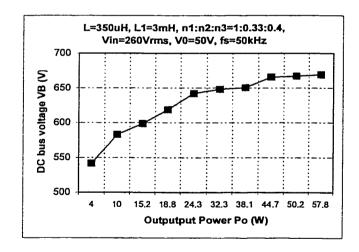

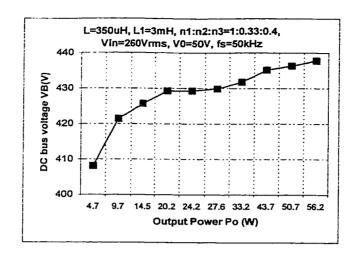

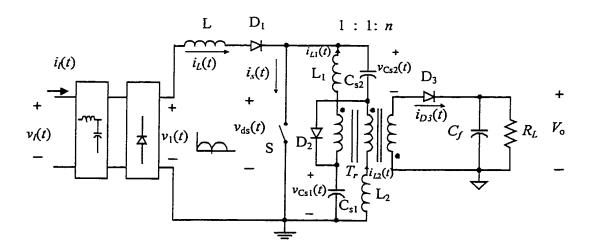

| Fig 3-7    | Bus voltage stress at line voltage for the converter in Fig. 3-6                | 64   |

| Fig. 3-8.  | Bus voltage at output power for the converter in Fig. 3-6                                       | .64 |

|------------|-------------------------------------------------------------------------------------------------|-----|

| Fig. 3-9.  | A S <sup>2</sup> AC/DC converter implementing 3.3Vdc output                                     | .65 |

| Fig. 3-10. | Basic BIFRED converter                                                                          | .66 |

| Fig. 3-11. | BIFRED converter with DC voltage feedback                                                       | .67 |

| Fig. 3-12. | DC bus voltage variation without bus voltage feedback                                           | .67 |

| Fig. 3-13. | DC bus voltage variation with bus voltage feedback                                              | .68 |

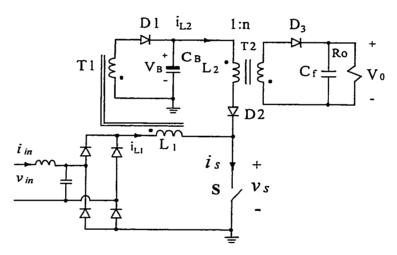

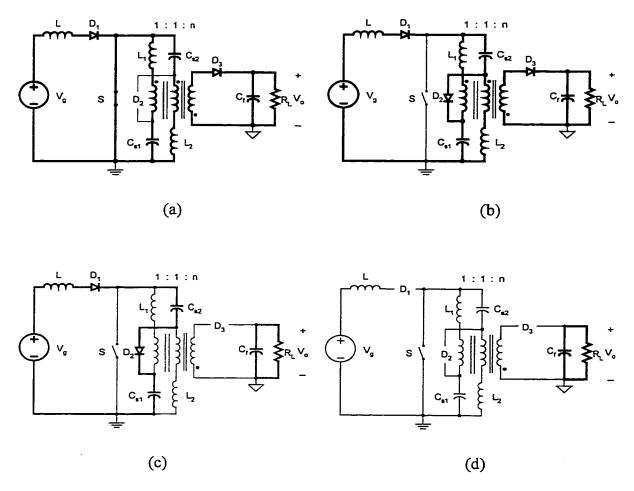

| Fig. 3-14. | Basic circuit schematic of the proposed two-storage capacitor converter                         | .70 |

| Fig. 3-15. | Equivalent topologies for the four switching periods: (a) $P_1(t_0 \le t \le t_1)$ , (b)        |     |

|            | $P_2(t_1 \le t < t_2)$ , (c) $P_3(t_2 \le t < t_3)$ , and (d) $P_4(t_3 \le t < t_0 + T_s)$      | 71  |

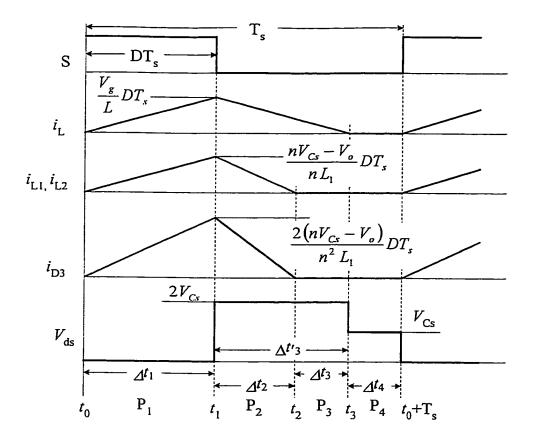

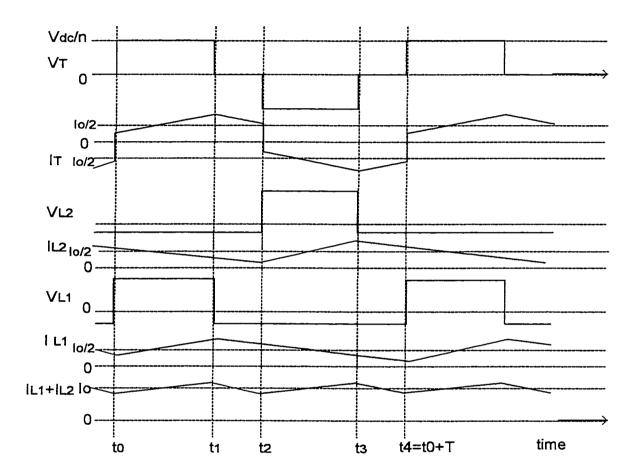

| Fig. 3-16. | Theoretical key waveforms of the proposed converter                                             | .72 |

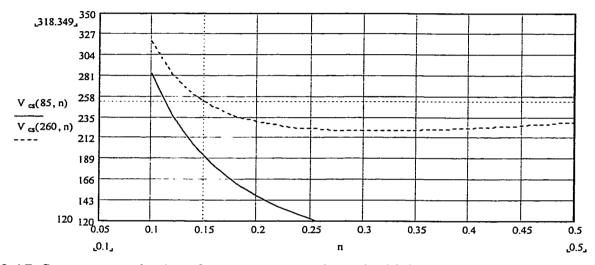

| Fig. 3-17. | Storage capacitor's voltage vs. turns ratio under high line and low line at                     |     |

|            | full load (specs: $V_o$ =28Vdc, L=50uH, R=4.2ohm, $f_s$ =100kHz, L1=10uH,                       |     |

|            | steady-state nominal D <sub>1</sub> =0.33)                                                      | 85  |

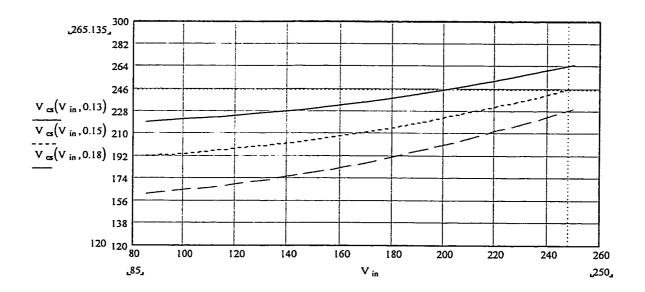

| Fig. 3-18. | Storage capacitor's voltage vs. input voltage under different $n$ at full load                  |     |

|            | (specs: $V_o=28$ , L=50uH, R=4.2ohm, $f_s=100kHz$ , L1=10uH, n=0.15,                            |     |

|            | C <sub>s</sub> =220uF, steady-state nominal D <sub>1</sub> =0.334)                              | 86  |

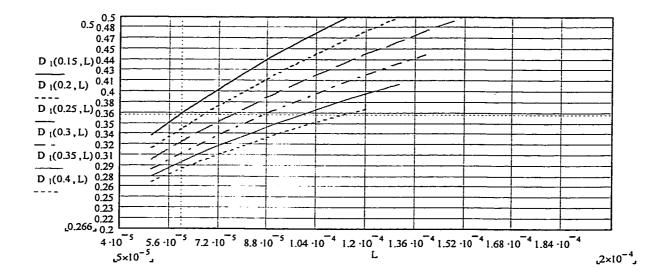

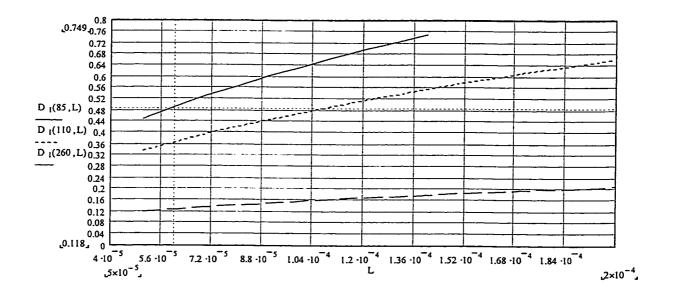

| Fig. 3-19. | Duty cycle vs. inductance of the choke inductor under typical turns ratio $n$                   |     |

|            | (specs: $V_o$ =28, R=4.20hm, $f_s$ =100kHz, $L_1$ =10uH, $V_{in}$ =110 $V_{rms}$ , $C_s$ =220uF | 87  |

| Fig. 3-20. | Duty cycle curves vs. inductance of the choke inductor under typical input                      |     |

|            | voltages (specs: $V_o=28$ , $R=4.2$ ohm, $f_s=100$ kHz, $L_1=10$ uH, $n=0.15$ ,                 |     |

|            | C <sub>s</sub> =220uF)                                                                          | 87  |

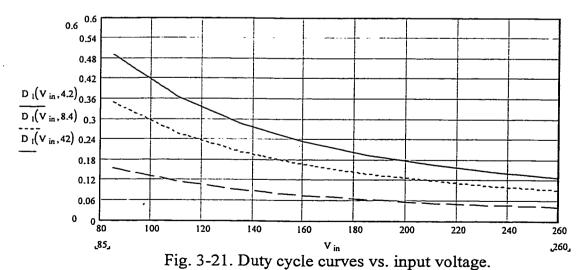

| Fig. 3-21. | Duty cycle vs. input voltage                                                                    | 88  |

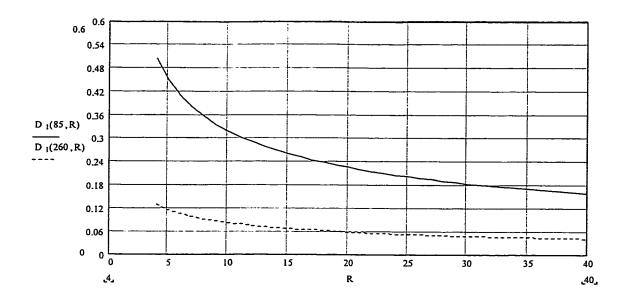

| Fig. 3-22. | Duty cycle vs. load under high line and low line input voltages                                 | 89  |

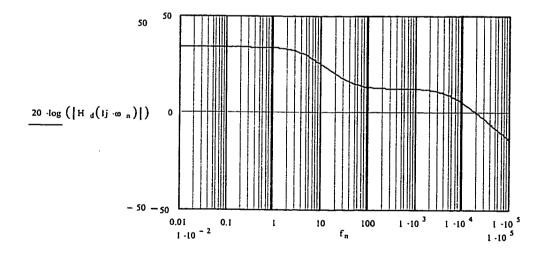

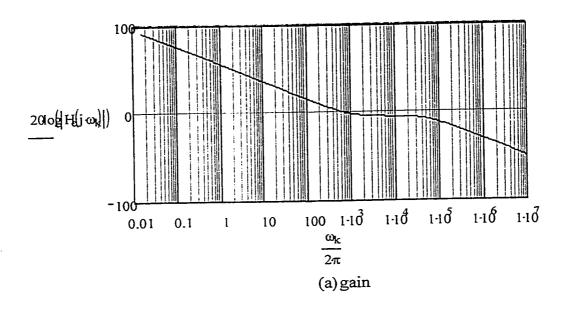

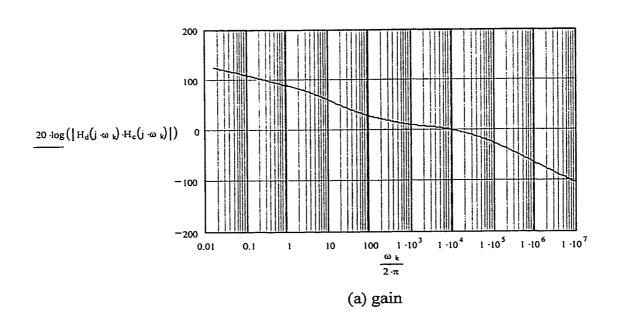

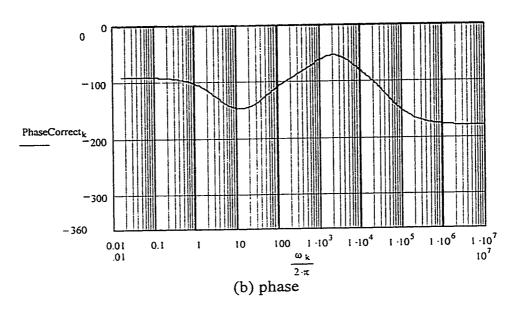

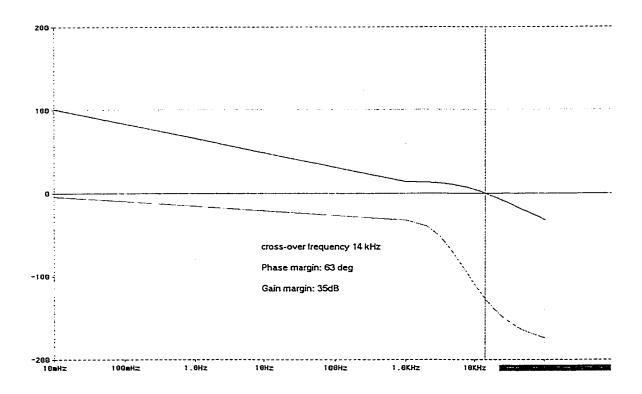

| Fig. 3-23. | Bode plot of open loop transfer function of power stage: (a) gain, and (b)                      |     |

|            | phase                                                                                           |     |

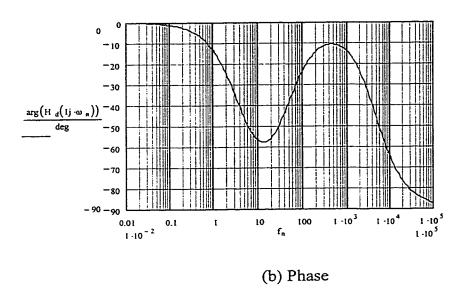

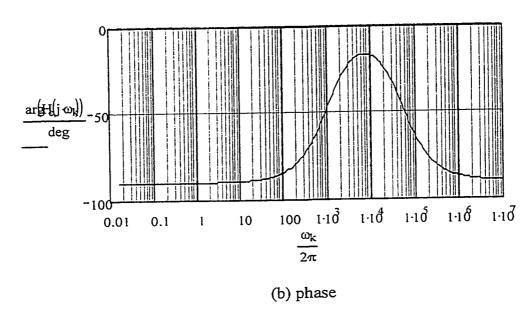

| Fig. 3-24. | Bode plot of compensator transfer function: (a) gain, and (b) phase                             | 92  |

| Fig. 3-25. | Bode plot of closed loop transfer function (a) gain, and (b) phase                              | 93  |

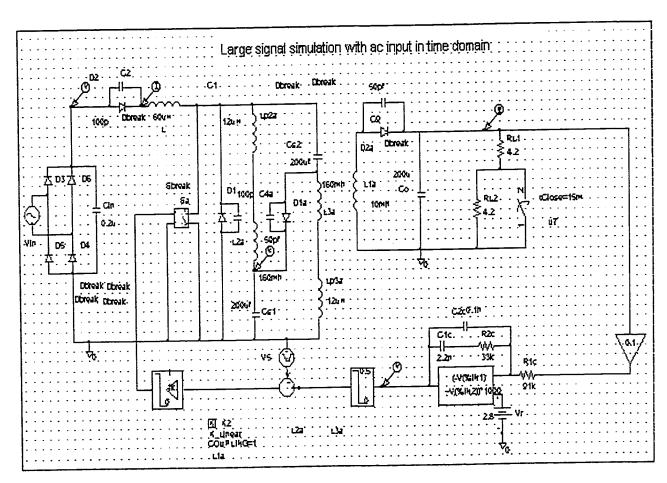

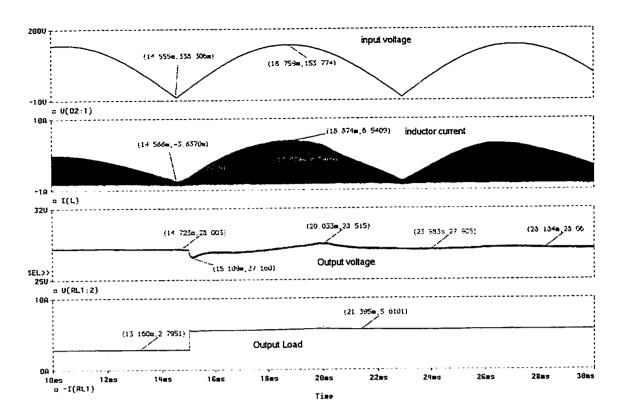

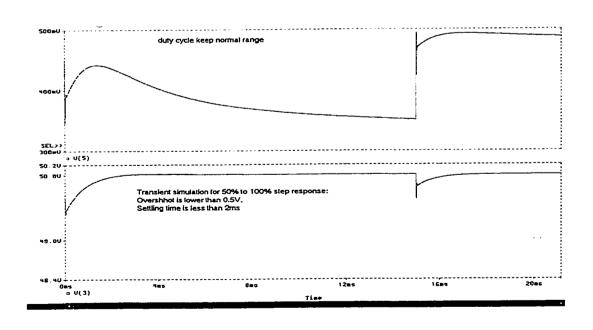

| Fig. 3-26. | Simulated schematics for transient in time domain                                               | 95  |

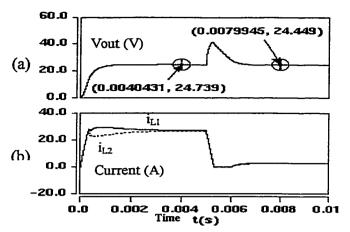

| Fig. 3-27. | 50% step up response with loop crossover frequency at about 1 kHz                               | 96  |

| Fig. 3-28. | 50% step up response with loop crossover frequency at about 14 kHz                              | 96  |

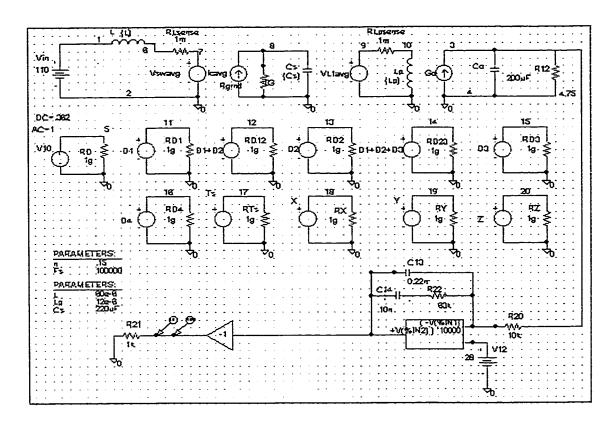

| Fig. 3-29. | Simulated schematics of small signal analysis with averaging model                              | 97  |

| Fig. 3-30. | Simulated Bode plot based on the Fig. 3-29.                                                        | 97         |

|------------|----------------------------------------------------------------------------------------------------|------------|

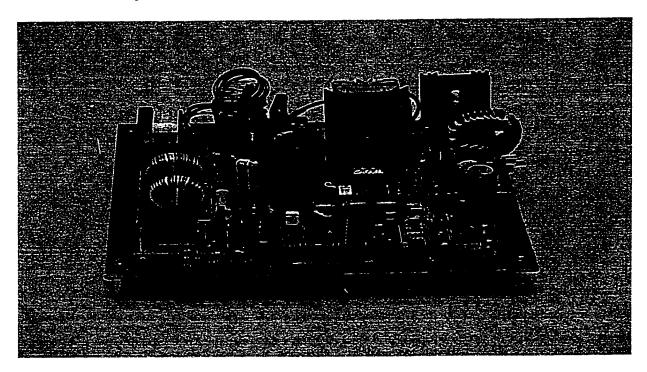

| Fig. 3-31. | Experimental testbed prototype                                                                     | 98         |

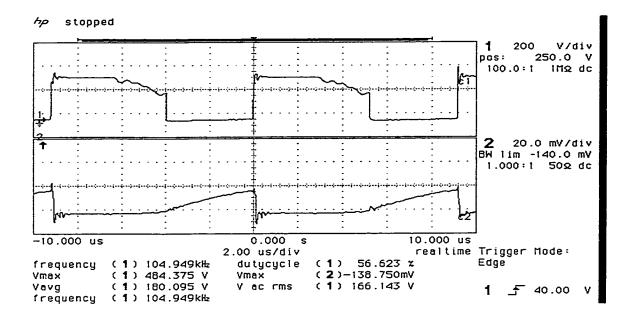

| Fig. 3-32. | Experimental waveforms of the proposed converter: (a) voltage (upper) and                          |            |

|            | current (lower) on the switch, and (b) line voltage and filtered input current                     |            |

|            | of the converter                                                                                   | 99         |

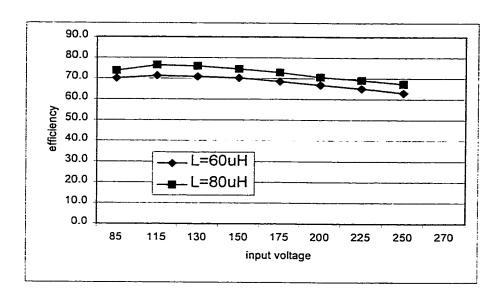

| Fig. 3-33. | Experimental input power factor                                                                    | 00         |

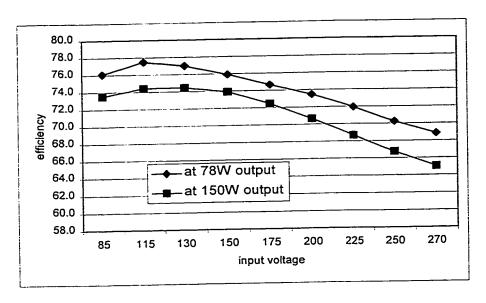

| Fig. 3-34. | Experimental efficiency comparison under different boost inductors at                              |            |

|            | n=0.16 and full load at 160W output                                                                | 01         |

| Fig. 3-35. | Experimental dc bus voltage comparison under different turns ratio $n$ at                          |            |

|            | L=60uH and full load                                                                               | 01         |

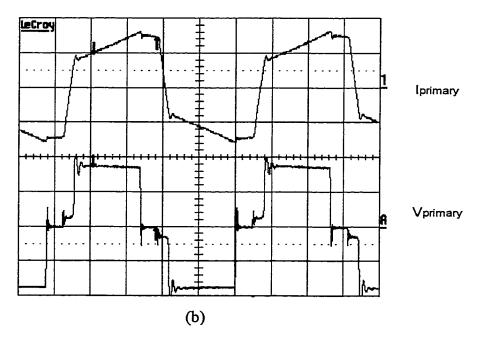

| Fig. 3-36. | Experimental efficiency comparison under half load and full load                                   | 02         |

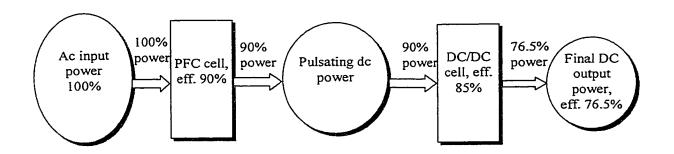

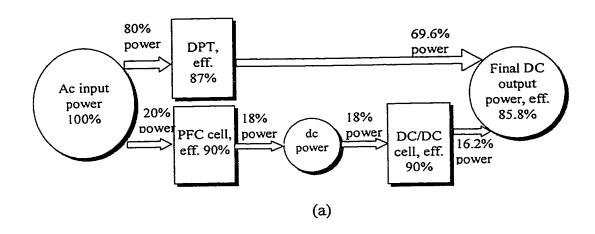

| Fig. 4-1.  | Functional block diagram of a general S <sup>2</sup> PFC converter                                 | 06         |

| Fig. 4-2.  | Functional block diagram of a general two-stage PFC converter                                      | ე6         |

| Fig. 4-3.  | An example of power flow implemented at 150 W in Fig. 3-14                                         | <b>)</b> 8 |

| Fig. 4-4.  | A new roadmap of power process: (a) predicted efficiency with DPT                                  |            |

|            | concept based on the Fig.3-14, and (b) generalized conceptual comparison . 10                      | <b>)9</b>  |

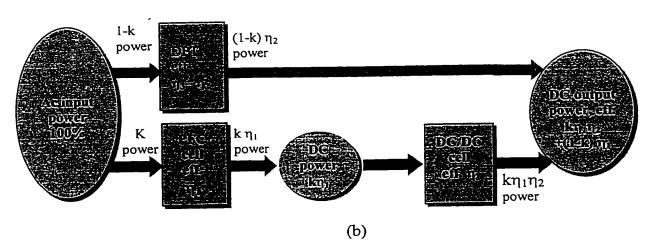

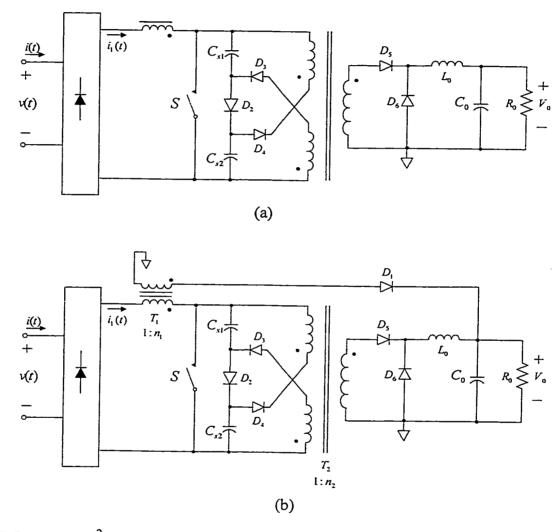

| Fig. 4-5.  | Improved S <sup>2</sup> topologies (a) Russian topology based on Fig. 3-14 topology,               |            |

|            | and (b) new topology with DPT concept based on Russian topology 1                                  | 12         |

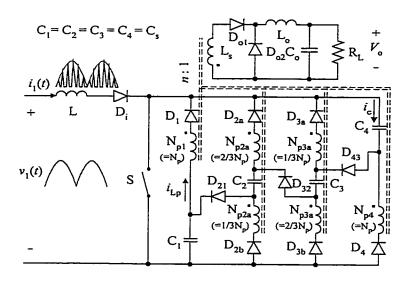

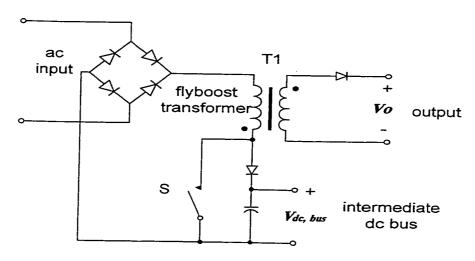

| Fig. 4-6.  | Flyboost PFC cell as a general PFC cell                                                            | 13         |

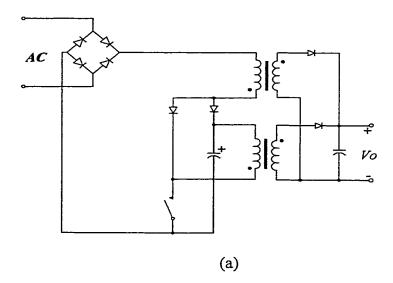

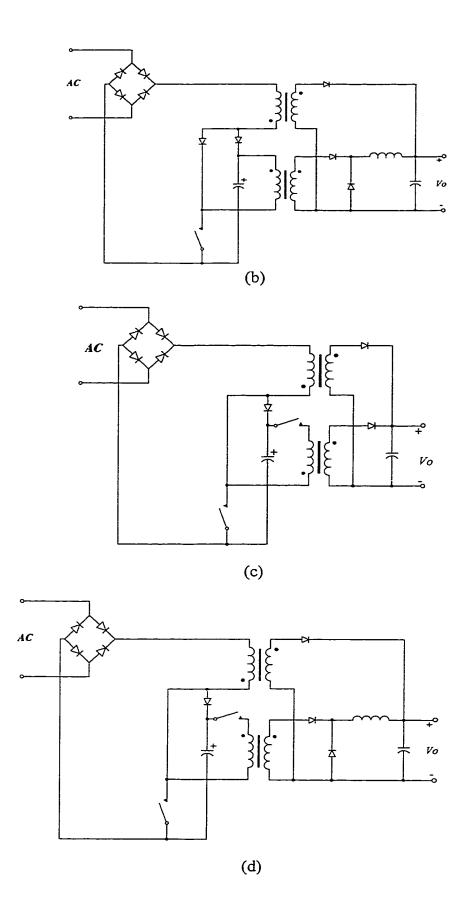

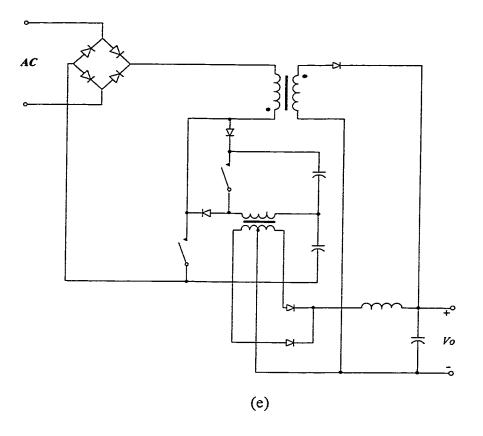

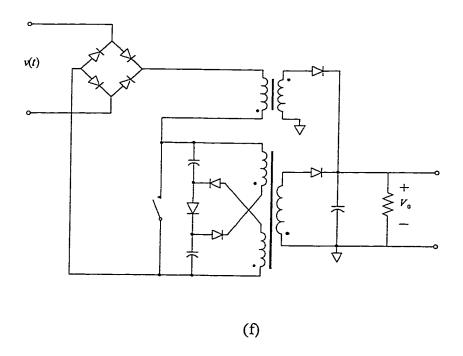

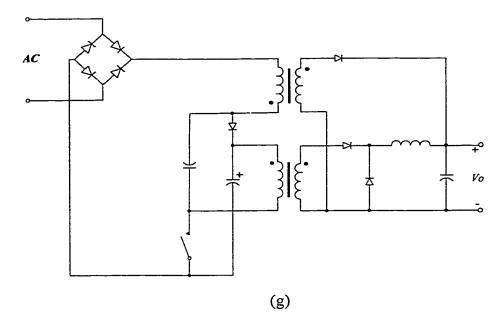

| Fig. 4-7.  | Derived new family of topologies based on the flyboost PFC cell and                                |            |

|            | typical DC/DC cells: (a) flyboost PFC + flyback DC/DC, (b) flyboost PFC                            |            |

|            | + forward DC/DC, (c) flyboost PFC + two switch flyback DC/DC, (d)                                  |            |

|            | flyboost PFC + two switch forward DC/DC, (e) flyboost PFC + half-bridge                            |            |

|            | DC/DC, (f) flyboost PFC + series/parallel flyback, and (g) flyboost PFC +                          |            |

|            | forward DC/DC, but both cells operating in CCM.                                                    | 15         |

| Fig. 4-8.  | Topology with flyboost PFC cell and series/parallel forward cell with                              |            |

|            | center-tapped secondary side rectification                                                         | 19         |

| Fig. 4-9.  | Topology with reduced low-frequency ripple                                                         | 20         |

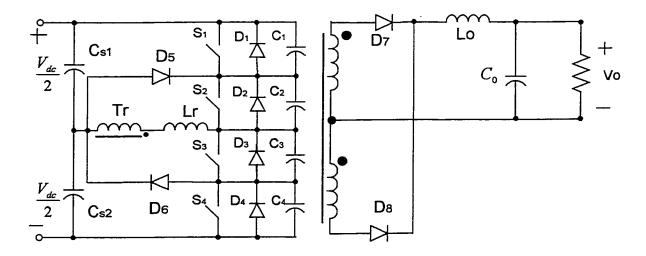

| Fig. 4-10. | Combined topology with flyboost PFC cell and series/parallel forward cell. 12                      | 21         |

| Fig. 4-11. | Sections of circuit operation: (a) other S <sup>2</sup> converter, and (b) proposed S <sup>2</sup> |            |

|            | converters12                                                                                       | 23         |

| Fig. 4-12  | . Operation modes for flyboost under ideal case                                | 124         |

|------------|--------------------------------------------------------------------------------|-------------|

| Fig. 4-13  | . Key waveforms corresponding to Table 4-1                                     | 125         |

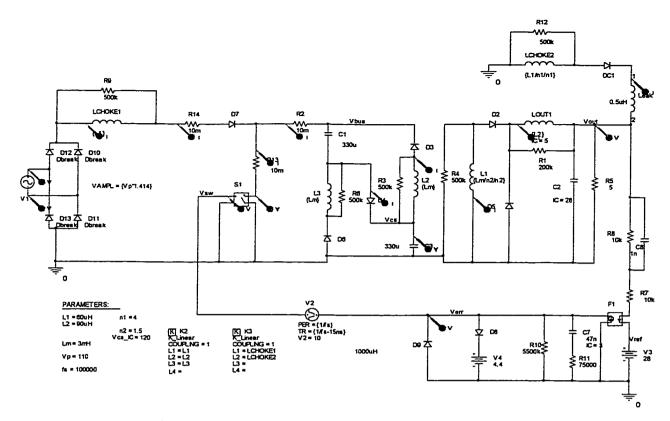

| Fig. 4-14  | . Simulated Schematics based on the OrCAD 9.2                                  | 131         |

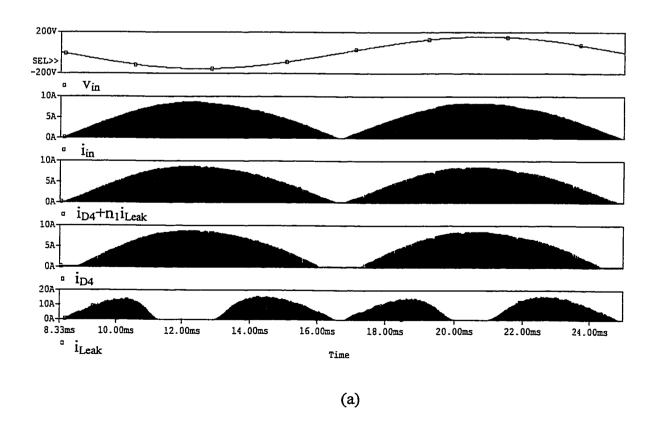

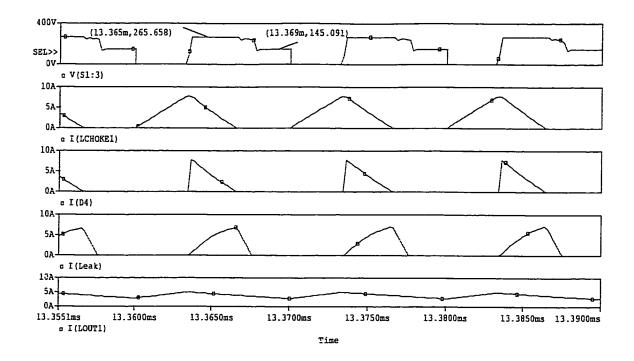

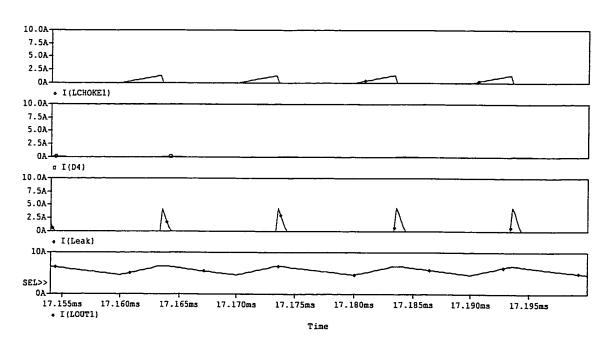

| Fig. 4-15  | . Interested simulation waveforms of proposed topology for different           |             |

|            | operation modes under DCM +CCM operation: (a) power flow in terms of           | •           |

|            | line cycle, (b) mixed mode in terms of switching cycle, (c) flyback mode       |             |

|            | and (d) boost mode.                                                            | 131         |

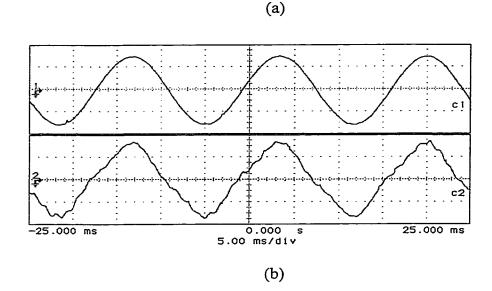

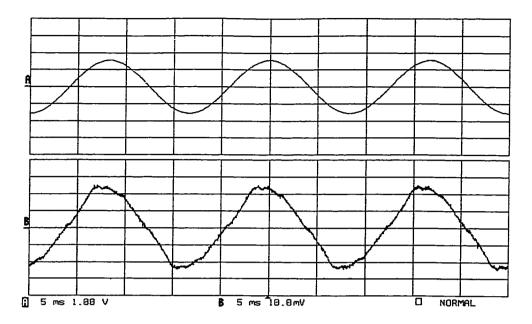

| Fig. 4-16  | . Experimental line voltage and line current at nominal voltage=110Vrms:       |             |

|            | trace A, line voltage (100V/div, 5ms/div); trace B, line current (measured     |             |

|            | after auxiliary line filter; 1 A/div; 5ms/div), and the measured power factor  |             |

|            | is 99.4%                                                                       | 135         |

| Fig. 4-17. | . Simulated and experimental waveforms of drain-source voltage and drain       |             |

|            | current of the main switch                                                     | 136         |

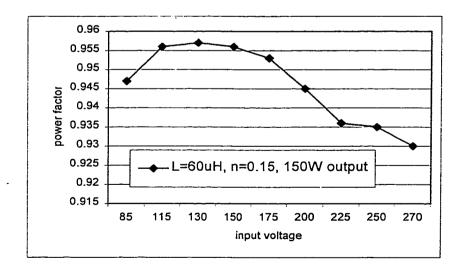

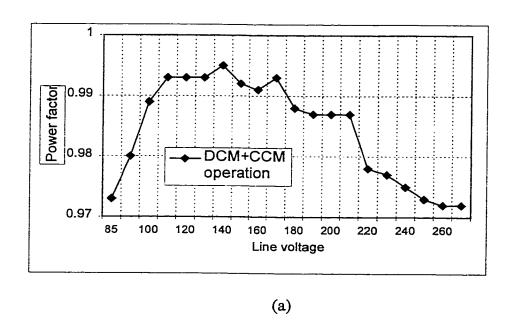

| Fig. 4-18. | Experimental results: (a) power factor, (b) Efficiency, and (c) Storage        |             |

|            | capacitor voltage varying with input line voltage                              | 136         |

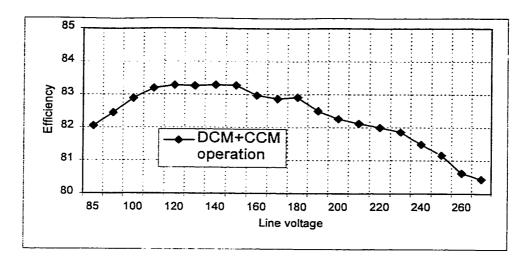

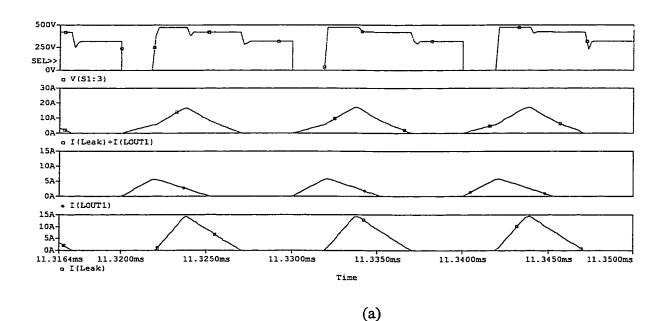

| Fig. 4-19. | Simulated and experimental waveforms of showing interleaving at high           |             |

|            | line, from upper to lower lines, $V_{ds}$ , interleaved secondary side output  |             |

|            | current, forward and flyboost secondary side currents (a) simulated results,   |             |

|            | and (b) experimental results                                                   | 138         |

| Fig. 4-20. | Simulated and experimental waveforms for the active switch at low line:        |             |

|            | (a) simulated waveforms, and (b) Experimental waveforms.                       | 139         |

| Fig. 4-21. | Experimental power factor comparison for a 150W S <sup>2</sup> converter using |             |

|            | several similar topologies                                                     | 141         |

| Fig. 4-22. | Experimental efficiency comparison with several similar topologies             | 141         |

| Fig. 4-23. | Experimental dc bus voltage comparison with several similar topologies         | 142         |

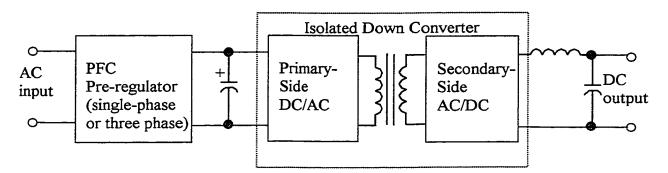

| Fig. 5-1.  | Basic structure of a two-stage front-end converter                             | l46         |

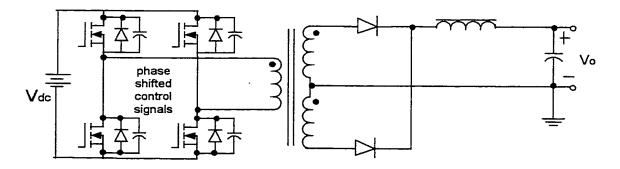

| Fig. 5-2.  | A classical ZVT-PS-FB schematic                                                | i 47        |

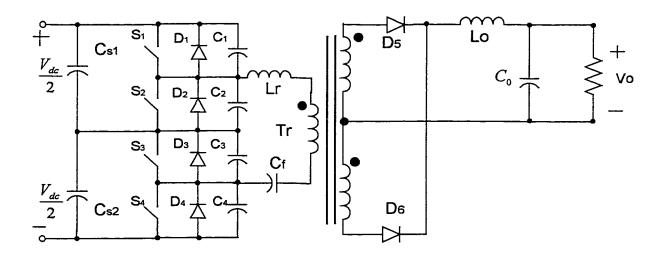

| Fig. 5-3.  | Topology #1: based on the multilevel voltage cell with neutral point           |             |

|            | clamped                                                                        | l <b>49</b> |

| Fig. 5-4.  | Topology #2: based on the multilevel voltage cell with a floating capacitor.   | 150         |

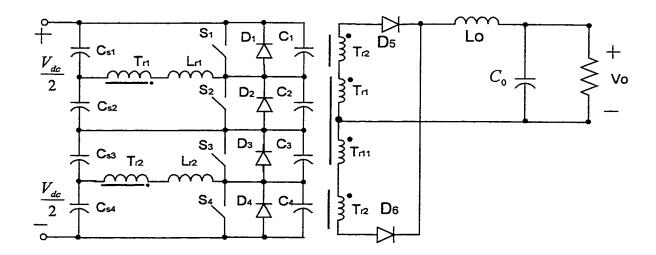

| Fig. 5-5.  | Topology #3: based on the series combination of half bridge converter 1        | 151         |

| Fig. 5-6.  | Topology #4: double full bridge ZVS converter                                         |

|------------|---------------------------------------------------------------------------------------|

| Fig. 5-7.  | Topology #5: double full bridge ZVS converter coupled by a transformer 153            |

| Fig. 5-8.  | Topology #6: double full bridge ZVS converter coupled by two                          |

|            | transformers                                                                          |

| Fig. 5-9.  | Three commonly used secondary-side topologies (a) full-bridge diode                   |

|            | rectification, (b) center-tapped rectification, and (c) current doubler               |

|            | rectification                                                                         |

| Fig. 5-10. | Key waveforms of center-tapped rectification topology of Fig. 5-9(b)157               |

| Fig. 5-11. | Key operation waveforms of current doubler rectification topology 159                 |

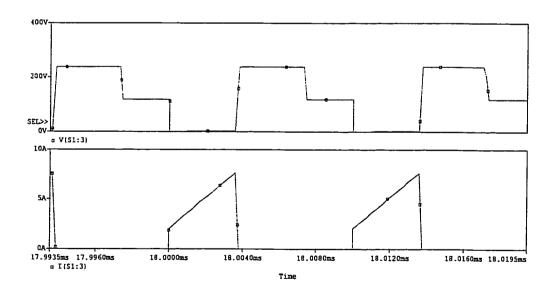

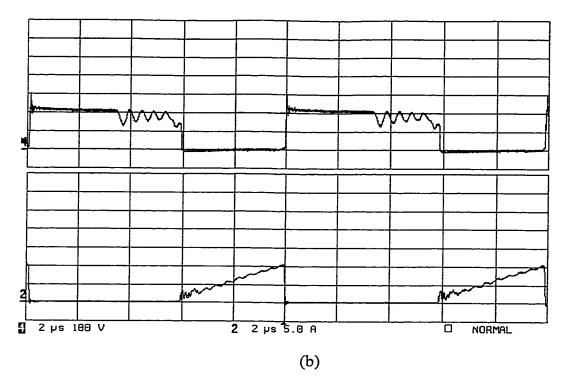

| Fig. 5-12. | Experimental prototype of a 3500W for comparing secondary-side                        |

|            | topologies, using UC3879 as primary controller to realize ZVT 165                     |

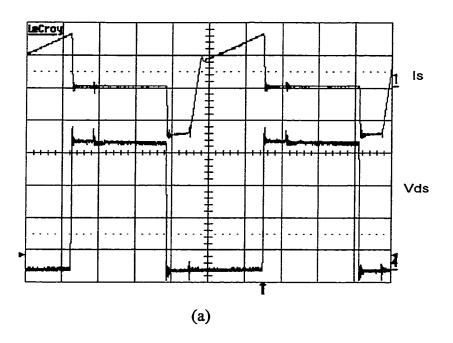

| Fig. 5-13. | Fig. 5-13. Operation waveforms at the primary-side (a) waveforms on the               |

|            | switch: positive and negative peak currents are 15.5A and 16.2A                       |

|            | (10A/div); peak voltage 440V and dc bus voltage 400V (100V/div),                      |

|            | f <sub>s</sub> =95.272kHz, and (b) waveforms on the transformer at dc bus voltage     |

|            | 360V (upper trace: 10A/div; lower trace: 400V/div)                                    |

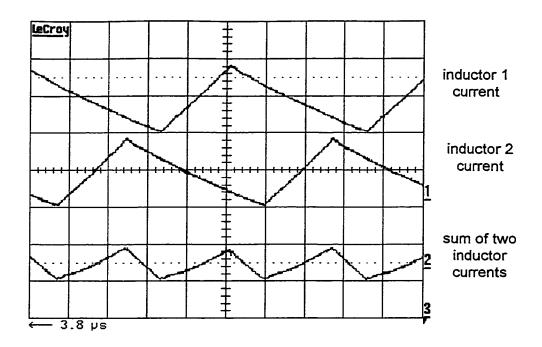

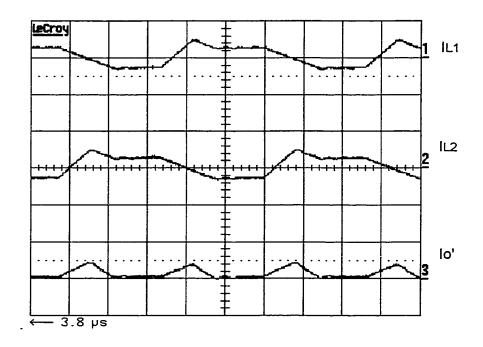

| Fig. 5-14. | Operation waveforms of secondary-side for current doubler at full load,               |

|            | current ripple $\Delta I_1 = \Delta I_2 = 17.5$ A, $\Delta I_0 = 9.1$ A; 10A/div atio |

| Fig 5-15.  | DCM operation of secondary-side for current doubler at light load, 53V @              |

|            | 1A output, 10A/div                                                                    |

| Fig. 5-16. | Experimental efficiency comparison (a) at 360V input, and (b) at 400V                 |

|            | input                                                                                 |

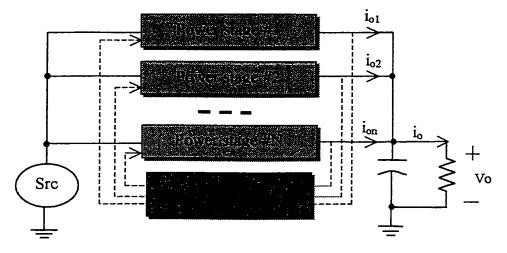

| Fig. 6-1.  | Block diagram of power supply with interleaved power stages                           |

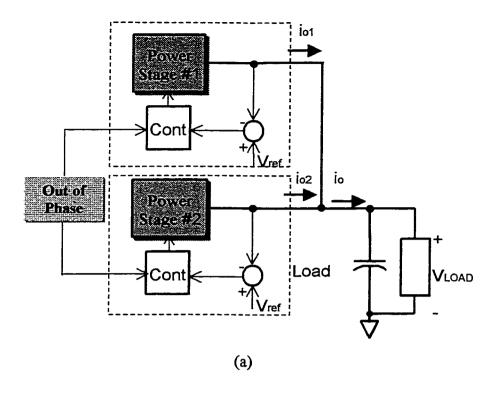

| Fig. 6-2.  | An example of interleaving implementation for two power stage case: (a)               |

|            | interleaved power stages, and (b) output ripple cancellation demonstration . 175      |

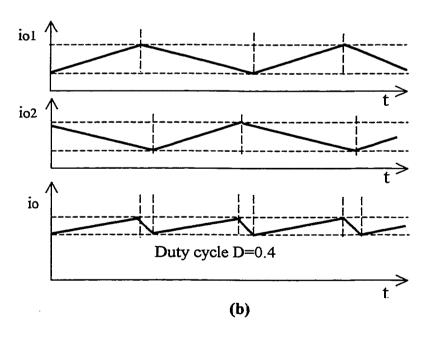

| Fig. 6-3.  | Optional schematics to implement high power conversion: (a) single power              |

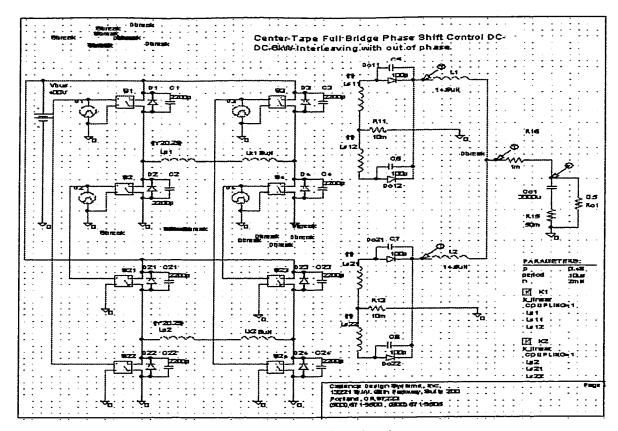

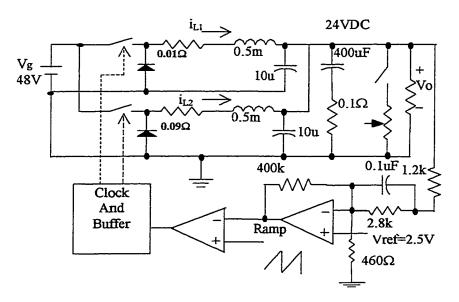

|            | stage, (b) two-interleaved power stage                                                |

| Fig. 6-4.  | Simulated schematics for interleaving power stage                                     |

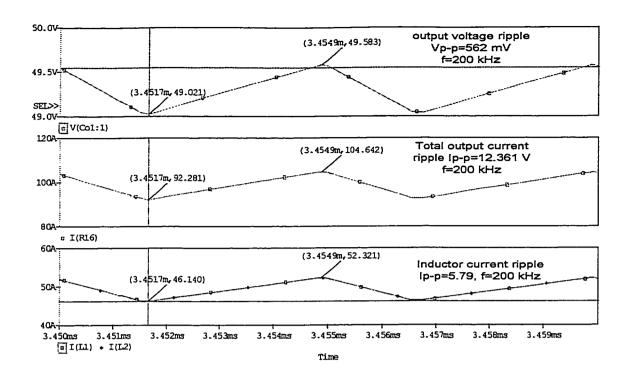

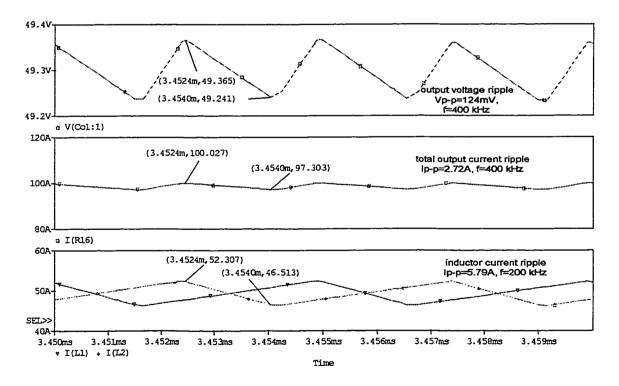

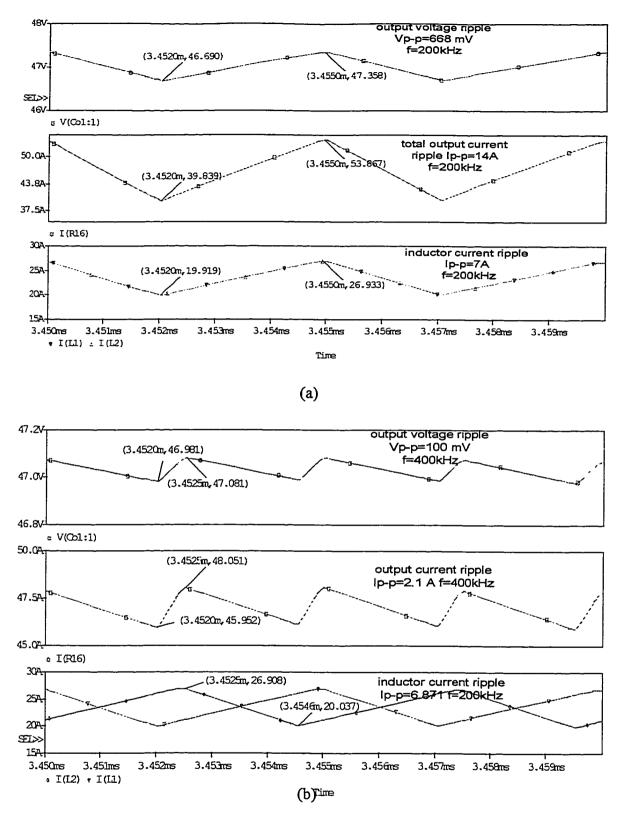

| Fig. 6-5.  | Simulation waveforms for one power stage case                                         |

| Fig. 6-6.  | Simulated waveforms of interleaved power stage implementation but using               |

|            | conventional interleaving control strategy                                            |

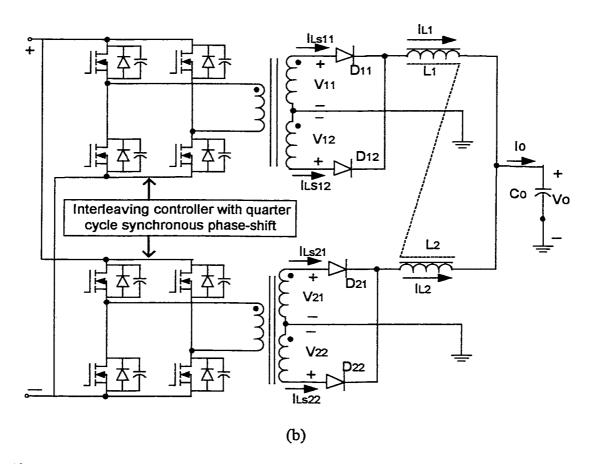

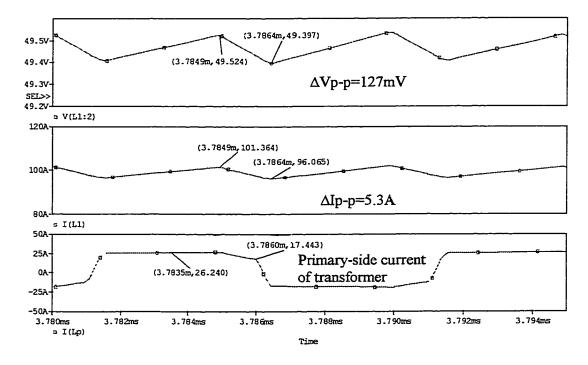

| Fig. 6  | 5-7.         | Simulated results with new interleaving method.                               | 185 |

|---------|--------------|-------------------------------------------------------------------------------|-----|

| Fig. 6  | 5-8.         | Simulated comparison for different phase-shift strategy under 50% load        | i   |

|         |              | operation: (a) conventional interleaving method, and (b) new interleaving     | 5   |

|         |              | method                                                                        | 186 |

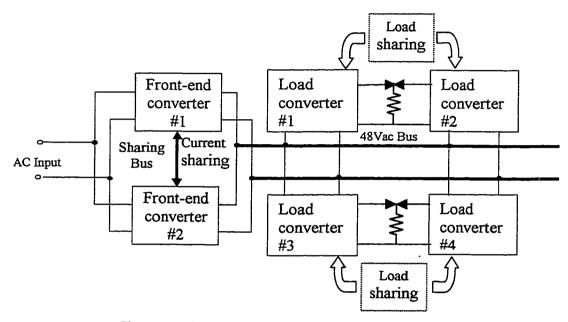

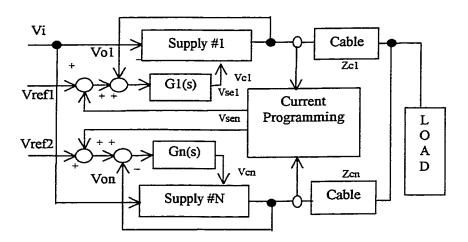

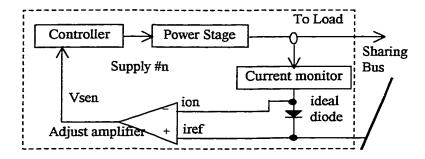

| Fig. 7  | <b>7-</b> 1. | Block diagram of a multiple converter system                                  | 191 |

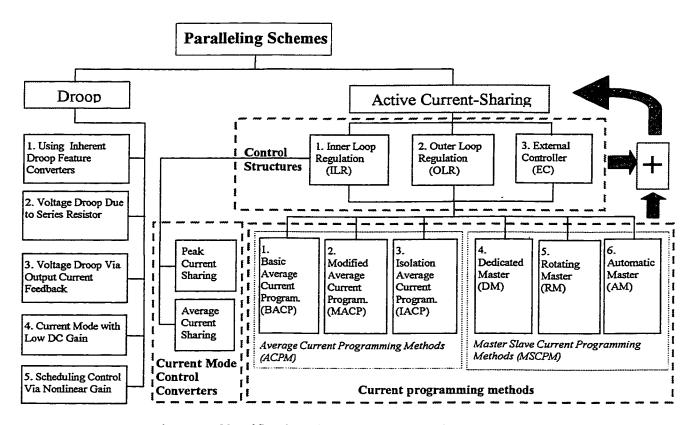

| Fig. 7  | <b>7-</b> 2. | Classification diagram for paralleling methods                                | 192 |

| Fig. 7  | <b>7-</b> 3. | Voltage droop via output current feedback                                     | 195 |

| Fig. 7  | <b>-</b> 4.  | Current mode with low DC gain                                                 | 196 |

| Fig. 7  | <b>'-</b> 5. | Scheduling control via nonlinear gain                                         | 197 |

| Fig. 7  | <b>'-</b> 6. | A typical block diagram of inner loop regulation structure                    | 198 |

| Fig. 7  | <b>-</b> 7.  | A typical block diagram of outer loop regulation structure                    | 200 |

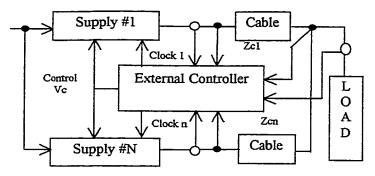

| Fig. 7  | <b>'-8</b> . | A typical block diagram of external controller structure                      | 201 |

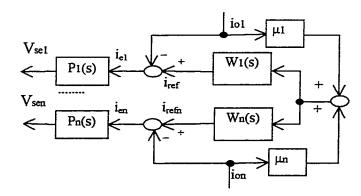

| Fig. 7  | <b>-</b> 9.  | A unified block diagram for current-programming                               | 203 |

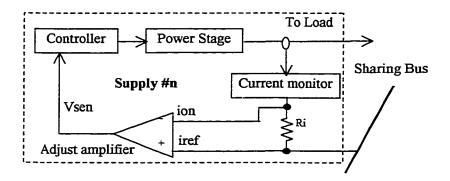

| Fig. 7  | -10.         | A typical example for basic BACP                                              | 204 |

| Fig. 7  | -11.         | A typical implementation of automatic master scheme                           | 208 |

| Fig. 7  | -12.         | Controller and power circuit used in simulation for two parallel-connected    | -   |

|         |              | buck converters under single-loop control                                     | 209 |

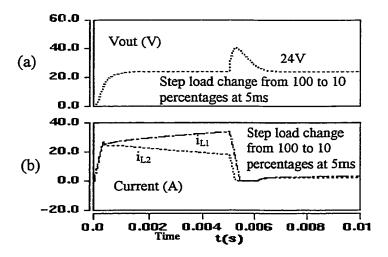

| Fig. 7  | -13.         | Simulated results without sharing control: (a) output voltage, and (b) output | ,   |

|         |              | currents of two buck converters under no current-sharing control (Step-load   |     |

|         |              | change at t=5ms)                                                              | 209 |

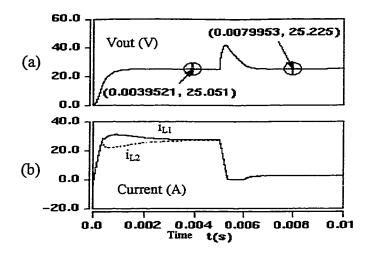

| Fig. 7- | -14.         | Simulated results using (AM+OLR) sharing method, i.e., automatic master       |     |

|         |              | under outer loop regulation: (a) Output voltage, and (b) output current       | 210 |

| Fig. 7- | -15.         | Simulated results using (BACP+OLR) sharing method: (a) output voltage,        |     |

|         |              | and (b) utput current                                                         | 211 |

| Fig. 7- | -16.         | Simulated results using (AM+ILR) sharing method. (a) output voltage, and      |     |

|         |              | (b) output current                                                            | 211 |

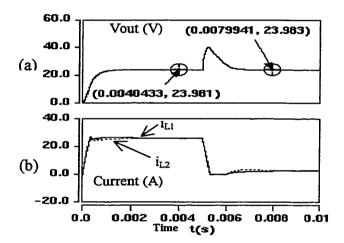

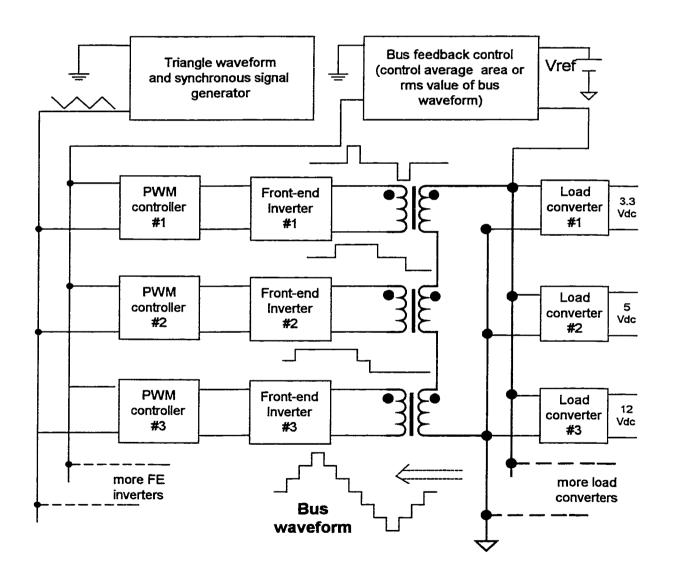

| Fig. 8- | <b>-</b> 1.  | System configuration block diagram of a new DPS with multiple PWM-            |     |

|         |              | wave bus                                                                      | 215 |

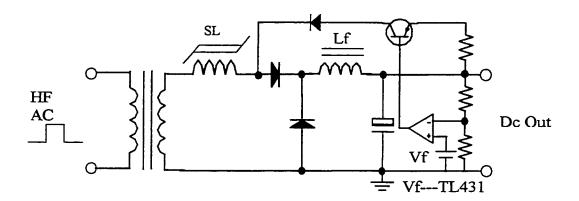

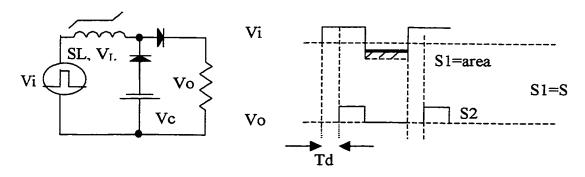

| Fig. 8- | <b>-2</b> .  | An example circuit of half-wave magamp                                        | 218 |

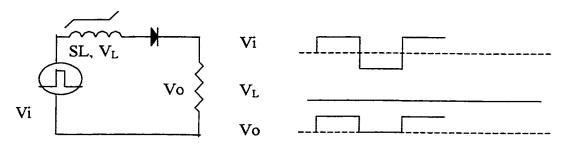

| Fig. 8- | -3.          | Principle of operation for half-wave magamp using ideal magnetic core         | 219 |

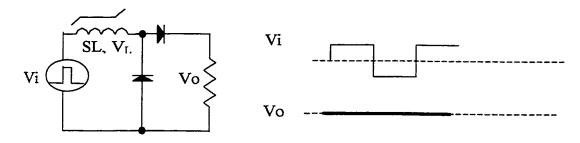

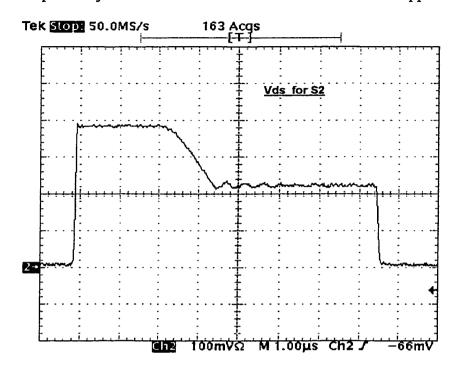

| Fig 8-  | -4           | Drain to source voltage for switching MOSEET S <sup>2</sup> 100V/div          | 225 |

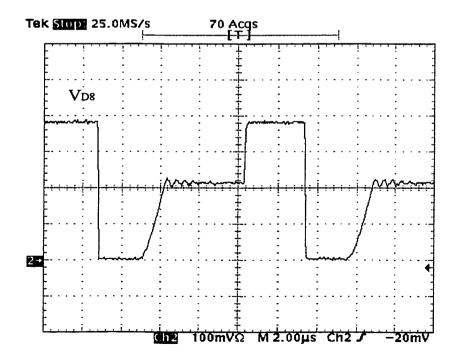

| Fig. 8-5. | Blocking voltage on D <sub>8</sub>                                | 225  |

|-----------|-------------------------------------------------------------------|------|

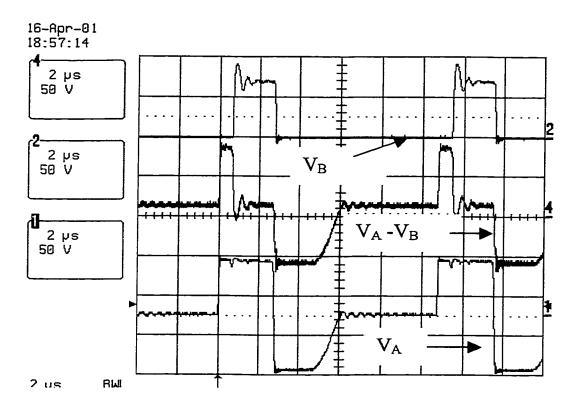

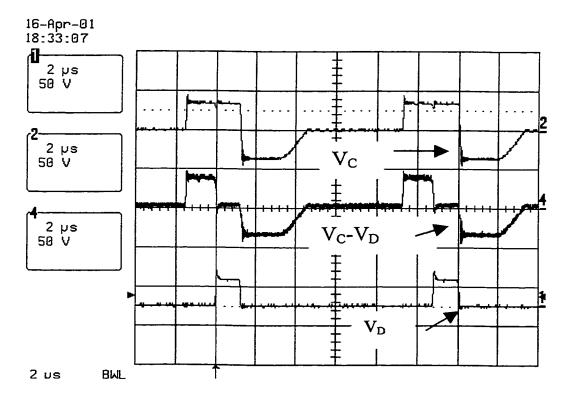

| Fig. 8-6. | Operating waveform of magamp at 12V output                        | .226 |

| Fig. 8-7. | Magamp waveform for 3.3V output.                                  | .226 |

| Fig. 8-8. | Proposed scheme to implement AC-DPS with trapezoidal waveform bus | .229 |

#### 1. INTRODUCTION

### 1.1 Background and Motivations

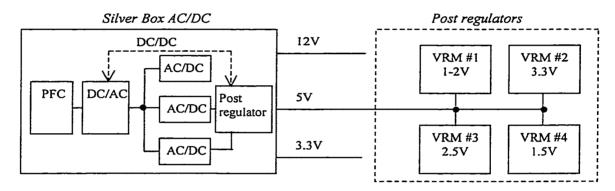

Power conversion system design issues are becoming increasingly important in state-of-the-art electronics systems, especially in computing and information system applications. However, the basic power architecture in current electronic systems remains the same as it was decades ago [1,3]. Many of current power architectures are no longer effective in terms of performance and/or cost. For example, current stand-alone "silver box" designs in computers are unable to meet transient voltage regulation requirements for future computer systems. As a result, post-regulators (known as voltage regulator modules or "VRM") are being developed. The power processing combination of the silver box and VRM is used to meet the future microcomputer's stringent power quality requirement, as shown in Fig. 1-1. However, VRM performance (e.g., efficiency and transient response) is constrained to the limitations imposed by the silver box outputs. A power processing structure where there are several conversion steps in series will lead to an inefficient overall power system design, accompanying a relatively larger size and weight [4,5]. A target area for reducing the power system cost is to eliminate and/or simplify as many conversion steps as possible. This is especially true in light of the more stringent power system performance objectives that lie in the future computer system design [2-7].

Also, it is very difficult to optimize the VRM design to further improve efficiency. The size is also difficult to reduced. It utilizes a large amount of input and output capacitors that contribute to the most part of the volume of VRM. In addition, another drawback to the power system architecture shown in Fig. 1-1 is its inflexibility. As a particularly important issue for high-availability/fault-tolerant computing systems (e.g., workstations and servers), this inflexibility causes the following profound impacts [8-11]:

Fig. 1-1. Power processing combination scheme using silver box and VRMs for future generation of computers.

- 1) As system power level increases, the distribution of multiple low-output voltages becomes impractical and the silver box efficiency suffers.

- 2) Non-isolated VRMs may lead to potential difficulties with ground loops, load-fault isolation, and system noise levels.

- 3) The power backup function at the output side of the silver box in the power system is complicated, primarily because there is no common output bus.

- 4) A fault-tolerant system design requires a redundant silver box, and this implies high system cost and complicated power architecture.

Solutions to the above problems can be found in distributed power system (DPS) structure [1,2,7-17]. Today's power system in electronic equipment is actually a hybrid system. As we see it, the trend toward distributed power and away from centralized power is being forced upon the industry because of the use of ICs with lower voltages and higher clock rates. The next decade projection from the Semiconductor Industry Association points out the need for efficient supplies with less than one volt output that can handle the load of processors with giga-hertz clock rates. Distributed power can meet this need because it provides better point-of-load voltage regulation than centralized power for high-speed, low-voltage microprocessor. However, the jury is still out on deciding exactly what distributed power system design approach should be followed [1-5].

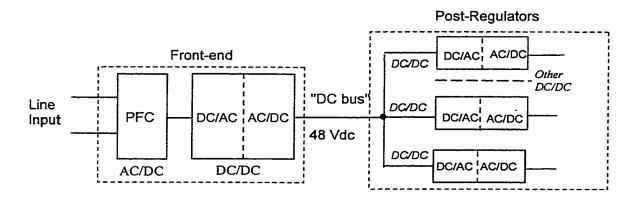

Broadly speaking, there are two possible distributed power approaches: AC-bus or DC-bus. The DC approach employs an intermediate DC voltage, say 48V, which is distributed to multiple DC-DC converters in system. In the AC approach, an intermediate high frequency AC voltage (might be 48V) is distributed to each AC-DC power supply in the system. The DC outputs of load converters may range from 1V to 12V for computer system applications.

A typical DPS architecture with 48 Vdc bus is shown in Fig. 1-2. Generally, four to five power conversion steps are required to obtain ideal electrical specifications to meet load need from an AC line input. One way to reduce the power system cost is to eliminate and/or simplify as many conversion steps as possible. It is expected that this will be the trend in future power supply system design. Compared to the above power processing approach-combination of the silver box and VRM, with a 48 Vdc bus, VRM

efficiency can be improved by as much as 3% [4,5]. Not only is the VRM efficiency improved; but also the accompanying I<sup>2</sup>R loss is decreased in distributing power to the VRMs from silver box.

Fig. 1-2. A typical architecture of DC distributed power system.

In fact, the DC-DPS is not a new concept, as it has been used extensively in mainframe computer systems, communication systems, aircraft, fighting jets, warships, phased-radar arrays, and space vehicles, and lately been used in the construction of the international space station [7-12]. In the system of Fig. 1-2, although the front-end-design is now simplified, the power architecture in the system still requires five conversion steps (an inner AC/DC or DC/AC as a step) to process power from the AC line to the system loads. Three of these conversion steps reside within the front-end converter. Therefore, it becomes a natural target for further simplification [18-24].

DC-DPS system has been an improvement over supply system of Fig. 1-1. However, the complexity of the DC-DPS shown of Fig. 1-2 can be further simplified by using high frequency AC-DPS structure. As shown in Fig. 1-3, AC/DC conversion step in front-ended DC/DC stage and DC/AC conversion step in post-regulator of Fig. 1-2 are

eliminated, i.e., two out of five power conversion steps that may be removed. The resultant AC-DPS structure, if successful, can be expected to have less components and higher efficiency [31-45].

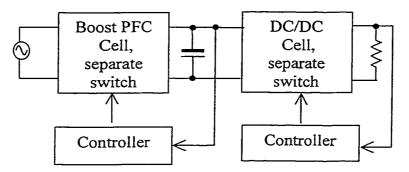

Fig. 1-3. A typical architecture of AC distributed power system.

From a structural complexity viewpoint, we believe that the proposed AC-DPS shown in Fig. 1-3 is a significant improvement over the DC-DPS counterpart system shown in Fig. 1-2. These two systems have a common feature that the front-end converters in DPS with AC or DC bus are implemented with two-stage schemes to meet stringent power factor and harmonics regulations. In this two-stage scheme, an active power-factor correction stage (usually boost converter) is adopted as first stage to force the line current track the line voltage. The second stage is a DC/DC converter in a DC-DPS and a DC/AC inverter in an AC-DPS, which provides the both isolation and the tightly regulated output voltage to meet bus requirements. This two-stage scheme suffers from some drawbacks such as an increased number of components, and a complicated power train and controller. This is why such schemes are not ideal for a cost-effective and efficient structure. We need to make sure if it is possible to further simplify power conversion steps in front-ended through applying advanced power conversion techniques.

This is just one of the major motivations of this dissertation work, namely, how to design front-end converters with simplified system configuration, high efficiency, and low cost.

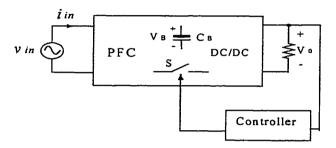

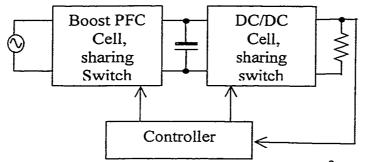

The above motivation drives us to incorporate advanced power conversion techniques into the systems of Figs. 1-2 and 1-3 in order to obtain further simplification of the overall DPS structure. An alternative solution to realize the goal is to integrate the active PFC stage with the isolated high quality output DC/DC or DC/AC stage into one stage, which is known as single stage (S<sup>2</sup>) converter with PFC or S<sup>2</sup> inverter with PFC. The S<sup>2</sup> converter or S<sup>2</sup> inverter has the least number of components and uses only one controller in the front-end power stage of DC or AC-DPS.

The underlying strategy of S<sup>2</sup> converter is to design the circuit in such a way that it allows its PFC circuit and voltage regulation circuit to share the same power stage. It is the S<sup>2</sup> converter that has least components and simplest controller. Therefore, by applying S<sup>2</sup> converter to implement all the functions of a front-end converter in a DC-DPS, we will obtain the simplest DC-DPS, as shown in Fig. 1-4.

Fig. 1-4. Simplified DC distributed power system.

Correspondingly, by applying the S<sup>2</sup> inverter as a front-end stage in AC-DPS, we will obtain the simplest system structure of the AC-DPS, as shown in Fig.1-5. So far there is no significant research efforts in the proposed system structure as there is no published work in the open literature.

Fig. 1-5. Simplified AC distributed power system.

Although a certain number of S<sup>2</sup> converters have been reported in [17-23], all of those S<sup>2</sup> converters are not for application to front-end converters in DC-DPS. So those S<sup>2</sup> converter generally have low power rating and/or low efficiency. In order to use S<sup>2</sup> converter into a DPS, its power level must be first pushed to/over medium power level. Currently this is one of the most challenge issues to useful application of S<sup>2</sup> converters into DPS. Other issues include high bus capacitor voltage-stress, wide DC bus voltage range, difficult design for power train, and low efficiency at relatively high power output. Thus, the target of this work also aims at the above issues and present new approaches to innovate conventional power conversion techniques.

Today's electronic systems become more and more sophisticated. In many of advanced application cases, it is difficult for a single power converter or power supply to meet all system performance requirements. In particular, for a high power, high reliability power system, system integration technology employing multiple power stages or

multiple converters have gained rapid acceptance in recent years [47, 48].

In fact, system integration techniques cover very extensive multiple branch research areas, such as interleaving techniques, paralleling, system simplifying, stocking, device integration, control integration and packaging integration etc. System integration techniques can be used in "building blocks" to implement a wide range of power electronics circuit and systems

For almost all practical DPSs, another common feature is that multiple power stages or converters are simultaneously used in a DPS. So another study subject of this dissertaion work is placed in system integration techniques, that is to say, how to achieve good system performance by integrating multiple power stages or multiple converters into a DPS.

Theoretically, changing the "DC" power distribution to "AC" power distribution can substantially mitigate the cost and complexity of DC-DPS. Then the question arised here is why such a concept has not been extensively adopted in today's power systems. This is because there are still some of the existing technical challenges with respect to the development of an applicable AC-DPS. Furthermore, unlike the DC-DPS structure with a considerable amount of available design documents, the open literature shows that the research of AC-DPS is still in conceptual stage. Significant work remains to be done ahead.

### 1.2 <u>Dissertation Outline and Major Results</u>

The dissertation is organized into three parts and divided into nine chapters, including the conclusion chapter. Part I consists of Chapters 1 and 2 and reviews current techniques of distributed power systems. Part II consists of Chapters 3, 4 and 5 that

focuses the study on front-end converters to be used in DPS. Part III consists of Chapters 6, 7 and 8 and brings investigations into system level technology, namely, system interleaving, paralleling and simplifying. Please see framework description about this dissertation coverage, as shown in Fig. 1-6.

Fig. 1-6. Framework description of dissertation coverage.

Chapter 1 presents background and motivations of this work, and provides a baseline assessment of distributed power systems.

Chapter 2 offers a review for current techniques in distributed power systems, and identifies what the issues and challenges are in this research direction. These issues include not only improving efficiency, but also increased concerns regarding the cost and complexity of power supplying system. Major potential advantages using AC bus into DPS include simplified system configuration, low cost, high efficiency, and ease of voltage and current transformation. However, several practical issues still exist, including high EMI level, difficulty to back up power, non-redundant system structure and limited post-regulation approaches, etc.

Chapter 3 addresses key issues of S<sup>2</sup> converters, and possible solutions are explored. The high bus capacitor voltage-stress generally makes most of existing S<sup>2</sup> converters impractical. The inherent reason of high DC bus voltage is in power unbalance between the input and the output. Another challenging issue in designing S<sup>2</sup> converters is wide DC bus voltage range, which makes the design of a high efficiency converter to very difficult. An optimization methodology, which is applicable to most of S<sup>2</sup> converters, has been presented and verified through both simulation and experiments on the basis of a 150 W prototype at 28 V output. From the research on target S<sup>2</sup> converters, it can be generalized that higher the turns ratio, lower DC bus voltage, wider DC bus voltage range, larger boost inductor and wider duty cycle at nominal condition result in higher efficiency at the same operation mode.

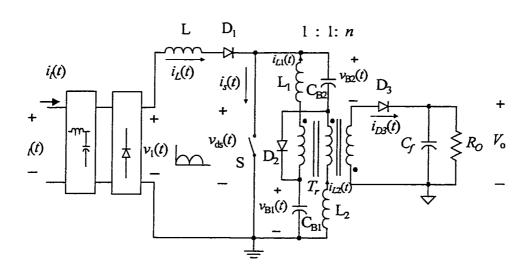

Chapter 4 first introduces a new direct power transfer (DPT) concept to implement high efficiency S<sup>2</sup> PFC converters. Then a new PFC cell with DPT feature,

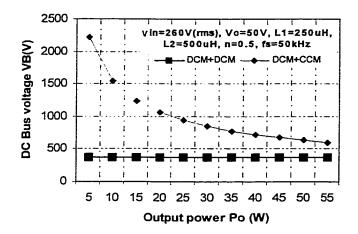

called "flybcost", is presented. It combines functions of flyback transformer and boost inductor. By having the flyboost cell operating in DCM, only a simple control will be required to achieve high power factor (greater than 0.97). The flyboost cell also significantly helps improve the efficiency above 5% over converters without using flyboost. Another important characteristic of the flyboost cell is that it will also automatically limit the DC bus voltage through a properly designed flyboost transformer and power train, which means that the converters using flyboost PFC cell can operate either DCM+DCM mode or DCM+CCM mode. As a result, the proposed converters are especially suitable for universal voltage applications with higher power handling capability than other known S² converters. By combining the flyboost cell and any family of other DC/DC conversion cell, we can obtain new family of S² PFC converters.

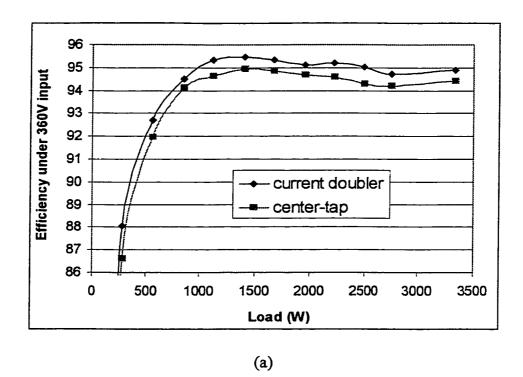

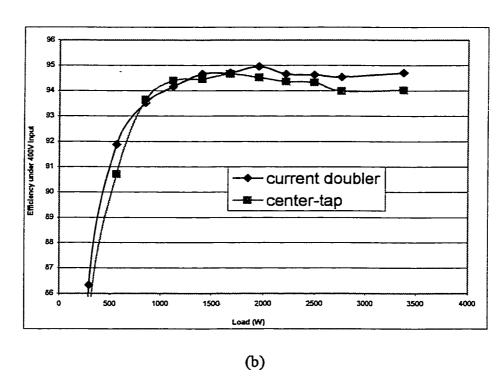

Chapter 5 presents a comparison study of high-power down-converters to be used in front-end converters of DC-DPS. In primary-side topologies for medium input voltage level such as 400Vdc, ZVT-PS-FB topology is the best choice. In primary-side topologies for high input voltage such as 800Vdc bus, generally, the topologies based on multilevel cell combination have relatively simple structure and low switch number. The topologies based on association of converters have higher magnetic volume than the structures based on multilevel cell association. For the secondary-side topologies, though the current-doubler rectifier has higher efficiency, the center-tap counterpart may have somewhat benefits in terms of cost and power density. In summary, regardless of primary-side or secondary-side topologies, the desirable approach would vary depending on which criteria is deemed most critical, such as cost, size, or efficiency. It also varies depending on specific application.

Chapter 6 investigates system integration technique using interleaving to be suited for high power topologies. According to frequency relationship between switching frequency and output ripple frequency, topologies are reclassified into secondary-side, same-frequency rectification topologies and secondary-side, double-frequency rectification topologies. It was found that the conventional interleaving techniques are actually suited only for the secondary-side same-frequency rectification topologies. For secondary-side double-frequency rectification topologies, phase-shift quantity among module control signals for N interleaved modules should be reduced to  $\pi/N$ . Typically, for the two-power stage case, a special quarter-cycle phase-shift between two control signals is required, not the previous half-cycle (180 degree) phase-shift. The characteristics achieved from the new interleaving method are as the same as those by conventional one, such as increased output ripple frequency, automatic ripple cancellation, and less EMI level, etc.

Chapter 7 details investigations into system integration technique using paralleling. Based on the classification of paralleling approaches of power modules, some new active current-sharing schemes can be obtained by proper combination of the sharing control structures and the current-programming methods. For instance, a combination of the inner regulation sharing control structure and current-programming scheme of an automatic master can be expected to achieve some special advantages. This chapter also gives a comprehensive evaluation of paralleling schemes for power supply modules. In summary, each paralleling scheme has its own merits and limitations, and each application has different criteria. The author's opinion is that there is no single best scheme suitable to all paralleling systems at the present time.

Chapter 8 explores another system integration technique-simplifying by using HF AC bus. A new DPS with multiple HF PWM buses is proposed and experimental prototype was built with a total of 210W output power for three independent outputs, i.e, 3.3V@30A, 5V@10A, and 12V@5.1A. The experimental results demonstrate that the proposed system works fine and a comparable efficiency around 80% can be obtained by this simple DPS system. In order to realize system redundancy, a new AC-DPS with trapezoidal waveform bus is presented and a conducting scheme is proposed. The scheme is expected to combine major advantages and eliminates main disadvantages coming from both of conventional sine-wave and square-wave buses.

Chapter 9 summarizes the conclusions of this work and contains suggestions for future work in related research areas.

# 2. REVIEW OF DISTRIBUTED POWER SYSTEMS (DPS)

## 2.1 Introduction

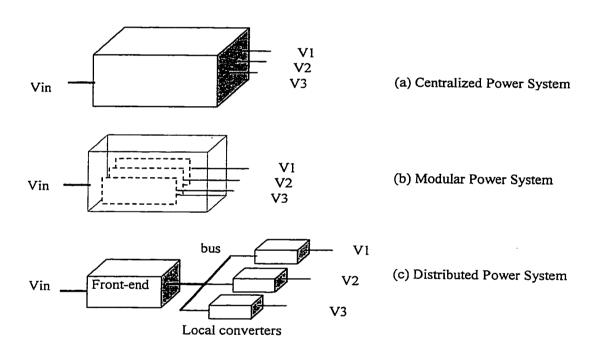

Basically, there are three different types of "power supply" architectures, i.e., centralized power system, modular power system and distributed power system (DPS), as shown in Fig. 2-1.

Fig. 2-1. Three types of "power supply" architectures.

The features of centralized power systems are:

- 1) One power conversion stage is located in one physical location in the system.

- 2) Multiple outputs are generated and bussed to the load.

The advantages of centralized power systems include concentrating all the power processing technology-including thermal management into a single box that can be designed, subcontracted, or purchased as a stand-alone item. However, this system often fails to provide adequate performance for new generations of electronic equipment.

Comparatively, modular power systems include features:

- 1) Multiple power conversion stages or converters are located in one location in the system, usually far away from the load.

- 2) Voltages and current can be combined to meet load requirements.

Modular power system is particularly suited for high power design. High power is achieved by paralleling multiple small power stages in a single package, producing the physical equivalent of a single large device. This way, power modules are easily standardized and traditional low power converter design techniques can be used. System's potentials for improved functional performance depend on both the individual power cells and their aggregation.

Distributed power systems, usually employing the modular design technique, incorporate the advantages of modular power system. But all outputs of the front-end converters will go to the intermediate bus by paralleling technology. Its basic characteristics are:

- 1) Multiple power conversion stages and/or converters can be allocated in different locations.

- 2) Intermediate voltage is bussed around the system; and

- 3) Multiple DC/DC converters located at the point-of-use are used to provided the local voltage.

While the ultimate extension of this concept is the "on-board" regulator or power supply, many other solutions for distributing power processing tasks are common. Before going to deep discussion for various issues, it is helpful to understand the motivation for considering distributed power.

# 2.2 Characteristics of Distributed Power Systems

DPS approach is gaining increased acceptance in many of advanced electronics systems due to its various attractive characteristics over traditional "power supply" architectures. The features listed below are summary of recent research work in references [7-17]. While not all of the following list potential advantages are common to all distributed power configurations, it is still a list worthy of consideration during any power system definition phase.

- 1) Thermal Management and Packaging: Modularization is a major characteristic in a modern DPS. Cellular power processing system can take advantage of a heat sink area much more effectively than can a single power module, and so lower cost thermal manipulating (air-cooling) rather than expensive liquid cooling technologies can be employed. Obviously, thermal design becomes simplified. By distributing the sources of heat generation, thermal management can often rely on conducted and radiated cooling, sometimes eliminating the need for air moving equipment, compact package can be achieved.

- 2) Module Size Reduction: Modular design in DPS may provide increased power density because lower power modules can operate at higher switching frequencies with reduced filter component size. Interleaving (phase-shifting of clock signals) of parallel

modules increases the ripple frequency, leading to reduction of the overall filter size. In addition, the small devices with less parasitic elements have considerable advantage as the switching frequency is increased.

- 3) Less EMI and Harmonics: By using interleaving technology for front-end and load converters, ripple frequency can be increased and the phases of the stages can be shifted to be beneficial to cancel ripples each other. Therefore, ripples are more easily manipulated than in a higher power, single power converter. Furthermore, aggregated outputs of parallel modules produce a low energy density spectrum with stochastically reduced harmonic components. The effects of aggregation considerably reduce both acoustic noise and EMI.

- 4) Modularity and Standardized Designs: DPS's layout is very suitable for modular system design. A centralized power supply almost by definition must be designed specifically for each new set of requirements. A goal of a modular design is the availability of standardized off-the-shelf modules or designs which could be combined in a variety of ways to meet a specific application. This has various benefits in development time and engineering costs as well as the confidence gained from using pre-qualified power components.

- 5) Redundancy and Reliability: An important characteristic of a DPS is the possibility of configuring a redundancy system using more modules than the minimum required by the load. Usually (m+r) modules are used, where m is the minimum number of modules required delivering the load power and r is the number of redundant units (usually 1), which gives the system the ability to tolerate r failures without impact. Redundancy is desirable in many high reliability applications. Moreover, the paralleling

in DPS reduces electrical and thermal stress on semiconductor devices. In addition, the higher switching frequency of parallel converters results in a higher control bandwidth, and so a parallel system can respond more quickly to abnormal and damaging system conditions, such as short circuits and overloads. These simple arguments indicate that though the number of components in a parallel structure may go up, the reliability of overall system is still increased.

- 6) Availability and Maintainability: Availability is defined as the fraction of time the converter is expected to be operational. When using a Mean Time Between Failure (MTBF) and a Mean Time To Repair (MTTR) as specifications, we will find that the availability of parallel system is much higher than in a single, high-power supply, since repairing a paralleling system involves only replacing a single standard cell [47]. In addition, a properly designed parallel configuration allows the on-line replacement (hotswapping) of defective modules. This provides the means for non-interrupting maintenance and repair.

- 7) Point-of-Load Regulation: DPS configuration facilitates placement of a power supply in close vicinity to the load for improved voltage regulation and dynamic response. If the load converter can be fabricated with sufficiently high power density, it can be placed directly on a logic board next to the load (so called "on-board application"). This characteristic is expected to use to meet challenging requirements for new generation of processors.

- 8) Flexible System Structure and Layout: Unlike centralized power system with only one power converter, DPS can realize very complicated power "supply" architecture to meet different load requirements in an electronic system. For instance, hot-plug

redundant system can be obtained by power module paralleling; by using cascading connection, the point-of-load regulation can be obtained and wide input voltage can be easily accommodated. In addition, based on the consideration of reliability, you can use multiple resources to supply power to the bus, such as utility resource, generator, and battery, etc. Also, loads could be split to obtain distributed load regulation and reduced noise coupling.

## 2.3 Basic Distributed Structures

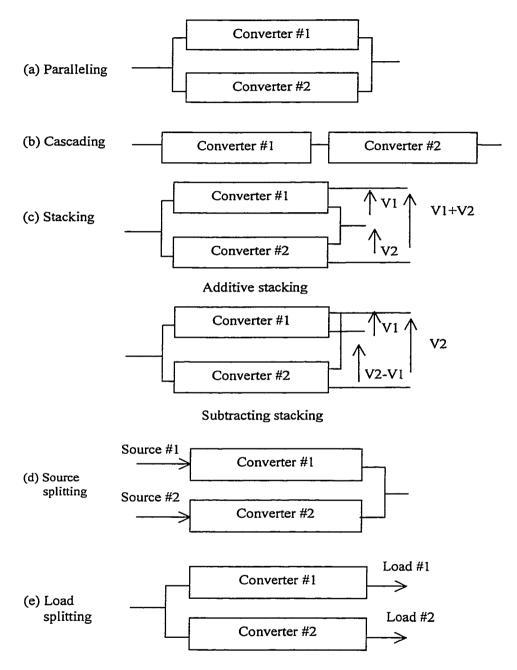

Although distributed power architectures can get quite complex and specialized, most are either derived from or combinations of five basic configurations that are shown in Fig. 2-2, including parallel, series, split source, split load and stacked modules. It should be recognized that in addition to different interconnections, each of these approaches represents a solution to a different set of objectives. A description of these architectures and their characteristics is given below:

1) Paralleling: Paralleling power modules infers a common source and load. This usually means retaining a central location where a single high power supply is replaced with a grouping of paralleled lower power modules. While power processing is distributed, it may not be distributed very far. Parallel connections are often generated by the need for standardization and redundancy rather than reducing distribution losses. With higher reliability as an objective, equalizing stress by insuring load sharing between modules is usually required. Configuring power converters for current sharing when paralleled is not a trivial problem but IC's for that purpose as well as the use of current-

mode control methods provide ready solutions. In some of literature, such a configuration is often referred to as a modular power supply system.

Fig. 2-2 Basic distribution structures (a) paralleling, (b) cascading, (c) stacking, (d) source splitting, and (e) load splitting.

2) Cascading: With a cascaded power system, an intermediate bus voltage is developed with each interconnection as shown in Fig. 2-2 (b). A typical cascaded system would be to follow a power factor correction pre-regulator with a down converter. Since each block handles the same current, it would not seem prudent to process the power twice, however there are offsetting benefits, specially in the example of two stage frontend converter, the PFC stage, in addition to removing distortion in the input line current waveform, accommodates a wide range of input line voltage variation and provides a roughly regulated intermediate voltage of 380 Vdc. Using this voltage on the bulk storage capacitor provides a very efficient means of accommodating long hold-up requirements.

The down converter then reduces the 380 Vdc to a more manageable bus voltage but, with minimum input variation, this converter can be designed very efficiently with large duty cycle and have a fast control loop for good dynamic load regulation. Additionally, with this structure, point-of-load regulation is easily obtained.

3) Stacking: Stacking of converters (usually DC/DC converters) allows combining the outputs of individual converters to obtain voltage different than the nominal voltage of each individual converter. This technique can be used to obtain non-standard output voltages using standardized converter modules. Taking high voltage application for instance, the additive stocking configuration of Fig. 2-2(c) provides output voltage equal to the sum of the nominal voltages of stocked converters. For low voltage applications, the subtractive stacking configuration provides output voltage equal to the difference between the voltages of the individual converters, thus providing an improved overall efficiency in some applications.

- 4) Source Splitting: Splitting structure shown in Fig. 2-2(d) allows the use of separate power sources to supply a common load. The typical applications are:

- a) Battery Backup: Many systems require uninterrupted power supply operation. Battery backup is the technology most commonly used to provide a temporary power supply in the case of a primary power failure;

- b) Separate Phase: Another form of power source redundancy can be achieved by supplying power to the equipment from separate utility phases. In such a case, redundancy is achieved by using separate power processing unit for each phase;

- c) Multiple Buses: An additional level of system redundancy can be achieved by using multiple power distribution buses and using a separate load converter for each bus.

- 5) Load Splitting: Load splitting is a configuration where separate load converters are used to supply different loads, as shown in Fig. 2-2(e). The most common understanding of distributed power assumes split loads where different portions of the system are each powered by their own power-processing unit. Load splitting is used based on the following considerations:

- a) Distribution power: in many large-scale systems (spacecraft, mainframe computer, etc), loads are physically distributed over substantial distances, also multiple voltage levels are required;

- b) Regulation: in systems with distributed loads, centralized power supply often cannot provide adequate regulation at the point-of-load due to the bus impedance. This problem is eliminated by using a DPS with the separate load converters located in close proximity to each load.

c) Noise decoupling: when several loads are connected to a common power distribution bus, noise interference may occur between the loads. Load splitting technique minimizes this problem by introducing more load converters with the individual filters. An additional advantage is the possibility of isolating noise-generating loads from the rest of the system.

#### 2.4 DC Distributed Power Systems

DC-DPS structures have been gaining increased popularity and are becoming mature technologies due to numerous attractions to industry. The application range from small several hundreds of watts personal computers, through 1 kW military electronic systems, to 100 kW commercial mainframe computers as well as telecom industry.

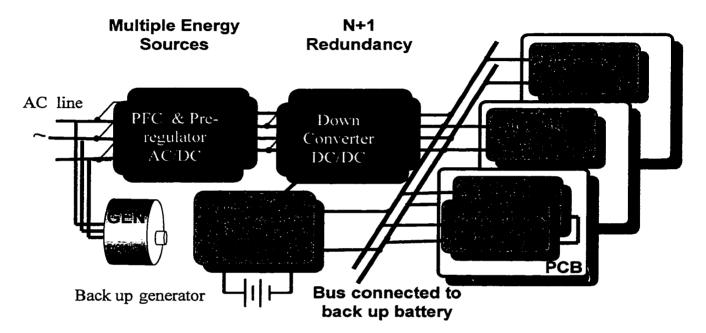

Figure 2-3 shows the mostly common implementation of a distributed power systems being used in many industry sectors such as communication system, computer system and advanced electronics equipment. The first block in foreword power path be designed for either single or three phase inputs to provide the line conditioning, power factor correction, EMI filtering, line pre-regulation, and energy storage at a high bulk voltage capacitors.

The second block in the forward path is typically a forward down converter operating with tight voltage regulation for maximum dynamic response to load variations.

A transformer is included for isolation and efficient step-down to the bus voltage.

The load converters are connected between the bus and loads either in single or in parallel to handle high load currents and insure reliability. The front-end converters and load converters all can operate in parallel to provide the required power and n+1

system redundancy. Also, DC battery backup and AC generator backup are provided to system. Therefore, the system is completely protected from any single-point failure and shut down from utility system. When utility power is shut down, the power from battery will supply DC bus, with time the backup generator will be started up while the bus voltage drop down to some preset level.

Fig. 2-3. A typical example for distributed power system.

## 2.4.1 System Design Considerations

Design of a DC bus DPS involves a number of trade-offs and choices related to the selection of distribution bus voltage, optimization of the front-end and load converters, and integration of the system. They are discussed as follows:

#### 1) Bus Voltage Selection

Selection of the bus characteristics is an important step in DPS design since it affects all power system components. The level of bus voltage and degree of bus voltage

regulation are the main characteristics of the DC bus. The major considerations in the selection of the DC-bus voltage are [7-11]:

- a) Power level: To minimize distribution losses, bus voltage must be sufficiently high to reduce distribution currents to acceptable levels. This implies higher bus voltages for higher power systems.

- b) Power losses: With the recognition that losses in the distribution network are usually determined by I<sup>2</sup>R, higher bus voltage levels with correspondingly lower currents make for a more efficient system.

- c) Safety considerations: If safety is an important consideration, the bus voltage must be within safety-defined levels. In most cases this means a bus voltage below 60 V DC. To avoid possibility of a sustained arc, a bus voltage below 32 V must be selected [8, 10]. An equally troublesome feature is that this voltage (actually any DC voltage much over 32V) may sustain an arc which makes every switch and connector a significant problem.

- d) System simplification and dynamics: An interesting counterpoint to a high voltage bus is the use of a very low voltage DC for distribution. The decision here is to accept some I<sup>2</sup>R losses in the distribution bus in return for very simple, low cost point-of-use regulators. While this demands good regulation of the bus voltage, say around 5V and a well-engineered network, the gain is that the local on-card 5V regulators can be simple, low-drop linear types. These provide excellent dynamic load regulation at a very low cost.

- e) Isolation consideration: While the transmission losses are low with high voltage, each point-of-use will require a relatively sophisticated DC/DC converter which must include a transformer (albeit at high frequency) for voltage step-down to load levels.

- f) Battery backup requirement: In many systems with a battery backup, the bus voltage

must be compatible with the battery voltage to eliminate the battery discharger unit.

In some applications (e.g., telecom) this single item determines the bus voltage level.

# 2) Regulation of Bus Voltage Range

The regulation of bus voltage has a serious impact on the power system components. A tightly regulated bus allows the optimization of the load converters for maximum efficiency. To provide a tightly regulated bus voltage, however, the front-end section must include a regulating stage, typically a DC/DC converter. As a result, the efficiency of the front-end section is reduced. Hence the bus voltage regulation must be specified based on the overall system performance after careful consideration of the involved trade-offs.

# 3) System Hold-up Time

Typically, most power systems have a requirement to maintain some intelligence for a specified period of time after removal of the input supply. Without a backup power source, this means energy storage somewhere in the power path. If only a small and defined portion of the load has the holdup requirement, it might well be provided with capacitor storage at the point of use; but more often the location of hold-up energy will be on or before the distribution bus. So it might be another important criteria that is used to define the bus voltage level.

Since energy stored in a capacitor is proportioned to the square of the voltage, it is clear that the higher the voltage, the less capacitance is required for the same energy storage.

To derive a general formula, if we assume a constant load power,  $P_L$ , and require a  $T_{hold}$  millisecond as a hold-up time during which the bus voltage is allowed to drop

from  $V_1$  to  $V_2$  by no more than 20%, the value of the required storage capacitance, C, is given by Eq. (2.1):

$$C = \frac{2P_L T_{hold}}{{V_1}^2 - {V_2}^2} \tag{2.1}$$

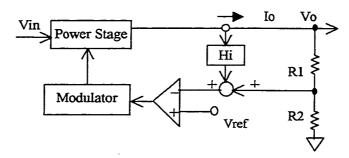

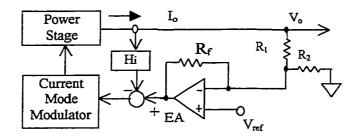

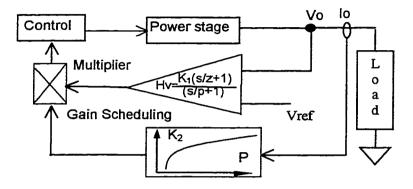

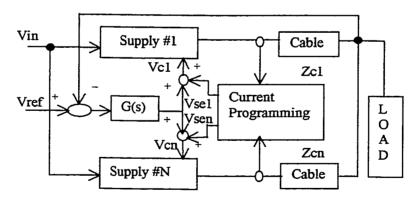

#### 4) System Cost