Novel voltage regulator controllers and transient compensators for powering microprocessors

Luo, Jia *ProQuest Dissertations and Theses;* 2004; ProQuest Dissertations & Theses (PQDT) pg. n/a

# NOVEL VOLTAGE REGULATOR CONTROLLERS AND TRANSIENT COMPENSATORS FOR POWERING MICROPROCESSORS

By

# JIA LUO B.S. Hangzhou Institute of Applied Technology, 1993 M.S. Zhejiang University, 1999

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer science at the University of Central Florida Orlando, Florida

Fall Term 2003

Major professor: Issa Batarseh

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 3134682

Copyright 2004 by Luo, Jia

All rights reserved.

### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

### UMI Microform 3134682

Copyright 2004 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## ABSTRACT

This dissertation provides advanced solutions related to the power management of Intel's microprocessors. The main solutions presented here focus on the controller design and extremely fast transient compensation.

The analog controller described in this dissertation is a proportional ON-TIME system for portable usage. No pre-stage is needed for powering the voltage regulator to achieve better efficiency. It could be considered as improved hysteretic control with controllable "ON-TIME" duration. It is also very easy to achieve current sharing.

The digital controller introduced here is a current senseless system. Based on adaptive control theorem, it observes the instantaneous phase currents and load resistance. This is the basis of a novel peak current control method for achieving current sharing. Combined with hysteretic control, a simple and fast controller is built for next generation of voltage regulator.

An extremely fast transient compensator is presented for the next generation of high current slew rate microprocessors. It dramatically reduces the decoupling capacitors mounted around the CPU by compensating the parasitic resistance and inductance at traces, connections and sockets. For easy understanding, it can be considered a discrete voltage regulator which only works at high di/dt transient and behaves as a linear regulator.

To My Parents and Husband

# ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Dr. Issa Batarseh, for his guidance, inspiration and support in these years. I would not have been able to complete my research without his extensive knowledge and creative thoughts. Through his enthusiasm and personality, he also gained my most sincere admiration.

I also thank many of my collegues at UCF, Dr. Shiguo Luo, Dr. Wei Gu, and Mr. Jaber Abu Qahouq for many enlightening discussions; Their invaluable suggestions were so helpful to my research.

My experience at UCF has been a great period in my life. I am grateful to have the chance to combine enjoyable education and productive research atmosphere through the dynamic group at UCF. I wish to thank my fellow researchers, Dr. Hong Mao, Mr. Khalid Krustom, Mr. Songquan Deng, Dr. Weihong Qiu, Mr. Nattorn Pongratananukul, Dr. WenKai Wu, and Mr. Joy Mazumdar for their help and cooperation.

And I would like to express my deep appreciation to Ms. Elizabeth Plaisted and Mr. Curtis Brown for their invaluable editing of my dissertation.

Finally, my heartfelt appreciation goes to my parents and my husband for their love and support.

# **TABLE OF CONTENTS**

| LIST OF TABLES viii                                                       |

|---------------------------------------------------------------------------|

| LIST OF FIGURESix                                                         |

| CHAPTER ONE INTRODUCTION1                                                 |

| 1.1 Developing Tendency of Voltage Regulator Modules (VRMs) for New       |

| Generation of Microprocessors1                                            |

| 1.2 Technical Challenges of Low-Voltage High-Current Fast-Transient VRMs3 |

| 1.3. Contributions of this Dissertation5                                  |

| References10                                                              |

| CHAPTER TWO TECHNICAL REVIEW13                                            |

| 2.1 Review of multiphase VRMs13                                           |

| 2.1.1 Interleaved (Multiphase) Technique on a Buck Converter14            |

| 2.1.2 Single-Phase Hysteretic Voltage-Mode Control17                      |

| 2.2 Review of Transient Improvement Circuits                              |

| 2.3 Review of ON-TIME Control                                             |

| References                                                                |

| CHAPTER THREE ACTIVE CURRENT COMPENSATION FOR LOW-                        |

| VOLTAGE HIGH CURRENT FAST TRANSIENT VRMS                                  |

| 3.1 Introduction                                                          |

| 3.2 Transient Response Delay in Fast Current Slew Rate System             |

| 3.3 Presented Active Transient Current Compensator                        |

| 3.3.1 Voltage Monitor                                             |

|-------------------------------------------------------------------|

| 3.3.2 Active Transient Current Compensator                        |

| 3.3.3 Complete Schematics for the Simulation44                    |

| 3.4 Simulation Results                                            |

| 3.5 Summary                                                       |

| References                                                        |

| CHAPTER FOUR DIGITAL TIME-VARYING CURRENT OBSERVER AND            |

| FEEDBACK CONTROL FOR MULTIPHASE VRMS59                            |

| 4.1 Introduction                                                  |

| 4.2 Observer for PWM and hysteretic control                       |

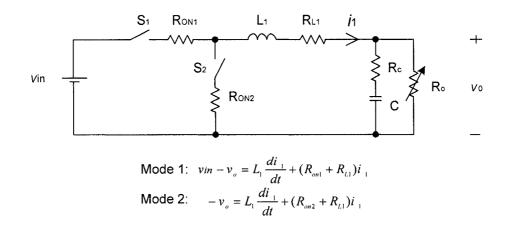

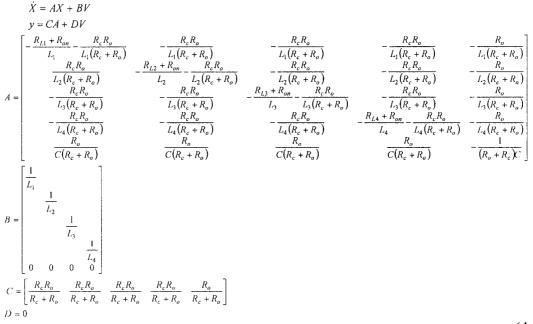

| 4.2.1 State Space Model for Power Stage61                         |

| 4.2.2 Observability                                               |

| 4.2.3 Adaptive Controller                                         |

| 4.2.4 Current Observer Design                                     |

| 4.3 Observer for PWM control72                                    |

| 4.3.1 State Space Model for Power Stage72                         |

| 4.3.2 Design of Current Observer with Parameter Estimator         |

| 4.4 Design of Feedback Controller                                 |

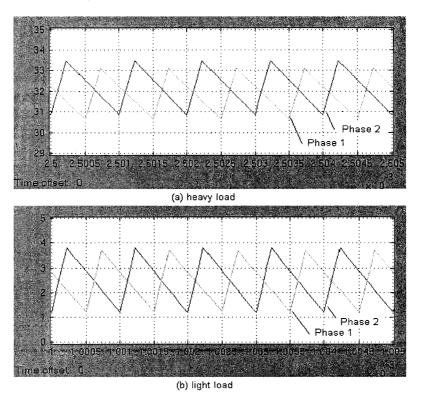

| 4.5 MATLAB/SIMULINK Simulation Result and Experiment Verification |

| for Observer                                                      |

| 4.6 Summary90                                                     |

| References                                                        |

,

| CONTROL WITH CURRENT SHARING FOR WIDE RANGE INPUT VOLTAGE             |

|-----------------------------------------------------------------------|

| VARIATION VRMS                                                        |

| 5.1 Introduction94                                                    |

| 5.2 Control Method of the Proportional ON-TIME Voltage Hysteretic     |

| Control96                                                             |

| 5.3 Simulation Results for Proportional ON-TIME Voltage Hysteretic    |

| Control104                                                            |

| 5.4 Current Sharing108                                                |

| 5.5 Simulation results for Current Sharing113                         |

| 5.6 Block Diagram of the Proportional ON-TIME Hysteretic Control with |

| Current Sharing113                                                    |

| 5.7 Experiment Results                                                |

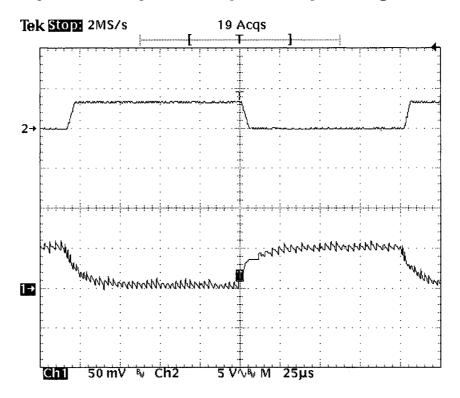

| 5.7.1 Single Phase Experiment Results115                              |

| 5.7.2 Frequency Comparison between ON-TIME Control and Hysteretic     |

| Control115                                                            |

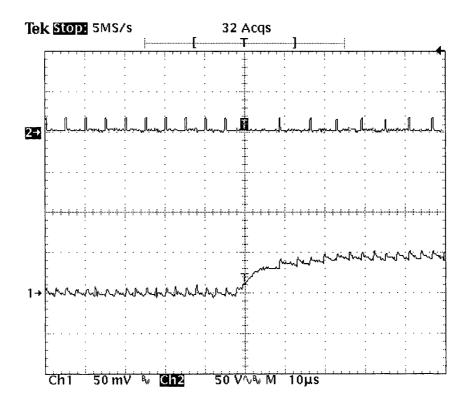

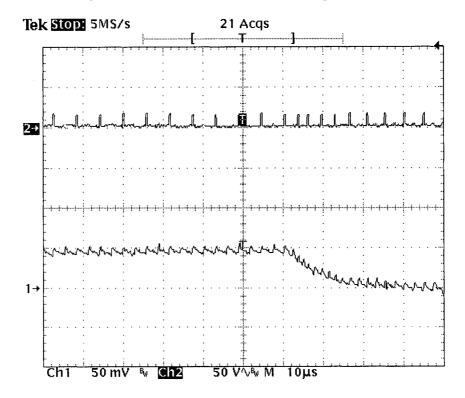

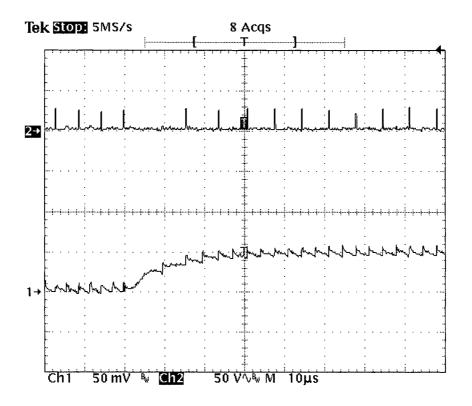

| 5.7.3. Two Phase Experiment Results116                                |

| 5.8 Summary117                                                        |

| References128                                                         |

| CHAPTER SIX CONCLUSION130                                             |

| APPENDIX A COMPLETE DIGITAL OBSERVER                                  |

| APPENDIX B MATLAB PROGRAM FOR THE OBSERVER                            |

# CHAPTER FIVE PROPORTIONAL ON TIME VOLTAGE HYSTERETIC

# LIST OF TABLES

| Table 1.1: Current and Voltage Specifications for Pentium Microprocessors         7 |

|-------------------------------------------------------------------------------------|

| Table 1.2: Voltage and Current Specifications for Present Pentium 4 Processors      |

| Table 1.3: VCC Static and Transient Tolerance                                       |

| Table 1.4: International Technology Roadmap for Semiconductors (ITRS-1999)9         |

| Table 3.1: Device Specification of 0.8 micro CMOS Process    45                     |

| Table 3.2: Compensation Result when Microprocessor Operates from Sleep Mode to      |

| Active Mode @ 2A/ns Current Slew Rate and $IV V_{cc}$ ( $C_m = 100n$ )              |

| Table 3.3: Compensation result when Microprocessor Operates within Active Mode @    |

| $0.5A/ns$ Current Slew Rate and $1V V_{cc} (C_m = 100n)$                            |

| Table 3.4: Compensation Responses versus Capacitor $C_m$                            |

| Table 3.5: Critical response value @ $C_m = 60nF$                                   |

| Table 4.1: Parameter List                                                           |

| Table 5-1: Simulation Parameter Values    103                                       |

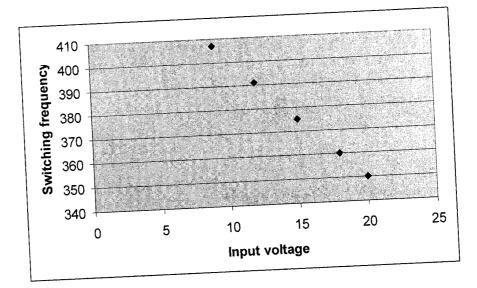

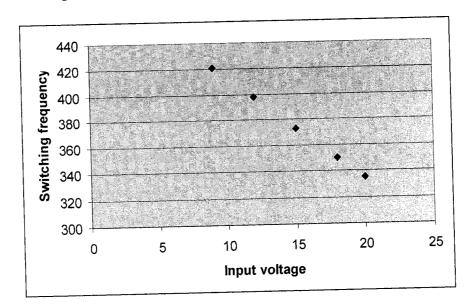

| Table 5.2: ON-TIME Control Input Voltage vs. Switching Frequency    122             |

| Table 5.3: Input Voltage vs. Switching Frequency    122                             |

| Table 5.4: Voltage Hysteretic Control Input Voltage vs. Average Switching Frequency |

|                                                                                     |

# **LIST OF FIGURES**

| Figure 1-1: VCC static and transient tolerance                                               |

|----------------------------------------------------------------------------------------------|

| Figure 2-1: Multiphase buck converters and its output inductor currents                      |

| Figure 2-2: Voltage hysteretic control 16                                                    |

| Figure 2-3: Fast transient compensation circuit                                              |

| Figure 2-4: Fast transient compensation type                                                 |

| Figure 2-5: Comparisons of PWM, hysteretic and ON-TIME control                               |

| Figure 2-6: Constant ON-TIME control                                                         |

| Figure 2-7: Conceptual circuit diagram for duty ratio model                                  |

| Figure 3-1: Power delivery model for transient response for Intel Pentium 4 processor 34     |

| Figure 3-2: $V_{cc}$ of processor when $I_{cpu}$ changes from 5A to 56A @ $di/dt=350A/us$ 35 |

| Figure 3-3: $V_{cc}$ of microprocessor @ $I_{cpu,max}=100A$ and $di/dt=2000A/us$             |

| Figure 3-4: The comparison of power delivery models                                          |

| Figure 3-5: Voltage monitor and output                                                       |

| Figure 3-6: Active transient current compensator                                             |

| Figure 3-7: Schematics                                                                       |

| Figure 3-8: Pin configuration of the voltage monitor                                         |

| Figure 3-9: Typical application circuit of voltage monitor                                   |

| Figure 3-10: Voltage monitor layout and application circuit                                  |

| Figure 3-11: Simulation results after transient current compensation                         |

| Figure 3-12: Voltage monitor output signal                                                   |

| Figure 3-13: Compensation for second spike during transient                  | . 55 |

|------------------------------------------------------------------------------|------|

| Figure 4-1: Multiphase VRM buck converter                                    | . 64 |

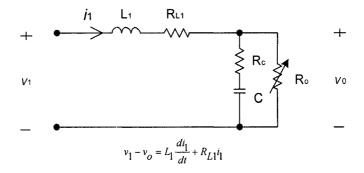

| Figure 4-2: State space equation for phase one                               | . 64 |

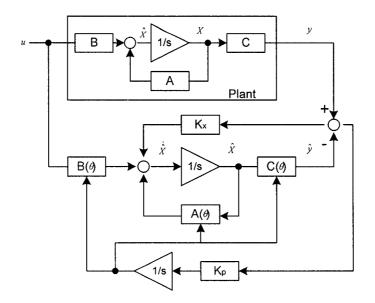

| Figure 4-3: Adaptive controller for state observing and parameter estimating | . 69 |

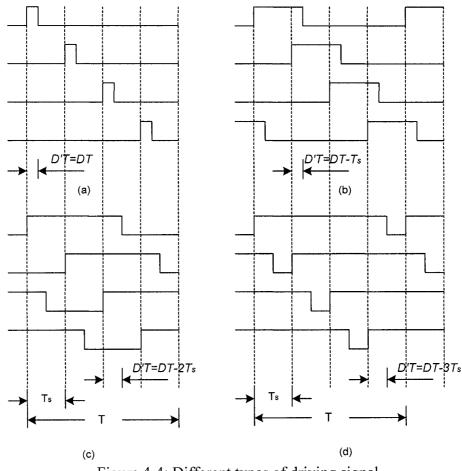

| Figure 4-4: Different types of driving signal                                | . 73 |

| Figure 4-5: State space equation for phase one                               | . 73 |

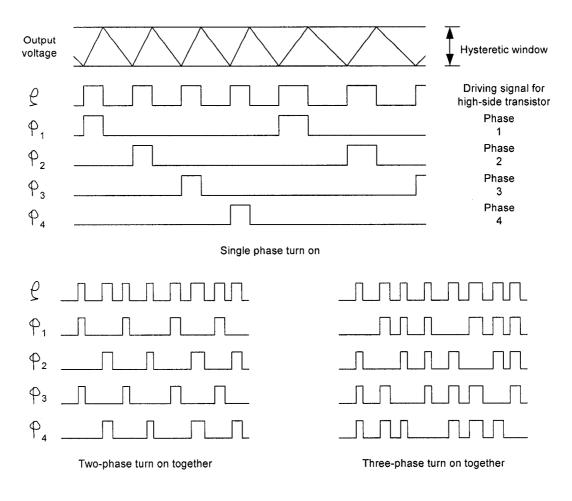

| Figure 4-6: Driving signal for each phase                                    | . 81 |

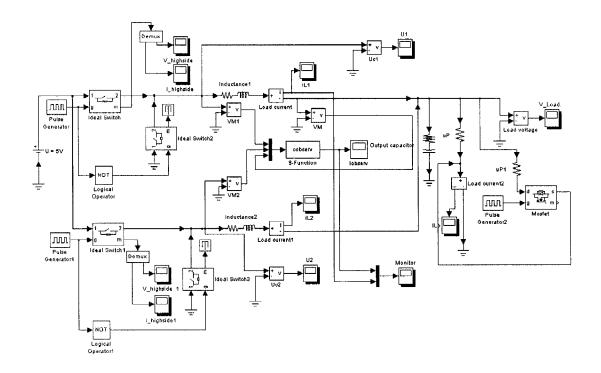

| Figure 4-7: Schematics                                                       | . 86 |

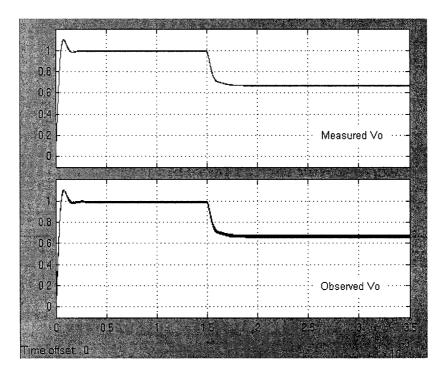

| Figure 4-8: The waveforms of measured and observed output voltage $V_o$      | . 87 |

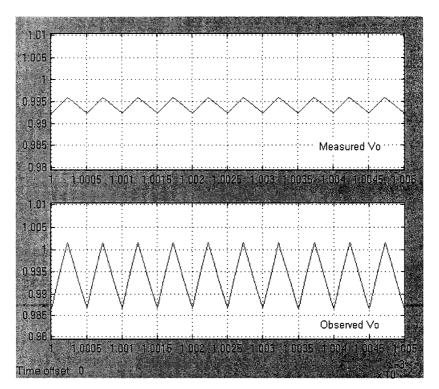

| Figure 4-9: The waveform of Zoomed V <sub>o</sub>                            | . 87 |

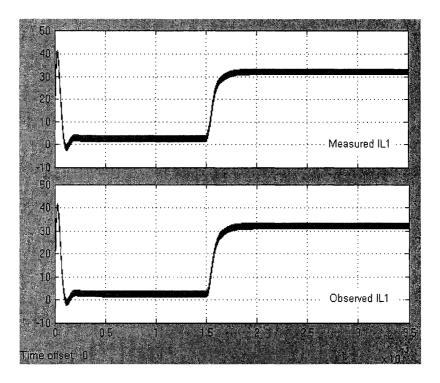

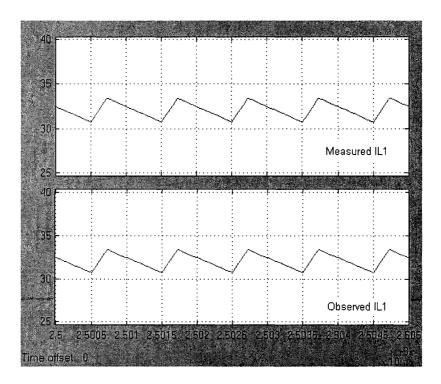

| Figure 4-10: The waveforms of measured and observed phase current <i>IL1</i> | . 88 |

| Figure 4-11: The waveforms of Zoomed <i>IL1</i>                              | . 88 |

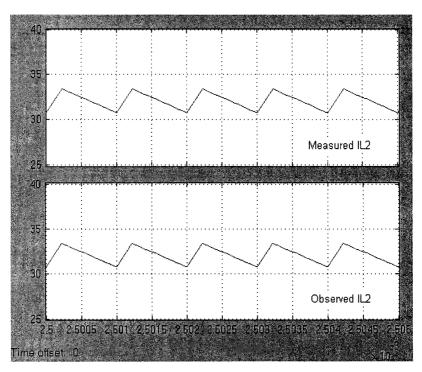

| Figure 4-12: The waveforms of zoomed <i>IL2</i>                              | . 89 |

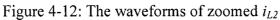

| Figure 4-13: The waveforms of imbalanced phase inductors                     | . 89 |

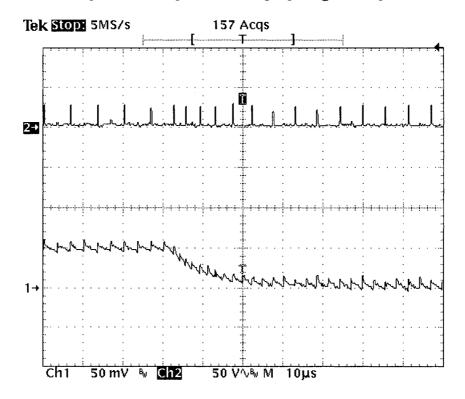

| Figure 4-14: Experiment results of phase currents                            | . 91 |

| Figure 4-15: Experiment results of observed phase current                    | . 91 |

| Figure 5-1: Low output voltage limit setting circuit                         | . 99 |

| Figure 5-2: ON-TIME circuit                                                  | . 99 |

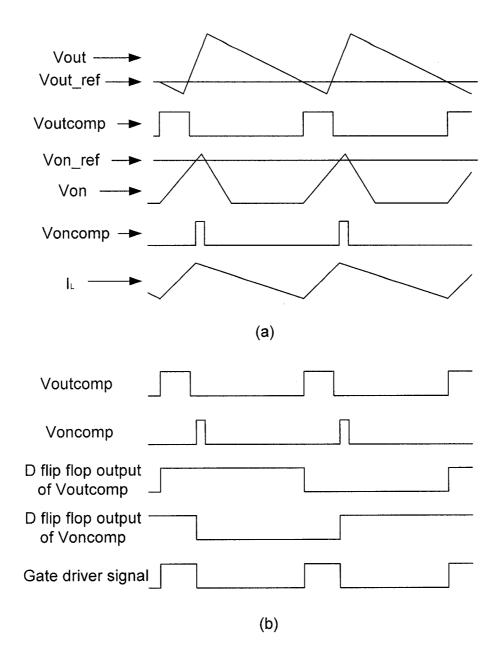

| Figure 5-3: Proportional on time controller timing                           | 100  |

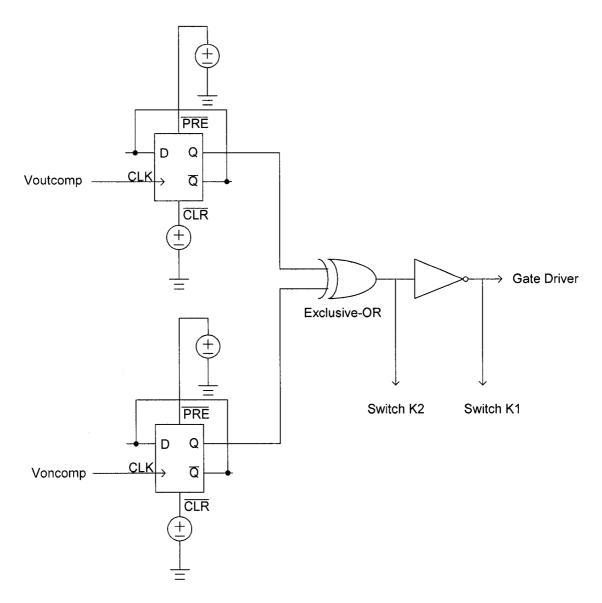

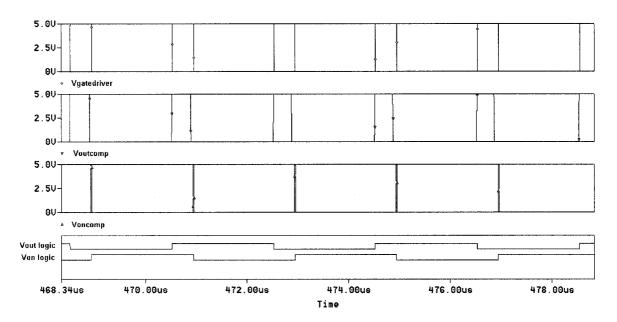

| Figure 5-4: On time control logic schematics                                 | 101  |

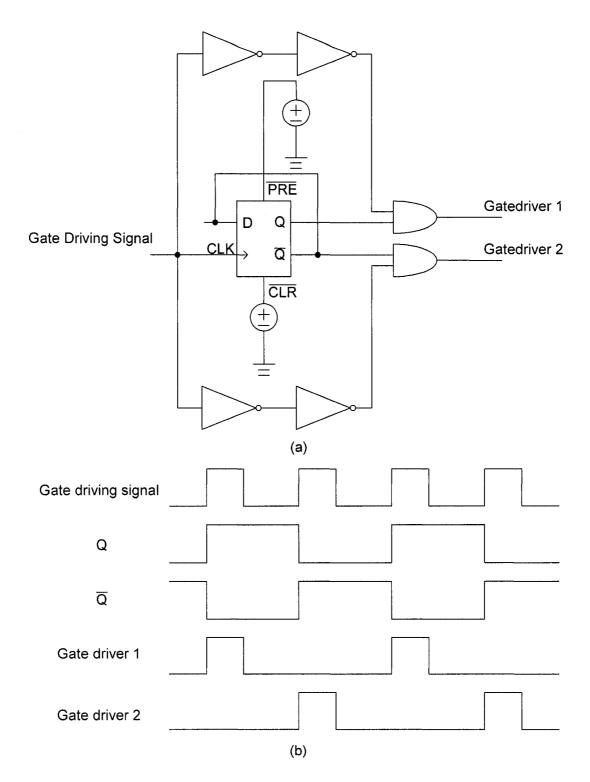

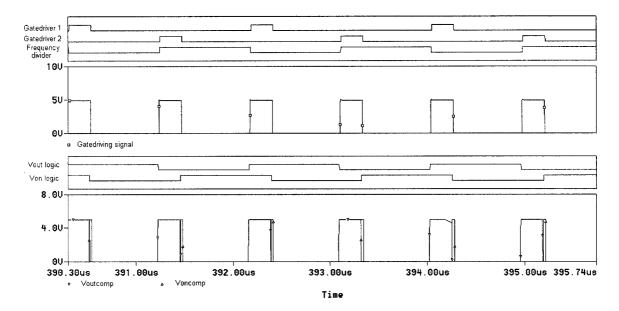

| Figure 5-5: Gate driver signals and their logic                              | 102  |

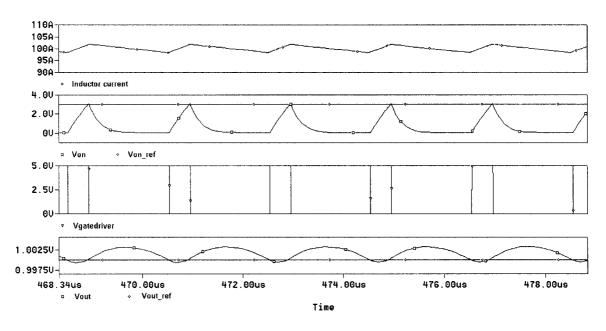

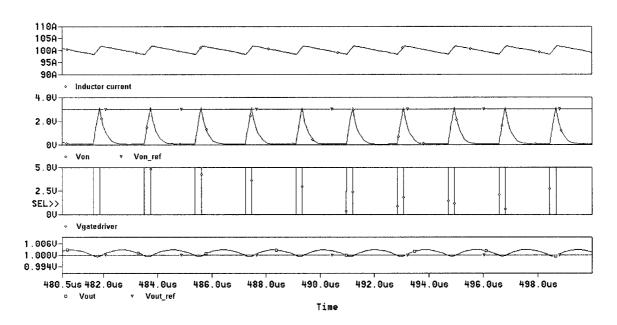

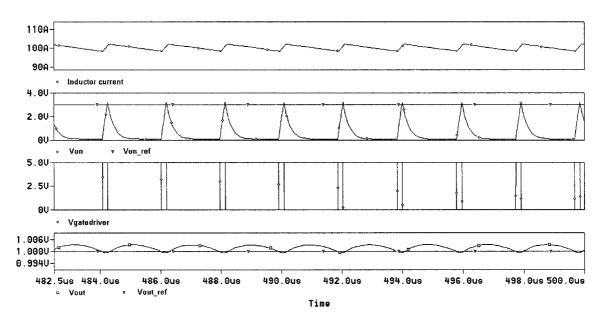

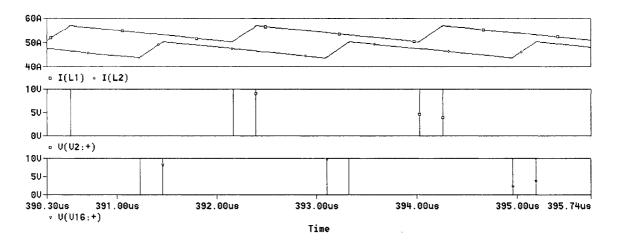

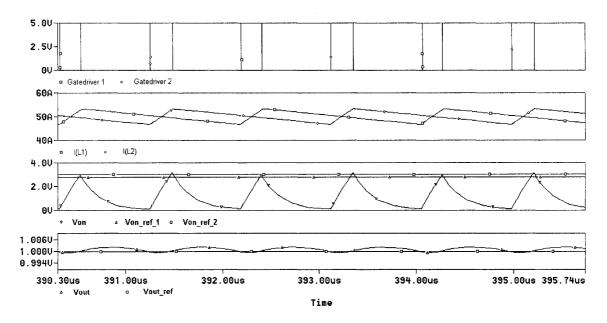

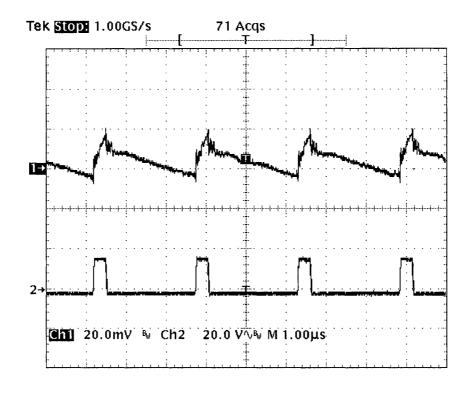

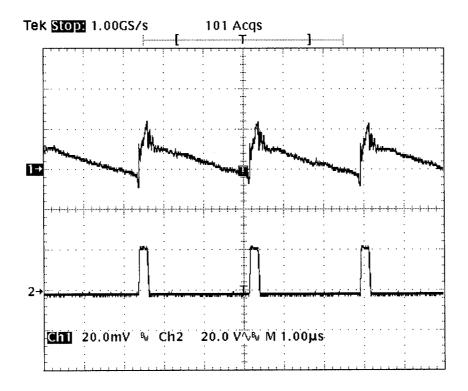

| Figure 5-6: Single phase @ 9V input                                          | 106  |

| Figure 5-7: Single phase @ 15V input                                         | 106  |

| Figure 5-8: Single phase @ 20V input 10                                                                                   | 7           |

|---------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 5-9: Gate driving signal @ 9V input 10                                                                             | 7           |

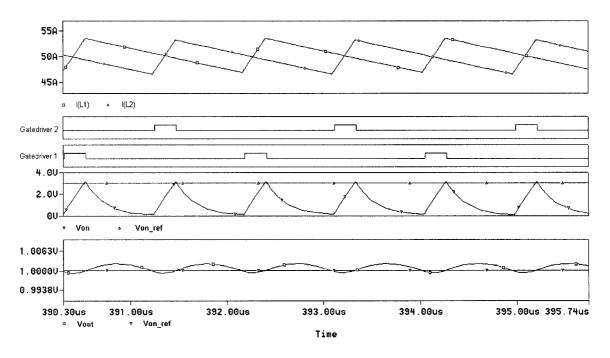

| Figure 5-10: Two-phase VRM @ 15V input 109                                                                                | 9           |

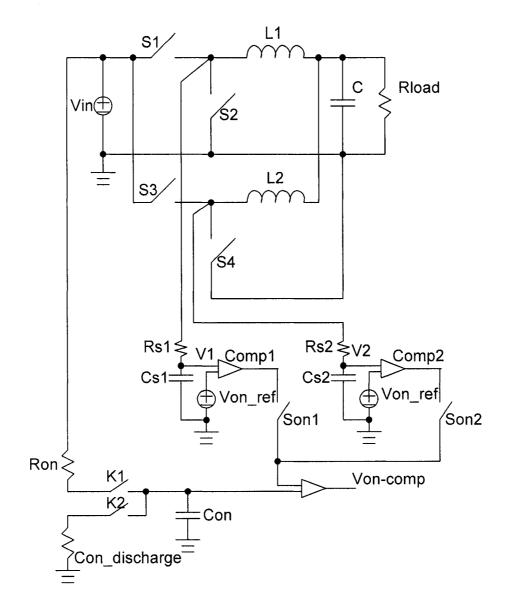

| Figure 5-11: Control logic of two-phase VRM 10                                                                            | 9           |

| Figure 5-12: Current sharing control 11                                                                                   | 0           |

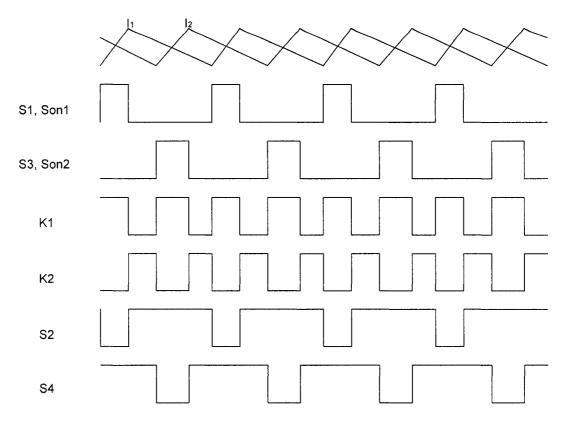

| Figure 5-13: Current sharing switch timing                                                                                | 1           |

| Figure 5-14: Two-phase VRM phase current without current sharing 112                                                      | 2           |

| Figure 5-15: Two-phase VRM phase current with current sharing                                                             | 2           |

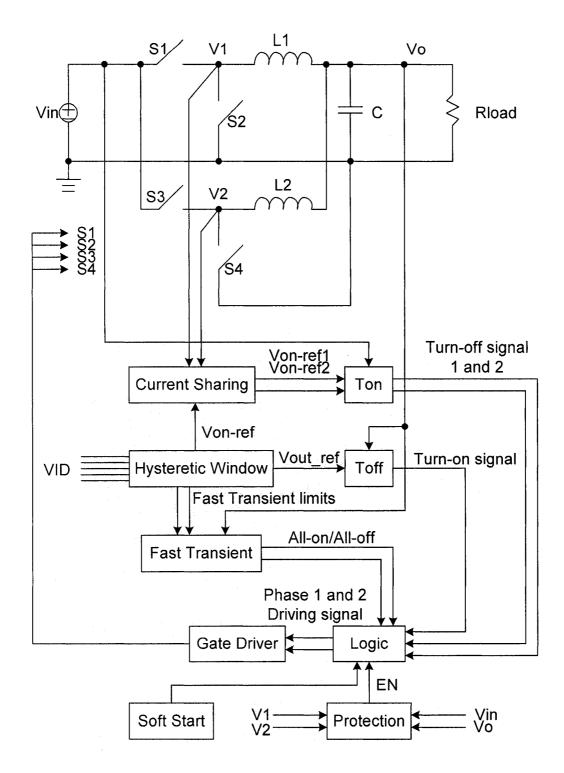

| Figure 5-16: Block diagram11                                                                                              | 8           |

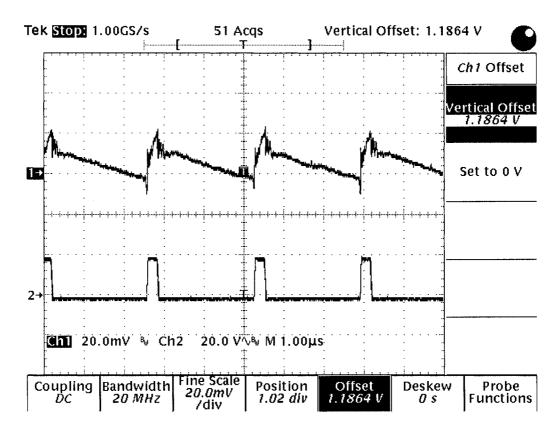

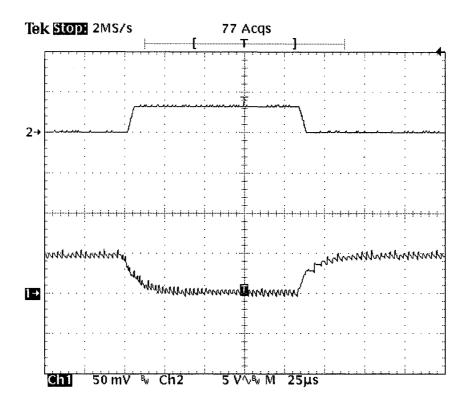

| Figure 5-17: Waveforms of Single-phase 15V input 1.2V output @ 10A output current                                         |             |

|                                                                                                                           | 9           |

| Figure 5-18: Single-phase 9V/1.2V 10A output voltage waveform                                                             | 0           |

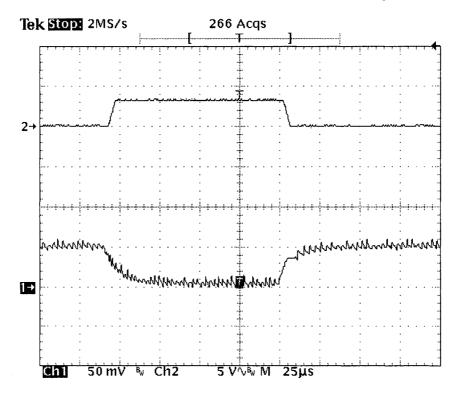

| Figure 5-19: Single-phase 12V/1.2V 10A output voltage waveform                                                            | 0           |

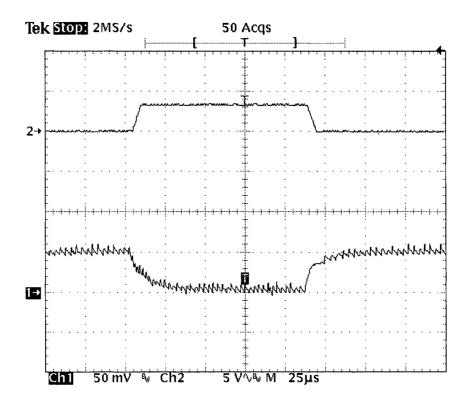

| Figure 5-20: Single-phase 18V/1.2V 10A output voltage waveform                                                            | 8           |

| Figure 5-21: Single-phase 20V/1.2V 10A output voltage waveform                                                            | 8           |

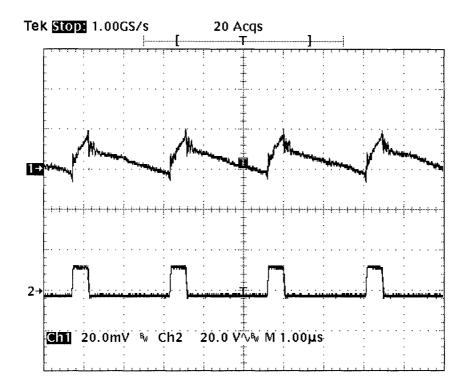

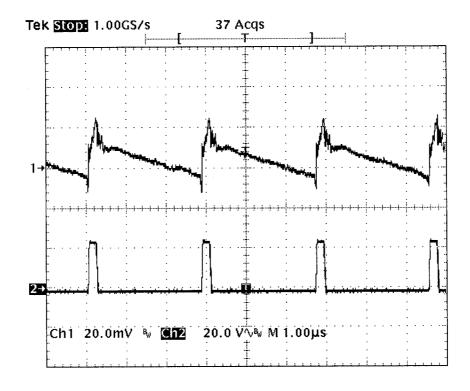

| Figure 5-22: Two phases 10V input 1.2V output VRM @ 20A/8A 12                                                             | 4           |

| Figure 5-23: Two phases 15V input 1.2V output VRM @ 20A/8A 12                                                             | 4           |

|                                                                                                                           |             |

| Figure 5-24: Two phases 20V input 1.2V output VRM @ 20A/8A 12                                                             | 5           |

| Figure 5-24: Two phases 20V input 1.2V output VRM @ 20A/8A                                                                |             |

|                                                                                                                           | 5           |

| Figure 5-25: Two phases 25V input 1.2V output VRM @ 20A/8A 12                                                             | 5<br>6      |

| Figure 5-25: Two phases 25V input 1.2V output VRM @ 20A/8A 12<br>Figure 5-26: High-side driving signal @ <i>10V</i> input | 5<br>6<br>6 |

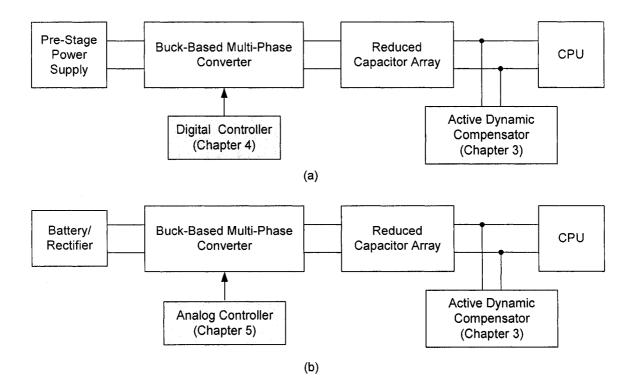

| Figure 6-1: Advanced solutions for powering microprocessors | 132 |

|-------------------------------------------------------------|-----|

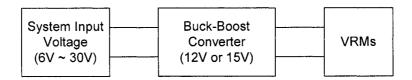

| Figure 6-2: Two stage solution                              | 132 |

# CHAPTER ONE

## INTRODUCTION

# 1.1 Developing Tendency of Voltage Regulator Modules (VRMs) for New Generation of Microprocessors

Recent microprocessor technology enables the new generation processors to operate above 3GHz. The operation frequency will be further boosted in the near future. Due to the thermal problems, the new generation of chips is developed based on low-voltage operation. Furthermore, the semiconductor companies are targeting chips running below 1V for higher speeds. Meanwhile, the operating current for present Pentium 4 microprocessors already reaches the 70A level and it will be larger than 100A in the coming years.

The Pentium<sup>®</sup> family [1-6] allows the processor to operate in active mode and sleep mode (including three states, i.e., Stop-Grant, Sleep, and Deep Sleep) to reduce unnecessary energy consumption and thermal generation. For example, the microprocessor draws a high current (70A) from the power supply known as Voltage Regulator Modules (VRMs) during the "active-mode" state and low current (5A ~10A) when it switches to the "sleepmode" state. The largest current slew rates during state shift might reach 500A/µs level for Pentium 4 processors. Thanks to the contributions of huge decoupling capacitors mounted beside the processor [3], the current slew rate at the VRM end is reduced dramatically to 1/10 of the processor's VCC output end, i.e.  $50A/\mu s$  level when the microprocessor switches from one state to the other [1-6]. However, it still causes voltage spikes at the VRMs' output end and processors' VCC end. Based on the design guidelines, these transient spikes must be limited to a certain maximum value such as 1%-2%. Obviously, as the processors' operating voltage becomes lower, the allowed voltage deviation during the load transient becomes tighter.

What makes the challenge even more difficult is that the current drawn from the VRM by the microprocessor is unknown and time varying, since it depends on the operation task of the microprocessor. Furthermore, the VRM itself is a nonlinear system with switching elements, inductors and capacitors. All of these make it complicated to design a high performance controller [6-18].

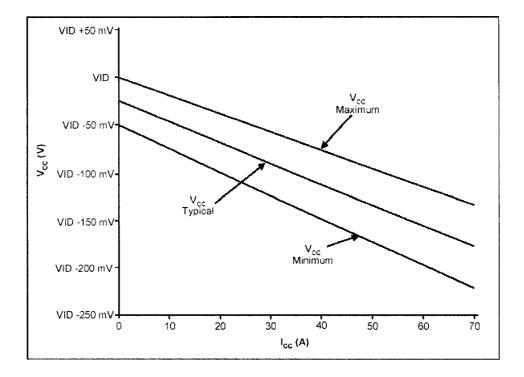

Tables 1.1 shows the current and voltage specifications for Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> 4 processors, respectively to show the developing tendency [1-6]. Table 1.2, Table 1.3 and Figure 1-1 give the operating voltage and current requirement for present Pentium 4 2.0GHz ~ 3GHz processors. Table 1.4 shows an estimated current and voltage roadmap for future generation. It shows how low the required voltage will be and how large the required current will be [1-6].

### 1.2 Technical Challenges of Low-Voltage High-Current Fast-Transient VRMs

Unfortunately, it is difficult to provide a satisfactory solution for the traditional power supply. Power management for the new and future generation computer systems is challenging mainly due to the following issues:

- The current drawn from the VRM increases dramatically, resulting in significant power loss in components, causing difficulties in the thermal management.

- 2) Large load current changes and high current slew rate together with highly restricted transient voltage tolerance severely challenges the dynamic response performance of the VRM.

- 3) Noise and EMI immunity becomes dominant in such a low voltage system.

- 4) Lower static supply voltage tolerance 2% or less for future generation.

- 5) Because the output current of VRM is extremely high, the distinction between normal operation and short circuit operation becomes vague, resulting in difficulty in short circuit protection.

- 6) Due to the requirement of the high efficiency, current senseless topology is a demand for the controller.

3

7) Smaller size and lower cost are required for a high-integrated system board.

Hence, the "Driving Forces" for the future VRMs includes: reduced voltages, increased currents, faster response, lower output voltage deviation, reduced cost, increased reliability, increased efficiency, increased power density, improved electromagnetic compatibility (EMC), and improved packaging (Mainly, thermal management and surface-mount components).

In order to address the above technical challenges, the following research issues need to be emphasized:

- Development of advanced control schemes, which should be fast and smart enough to react to the fast load change. Advanced Digital Signal Processing (DSP) controlling schemes are the strongest candidates for this purpose.

- 2) Development of advanced power conversion circuit topologies with optimized power system configurations and high efficiency to meet the even increase stringent specifications. This option seems to be somewhat limited since the most practical topologies until now are buck converter derived.

- Development of advanced power devices, including high current and high frequency, low loss and high density magnetic components and low ESR and low ESL capacitors.

- 4) Development of advanced packaging techniques.

### 1.3 Contributions of this Dissertation

This dissertation introduces three advanced solutions for powering Pentium series microprocessors:

- 1) Active current compensation for compensating voltage drops during high current slew rate load changes. This idea not only solves the problem of transient voltage spikes it also dramatically reduces the size of the decoupling capacitors on the system board. Therefore, it provides a fast transient, small voltage deviation, small size (compared with tens of capacitors), and low cost solution (compared with tens of capacitors).

- 2) Time-varying current observer with digital feedback control for achieving current senseless control and realizing current sharing. This idea uses adaptive control method to estimate the time-varying load resistance and calculates instantaneous phase currents and load current. Based on those values, the digital controller can execute a novel peak current control as well as voltage hysteretic control for

multiphase VRMs. Therefore, it provides a low noise, low EMI, high efficiency and high integration solution.

3) Multiphase proportional ON-TIME control for wide input voltage systems like portable usage. This improves the defect of voltage hysteretic control in portable systems that the frequency varies dramatically when input voltage changes. The varying ON-TIME window based on the average phase current provides better current sharing performance compared with hysteretic control. Therefore, it provides a fast transient, good current sharing and low EMI solution for portable usage.

|                          | $V_{cc}(V)$ |       |       | $I_{cc}(A)$ |      |  |

|--------------------------|-------------|-------|-------|-------------|------|--|

|                          | 2.8         |       |       | (MHz)       | Max  |  |

| Pentium <sup>®</sup> II  |             |       |       | 233         | 11.8 |  |

|                          |             | 2.0   |       | 266         | 12.7 |  |

|                          |             |       |       | 300         | 14.2 |  |

|                          | (MI         | Hz)   |       | Max         |      |  |

|                          | 600/600B    |       |       | 17.8        |      |  |

| Pentium <sup>®</sup> III | 550         |       | 2.00  | 17.0        |      |  |

| r chuuni m               | 533B        |       | 2.00  | 16.7        |      |  |

|                          | 500         |       |       | 16.1        |      |  |

|                          | 450         |       |       | 14.5        |      |  |

| (GHz) Min                |             | Max   | Max   |             |      |  |

| Pentium <sup>®</sup> 4   | 1.4         | 1.560 |       | 40.6        |      |  |

| renuum 4                 | 1.5         | 1.555 | 1.700 | 43.0        |      |  |

|                          | 1.7         | 1.530 |       | 52.7        |      |  |

Table 1.1: Current and Voltage Specifications for Pentium Microprocessors

Figure 1-1: VCC static and transient tolerance

| Symbol       | Parameter                      | Min   | Тур        | Max   | Unit |

|--------------|--------------------------------|-------|------------|-------|------|

|              | VCC for CPU at VID=1.476       |       |            |       |      |

|              | 2.4GHz                         | 1.285 |            | 1.375 |      |

|              | 2.6GHz                         | 1.280 |            | 1.370 |      |

|              | 2.8GHz                         | 1.268 |            | 1.368 |      |

|              | 3GHz                           | 1.265 |            | 1.350 |      |

|              | 3.2GHz                         | 1.260 |            | 1.345 |      |

|              | VCC for CPU at VID=1.600       |       |            |       |      |

|              | 2.4GHz                         | 1.320 |            | 1.400 |      |

|              | 2.6GHz                         | 1.315 | Refer to   | 1.395 |      |

| VCC          | 2.8GHz                         | 1.313 | Table 1.3  | 1.394 |      |

| (800MHz FSB) | 3GHz                           | 1.290 | and        | 1.375 | V    |

|              | 3.2GHz                         | 1.285 | Figure 1-1 | 1.370 |      |

|              | VCC for CPU at VID=1.625       |       | riguie 1-1 |       |      |

|              | 2.4GHz                         | 1.345 |            | 1.425 |      |

|              | 2.6GHz                         | 1.340 |            | 1.420 |      |

|              | 2.8GHz                         | 1.338 |            | 1.418 |      |

|              | 3GHz                           | 1.315 | 1          | 1.400 | 1    |

|              | 3.2GHz                         | 1.310 |            | 1.395 |      |

|              | VCC for CPU at VID=1.650       |       |            |       |      |

|              | 3GHz                           | 1.340 |            | 1.425 |      |

|              | 3.2GHz                         | 1.335 |            | 1.420 |      |

|              | ICC for CPU with multiple VIDs |       |            |       |      |

|              | 2.4GHz                         |       |            | 52.4  |      |

| ICC          | 2.6GHz                         |       |            | 55.5  | Α    |

| (800MHz FSB) | 2.8GHz                         |       |            | 55.8  |      |

|              | 3GHz                           |       |            | 64.8  |      |

|              | 3.2GHz                         |       |            | 67.4  |      |

Table 1.2: Voltage and Current Specifications for Present Pentium 4 Processors

| ICC | Voltage deviation from VID Setting (V) |         |         |  |  |  |  |

|-----|----------------------------------------|---------|---------|--|--|--|--|

| (A) | Maximum                                | Typical | Minimum |  |  |  |  |

| 0   | 0.000                                  | -0.025  | -0.050  |  |  |  |  |

| 5   | -0.010                                 | -0.036  | -0.062  |  |  |  |  |

| 10  | -0.019                                 | -0.047  | -0.075  |  |  |  |  |

| 15  | -0.028                                 | -0.058  | -0.087  |  |  |  |  |

| 20  | -0.038                                 | -0.069  | -0.099  |  |  |  |  |

| 25  | -0.048                                 | -0.079  | -0.111  |  |  |  |  |

| 30  | -0.057                                 | -0.090  | -0.124  |  |  |  |  |

| 35  | -0.067                                 | -0.101  | -0.136  |  |  |  |  |

| 40  | -0.076                                 | -0.112  | -0.148  |  |  |  |  |

| 45  | -0.085                                 | -0.123  | -0.160  |  |  |  |  |

| 50  | -0.095                                 | -0.134  | -0.173  |  |  |  |  |

| 55  | -0.105                                 | -0.145  | -0.185  |  |  |  |  |

| 60  | -0.114                                 | -0.156  | -0.197  |  |  |  |  |

| 65  | -0.124                                 | -0.186  | -0.209  |  |  |  |  |

| 70  | -0.133                                 | -0.177  | -0.222  |  |  |  |  |

Table 1.3: VCC Static and Transient Tolerance

Table 1.4: International Technology Roadmap for Semiconductors (ITRS-1999)

| -                                         | 2002<br>0.13                      | 2003 | 2004 | 2005<br>0.1 |     |

|-------------------------------------------|-----------------------------------|------|------|-------------|-----|

| Power                                     | Maximum<br>(For best performance) | 1.5  | 1.5  | 1.2         | 1.2 |

| Supply<br>voltage, V                      | Minimum<br>(For lowest power)     | 1.2  | 1.2  | 0.9         | 0.9 |

| Maximum Power with heat sink, W           |                                   | 130  | 140  | 150         | 160 |

| Current (for maximum performance), A      |                                   | 87   | 93   | 125         | 133 |

| P-P tolerance (±3% V <sub>nom</sub> ), mV |                                   | 90   | 90   | 72          | 72  |

| Chip frequency, GHz                       |                                   | 2.1  | 2.49 | 2.952       | 3.5 |

## References

- [1] Intel Corporation, "VRM 8.1 DC-DC Design Guidelines", May 1997.

- [2] Intel Corporation, "VRM 8.4 DC-DC Design Guidelines", November 1999.

- [3] Intel Corporation, "VRM 9.0 DC-DC Design Guidelines", November 2001.

- [4] Intel Corporation, "Intel Pentium 4 Processor VR-Down Design Guidelines", November 2002

- [5] Intel Corporation, "Voltage Regulator-Down 10.0 (VRD) Design Guidelines", April 2003

- [6] Intel Application Note AP-912, "Pentium<sup>®</sup> III Xeon<sup>TM</sup> Processor Power Distribution Guidelines," March 1999.

- [7] B. Arbetter and D. Maksimocic, "DC-DC Converter with Fast Transient Response and High Efficiency for Low-Voltage Microprocessor Loads," IEEE Thirteenth Annual Applied Power Electronics Conference and Exposition, APEC'98, Vol. 1, pp. 156-162, 1998.

- [8] P. Wong, F. Lee, X. Zhou and J. Chen, "Voltage Regulator Module (VRM) Transient Modeling and Analysis," IEEE 34<sup>th</sup> Annual Industry Applications Conference Record, IAS'99, Vol. 3, pp. 1669-1676, 1999.

- [9] Y. Panov and M. Jovanovic, "Design and Performance Evaluation of Low-Voltage/High-Current DC/DC On-Board Modules," IEEE Fourteenth Annual Applied Power Electronics Conference and Exposition, APEC'99, Vol. 1, pp. 545-552, 1999.

- [10] Y. Panov and M. Jovanovic, "Design Considerations for 12-V/1.5-V, 50-A

Voltage Regulator Modules," IEEE Fifteenth Annual Applied Power Electronics

Conference and Exposition, APEC'00, Vol. 1, pp. 39-46, 2000.

- [11] M. Zhang, M. Jovanovic and F. Lee, "Design Considerations for Low-Voltage On-Board DC/DC Modules for Next Generations of Data Processing Circuits," IEEE Transaction on Power Electronics, Vol. 11, Issue 2, pp.328-337, March 1996.

- [12] J. Renauuer, "Challenges in Powering High Performance, Low Voltage Processors," IEEE Eleventh Annual Applied Power Electronics Conference and Exposition, APEC'96 Vol. 2, pp. 977-983, 1996.

- [13] Xunwei Zhou, "Low-Voltage High-Efficiency Fast Transient Voltage Regulator Modules", Ph.D. Dissertation, Virginia Polytechnic Inst. State Univ., Blackburg, 1999.

- [14] O. Djekic and M. Brkovic, "Synchronous Rectifiers vs. Schottky Diodes in a Buck Topology for Low Voltage Applications," IEEE 28<sup>th</sup> Annual Power Electronics Specialists Conference, PESC'97 Record, Vol. 2, pp. 1374-1380, 1997.

11

- [15] Art Brochschmidt, "Optimizing Distribution Bus Voltages," IEEE Thirteenth Annual Applied Power Electronics Conference and Exposition, APEC'98, Vol. 2, pp. 889-894, 1998.

- [16] Yuri Panov and Milan M. Jovanovic, "Stability and Dynamic Performance of Current-Sharing Control for paralleled Voltage Regulator Modules," Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2001, APEC 2001, Volume: 2, Page(s): 765-771, 2001.

- [17] Xunwei Zhou, Peng Xu, and Lee, F.C., " A novel current-sharing control technique for low-voltage high-current voltage regulator module applications," IEEE Transactions on Power Electronics, Volume: 15 Issue: 6 Page(s): 1153-1162, Nov., 2000.

- [18] Texas Instruments, "Designing Fast Response Synchronous Buck Regulators Using the TPS5210," Application Report, March 1999.

## CHAPTER TWO

# TECHNICAL REVIEW

### 2.1 Review of multiphase VRMs

Most of today's non-isolated Low-Voltage Regulator Modules (LVRMs) are buck derived such as the conventional buck, the synchronous buck and the Quasi-Square-Wave (QSW) buck [1-8]. While the isolated LVRMs are those such as symmetrical and asymmetrical half-bridge, active clamped forward, flyback forward and push-pull structures [9-12]. The secondary side of the isolated topology can have different schemes such as forward, center-tapped, or current-doubler as discussed in [12, 13].

The VRM and microprocessor systems are highly nonlinear and time varying. A high performance control loop is essential and requires extensive knowledge of converter behavior and load changes. In general, voltage PWM control, voltage hysteretic control, peak current control, average current control, and  $V^2$  control are the most popular control methods [14].

Among the above-mentioned topologies and control methods, mainly the voltage hysteresis based synchronous buck converter is adapted in this dissertation.

#### 2.1.1 Interleaved (Multiphase) Technique on a Buck Converter

It is well known, the current ripple depends on the inductor value, the larger the inductor, the smaller the current ripple. However, a large inductor does not only mean greater volume but also deteriorated dynamic response. The other method to reduce current ripple is to increase the switching frequency, unfortunately this will lower the efficiency due to switching loss. It must be also noted that adding large output capacitors to reduce the output voltage ripple is not practical since it will reduce the VRM power density.

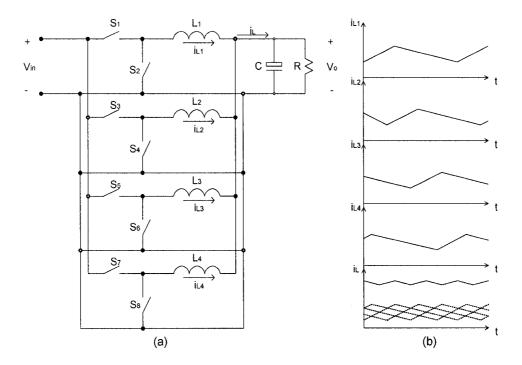

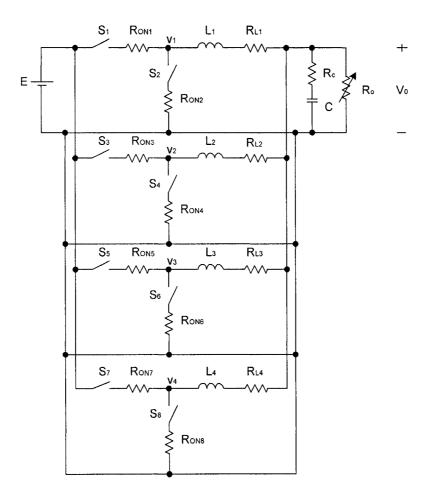

The interleaved technique was introduced to reduce output ripple while maintaining transient performance and limiting inductor value [7, 14-18]. The essential principle of interleaved technique is to parallel switches and inductors between input voltage and output capacity. The reason for reducing the current ripple by interleaved technique is phase shifting among the different switches and the current delay they generate corresponding to the respective inductors. Obviously, output current is a summary of all branches and the total current ripple can be cancelled due to the phase shifting of each branch current. This is illustrated in Figure 2-1. In general, interleaved technique is tantamount to increasing switching frequency while the effective output inductor is reduced due to parallel.

There are many advantages for interleaved technology with N interleaved converters that include:

1) The output voltage ripple frequency is N times larger than switching frequency  $f_s$  of each individual converter in the interleaved VRM. Therefore, it reduces output ripple while maintaining high efficiency. This is because the switching frequency for power devices and inductors is only  $f_s$ .

2) The effective output inductor is N times smaller than each individual phase inductor which speeds the transient.

3) The total VRM output current is distributed into every individual phase which makes the VRM current carrying capability larger and reduces the conducting losses in power devices and inductors.

4) The dynamic performance is much better than the single-phase converter since the 2, 3, ...N branches can be turned on simultaneously for providing large slew rate current.

Interleaved technique is not limited in the buck converter, all the other converters like boost, flyback, push-pull, half bridge, full bridge, can use the interleaving technology for the same purpose. Actually, what need to do is duplicating switches, inductors or transformers, putting them in parallel and having a phase shift. In this dissertation, the adaptive digital controller is based on multiphase buck converters since this is the most popular topology of microprocessors' power supply in the industry.

Figure 2-1: Multiphase buck converters and its output inductor currents (a) Interleaved buck converter (b) Current waveform of 4-phase interleave

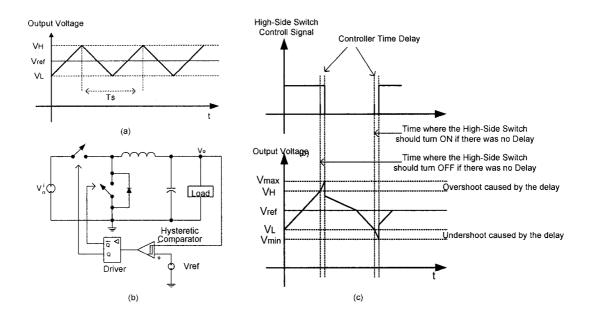

Figure 2-2: Voltage hysteretic control(a) Theoretical hysteretic window(b) Block diagram(c) Actual output ripple waveform

16

### 2.1.2 Single-Phase Hysteretic Voltage-Mode Control

For a specific converter, there are many different control techniques to meet the output requirements. Choosing the most suitable one depends on the cost, physical size, logical complication, noise immunity, steady-state performance and dynamic response. The most popular control methods for interleaved converters are pulse width modification (PWM), peak current control, and voltage hysteretic control.

To control the output voltage ripple and limit it within a specific band centered at a reference voltage, the voltage hysteretic control is a good candidate [19]. It tracks the output voltage and keeps it between a maximum voltage ( $V_H$ ) and a minimum voltage ( $V_L$ ) as shown in Figure 2-2.(a).

Figure 2-2.(b) shows a simplified block diagram for a single-phase voltage-mode hysteretic controlled buck converter. The controller will turn-on the high-side switch and turn-off the low side switch if the output voltage drops below  $V_L$ , and it will turn-off the high-side switch and turn-on the low side switch if the output voltage exceeds  $V_H$ .

The feedback delay of the control loop generates an actual output voltage overshoot as shown in Figure 2-2.c. The extra small ripple caused by those delays must be considered in the design.

In addition to the advantage of controlling the ripple within a hysteretic window, it is also good because there is no need to consider loop compensation and the output voltage ripple becomes relatively independent of the output capacitor value. In fact, both the capacitor and the inductor values can now be selected more freely to satisfy only the transient requirements without taking into consideration the output voltage requirements since the operation of the hysteretic control can take care of it automatically. Also, the response of the controller is pretty fast since the switch control signals are derived directly from the output voltage ripple which allow the controller to respond within one switching cycle.

The digital controller in this dissertation is based on voltage hysteretic control. Due to the high current carrying in each mode, an adaptive current observer is designed for achieving current senseless control for high efficiency and small size purposes.

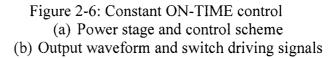

### 2.2 Review of Transient Improvement Circuits

For improving the dynamic performance of the VRM, two different kinds of methods have been presented [20-22]. One is to add a redundant circuit in parallel with the VRM, kicking in when load changes dramatically and kicking off at steady state; the other is focusing on the VRM itself, and speeds the transient by improving the control method.

ALL-ON and ALL-OFF control is one of the ideas for improving the control method. When it comes the fast transient, the load normally generates a voltage spike which is sensed by the controller. If the voltage drops significantly, the controller will turn on all the high-side switches together to source more current. This is called ALL-ON control. If the voltage increases significantly, the controller will turn on all the low-side switches together to sink more current. This is so-called ALL-OFF control. This is a very popular method used in industry.

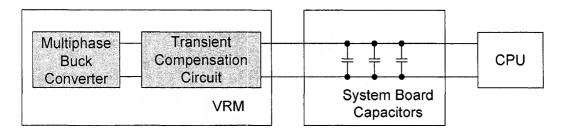

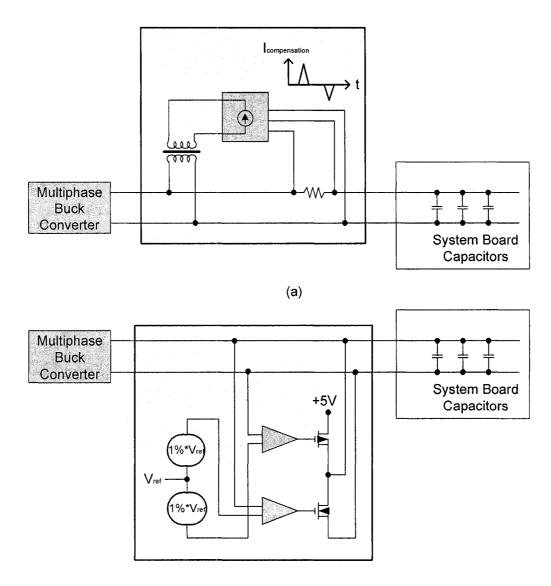

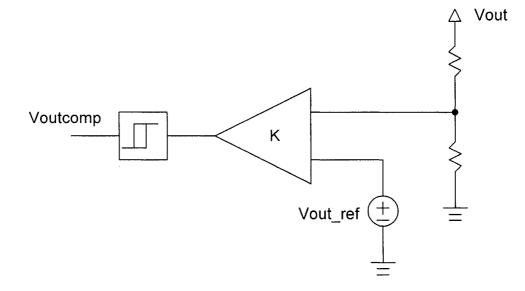

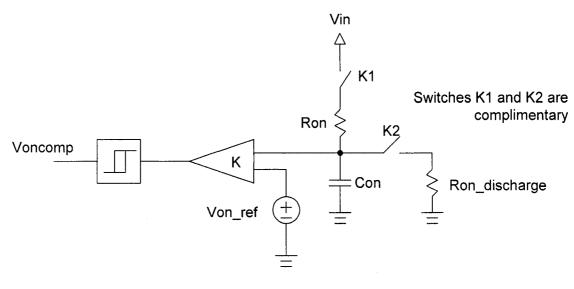

The other kind of solution is the redundant control. It focuses on adding an extra stage at the output of the VRM to improve the fast transient response. The typical structure is shown in Figure 2-3. The transient compensation circuit normally only operates at fast transient, not at steady state mode or slow transient mode.

There are two different dominant control methods as shown in Figure 2-4. The current regulator type compensator is used to generate a high di/dt current at transient to compensate the high current slew rate load changes. It only works when the di/dt of the load current is larger than the reference value. It stops after voltage recovery. The voltage regulator type compensator works like a linear regulator with voltage hysteresis. When the output voltage value is not in the hysteresis window, the linear regulator is triggered.

However, the main reasons of generating voltage drops at fast transient are caused by: 1) propagation delay compared with the huge di/dt; 2) controller delay; 3) inductor response delay. Therefore, transformer or inductor type compensators are not as effective as voltage regulator type compensators. Even the latter is not fast enough to respond to the microprocessor's load changes due to the propagation delay of the system board.

An active compensator proposed in this dissertation gives a voltage regulator type compensator somehow similar to the one in Figure 2-4 (b). But it monitors the voltage drop of the CPU core voltage rather than setting a hysteretic window for it. Also, it provides enough voltage drop cross the socket inductance and trace inductance and resistance, therefore it compensates the transient voltage spike by generating a large transient compensation current.

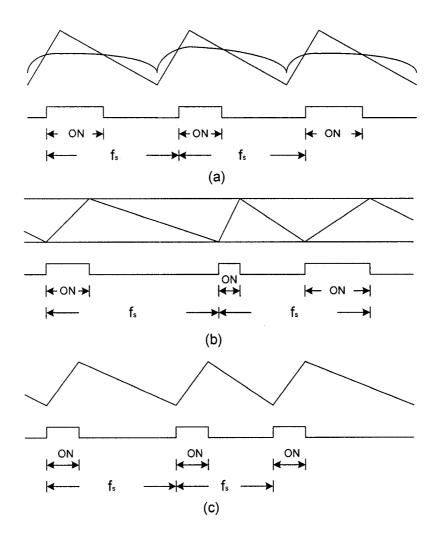

#### 2.3 Review of ON-TIME Control

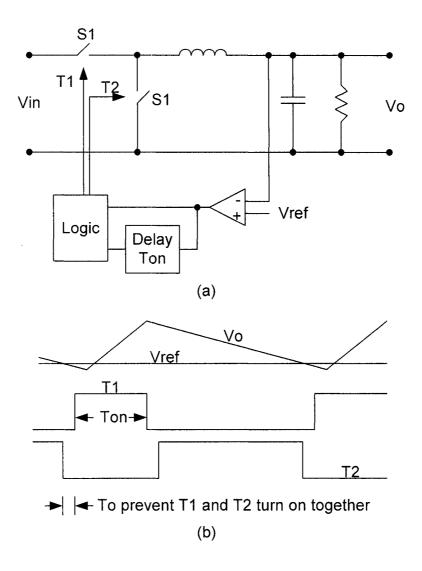

ON-TIME control is widely used in rectifiers, converters and inverters. It is different from PWM control since its switching frequency is not fixed like in PWM control. The controller regulates the ON-TIME duration of the switching circle with a specified rule, and the OFF-TIME of the circle is normally decided on the output value like output voltage [23-27]. Although it is variable frequency control, it is not the same as hysteretic control. The latter only set rule for output variation, and it does not take the ON-TIME, OFF-TIME duration and the switching frequency into account. Therefore, even the designer himself can only give a wide range of the frequency variation, and hardly to tell the ON-TIME duration. With the changes of the power switches, inductors, capacitors and loads, the frequency and ON-TIME duration will deviate. In this dissertation, we can see the advantage of the ON-TIME control, although it is variable frequency, the ON-TIME duration is known and regulated. It does not shift with the component or load changes. Figure 2-5 shows the comparison of the three different kinds of controls. Figure 2-5 (c) shows a fixed ON-TIME control. However, the ON-TIME duration is not necessarily constant. It could be proportional to some control parameters or some system variables which is defined by the designer. Normal, the ON-TIME information is decided by the system behaviors, for example, the input voltage, reference voltage, output current, load current slew rate, temperature, phase difference, etc.

A buck converter with constant ON-TIME control is shown in Figure 2-6. When output voltage is lower than pre-determined value, the high-side switch is turned on. It is turned off after a preset period of Ton which can be achieved by a delay circuit. The output ripple and switching frequency, therefore, is determined by the Ton delay. The longer the Ton, the larger the output ripple and the lower the switching frequency.

ON-TIME control was used on VRM along with PWM control to improve efficiency [15]. At regular operation, PWM is used for low EMI purposes, while constant ON-TIME control is used for light load to improve efficiency. This kind of controller has a load current sensor to switch between these two control methods. At ON-TIME control, the output ripple is slightly larger than PWM control, while the switching frequency is smaller, so it greatly reduces switching loss, especially for multiphase converters.

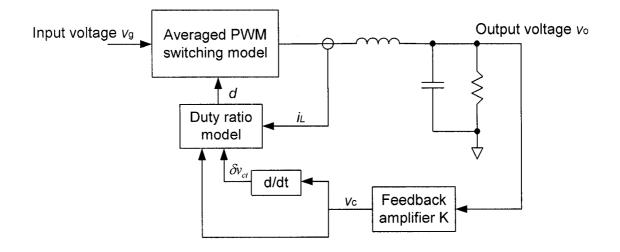

An average duty ratio model for DC-DC converters employing constant ON-TIME control is derived in [25]. The conceptual circuit diagram for average duty ratio model is

given in Figure 2-7. And the final model is given in Equation (2-1) where *Ri* is the DC gain of the current sensing network and all the other variables are defined in Figure 2-7.

$$d = \frac{d_{p} + d_{r}}{2}$$

$$d_{p} = \frac{v_{c} - R_{i}i_{L} + \sqrt{(R_{i}i_{L} - v_{c})^{2} + (m_{1} + m_{2})m_{2}}}{m_{1} + m_{2}}$$

$$d_{r} = \frac{v_{c} - R_{i}i_{L} + \sqrt{(R_{i}i_{L} - v_{c})^{2} + (m_{1} + m_{2})(m_{2} + 2\delta v_{c})}}{m_{1} + m_{2}}$$

$$m_{1} = \frac{R_{i}(v_{g} - v_{o})}{L}T_{on}$$

$$m_{2} = \frac{R_{i}v_{o}}{L}T_{on}$$

$$\delta v_{c} = \delta v_{cl}T_{on}$$

(2-1)

In this dissertation, the concept in Figure 2-6 is used and expended to multiphase VRMs for laptop usage. For this usage, the input voltage is changing in a wide range and the constant ON-TINE is expended to proportional ON-TIME with the definition of ON-TIME is proportional to the input voltage.

Figure 2-3: Fast transient compensation circuit

(b)

Figure 2-4: Fast transient compensation (a) Current regulator type (b) Voltage regulator type

23

Figure 2-5: Comparisons of PWM, hysteretic and ON-TIME control (a) PWM control (b) Hysteretic control (c) Constant ON-TIME control

Figure 2-7: Conceptual circuit diagram for duty ratio model

## References

- Xu, P.; Wei, J.; Lee, F.C.; "The active-clamp couple-buck converter-a novel high efficiency voltage regulator modules", Applied Power Electronics Conference and Exposition, 2001. APEC 2001. Sixteenth Annual IEEE, Volume: 1, 4-8 March 2001 Page(s): 252 -257 vol.1

- [2] Kaiwei Yao; Yu Meng; Lee, F.C.; "Control bandwidth and transient response of buck converters", Power Electronics Specialists Conference, 2002. pesc 02. 2002 IEEE 33rd Annual, Volume: 1, 23-27 June 2002 Page(s): 137 -142 vol.1

- [3] Peng Xu; Jia Wei; Lee, F.C.; "Multiphase coupled-buck converter-a novel high efficient 12 V voltage regulator module", Power Electronics, IEEE Transactions on, Volume: 18 Issue: 1, Jan. 2003 Page(s): 74 –82

- [4] Pit-Leong Wong; Wu, Q.; Peng Xu; Bo Yang; Lee, F.C.; "Investigating coupling inductors in the interleaving QSW VRM", Applied Power Electronics Conference and Exposition, 2000. APEC 2000. Fifteenth Annual IEEE, Volume: 2, 6-10 Feb. 2000 Page(s): 973 -978 vol.2

- [5] Xunwei Zhou; Donati, M.; Amoroso, L.; Lee, F.C.; "Improve light load efficiency for synchronous rectifier buck converter", Applied Power Electronics Conference and Exposition, 1999. APEC '99. Fourteenth Annual, Volume: 1, 14-18 March 1999 Page(s): 295 -302 vol.1

- [6] Deuty, S.; "Optimizing transistor performance in synchronous rectifier buck converters", Applied Power Electronics Conference and Exposition, 2000. APEC 2000. Fifteenth Annual IEEE, Volume: 2, 6-10 Feb. 2000 Page(s): 675 -678 vol.2

- [7] Abu Qahouq, J.A.; Jia Luo; Batarseh, I.; "Voltage regulator module with interleaved synchronous buck converters and novel voltage-mode hysteretic control", Circuits and Systems, 2001. MWSCAS 2001. Proceedings of the 44th IEEE 2001 Midwest Symposium on, Volume: 2, 14-17 Aug. 2001 Page(s): 972 -975 vol.2

- [8] Panov, Y.; Jovanovic, M.M.; "Design considerations for 12-V/1.5-V, 50-A voltage regulator modules", Power Electronics, IEEE Transactions on, Volume: 16 Issue: 6, Nov. 2001 Page(s): 776 –783

- [9] Kaiwei Yao; Yu Meng; Lee, F.C.; "A novel winding coupled-buck converter for high-frequency, high step-down DC/DC conversion", Power Electronics Specialists Conference, 2002. pesc 02. 2002 IEEE 33rd Annual, Volume: 2, 23-27 June 2002 Page(s): 651 -656 vol.2

- [10] Mao Ye; Peng Xu; Bo Yang; Lee, F.C.; "Investigation of topology candidates for

48 V VRM", Applied Power Electronics Conference and Exposition, 2002. APEC

2002. Seventeenth Annual IEEE, Volume: 2, 10-14 March 2002 Page(s): 699 -705

vol.2

- [11] Xu, P.; Lee, F.C.; "Design of high-input voltage regulator modules with a novel integrated magnetics", Applied Power Electronics Conference and Exposition, 2001.

APEC 2001. Sixteenth Annual IEEE, Volume: 1, 4-8 March 2001 Page(s): 262 -267 vol.1

- [12] Jia Wei; Peng Xu; Lee, F.C.; "A high efficiency topology for 12 V VRM-pushpull buck and its integrated magnetics implementations", Applied Power Electronics Conference and Exposition, 2002. APEC 2002. Seventeenth Annual IEEE, Volume: 2, 10-14 March 2002 Page(s): 679 -685 vol.2

- [13] Peng Xu; Mao Ye; Lee, F.C.; "Single magnetic push-pull forward converter featuring built-in input filter and coupled-inductor current doubler for 48 V VRM", Applied Power Electronics Conference and Exposition, 2002. APEC 2002. Seventeenth Annual IEEE, Volume: 2, 10-14 March 2002 Page(s): 843 -849 vol.2

- [14] Texas Instruments, "Designing Fast Response Synchronous Buck Regulators Using the TPS5210," Application Report, March 1999.

- [15] Xunwei Zhou; Xu Peng; Lee, F.C.; "A high power density, high efficiency and fast transient voltage regulator module with a novel current sensing and current sharing technique", Applied Power Electronics Conference and Exposition, 1999. APEC '99. Fourteenth Annual, Volume: 1, 14-18 March 1999 Page(s): 289 -294 vol.1

- [16] Xunwei Zhou; Peng Xu; Lee, F.C.; "A novel current-sharing control technique for low-voltage high-current voltage regulator module applications", Power Electronics, IEEE Transactions on , Volume: 15 Issue: 6 , Nov 2000 Page(s): 1153 –1162

- [17] Capponi, G.; Minneci, L.; Librizzi, F.; Scalia, P.; "Multiphase voltage regulator module with transient step changing phases", Power System Technology, 2000.

Proceedings. PowerCon 2000. International Conference on, Volume: 1, 4-7 Dec. 2000 Page(s): 463 - 467 vol.1

- [18] Xiaoguo Liang; Jian Wei; Xinbo Ruan; "An interleaved three-level forward converter -- Suitable for the application of voltage regulator module (VRM)", Power Electronics Specialist, PESC. 2003 IEEE 34th Annual Conferece on, Volume: 1, June 15-19, 2003 Page(s): 127 –131

- [19] Wei Gu; Weihong Qiu; Wenkai Wu; Batarseh, I.; "A multiphase DC/DC converter with hysteretic voltage control and current sharing", Applied Power Electronics Conference and Exposition, 2002. APEC 2002. Seventeenth Annual IEEE, Volume: 2, 10-14 March 2002 Page(s): 670 -674 vol.2

- [20] Hoffman, K.; Ledwich, G.; "Resonant link topologies for fast power system transient compensation", Advances in Power System Control, Operation and Management, 1993. APSCOM-93, 2nd International Conference on, 7-10 Dec 1993 Page(s): 108 -113 vol.1

- [21] Peng, F.Z.; Akagi, H.; Nabae, A.; "Compensation characteristics of the combined system of shunt passive and series active filters", Industry Applications Society Annual Meeting, 1989, Conference Record of the 1989 IEEE, 1-5 Oct. 1989 Page(s): 959 -966 vol.1

- [22] Bussmann, M.; Langmann, U.; "Active compensation of interconnection losses for multi-GHz clock distribution networks", Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on, Volume: 39 Issue: 11, Nov. 1992 Page(s): 790-798

- [23] Suntio, T.; "Small-signal modeling of switched-mode converters under direct-on-time control-a unified approach", IECON 02 [Industrial Electronics Society, IEEE 2002 28th Annual Conference of the], Volume: 1, 5-8 Nov. 2002 Page(s): 479 -484 vol.1

- [24] Chen, D.S.; Lai, J.S.; "A study of power correction boost converter operating at CCM-DCM mode", Southeastcon '93, Proceedings., IEEE, 4-7 April 1993 Page(s): 6

- [25] Sung-Soo Hong; Byungcho Choi; "Technique for developing averaged duty ratio model for DC-DC converters employing constant on-time control", electronics Letters, Volume: 36 Issue: 5, 2 March 2000 Page(s): 397 –399

- [26] Lippincott, A.C.; Nelms, R.M.; Garbi, M.; Strickland, E.; "A series resonant converter with constant on-time control for capacitor charging applications", Applied Power Electronics Conference and Exposition, 1990. APEC '90, Conference Proceedings 1990, Fifth Annual, 11-16 March 1990 Page(s): 147-154

- [27] Ridley, R.B.; "A new continuous-time model for current-mode control with constant frequency, constant on-time, and constant off-time, in CCM and DCM", Power Electronics Specialists Conference, 1990. PESC '90 Record, 21st Annual IEEE, 11-14 June 1990 Page(s): 382 –389

## CHAPTER THREE

## ACTIVE CURRENT COMPENSATION FOR LOW-VOLTAGE HIGH CURRENT FAST TRANSIENT VRMS

### 3.1 Introduction

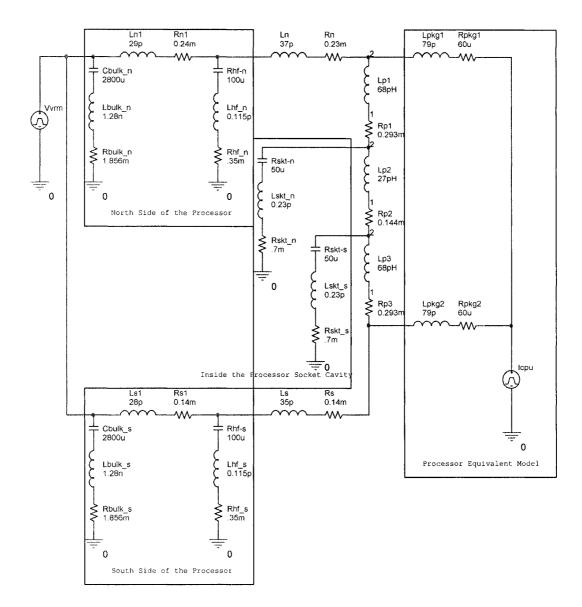

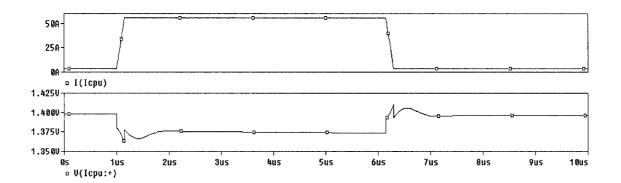

The recent generation of microprocessors work at a low operating voltage, high current, and a high current slew rate. For example, Intel's Pentium 4 2.8G processor operates between  $1.34V \sim 1.42V$  @ 55.9A, and  $350A/\mu s$  of current slew rate [1, 2]. To achieve such a high slew rate, a large capacitance is typically mounted on the microprocessor package and system board to absorb the voltage spike in load-change transient. Figure 3-1 shows an equivalent power delivery Pentium 4 model for transient response provided by Intel [1]. Under any transients, this system design can guarantee to limit the voltage variation within 4%. The stringent transients of full-load to sleep mode and sleep mode to full load are shown in Figure 3-2. Here, *Icpu* is the total current flowing through the CPU.

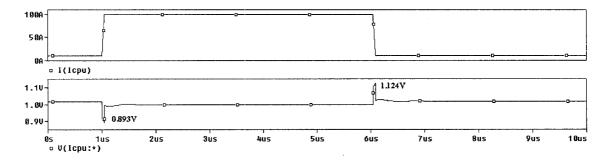

The next generation of microprocessors will work at lower operating voltages, higher current and higher current slew rate as mentioned in chapter one. Therefore, more capacitance at VRM output is required. Unfortunately, the space in a microprocessor package is very limited, making it difficult to add more capacitors. Furthermore, increased motherboard capacitance has little effect to limit the voltage spike in a fast transient due to the current response delay of large socket inductance and the ESL, ESR of capacitors. A simulation result is provided in Figure 3-3 to illustrate how voltage spikes could potentially reach 10% above the nominal value. Even all the capacitances are doubled, the total voltage variation still reaches 12% and cannot meet the stringent requirement. It should be noted that the steady-state voltage difference in Figure 3-3 is generated by voltage drops on interconnect resistance due to its high conduction current because the simulation is done in open loop.

A novel dynamic current compensator is presented here to minimize the voltage spike without additional capacitors. Instead, the capacitance on system board could reduce down to 2/3 of the present level; and the capacitance in microprocessor package can be decreased to approximate 3/4.

Another advantage of this compensator is its capability to compensate the transient response delay caused by large socket inductance under high current slew rate. Therefore, it provides for more freedom in package design.

Since this compensator works like a discrete linear regulator, by being active only during large load-change transients; the average power dissipation is very low. Hence, efficiency is reduced only a small amount.

Figure 3-1: Power delivery model for transient response for Intel Pentium 4 processor

Figure 3-2:  $V_{cc}$  of processor when  $I_{cpu}$  changes from 5A to 56A (a) di/dt=350A/usUpper: Microprocessor load change Lower: Vcc of microprocessor

Figure 3-3:  $V_{cc}$  of microprocessor when  $I_{cpu}$  changes from 10A to 100A @di/dt=2000A/us Upper: Microprocessor load change Upper: Microprocessor load change

#### 3.2 Transient Response Delay in a Fast Current Slew Rate System

High voltage spikes are caused during high slew rate load change because of the current response delay of socket inductance and the voltage drop across ESR and ESL of the capacitors.

For the high current slew rate model, the capacitor should be considered as a series of RLC circuits whose total voltage can be expressed as,

$$v_{c,total} = L_{ESL} \frac{di_c}{dt} + r_{ESR} i_c + v_c$$

(3-1)

where,  $L_{ESL}$  and  $r_{ESR}$  are equivalent series inductance and resistance, and  $i_c$  and  $v_c$  are the current and voltage of the ideal capacity. To provide a current slew rate at 2A/ns, the voltage drops across ESL and ESR of high-frequency capacitors will reach tens of millivolt level while the voltage drops across ESL of bulk capacitors will be larger than IV. Considering the operating voltage is IV, the actual current slew rate provided by capacitors is much smaller than desired so the voltage spike is generated. Therefore, few advantages can be achieved by paralleling more capacitors on system board.

Another reason for the transient response delay is the large connector and socket parasitic inductance as shown in Figure 3-1. If 2A/ns of current slew rate is assumed through connection inductance, it can only by achieved by a 150mV voltage drop, as calculated in Equation (3-2).

$$V_L = L_{skt} \frac{di_c}{dt} = 75 pH \times 2A / ns = 150 mV$$

(3-2)

The 150mV voltage drop compared for a 1V nominal output is significant and exceeds the required tolerance given in Figure 1-1. In Figure 3-1, the trace inductance is only  $20 \sim 30pH$ , while the socket inductance is about  $60 \sim 80pH$ . The challenge is that the socket inductance is very difficult to decrease and the VRM and capacitors have already been put as close as possible to the processor [3-6].

Based on the two reasons mentioned above, there is almost no effect on the voltage spike during such a fast load-change transient by simply adding more capacitors on system board. This is verified in simulation by doubling all the system capacitance mentioned before.

Hence, a novel compensation circuit will be introduced to increase the voltage drop across socket and trace inductances so that the current slew rate is not a limitation in fast transient response.

#### 3.3 Presented Active Transient Current Compensator

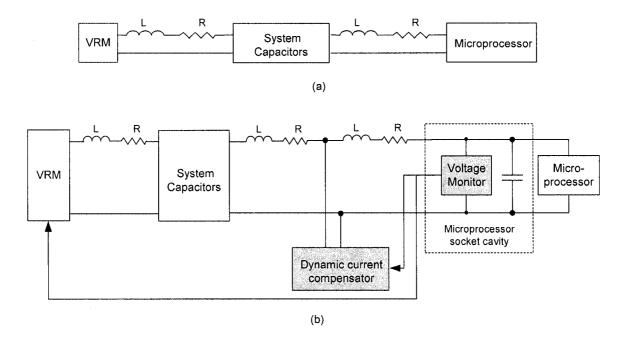

An active transient current compensator is presented here to speed the transient response. The presented compensator is inserted between the microprocessor package and the on board capacitors. The new model is illustrated in Figure 3-4. The trigger signal of the compensator comes from a built-in voltage monitor in the microprocessor package. Since the output high slew rate current in the compensator only appears in load-change transient, it does not influence VRM steady-state operation.

The details of the new topology are described in Figures 3-5 and Figure 3-6. The concept of this topology is similar to electrical static discharge (ESD) protection technique [7, 8], however the energy here is transferred bi-directionally. When the microprocessor operation changes from sleep mode to full-load mode, the compensator provides high slew rate current quickly. When the microprocessor operation changes from full-load mode to sleep mode, the compensator will absorb the extra current provided by VRM. Ideally, if energy flowing between VRM and the microprocessor is balanced, there will be no voltage spike in load-change transient.

What distinguishes this topology from any other fast transient VRMs [9, 10] is its fast response and the immunity to current delay caused by large socket inductance. That is because this compensation is not mounted tightly at the output of the VRMs, instead the voltage sensor is located at the Vcc of the CPU side. Therefore the linear regulator can provide sufficient voltage drops across the socket and trace inductance. Hence, it generates large slew rate current to minimize voltage spikes during transient. For other load-change corrections [9, 10], the compensators are combined with VRM and make the compensation impossible since they did not catch the main reason causing the current delay: the ESL and ESR of capacitors and the inductors of the socket and trace.

Figure 3-4: The different power delivery models for VRMs (a) Present power delivery model (b) Novel power delivery model

## 3.3.1. Voltage Monitor

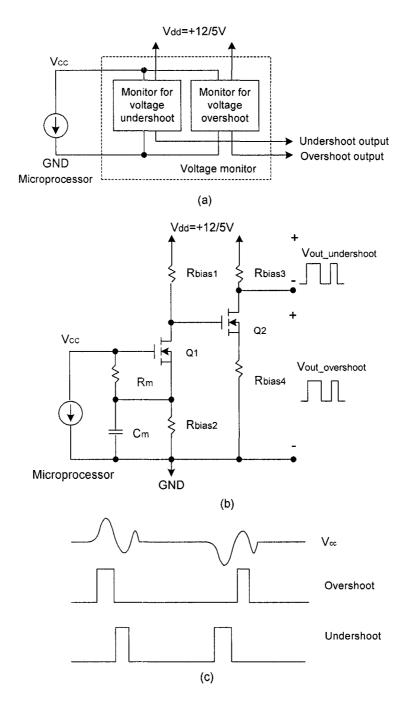

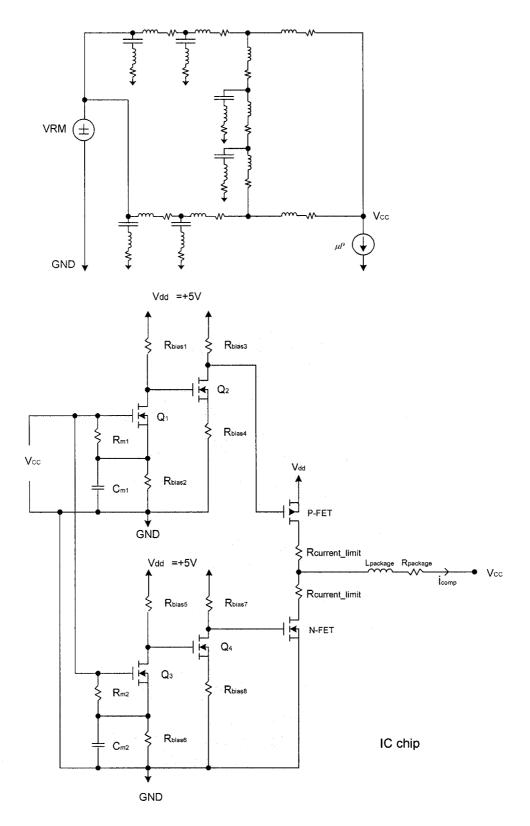

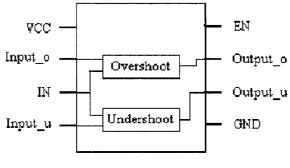

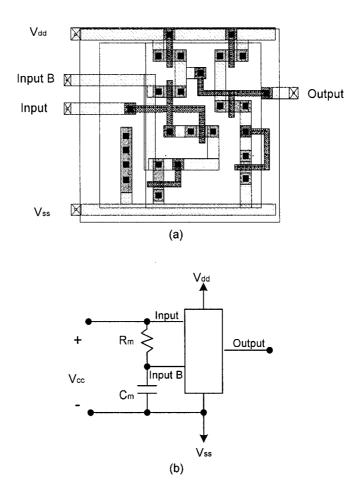

The voltage monitor is mounted inside the socket cavity and very close to the microprocessor's *Vcc* pin so it can monitor voltage variation in no time. The whole monitor is composed of two parts as shown in Figure 3-5. One is for voltage undershoot; the other is for voltage overshoot. These two parts have the same circuit but different biasing values.

The function of the voltage monitor is to sense the core voltage change of the microprocessor by  $R_m$  and  $C_m$ . These two values with matching biasing  $V_{GS}$  value of Q1 can set voltage sensitivity and output pulse duration. Q2 circuit transfers the Q1 output into pulse output as shown in Figure 3-5 (b).

The input and output relationship of the voltage monitor is shown in Figure 3-5 (c). When the load changes from sleep mode to full-load mode, current increases and voltage decreases so undershoot circuit has output and vice versa.

Another function of the voltage monitor is to inform the VRM controller that the loadchange transient has occurred so that the controller can make the interleaved VRM to operate at "ALL-ON" or "ALL-OFF" mode. Since there is almost no time delay for this monitor, it can improve VRM transient response as illustrated later.

Figure 3-5: Voltage monitor (a) Block diagram of voltage monitor (b) Voltage monitor schematics (different biasing for undershoot and overshoot) (c) Voltage monitor output

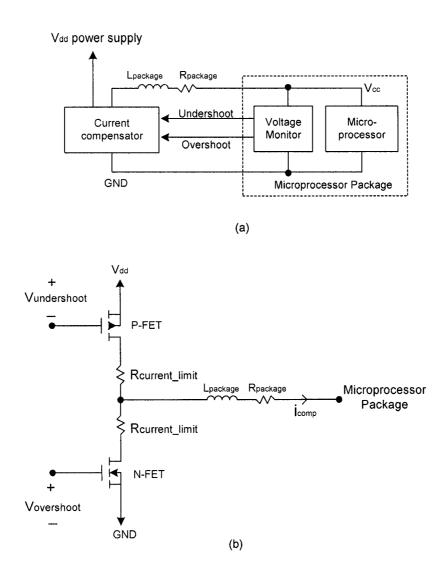

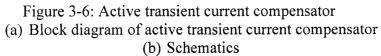

#### 3.3.2 Active Transient Current Compensator

The transient current compensator is shown in Figure 3-6. The compensator is mounted on the motherboard very close to the microprocessor package. The energy comes from the +5V/12V power supply on the motherboard and low ESL and ESR capacity is mounted beside it.

As shown in Figure 3-6(b), the compensator is composed of one P-type and one N-type MOSFET.  $R_{current\_limit}$  is optional and can be used to adjust injection current. When the load changes from sleep mode to full-load mode, P-FET is triggered by the undershoot output so current flows through PFET,  $R_{current\_limit}$ ,  $L_{package}$ ,  $R_{package}$  to microprocessor package. Since the voltage drop across  $L_{package}$  is large, current slew rate can be high enough to meet the load requirement. Therefore, the current change in the load is compensated so the voltage spike is minimized.

The current compensator works like a linear regulator. The regulation point is core voltage of the CPU, other than the VRM output end. Also, if the voltage changes are not large enough, the compensator circuit will not implement and no power is wasted during the stead state operation

3.3.3 Complete Schematics for the Simulation

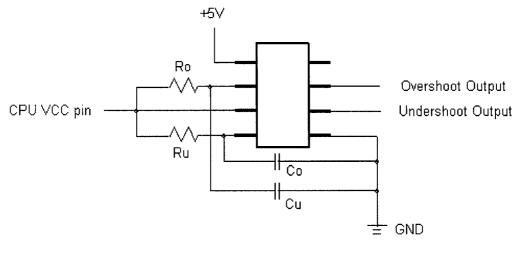

ASMC 0.8 micro CMOS process technology, C08DPDM is used to design the voltage monitor. The device specifications are listed in Table 3.1. Full schematics of the voltage monitor, compensator and power stage are given in Figure 3-7.

A top view of the voltage monitor IC chip and a typical application circuit are given in Figure 3-8 and Figure 3-9. Here, two input resistors and capacitors are moved out of the IC chip to provide more flexibility for frequency response. A layout of the undershoot circuit for the structure is shown in Figure 3-10. The overshoot circuit is symmetric with difference W/L scale.

| Device     | Parameter | Specification |         |       |      |

|------------|-----------|---------------|---------|-------|------|

|            |           | Min.          | Average | Max.  | Unit |

|            | Vto_N     | 0.60          | 0.70    | 0.8   | V    |

| W/L 20/0.8 | Isat_N    | 300           | 400     | 500   | uA/m |

| N-Channel  | BVdb_N    | 9             | 10      | -     | V    |

|            | Leff_N    | 0.65          | 0.75    | 0.85  | т    |

|            | Vto_P     | -0.8          | -0.9    | -1.0  | V    |

| W/L 20/0.8 | Isat_P    | -120          | -160    | -200  | uA/m |

| N-Channel  | BVdb_P    | -9            | -12     | -     | V    |

|            | Leff_P    | -0.65         | -0.75   | -0.85 | т    |

Table 3.1: Device Specification of 0.8 micro CMOS Process

Figure 3-7: Schematics

Pin configuration (top view)

Figure 3-8: Pin configuration of the voltage monitor

Typical Application Circuit

Figure 3-9: Typical application circuit of voltage monitor

#### 3.4 Simulation Results

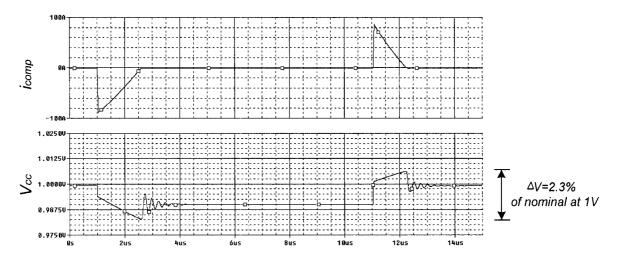

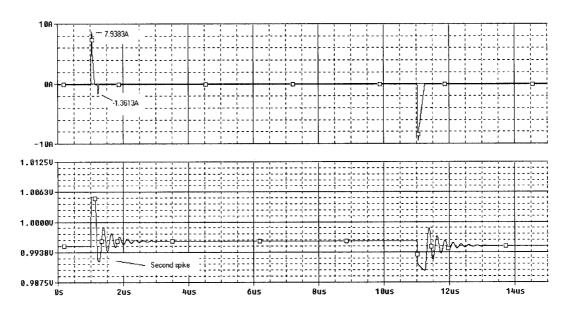

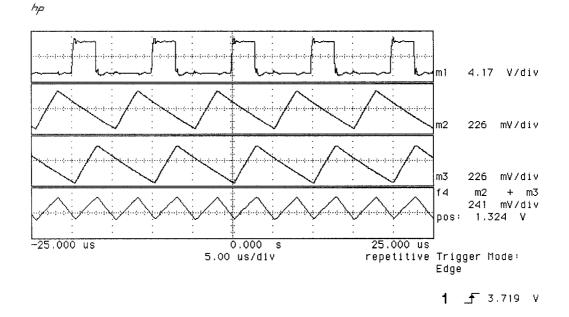

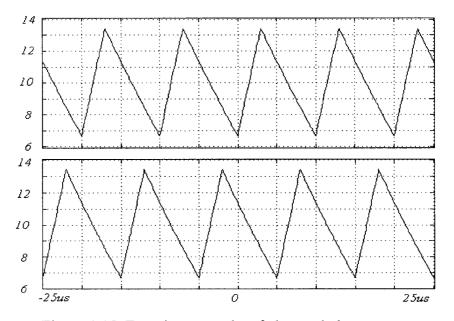

Simulation results for transient current compensation are shown in Figure 3-12. It is shown that the microprocessor operates at IV of  $V_{cc}$ , 100A of  $I_{cc}$ , and 2A/ns of current slew rate. All parasitic component values are the same as those in Figure 3-1 except package capacitance decreased to 3/4 of the present value and system capacitance reduced down to 2/3 of the present level. The top waveform in Figure 3-11 is the compensator's output current. It generates only in load-change transient. The bottom waveform is  $V_{cc}$  voltage of microprocessor. The total voltage variation is limited to 2.3% These values are much smaller than those in Figure 3-3.

More data when microprocessor operates from sleep mode to active mode and load change within active modes are provided in Table 3-2 and Table 3-3 to illustrate the behavior of the compensator.

From Tables 3.2 and 3.3 we can see that the total voltage variation could be limited to a very small value, less than 4% of the nominal value. However, the smaller the transient voltage variation is, the longer the transient duration will be. It also makes the compensator operate more frequently and may cause instability.

When we decrease the values of capacitor  $C_m$ , the voltage monitor will not be so sensitive and it compensates less. Therefore, a tradeoff is always made by choosing the desired voltage variation and the compensator's operating duration. Table 3.4 shows the compensation response versus capacitor value  $C_m$ . It is clear that the transient duration reduced (less compensation) when  $C_m$  decreased and the voltage variation increased.

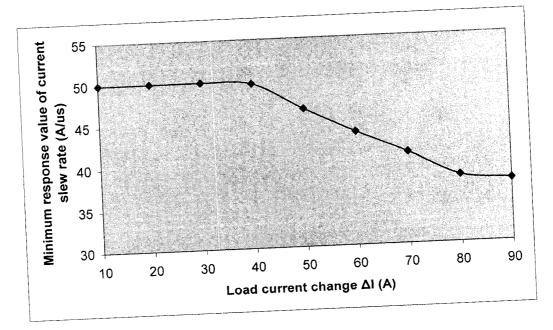

Another consideration for the transient compensator is its stability, determined by the compensation for all the current change frequencies. If the compensator operates whenever the current changes, even when the voltage variation is very small, then the system will be unstable. The design target of the compensator is to compensate high current slew rate load changes not all load changes. Therefore, a minimum response value of the current slew rate should be set so that the compensator does not work when load change is slower than the critical value.

As discussed before, this can be adjusted by changing  $C_m$ , the voltage ratio of the twostage amplifier. Table 3.5 is an example to show that the compensator only responds when current slew rate is higher than the specific value. The operating area for this compensator is above the curve. This is reasonable because the VRM could handle *50A/us* current slew rate and the decoupling capacitors on system board can also provide some extra *di/dt* currents. Obviously, the compensator is only on duty of high current slew rate range.

Figure 3-11: Simulation results after transient current compensation  $@V_{cc}=1V$ ,  $I_{max}=100A$ , and current slew rate=2A/ns ( $C_m=200n$ )

| Load change (A) | i <sub>comp</sub> (A) | Transient time<br>(µs) | $\Delta V_{cc}$ |

|-----------------|-----------------------|------------------------|-----------------|

| 10⇔100          | 88.1                  | 2.55                   | 3.2%            |

| 10⇔90           | 83.2                  | 2.36                   | 3.1%            |

| 10⇔70           | 58.2                  | 1.5                    | 2.4%            |

| 10⇔50           | 38.4                  | 0.93                   | 1.9%            |

| 10⇔30           | 18.8                  | 0.4                    | 1.8%            |

Table 3.2: Compensation Result when Microprocessor Operates from Sleep Mode to Active Mode @ 2A/ns Current Slew Rate and  $1V V_{cc} (C_m=100n)$

Table 3.3: Compensation result when Microprocessor Operates within Active Mode @ 0.5A/ns Current Slew Rate and  $1V V_{cc} (C_m = 100n)$

| Load change (A) | i <sub>comp</sub> (A) | Transient time<br>(μs) | $\Delta V_{cc}$ |

|-----------------|-----------------------|------------------------|-----------------|

| 50⇔30           | 18.8                  | 0.43                   | 1.8%            |

| 50⇔40           | 8.6                   | 0.23                   | 1.8%            |

| 50⇔60           | 8.7                   | 0.25                   | 1.8%            |

| 50⇔80           | 28.6                  | 0.71                   | 1.9%            |

| 50⇔90           | 38.4                  | 0.98                   | 2.0%            |

| Capacitor $C_m$ ( <i>nF</i> ) | Transient time (µs) | $\Delta V_{cc}$ |

|-------------------------------|---------------------|-----------------|

| 200                           | 3.21                | 2.3%            |

| 100                           | 2.55                | 3.2%            |

| 80                            | 2.23                | 3.4%            |

| 60                            | 1.82                | 3.6%            |

| 40                            | 1.34                | 4.1%            |

| 20                            | 0.91                | 5.5%            |

| 10                            | 0.84                | 17.5%           |

|                               |                     |                 |

Table 3.4: Compensation Responses versus Capacitor  $C_m$

Table 3.5: Critical response value @  $C_m = 60nF$

The output signal of the voltage monitor is shown in Figure 3-12. At steady state, the signal is small enough and will not turn on compensator's switches. During transient, it has a high voltage output with different voltage values to generate corresponding compensation currents. This is similar to a linear regulator. In general, one can say that the compensator switches off at steady state while it works like a linear regulator at transient.

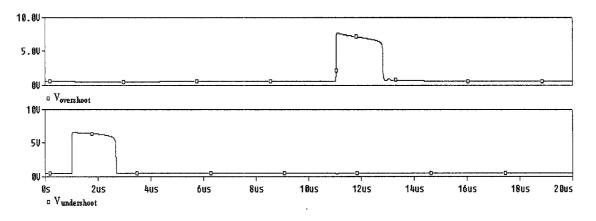

A poorly designed compensator might have over compensation problems like those shown in Figure 3-13. It may generate ringing in transient process. This is because the first compensation is too big, and it causes the second spike to reverse trigger the compensator. This is the stability problem mentioned before. It can be resolved by decreasing the  $C_m$  value.

There is a large dynamic current flowing through the current compensator and it may cause a system voltage drop on the system board. As mentioned before, the energy of the compensator comes from the motherboard, hence capacitors should be mounted close to the compensator to avoid large voltage drops.

The total charge the compensator needed for each transient can be calculated in Equation (3-3),

$$\Delta Q = C \bullet \Delta V = \int i(t) dt \tag{3-3}$$

54

Figure 3-12: Voltage monitor output signal

Figure 3-13: Compensation for second spike during transient

Using Equation (3-3), we can approximately obtain Equation (3-4) based on Figure 3-11.

$$\Delta Q = \frac{1}{2} \times 90 \times 1.7 = 76.5(\mu q) \tag{3-4}$$

Therefore, if the voltage drop in the power supply caused by the compensator current is 0.5V for a +5V power supply, the capacitance value for system voltage is

$$C = \frac{\Delta Q}{\Delta V} = \frac{76.5}{0.5} = 153(\mu F)$$

(3-5)

This value is very small compared with the bulk capacitance value and approximates the high frequent capacitance value on the motherboard. Therefore, it should not be a problem to mount such a capacitor beside the compensator.

#### 3.5 Summary

A novel active transient current compensation is presented in this chapter to minimize the voltage spike during load-change transient for future generation of microprocessors. Therefore, the total voltage variation at  $V_{cc}$  can be limited within 2% (with 240nF capacitors) with the package and system capacitance both decreasing to a much smaller value. Since the compensator has good immunity to large inductance, the layout of system board can be designed more easily and the package inductance requirement will be easier to fulfill.

## References

- [1] Intel Pentium 4 Processor/Intel 850 Chipset Family Platform Design Guide

- [2] Pentium 4 Processor VR-Down Design Guidelines

- [3] J. Drnauer et. al., "Electrical Evaluation of Flip-Chip Package Alternatives for Next Generation Microprocessors", IEEE Trans. on Advanced Packaging, vol. 22, pp. 407-415, Aug. 1999

- [4] D. J. Herrell and B. Beker, "Modeling of Power Distribution Systems for High-Performance Microprocessor", IEEE Trans. on Advanced Packaging, vol. 22, pp. 240-249, Aug. 1999

- [5] R. Panda et. al., "Model and Analysis for Combined Package and On-Chip power Grid Simulation", ISLPED '00, Rapalla, Italy

- [6] D. M. Hockanson, et. al., "FDTD and Experimental Investigation of EMI from Stacked-Card PCB Configurations", in IEEE Trans. on Electromagnetic Compatibility, vol. 43, pp.1-9, Feb. 2001

- [7] J. E. Vinson and J.J. Liou, "ESD Protection techniques for Semiconductor Devices", Proceedings of International Conference on Microelectronics, vol. 1, pp. 311-321, 2000

- [8] Z. H. Wang and Chen-Hui Tsay, "An on-chip ESD protection Circuit with Low Trigger Voltage in BiCMOS Technology", IEEE Journal of Solid-State Circuits, vol. 36, pp. 40-45, Jan. 2001

- [9] F.N.K. Poon et. al., "Very Fast Transient Voltage Regulators Based on Load Correction", 1999 IEEE

- [10] S.R. Sanders, Albert Wu, "Active Clamp Circuits for Switchmode Regulators Supplying Microprocessor Loads", 1997 IEEE

- [11] Jia Luo, Xiaofang Gao, and Issa Batarseh, "Active compensator to improve transient response delay for future generation of microprocessor", Devices, Circuits and Systems, 2002. Proceedings of the Fourth IEEE International Caracas Conference, 17-19 April 2002, Page(s): P018-1 -P018-5

- [12] Jia Luo, Issa Batarseh, Xiaofang Gao, and Tomas Wu, "Transient current compensation for low-voltage high-current voltage regulator modules", Applied Power Electronics Conference and Exposition, 2002. APEC 2002. Seventeenth Annual IEEE, Volume: 1, 10-14 March 2002, Page(s): 223 -228 vol.1

## CHAPTER FOUR

# DIGITAL TIME-VARYING CURRENT OBSERVER AND FEEDBACK CONTROL FOR MULTIPHASE VRMS

#### 4.1 Introduction