Improved family of resonant dc-to-dc and dc-to-ac power converters

Khan, Aslam Fakhrulislam

ProQuest Dissertations and Theses; 1999; ProQuest Dissertations & Theses (PQDT)

pg. n/a

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

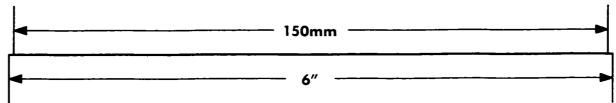

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

IMI

A Bell & Howell Information Company

300 North Zeeb Road, Ann Arbor MI 48106-1346 USA

313/761-4700 800/521-0600

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# IMPROVED FAMILY OF RESONANT DC-TO-DC AND DC-TO-AC POWER CONVERTERS

by

ASLAM F. KHAN

B.E. Gujarat University, India 1991

M.S. University of Central Florida, 1994

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Department of Electrical and Computer Engineering in the College of Engineering at the University of Central Florida

Orlando, Florida

Spring Term 1999

Major Professor: Issa E. Batarseh

UMI Number: 9923711

Copyright 1999 by Khan, Aslam Fakhrulislam

All rights reserved.

UMI Microform 9923711 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

#### **ABSTRACT**

A family of dc-to-dc boost derived isolated resonant power converter topologies and new modified boost isolated dc-to-ac zero-voltage-switching inverter topology are proposed. The dc-to-dc converters include the basic isolated boost, modified isolated boost with active clamp and a modified isolated boost with output resonant network. The principle of operation and steady-state analyses for all these topologies are presented. It is shown that the dc-to-dc converters proposed operate at zero-voltage switching and have better control characteristic performance with improved efficiency and lower current and voltage stresses. The application of the proposed topologies is not limited to dc-to-dc and dc-to-ac power supplies but can also be used for improving power factor. Simulation of these converters using PSPICE is given to verify the theoretical and experimental results. In addition, the new isolated dc-to-ac modified boost converter is proposed which achieves zero-voltage switching for the main power switch. Furthermore, parasitic components in the circuit are utilized to achieve resonance condition essential for zerovoltage switching for the two switches employed in this topology. As a result, enhanced performance and improved efficiencies are achieved in the newly developed inverter. Steady state analysis, PSPICE simulation, small signal modeling and experimental results are given to verify the theoretical, simulation and experimental results. The simulation and experimental results for the dc-to-ac inverter are in good agreement with the predicted results.

#### **ACKNOWLEDGEMENTS**

## In the Name of God, Most Beneficent Most Merciful

I would like to thank Dr. Issa Batarseh first and foremost for making this dissertation possible. He has truly shown all qualities of an academic advisor; by guidance, encouragement, help and support, for a successful completion of a Doctoral Dissertation. I thank him sincerely for this unique opportunity given to me which is a lifetime achievement in the academic area.

Secondly, I would like to thank my thesis committee consisting of Drs. W. Mikhael, Z. Qu, O. Demirci and J. Nayfeh for the valuable feedback and guidance at the time of Candidacy proposal and during thesis completion. Each one of them has my highest respect and regards.

Special thanks to Don Shumake for his support and granting me three weeks leave from my job on very short notice for the completion of this thesis.

I would like to thank my family for the unending support towards this endeavor. This consists of my brothers and sister and their families. Very special thanks to my parents, Abida and Fakhrulislam Khan, for all the love and support and believing in me.

Lastly, I want to thank God for all His blessings on me in my academic endeavors and otherwise.

I dedicate this thesis to my grandfather Gulamrab Abdul Rahim Khan and his vision.

## TABLE OF CONTENTS

|                                                                            |       |                                                      | Page |

|----------------------------------------------------------------------------|-------|------------------------------------------------------|------|

| List of Fig                                                                | gures |                                                      | viii |

| List of Tables                                                             |       |                                                      | хi   |

| Chapter 1 Introduction                                                     |       |                                                      | 1    |

|                                                                            | 1.1   | Background                                           | 1    |

|                                                                            | 1.1.1 | Basic Active Power Factor Correction Circuits        | 5    |

|                                                                            | 1.2   | Proposed Work                                        | 8    |

|                                                                            |       |                                                      |      |

| Chapter 2 Family of isolated dc-to-dc zero-voltage switching converters 14 |       |                                                      |      |

|                                                                            | 2.1   | Introduction                                         | 14   |

|                                                                            | 2.2   | Topology 1: Basic isolated boost converter           | 15   |

|                                                                            |       | 2.2.1 Modes of Operation                             | 17   |

|                                                                            | 2.3   | Topology 2: Modified ZVS boost converter with active | 18   |

|                                                                            |       | clamp circuit                                        |      |

|                                                                            |       | 2.3.1 Modes of Operation                             | 19   |

|                                                                            | 2.4   | Modified boost converter with a network on the       | 22   |

|                                                                            |       | output side                                          |      |

|                                                                            |       | 2.4.1 Modes of operation                             | 25   |

| Chapter 3 | Sim                  | ulation a | and experimental results for the dc-to-dc      | 27 |

|-----------|----------------------|-----------|------------------------------------------------|----|

|           | converter topologies |           |                                                |    |

|           | 3.1                  |           | Basic isolated boost converter                 | 27 |

|           |                      | 3.1.1     | Simulation results                             | 28 |

|           |                      | 3.1.2     | Experimental results                           | 29 |

|           | 3.2                  | Modi      | fied boost converter with active clamp circuit | 30 |

| -         |                      | 3.2.1     | Simulation results                             | 30 |

|           |                      | 3.2.2     | Experimental results                           | 31 |

|           | 3.3                  | Modif     | Tied boost converter with output network       | 33 |

|           |                      | 3.3.1     | Simulation results                             | 33 |

|           |                      | 3.3.2     | Experimental results                           | 35 |

|           | 3.4                  | Comp      | arison of the three topologies                 | 36 |

|           |                      | 3.4.1     | Basic isolated boost converter                 | 37 |

|           |                      | 3.4.2     | Modified boost converter with active clamp     | 38 |

|           |                      |           | circuit                                        |    |

|           |                      | 3.4.3     | Modified boost converter with output network   | 38 |

|           |                      |           |                                                |    |

| Chapter 4 | Dc-to                | -Ac reso  | onant zero voltage switching inverter          | 40 |

|           | 4.1                  | Introdu   | action                                         | 40 |

|           | 4.2                  | Basic o   | circuit operation                              | 41 |

|           | 4.3                  | Steady    | state mathematical model                       | 44 |

|           | 4.4                  | Mather    | matical analysis                               | 49 |

|           |      | 4.4.1    | Sinusoidal approximation                                      | 49 |

|-----------|------|----------|---------------------------------------------------------------|----|

|           |      | 4.4.2    | The output circuit analysis                                   | 52 |

|           |      | 4.4.3    | The input circuit analysis                                    | 54 |

|           | 4.5  | Char     | acteristic curves                                             | 57 |

|           | 4.6  | Desig    | gn procedure and example                                      | 58 |

| Chapter 5 | Simu | ılation  | and experimental results for the Dc-to-Ac                     | 61 |

|           | inve | rter top | ology                                                         |    |

|           | 5.1  | Modi     | fied dc-to-ac zero voltage switching inverter                 | 61 |

|           |      | topol    | ogy                                                           |    |

|           | 5.2  | Simul    | ation results for the dc-to-ac inverter                       | 61 |

|           |      | 5.2.1    | Schematic for simulation                                      | 61 |

|           |      | 5.2.2    | Simulation waveforms                                          | 63 |

|           |      |          | 5.2.2.1 Input inductor current i <sub>Lg</sub> and gate       | 63 |

|           |      |          | control voltage for switch S <sub>1</sub>                     |    |

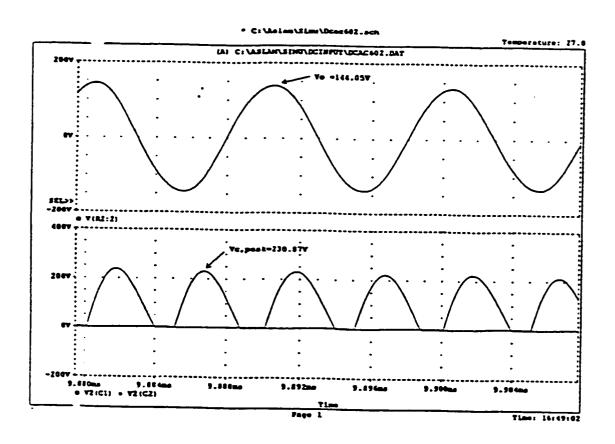

|           |      |          | 5.2.2.2 Output voltage Vo and voltages across                 | 64 |

|           |      |          | switches S <sub>1</sub> and S <sub>2</sub>                    |    |

|           | 5.3  | Experi   | imental results for the dc-to-ac inverter                     | 65 |

|           |      | 5.3.1    | Experimental waveforms                                        | 65 |

|           |      |          | 5.3.1.1 Gate control and voltage across switch S <sub>1</sub> | 65 |

|           |      |          | 5.3.1.2 Gate control pulses for switches $S_1$ and $S_2$      | 66 |

|           |      |          | 5.3.1.3 Gate control pulse of S1 and                          | 67 |

|           |      |          | output voltage v.                                             |    |

|            |       | 5.3.1.4 Gate control pulse of S <sub>1</sub> and output series  | 68 |

|------------|-------|-----------------------------------------------------------------|----|

|            |       | inductor current iLS                                            |    |

|            |       | 5.3.1.5 Gate control pulse of S <sub>2</sub> and input inductor | 69 |

|            |       | current i <sub>Lg</sub>                                         |    |

|            |       | 5.3.1.6 Gate control pulse of S1 and $V_{cpeak}$ of S2          | 70 |

|            | 5.4   | Comparison of simulation and experimental results               | 72 |

|            |       |                                                                 |    |

| Chapter 6  | Smal  | l signal modeling of the dc-to-ac resonant inverter             | 73 |

|            | 6.1   | Introduction                                                    | 73 |

|            | 6.2   | Basic concepts                                                  | 74 |

|            | 6.3   | State space averaging                                           | 76 |

|            |       | 6.3.1 Averaging technique                                       | 77 |

|            |       | 6.3.2 State variable perturbation                               | 83 |

|            | 6.4   | Derivation of transfer function                                 | 85 |

|            | 6.5   | Frequency response for various load values                      | 92 |

| Chapter 7  | Concl | lusions and future work                                         | 95 |

| References |       |                                                                 | 99 |

## LIST OF FIGURES

| 1.1(a) | Buck power factor correction topology                                  |

|--------|------------------------------------------------------------------------|

| 1.1(b) | Boost power factor correction topology                                 |

| 1.1(c) | Buck-boost power factor correction topology                            |

| 1.2    | Basic isolated boost derived ZVS converter                             |

| 1.3    | Modified basic isolated converter with active clamp                    |

| 1.4    | Modified basic isolated converter with output network                  |

| 1.5    | Boost derived resonant dc-to-ac inverter proposed                      |

| 2.1    | Basic isolated boost converter                                         |

| 2.2    | Steady state waveforms of the basic isolated boost converter           |

| 2.3    | Modified boost converter with active clamp circuit                     |

| 2.4    | Steady state waveforms for modified boost converter with clamp circuit |

| 2.5    | Modified ZVS boost converter with a small diode network at the output  |

|        | stage                                                                  |

| 2.6    | Steady state waveforms for the modified boost converter with an output |

|        | network                                                                |

| 3.1    | Basic isolated boost converter                                         |

| 3.2    | Simulation results for the isolated boost converter                    |

| 3.3    | Experimental waveforms for the isolated boost converter                |

| 3.4    | Modified boost converter with active clamp circuit                     |

|        |                                                                        |

| 3.5 | Simulation waveforms for the modified boost converter with active clamp                         |

|-----|-------------------------------------------------------------------------------------------------|

| 3.6 | Experimental results for the modified converter with active clamp circuit                       |

| 3.7 | Modified ZVS boost converter with a small diode network at the output                           |

|     | stage                                                                                           |

| 3.8 | Simulation results for modified boost converter with output network                             |

| 3.9 | Experimental waveforms for the modified boost converter with output                             |

|     | network                                                                                         |

| 4.1 | Dc-to-Ac ZVS converter with isolation                                                           |

| 4.2 | Typical steady state waveforms                                                                  |

| 4.3 | Modes of operation: a) Mode I(S1), b) Mode II(D2), c) Mode III(S2), d)                          |

|     | Mode IV(D1)                                                                                     |

| 4.4 | Primary voltage v <sub>p</sub> (t)                                                              |

| 4.5 | Equivalent output circuit                                                                       |

| 4.6 | Performance curves for the converter                                                            |

| 4.7 | Equivalent input circuit for Modes I and III                                                    |

| 4.8 | Characteristic curve for $V_{nc,peak}$ vs. $f_{ns}$ under different values of $Q_0$             |

| 4.9 | Characteristic curves for $V_{nc,peak}$ vs. $f_{ns}$ under different values of $f_{nor}$        |

| 5.1 | Dc-to-Ac ZVS inverter with isolation                                                            |

| 5.2 | PSPICE schematic for the dc-to-ac ZVS inverter                                                  |

| 5.3 | Simulation waveforms for input inductor current (i <sub>Lg</sub> )and S1 gate voltage           |

|     | $(V_{gS1})$                                                                                     |

| 5.4 | Simulation waveforms for output voltage (V <sub>o</sub> ) and voltage across S <sub>1</sub> and |

|     | $S_2$                                                                                           |

| 5.5  | Experimental waveforms for the gate control pulse and voltage across S <sub>1</sub>      |

|------|------------------------------------------------------------------------------------------|

| 5.6  | Experimental waveforms for the gate control pulses for S <sub>1</sub> and S <sub>2</sub> |

| 5.7  | Experimental waveforms for the gate control pulses for S <sub>1</sub> and output         |

|      | voltage v <sub>o</sub>                                                                   |

| 5.8  | Experimental waveforms for the gate control pulses for S <sub>1</sub> and S <sub>2</sub> |

| 5.9  | Experimental waveforms for the gate control pulses for $S_2$ and $i_{Lg}$                |

| 5.10 | Experimental waveforms for the gate control pulses for $S_1$ and $V_{cpeak}$ for         |

|      | $S_2$                                                                                    |

| 6.1  | Block diagram representation for power converter with transfer functions                 |

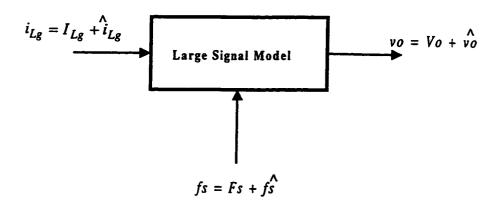

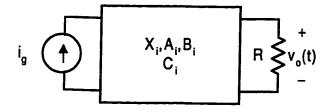

| 6.2  | Large signal model diagram representation for power converter                            |

| 6.3  | Block diagram representation for the dc-to-ac inverter                                   |

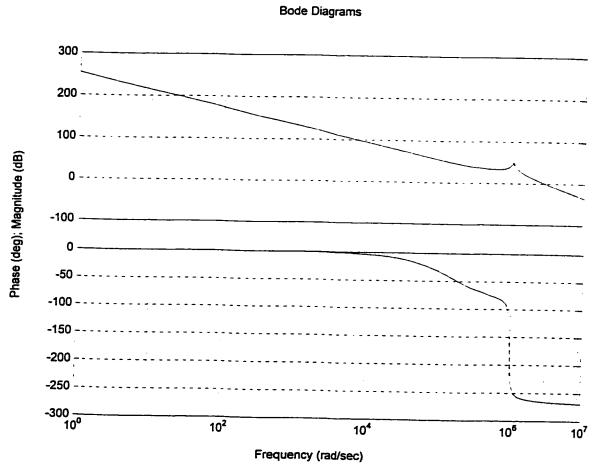

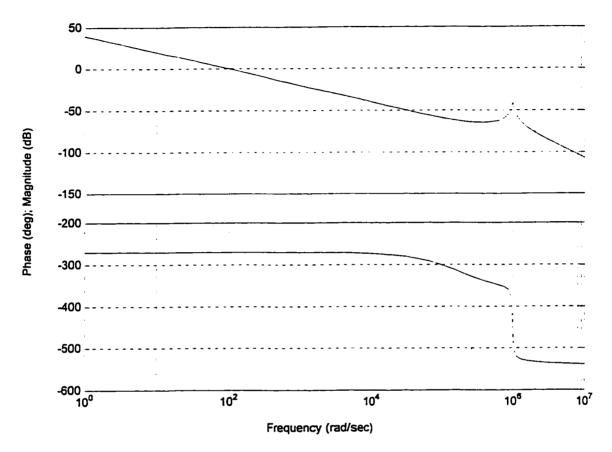

| 6.4  | Frequency response plot of the magnitude and phase of $H_l(s)$                           |

| 6.5  | Frequency response plot of the magnitude and phase of $H_2(s)$                           |

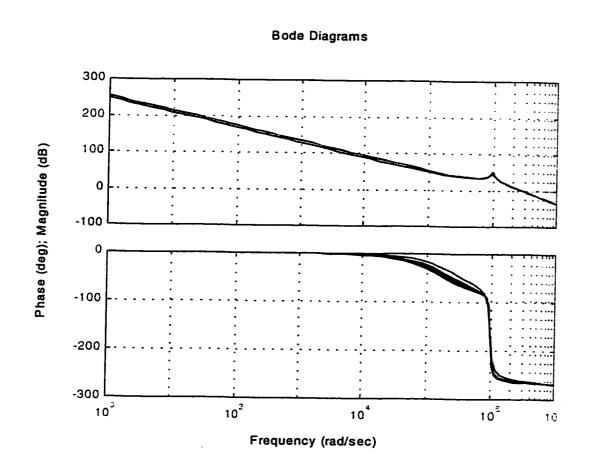

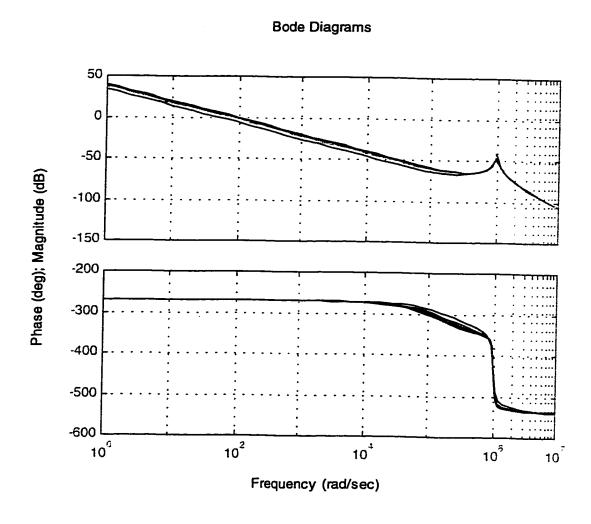

| 6.6  | Frequency response plot of the magnitude and phase of H <sub>I</sub> (s) for different   |

|      | load values                                                                              |

| 6.7  | Frequency response plot of the magnitude and phase of H <sub>2</sub> (s) for different   |

|      | load values                                                                              |

## LIST OF TABLES

- 3.1 Voltage stress across switches

- 3.2 Current through switches

- 3.3 Soft switching, complexity and efficiency

- 4.1 Parameters from design procedure

- 5.1 Simulation and experimental parameters results

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 BACKGROUND

Power electronics, which is multi-disciplinary in nature, principally deals with energy processing and control of power flow by using power semiconductor devices. Generally the power processor circuits rely on solid-state semiconductor devices operating on switched mode, i.e. either on or off. Ideally these switches should have no voltage drop when on and carry no current when in the voltage blocking stage. [13,14,15] The power electronic circuits are used to process power efficiently using semiconductor devices, modern control techniques, mathematical tools and computer simulation. The processing involves power conversion (dc-to-ac, ac-to-dc, dc-to-dc and ac-to-ac) for industrial, commercial and residential application. Because of a continuing demand for smaller, lighter and more efficient power processing equipment, significant improvements in circuit topologies, control techniques, simulation tools and semiconductor devices have been reported in recent years.

[1-10] Converters will be used to refer to single power conversion stage to perform any of the following functions defined by the nature of its input and output: ac to dc, dc to ac, dc to dc and ac to ac.

Due to switching, power electronic circuits normally exhibit square current and voltage waveforms. Also they produce nonlinearities, which introduce harmonic frequency components resulting in waveform distortion and reduction in power factor. Power factor is defined as the ratio of the real power to the apparent power in the circuit. Power factor can be enhanced by either passive elements like inductor and capacitors, which introduce phase shifts in the current waveforms resulting in unity power factor angle, or by active switching circuits that are used to program input current waveform to follow the line voltage. Improvement of power factor in switching power electronic circuits also implies reducing the total harmonic distortion.[3-10]

The reduction of power factor caused by switching circuits causes the power electronic equipment to get approximately two-thirds of the power available at the mains [4]. Due to the increase of power electronic equipment connected to the utility system, various national and international agencies have been considering limits on harmonic current injection to maintain good power quality. Various standards and guidelines are established that specify limits on the magnitudes of harmonic currents and harmonic voltage distortion at different harmonic frequencies. [24]

Efforts to solve the problem of poor power factor have been made for many years.

[2-10] Generally, two methods are used for power factor correction: passive and active methods. The passive methods used implementing passive elements, like inductors and capacitors, only adjust the phase difference in the current and voltage waveforms. The overall energy efficiency remains the same because of some losses occurring in the inductor. This

method is good for linear systems but not for dc-to-dc nonlinear systems. The disadvantages of this method are cost, size and losses. [6]

The second method used is the active shaping of the input line current. This method uses different types of active power converter to achieve unity power factor. The choice of the electronic power converter used is based on the following considerations:

- (1) The need for electrical isolation between the utility input and the output of the power electronic system. In some cases, this can be provided in the second converter stage as in the switch-mode dc power supplies.

- (2) In most applications it is desirable or acceptable to have regulated dc output voltage at a higher voltage than the maximum of the ac input. Hence, boost converters can be used in these applications.

- (3) The cost, power losses, and size of the current shaping circuit should be as small as possible.

Since the topologies here belong to two classes of power electronic circuits, it will be useful to review the different classes of power circuits. The power converters can be generally classified as: [15]

- i) Ac-to-dc converters (Rectifiers): These converters have used thyristors with phase control and ac line commutation to convert ac-to-dc power for applications like dc drives and electro-chemical processes.

- ii) Ac-to-ac converters (Ac controllers or Cycloconverters) Thyristor or triac ac voltage controller (same output frequency) implementing phase control is widely used in applications like heating control, light dimming control etc.

- Dc-to-ac converters (Inverters): These inverters are generally classified as voltage-fed and current-fed types primarily used in ac motor drives, UPS (Uninterruptible power supplies), and induction heating. The voltage-fed type inverter is the most popular for industrial applications.

- iv) Dc-to-dc converters (Choppers): They convert unregulated dc voltage to a regulated or controlled dc voltage at different level commonly used in dc motor drives and switching mode power supplies. These types of converters are further classified as:

- 1) PWM type converter, which can be further, classified as buck, boost or buck-boost type. A single-quadrant drive uses buck converter; a two-quadrant drive uses buck and boost types in combination, whereas a four-quadrant drive uses an H-bridge that uses buck and boost functions. High power converters use an H-bridge that provides buck and boost functions for either direction of rotation. High power converters generally use BJT, IGBT, or GTO switches with up to several kHz switching frequency, and low power low voltage converters use power MOSFETs at much higher frequency.[15]

- 2) For higher switching frequencies, resonant and soft-switching converters are used. There is reduction in switching losses but there is an increase in magnetic and capacitor losses. There is a LC tank circuit that generates quasi-sine waves that permits zero-voltage and zero-current switching. At

very high frequencies in the MHz range the tank elements are so small that the parasitic elements are used for this purpose.

#### 1.1.1 Basic Active Power Factor Correction Circuits

There are three basic active power factor correction circuits, namely, Buck, Boost and Buck-Boost topologies. These topologies use current control or voltage control mode to achieve the goal of power factor correction. Input current or voltage is used as the parameter to be controlled in this control strategy. Also another classification of control methods is based on the continuity of the input current through the converter. The two methods are CCM (continuous-conduction mode) and DCM (discontinuous-conduction mode). [16] CCM control requires that the current through the converter be continuous at every instant. In other words, the value of the current can be calculated at a given instance in time. This is not a requirement in DCM control that makes it a simpler control implementation.

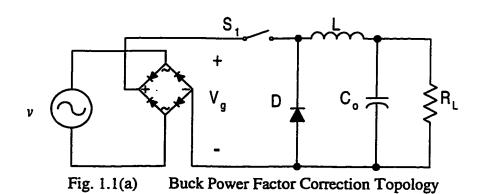

#### a. Buck power factor correction circuit

Figure 1.1(a) shows a typical buck converter with ac input and a full-wave rectifier.

The operation of the converter is the same as a dc-to-dc buck converter. The input to the converter is an unregulated dc input (which is the output of the full-wave rectifier). The control purpose is different for duty cycle control of this configuration. The transfer function, H(s), and input impedance,  $Z_{in}(s)$ , of this configuration are given by

$$H(s) = \frac{d}{s^2 L C_o + s L / R_L + 1};$$

(1)

$$Z_{in}(s) = \frac{R_L}{d^2} \frac{s^2 L C_o + s L / R_L + 1}{s R C_o + 1}$$

(2)

Proper control of duty cycle d is used to achieve pure resistive input impedance to obtain a unity power factor in practice. [2,16,22] Generally voltage mode control is used for this topology. The voltage of the input inductor or capacitor is controlled by the duty cycle in this voltage mode control technique.

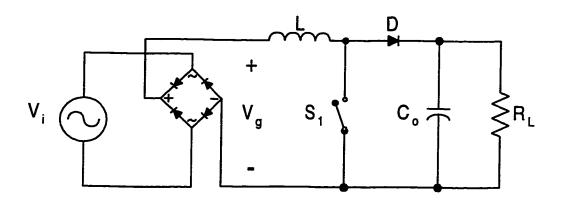

#### b. Boost power factor correction circuit

Fig. 1.1(b) Boost power factor correction topology

Figure 1.1(b) shows a typical boost power factor correction topology. The input to the boost converter is unregulated dc output from the full-wave rectifier.

The transfer function, H(s), and input impedance,  $Z_{in}(s)$ , of this configuration are given by

$$H(s) = \frac{1/d'}{s^2(L/d^2)C_o + s(L/d^2)/R_L + 1};$$

(3)

$$Z_{in}(s) = d^{2}R_{L} \frac{s^{2}(L/d^{2})C_{o} + s(L/d^{2})/R_{L} + 1}{sR_{L}C_{o} + 1}$$

(4)

where d'=1-d

The equivalent inductance of the topology is controlled by the duty cycle. Current control method is used in this configuration which programs the input current to achiever unity power factor. Therefore, there is control over the magnitude and phase of the impedance. This means better control to achieve "pure resistive impedance" and unity power factor.

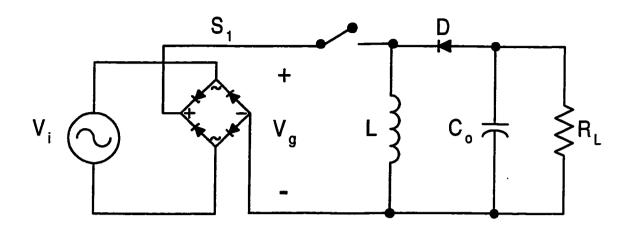

#### c) <u>Buck-Boost power factor correction circuit</u>

Fig. 1.1(c) Buck-Boost power factor correction topology

Figure 1.1(c) shows the buck-boost power factor correction topology. The transfer function, H(s), and input impedance,  $Z_{in}(s)$ , of this configuration are given by,

$$H(s) = \frac{d/d}{s^{2}(L/d^{2})C_{o} + s(L/d^{2})/R_{L} + 1};$$

(5)

$$Z_{in}(s) = \left(\frac{d'}{d}\right)^2 R_L \frac{s^2 (L/d^2) C_o + s(L/d^2) / R_l + 1}{s R_L C_o + 1}$$

(6)

Again, this topology uses the control of the duty cycle to achieve the current or voltage control to achieve unity power factor. Buck-boost topology combines the advantages of the buck and boost topologies.

#### 1.2 Proposed Work

The topologies presented in this dissertation are based on the boost configuration operating in continuous conduction mode. The proposed work is divided into two parts. The purpose of the first part is to analyze the three proposed different dc-to-dc power converter

topologies. The first topology is a basic isolated modified converter. The equivalent circuit of the basic isolated converter is shown below in Figure 1.2. [11] The steady state waveforms, simulation results, circuit performance parameters and experimental results are discussed.

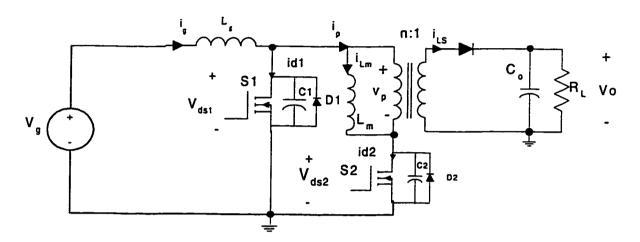

Figure 1.2 Basic Isolated Boost derived ZVS converter

This topology is derived from the basic boost topology having a transformer to isolate the output and a second switch is introduced to provide transformer core-resetting. The performance parameters mainly voltage stress across the two switches, are discussed. The analysis shows that the primary switch is hard switched while the secondary switched, switched complimentary to the primary switch, achieves zero-voltage switching.

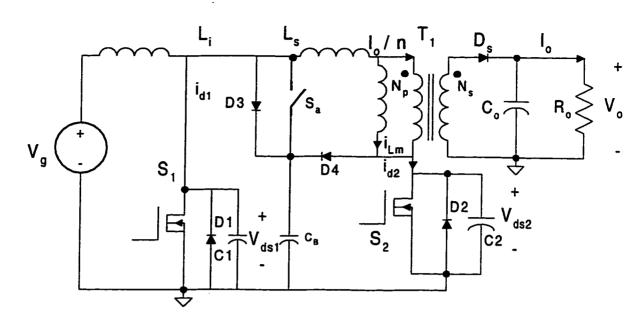

The second topology is a boost derived modified converter using an active clamp circuit to clamp the voltage across the secondary switch. This circuit is shown in Figure 1.3.

Figure 1.3 Modified basic isolated converter with active clamp

It will be shown that the secondary switch in Fig. 1.3 operates at zero-voltage switching (ZVS) but the primary switch is still hard switched. The current rating of the secondary switch is much lower than the primary switch.

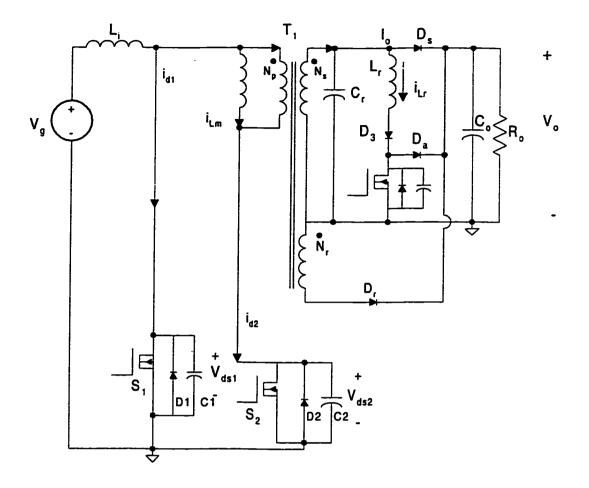

The third converter is the modified basic converter with an additional winding in the isolation transformer and a diode network at the output side of the converter as shown in Fig. 1.4.

Figure 1.4 Modified basic isolated converter with output diode network

Zero-voltage switching is achieved for both the primary and secondary switches. Switching losses are reduced as a result of ZVS for the primary switch also. There is also reduction in voltage peaks across the secondary switch. The ZVS switching for both reduces switching providing efficiency of about 92%. [12] The Pulse-width modulation technique is used for all these converters. These converters have potential applications in power factor correction, which can be implemented with relative ease

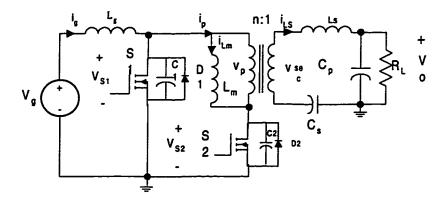

The second part of the proposed work is dc-to-ac resonant inverter used to produce high frequency ac output. Resonance technique is used similar to the dc-to-dc converters. Steady-state analysis using state-space approach along with PSPICE simulation is completed. Mathematical analysis is done with sinusoidal approximation for the secondary voltage across the transformer. Characteristic performance curves are derived and developed with the help of MATLAB. Comparison of simulation and theoretical mathematical values is successfully performed. The dc-to-ac inverter proposed is shown in Figure 1.5 is a modified basic converter with a LCC (series-parallel resonant tank) circuit at the output side of the inverter. The LCC tank provides symmetrical output voltage from a dc source at the input. The parasitic capacitance's across the two switches are used along-with the magnetizing inductance of the transformer to provide ZVS for both the switches.

Figure 1.5 Boost derived resonant dc-to-ac inverter proposed

The closed loop circuit for this inverter is frequency modulated, as ZVS is hard to maintain with the PWM approach under greater load variations. The voltage -controlled

oscillator is used in place of the PWM circuit to achieve the desired control maintaining the resonance.

For the above described dc-to-dc converters and dc-to-ac inverter, mathematical analysis, PSPICE simulation and experimental results will be presented. Comparison of the theoretical, simulation and experimental results will be made.

Chapter 2 outlines the steady-state waveforms, principle of operation of the three dc-to-dc converter topologies. Chapter 3 explains the simulation and experimental waveforms for the three dc-to-dc converters. Comparison of the important parameters for the three topologies is given in this chapter. Chapter 4 gives the dc-to-ac inverter steady-state analysis with waveforms. A steady-state mathematical model is presented along with the sinusoidal approximations. Performance curves of the inverter is presented that are used to present a detailed design procedure for an example of the inverter. The simulation and experimental results for the inverter topology will be given in Chapter 5. A table making comparison between the simulation and experimental results. Chapter 6 shows the small signal model developed for the dc-to-ac inverter. The frequency response plots of the input-to-output and control-to-output transfer functions are given for various load conditions. Conclusions are made, for the proposed improved resonant power converters, in Chapter 7.

#### **CHAPTER 2**

#### FAMILY OF ISOLATED DC-TO-DC

#### ZERO-VOLTAGE SWITCHING CONVERTERS

#### 2.1 Introduction

Electrical isolation between the input and output load is required in many power electronics applications. High frequency transformers in series with a switch are used to achieve this requirement. The challenge with implementing this method is the saturation problem of the transformer. This requires core resetting when the series switch is off which results in higher voltage stress across the switch and higher turn-off loss [23]. This is due to the energy stored in the transformer. An additional reset circuit with voltage clamp will reduce the voltage stress across the secondary switch.

Zero-voltage switching (ZVS) isolated boost converters are analyzed and investigated in this chapter. The magnetizing inductance of the isolation transformer and the parasitic capacitance of the switches resonate to provide ZVS for the secondary switches. The steady-state analysis will be presented to explain the circuit operation. The converters are simulated using PSPICE. The simulation and experimental results of these three converters are presented and performance comparison is done in Chapter 3.

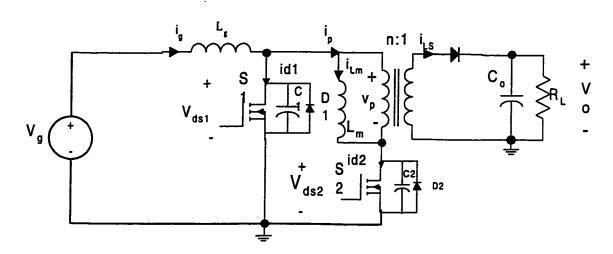

#### 2.2 Topology 1: Basic isolated boost converter

Figure 2.1 shows the circuit for the basic isolated boost converter. A series switch  $S_2$  is connected in series with the isolation transformer to allow core resetting. Switch  $S_1$  is the primary switch of the boost converter shown. The magnetizing inductance  $L_m$  of the transformer resonates with the parasitic capacitance  $C_2$  of switch  $S_2$  to provide ZVS for  $S_2$ . The transformer provides energy transfer from the input inductor  $L_g$  to the output.

Figure 2.1 Basic isolated boost converter

The steady-state waveforms for this converter are shown in Figure 2.2.

Figure 2.2 Steady state waveforms of the basic isolated boost converter

Switch  $S_2$  turns on at  $t_0$  and  $v_{ds1}$  reaches its maximum value of  $nV_o$  and goes to zero when  $S_1$  turns on at  $t_1$ . During this time  $v_{ds2}$  remains at zero. At  $t_1$   $v_{ds2}$  resonates sinusoidally to its maximum and goes down to zero at time  $t_3$ . At this time diode  $D_2$  turns on and clamps the  $v_{ds2}$  at zero and current iL<sub>m</sub> remains at its

negative minimum. At time  $t_4$ ,  $S_2$  turns on again and starts another cycle of the converter where  $i_{Lm}$  increases back to its positive maximum.

By equating magnetizing energy equal to energy storage in  $C_2$ , the maximum voltage stress  $V_{ds2,max}$ , is given by,

$$V_{ds\ 2.\,\text{max}} = n\,\pi\,V_0\,(1-D\,)\,\frac{\omega_o}{\omega_s}$$

where  $\omega_s$  and  $\omega_o$  are the switching and radial resonant frequencies defined as,

$$\omega_{s} = \frac{T_{s}}{2\pi}, \ \omega_{o} = \sqrt{\frac{1}{L_{m}C_{2}}}$$

The condition on ZVS operation for  $S_2$  is expressed by

$$\frac{\omega}{\omega} \leq 2 D \tag{2.2}$$

From Equation (2.2), it is seen that  $S_2$  operates at ZVS for a certain of duty cycle D and  $S_1$  operates with hard switching which causes high switching losses. The disadvantage with this converter is that, it is difficult to keep  $S_2$  operating with ZVS and keep the voltage it to a minimum over a wide load range [11].

#### 2.2.1 Modes of Operation

Mode I:  $t_0 < t < t_1$  [S<sub>2</sub> ON, S<sub>1</sub> OFF]

There are four modes of operation over one switching cycle as discussed below. Voltage across  $S_1$  is nVo (reflected output voltage where n is the isolating transformer turns ratio). Current  $i_{d2}$  flows through  $S_2$  and diode  $D_2$  is not "on". Magnetizing current  $i_{Lm}$  is increasing linearly and  $i_{d2}$  is decreasing linearly.

## Mode II: $t_1 < t < t_2$ [S<sub>1</sub> ON, S<sub>2</sub> OFF]

Input inductor  $L_m$  and  $C_2$  resonate causing voltage across  $S_2$   $v_{ds2}$  to increase sinusoidally and reaching its peak at  $t_3$ . Current through  $S_1$  ramps up sinusoidally and  $i_{Lm}$  decreases sinusoidally.

## Mode III: $t_2 < t < t3$ [S<sub>1</sub> ON, S<sub>2</sub> OFF]

Voltage across  $S_2$  decreases from maximum to zero sinusoidally at  $t_3$ .  $i_{Lm}$  is decreasing to its negative maximum. Here the magnetizing current is changing polarity which resets the output isolating transformer core (avoids saturation of transformer core).

#### Mode IV: $t_3 < t < t_4$ [S<sub>1</sub> ON, S<sub>2</sub> OFF]

Diode  $D_2$  turns "on" as voltage across  $S_2$  is zero and current across it is negative. This clamps the voltage  $v_{ds2}$  to zero providing Zero-voltage-switching (ZVS) for switch  $S_2$ . The proper duty cycle design of this converter is critical to ensure the ZVS for  $S_2$ . There should be enough time for the positive half of the sinusoid of  $v_{ds2}$  to come back to zero to ensure that the voltage across  $S_2$  is zero when it is turned "on" in the next cycle.

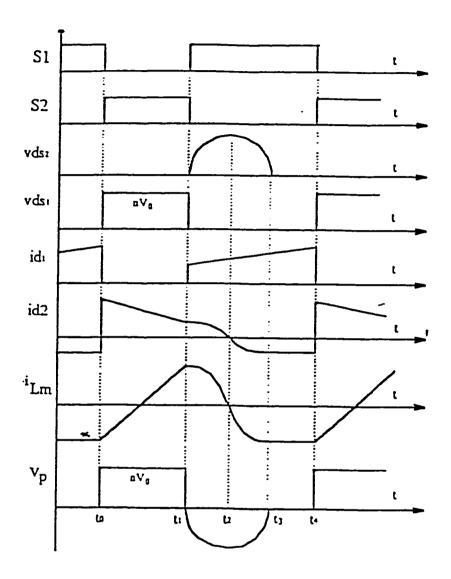

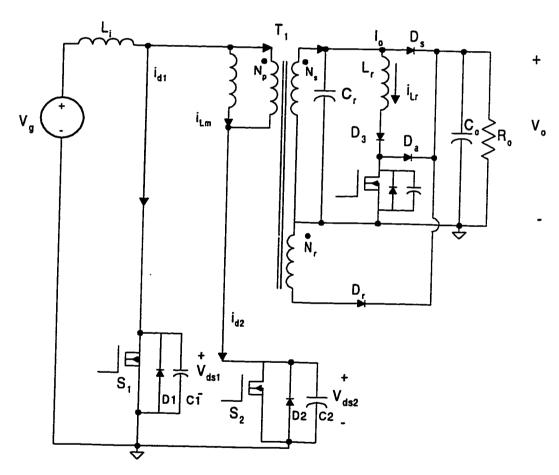

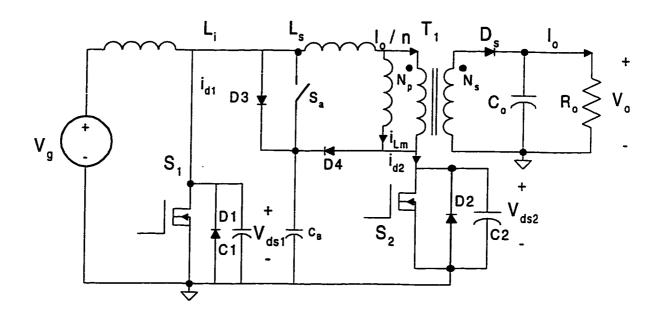

## 2.3 Topology 2: Modified ZVS boost converter with active clamp circuit

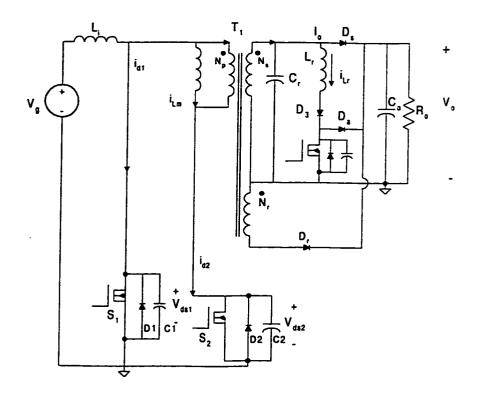

Figure 2.3 shows the modified boost converter with clamp circuit.  $S_a$ ,  $D_3$ ,  $D_4$  and  $C_B$  form the clamp circuit to reduce the voltage across  $S_2$ . There is inclusion of an additional switch, which makes this converter more complex and costly [17].

Figure 2.3 Modified boost converter with clamp circuit

Figure 2.4 shows the typical waveforms of the modified boost converter showing the clamped voltage across S<sub>2</sub>.

#### 2.3.1 Modes of operation

#### Mode $I: t_0 < t < t_1$ [S<sub>1</sub> OFF, S<sub>2</sub> and S<sub>a</sub> ON]

During  $t_0$ - $t_1$ ,  $S_1$  is turned off and  $S_2$  and  $S_a$  are turned on. The excess energy stored in  $C_B$  can is delivered to the output through the transformer so that the voltage across  $C_B$  can be balanced.

## Mode II : $t_1 < t < t_2$ [S<sub>1</sub> ON, S<sub>2</sub> and S<sub>a</sub> OFF]

At time  $t_1$ ,  $S_1$  is turned on and  $S_2$  turned off. The magnetizing current  $i_{Lm}$  sinusoidally decreases, due to the resonance between the magnetizing inductance  $L_m$  and  $C_2$ , and during this time the input inductor current decreases through  $S_1$ .

The magnetizing current  $i_{Lm}$  charges  $C_2$  which causes vds2 to increase sinusoidally and will be clamped by voltage  $C_B$  at  $t_2$ , where  $D_4$  starts conducting.

## Mode III: $t_2 < t < t_4$ [S<sub>1</sub> ON, S<sub>2</sub> and S<sub>a</sub> OFF]

After  $t_2$ , the magnetizing current decreases linearly since a negative  $nV_0$  is applied to the primary winding of the transformer. Voltage across  $S_2$  decreases to zero at  $t_4$  and  $i_{Lm}$  flows through  $D_2$  at its negative maximum constant value. Consequently  $S_2$  is turned on at zero-voltage.

## Mode IV: $t_4 < t < t_5$ [S<sub>1</sub> ON, S<sub>2</sub> and S<sub>a</sub> OFF]

Current  $i_{d2}$  is at negative maximum and  $i_{Lm}$  is constant at negative maximum. Voltage across  $S_2$  is clamped at zero by diode  $D_2$ .  $S_1$  is turned off at  $t_5$  while  $S_2$  and  $S_a$  are turned on.  $V_{ds1}$  is clamped to  $V_{CB}$  and then clamped to the reflected output voltage  $nV_0$ . Without  $C_B$  and  $D_3$ ,  $V_{ds1}$  would have high ringing transient voltage due to the resonance between parasitic capacitance  $C_1$  and the leakage inductance of the transformer. From Figure 2.6, it is observed that  $S_2$  can be operated at ZVS while  $S_1$  is still hard switched.

Figure 2.4 Steady state waveforms for modified boost converter with clamp circuit.

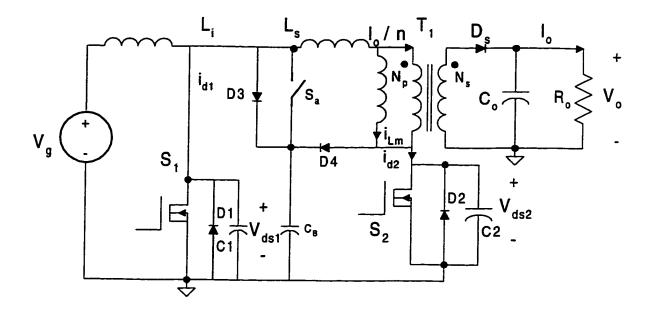

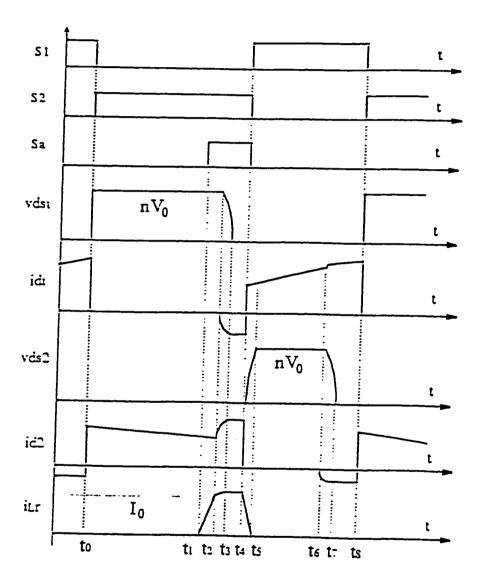

## 2.4 Topology 3: Modified boost converter with network on the output side

The next topology is a modified boost converter with a network on the output side of the transformer. An extra winding  $N_r$  and a diode  $D_r$  network is introduced for transformer core resetting. This also suppresses the voltage stress across  $S_2$  and transfers partial magnetizing energy to the output. The network consists of a resonant inductor  $L_r$ , an auxiliary switch  $S_a$ , diode  $D_a$  and resonant capacitor  $C_r$ . This network is implemented to achieve ZVS for switch  $S_1$ . Figure 2.5 shows the circuit diagram of this converter.

Figure 2.5 Modified ZVS boost converter with a small diode network at the output stage.

The steady-state waveforms for this converter are shown in Figure 2.6 below. At time  $t_1$ , the auxiliary switch  $S_a$  is turned on. The duration of time from  $t_1$  to  $t_2$  is given by

$$t_2 - t_1 = \frac{I_o}{V_o / L_r}$$

Figure 2.6 Steady state waveforms for the modified boost converter with an output network

The current through the inductor  $L_\tau$  increases linearly upto  $I_o$  while the current through  $D_S$  decreases linearly and  $D_S$  will be naturally turned off at  $t_2$  when  $i_{L_r} = I_o$ . The current through the resonant inductor  $L_\tau$  increases sinusoidally while the resonant capacitor  $C_\tau$  discharges during this period.  $C_\tau$  comprises of the output capacitance of  $S_1$ , the junction capacitance of diode  $D_S$ . The resonant voltage and current can be expressed as

$$v_{cr} = V_o \cos \omega_{o2} (t - t_2) \tag{2.3}$$

$$i_{Lr} = I_o + \frac{V_o}{Z_o} \sin \omega_{o2} (t - t_2)$$

(2.4)

where  $\omega_{o2}=1/\sqrt{L_rC_r}$  and  $Z_o=\sqrt{\frac{L_r}{C_r}}$ . Energy stored in these parasitic capacitors is

completely transferred to the inductor  $L_r$  at  $t_3$ , where the voltage across  $C_r$  and  $D_1$  decrease to zero and  $D_1$  begins to conduct. The resonant inductor current  $i_{Lr}$  flows through the secondary winding at a constant value. In order to achieve ZVS, the turn-on gate signal S1 should be applied during this period. Both switches operate at ZVS reducing switching losses. It is seen that ZVS is achieved for  $S_1$  with the help of  $L_r$ ,  $S_a$ , and  $C_r$  while ZVS of  $S_2$  is achieved by resonance of  $L_m$  and  $C_2$ . The voltage across  $S_2$  is clamped to  $nV_0$  through the extra secondary winding  $N_r$  and  $D_r$  [17].

# 2.4.1 Modes of operation

#### Mode I $t_0 < t < t_1$

In steady state, there are eight modes of operation as discussed below.  $S_2$  is turned on and  $S_1$  is turned off at  $t_0$ . Diode  $D_s$  is on while clamp diode  $D_r$  is off. Power is transferred to the output through the transformer in this mode. The duration of this mode is given by  $t_{1-2} = \frac{I_o}{V_o/I_{cr}}$

# Mode II $t_1 < t < t_2$

At t1 auxiliary switch  $S_a$  is turned on. The current through  $L_r$  ramps up linearly until it becomes equal to  $I_o$  at time  $t_2$ , where diode  $D_S$  will be turned off.

#### Mode III $t_2 < t < t_3$

Inductor  $L_r$  and capacitor  $C_r$  start to resonate at time  $t_2$ . Current through  $L_r$  increases in sinusoidal form while voltage across  $C_r$  decreases. At t3, voltages  $v_{cr}$  and  $v_{ds2}$  decrease to zero and body diode  $D_1$  turns on to clamp the voltage across  $S_2$  to zero. The duration of this mode is determined by

$$t_{2-3} = \frac{\pi}{2} \sqrt{L_r C_r}$$

where  $C_r = C_1 + C_{tr} + C_j$

$$C1 = capaci \tan ce \ of \ switch \ S_1$$

$$C_{tr} = capaci \tan ce \ of \ the \ transformer$$

$$C_j \ is \ the \ junction \ capaci \ tan \ ce \ of \ the \ D_s$$

#### Mode IV $t_3 < t < t_4$

Body diode D1 of switch S1 is on. The switch S1 is turned on during this time to achieve ZVS.

# Mode V $t_4 < t < t_5$

At  $t_4$ ,  $S_2$  and  $S_a$  are turned off when  $S_1$  is turned on. Current through  $L_r$  decreases to zero while voltage across  $S_a$  clamps to  $V_o$  due to  $D_a$  being on. Magnetizing current iLm linearly charges C2 capacitor. This mode is on until  $t_5$  when  $v_{ds2}$  ramps up to  $nV_o$ , when  $D_r$  turns on at ZVS.

# Mode VI $t_5 < t < t_6$

When  $D_r$  is on at  $t_5$ , the voltage across  $S_2$  clamps to  $nV_o$ . Energy stored in  $L_m$  is transferred to the load through winding  $N_r$  and diode  $D_r$ . This mode stays on until  $i_{Lm}$  becomes zero when  $L_m$  and  $C_2$  start to resonate.

#### Mode VII $t_6 < t < t_7$

When  $L_m$  and  $C_2$  start to resonate, at  $t_6$ , the energy is transferred from  $C_2$  to  $L_m$ , which makes  $i_{Lm}$  negative at  $t_7$ . Time  $t_7$  is determined by the time taken for vds2 to go to zero.

#### Mode VIII $t_7 < t < t_8$

At  $t_7$ ,  $v_{ds2}$  is zero and diode  $D_2$  turns on. This makes  $i_{Lm}$  a constant in this mode. Therefore, switch  $S_2$  operates at ZVS when it turns on at  $t_8$  [11].

#### **CHAPTER 3**

# SIMULATION AND EXPERIMENTAL RESULTS FOR THE DC-TO-DC CONVERTER TOPOLOGIES

In this chapter, we will give the detailed simulation and experimental results for the three dc-to-dc topologies discussed in chapter 2. In these circuits, in order to simplify, we use a constant input  $V_g$ . The line current is in continuous conduction modes and can be programmed to achieve unity power factor.

# 3.1 Basic Isolated Boost converter

Figure 3.1 Basic isolated boost converter

# 3.1.1 Simulation results

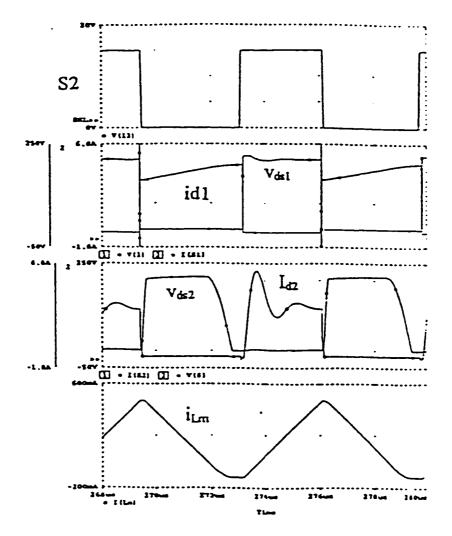

The simulation results for the basic converter shown in Figure 2.1 is shown in Figure 3.2. The voltage across  $S_2$  is high with ZVS and  $S_1$  is hard switched by high frequency ringing voltage after  $S_1$  is turned off. Magnetizing current  $I_{Lm}$  changes polarity to ensure transformer core resetting by varying from its positive maximum to its negative minimum and back.

Figure 3.2 Simulation results for the isolated boost converter

# 3.1.2 Experimental Results

Let us consider a specific design example with the following design specifications:

$V_0$ =200V Lm=415uH Lg=380 $\mu$ H

C1=C2=1.15nF Co=650 $\mu$ F Ro=400 $\Omega$

n=15/14

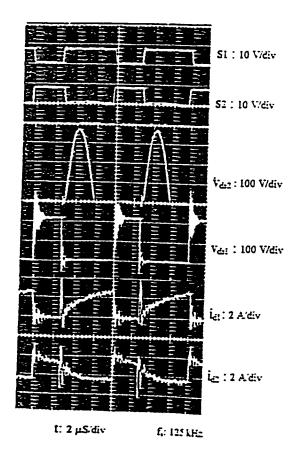

The experimental waveforms for the basic isolated boost converter are shown in Figure 3.3. The experimental waveforms closely match the simulation results.

Figure 3.3 Experimental Waveforms for the isolated boost converter

#### 3.2 Modified boost converter with active clamp circuit

The modified boost converter with active clamp circuit is shown below in Figure 3.4.

Figure 3.4 Modified boost converter with active clamp circuit

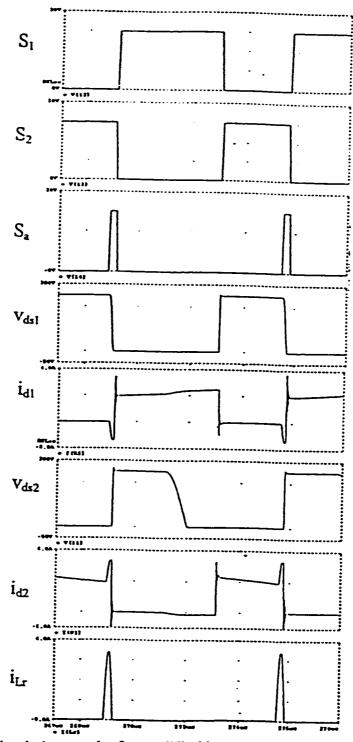

# 3.2.1 Simulation results

The simulation waveforms for this modified boost converter with active clamp is shown in Figure 3.5. It is seen that the volatge across  $S_1$  is hard switched while operating  $S_2$  at ZVS. The low frequency ringing current in  $i_{d2}$  is due to the discharge of capacitor  $C_B$  through the leakage inductance to the load. The voltage  $v_{ds2}$  is clamped to the reflected output voltage n  $V_o$ . The complementary switching of the two switches is seen and the input current is continuous as expected from the designed converter.

Figure 3.5 Simulation waveforms for the modified boost converter with active clamp.

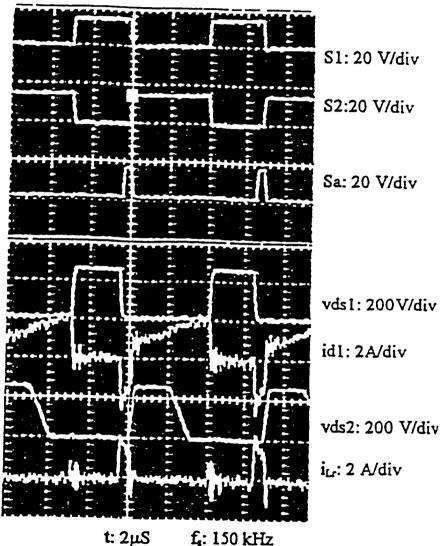

# 3.2.2 Experimental results

Let us consider a specific design example with the following design specifications:

| V <sub>o</sub> =200V | Lm=535uH | Lg=380μH | C2=680pF               |

|----------------------|----------|----------|------------------------|

| Co=650μF             | Ro=400Ω  | n=15/12  | $f_S = 150 \text{kHz}$ |

The experimental waveforms for the basic isolated boost converter are shown in Figure 3.6.

Figure 3.6 Experimental results for the modified converter with active clamp circuit

#### 3.3 Modified boost converter with output network

The modified boost converter with output network is shown below in figure 3.7

Figure 3.7 Modified ZVS boost converter with a small diode network at the output stage.

#### 3.3.1 Simulation Results

Simulation results for this topology is shown in Figure 3.8. Voltage  $v_{dS1}$  is not ringing compared to the basic isolated boost converter. A high current pulse  $i_{d2}$  exists during the transition period. Both  $S_1$  and  $S_2$  are operating at Zero-voltage-switching. Most of the waveforms compare to the basic boost topology except

during the transition time when  $i_{d2}$  is a high current pulse compared to the basic topology.

Figure 3.8 Simulation results for modified boost converter with output network

#### 3.3.2 Experimental Results

Specifications:

Lm=535 $\mu$ H Lr=6 $\mu$ H C1=C2=450pF Ro=266 $\Omega$

Co= $650\mu$ H n=15/14 fs=150kHz

The experimental waveforms for the modified boost converter with output network are shown below in Figure 3.9.

igura 2 0 Evnarimental Wayefarma for the market 11

Figure 3.9 Experimental Waveforms for the modified boost converter with output

network

Both switches operate at ZVS with minimized voltage stresses. The converter efficiency is 92% with less power loss.

# 3.4 Comparison of the three topologies

Tables 3.1 and 3.2 summarize the parameters of comparison for the three converters for voltage and current stresses, respectively.

Table 3.1: Voltage Stress of switches

| Topology | Basic Converter        | Converter with | Converter with  |

|----------|------------------------|----------------|-----------------|

|          | Fig. (3.1)             | active clamp.  | output network. |

| Switch   |                        | Fig. (3.4)     | Fig. (3.7)      |

| $S_{I}$  | nVo high freq. Ringing | $nV_0$         | $nV_o$          |

| $S_2$    | $nV_o(1-D)f_of_s$      | $nV_o$         | $nV_o$          |

| $S_a$    | NA                     | $nV_o$         | $nV_o$          |

Table 3.2: Current Stress through switches

| Switch   | Basic Converter              | Converter with active                 | Converter with output                                    |

|----------|------------------------------|---------------------------------------|----------------------------------------------------------|

| Topology | Fig. (3.1)                   | clamp. Fig. (3.4)                     | network. Fig. (3.7)                                      |

| $S_{t}$  | $I_i + \frac{DV_sT_s}{2L_i}$ | $I_i + \frac{DV_sT_s}{2L_i}$          | $I_i + \frac{DV_sT_s}{2L_i}$                             |

| $S_2$    | $I_i + \frac{DV_sT_s}{2L_i}$ | $I_i + \frac{DV_sT_s}{2L_i} + I_{CB}$ | $I_i + \frac{DV_sT_s}{2L_i} + V_o\sqrt{\frac{C_r}{L_r}}$ |

| $S_a$    | NA                           | $I_{CB}$                              | $I_o + V_o \sqrt{\frac{C_r}{L_r}}$                       |

Table 3.3 compares the performance of these topologies with respect to soft-switching and complexity.

Table 3.3: Soft switching, complexity and efficiency

| Topology               | Basic Converter | Converter with     | Converter with  |

|------------------------|-----------------|--------------------|-----------------|

| Parameter              | Fig. (3.1)      | active clamp. Fig. | output network. |

|                        |                 | (3.4)              | Fig. (3.7)      |

| Switch: S <sub>I</sub> | Hard switched   | Hard switched      | ZVS             |

| $S_2$                  | ZVS             | ZVS                | ZVS             |

| $S_a$                  | NA              | ZCS                | ZCS             |

| Circuit Complexity     | Simple          | Medium             | Medium          |

| Efficiency             | Medium          | Medium             | Higher          |

#### 3.4.1 Basic Isolated Boost Converter

The disadvantage of this converter is higher switching losses and high voltage stress due to hard switching of  $S_1$  and resonance between the magnetizing inductance and parasitic capacitance of switch  $S_2$ . Switch  $S_2$  may lose its soft switching ability due to an incorrect duty ratio. To keep  $S_2$  in soft switching mode over a wide range,  $S_2$  may be subjected to significant voltage stress. This is a simple configuration with lower cost. The efficiency is about 88%.

# 3.4.2 Modified Boost Converter with active clamp circuit

This configuration has less voltage stress on switch  $S_2$  because of the active clamp circuit. The voltage across  $S_2$  is clamped at the reflected output voltage  $nV_o$  (n is transformer turns ratio). There is an added current stress in  $i_{d2}$  due to the low frequency ringing current caused by the discharge of  $C_B$  through the leakage inductance to the load.

# 3.4.3 Modified Boost Converter with output network

The converter has a small network in parallel with the secondary winding of the transformer. The switches operate at lower voltage stresses compared to the other topologies. The parasitic components such as output capacitance of the switches, leakage inductance, winding capacitance of the transformer and junction capacitance of the diodes can be used a part of the resonance design. The efficiency of this converter is about 92%.

From Table 3.1 we see that the basic converter has high frequency ringing across the main switch equal to the reflected output voltage. This is the same value for the other two topologies but without ringing. The same reflected output voltage is the stress across the auxiliary switch in the converters in Fig. (3.4) and (3.7). There is no auxiliary switch for the basic boost converter. The current stresses are shown in Table 3.2 for the three converters. The current stresses for the two switches is the same for the basic topology in Fig. (3.1). For the topology with active clamp in Fig. (3.4) a little more current stress than the basic topology is present to provide current to capacitor CB for the second switch. The current stress for the main switch is the same. The topology with output network has added current stress compared to the basic topology for the second switch. This added

current is used, by the resonant tank circuit, in the output side of the converter transformer for the converter in Fig. (3.7). The main switch of the basic converter and the converter with active clamp is hard-switched while the second switch achieves ZVS. The auxiliary switch for the converter with active clamp achieves ZCS. The converter with output network in fig. (3.7) has all three switches that are soft-switched. The circuit complexity and efficiency for the converter with output network is higher compared to the basic converter and the converter with active clamp.

#### **CHAPTER 4**

# DC-TO-AC RESONANT ZERO VOLTAGE SWITCHING INVERTER

### 4.1. Introduction

There is a pressing demand to design off-line ac inverters with Zero-Voltage-Switching (ZVS) and electrical isolation with improved power factor. The topology proposed can be used for power factor correction because the input current, is the inductor current, can be programmed. Research activities, in the design and development of high power-factor correction circuits, continue to grow since mid 1980's. As the use of non-linear loads in today's electronic systems continues to increase, utility power systems continue to suffer from low power factor [4,16,23]. Over the last ten years, different converter topologies (passive and active) have been introduced to serve as an interface module between the ac mains and non-linear loads to enhance power factor [3-14]. Recent research emphasis is focused on the active power factor correction because of their many advantages over the passive ones. The commonly used PWM active power-factor correction circuits are the buck, boost and buck-boost [6]. Unlike the buck and buck-boost, the boost converter topology is the most commonly used topology to improve power factor since it draws a continuous input current from the mains. This topology has limited application due to the absence of an isolation transformer at the output side and low frequency of operation. This disadvantage is avoided in the push-pull configuration when a three winding transformer is used.

A new modified dc-to-ac converter with ZVS and output electrical isolation was first introduced in [11]. In this paper, using sinusoidal approximation, a new set of characteristic curves and a design procedure are presented. Compared to the conventional inverters, this inverter has several advantages including output isolation, ZVS of all power switches, low EMI radiation. In electronic ballast designed for high frequency gas-discharged lamps, the new converter reduces the acoustic phenomena in high intensity gas discharged lamps. Since a frequency modulation technique is applied in this converter for both controlling power flow and avoiding the acoustic phenomena to be observable. In Section 4.2, the basic circuit operation and the corresponding circuit modes are presented. The state-space equations for the steady state models are given in Section 4.3 and the sinusoidal approximation technique is given in Section 4.4.

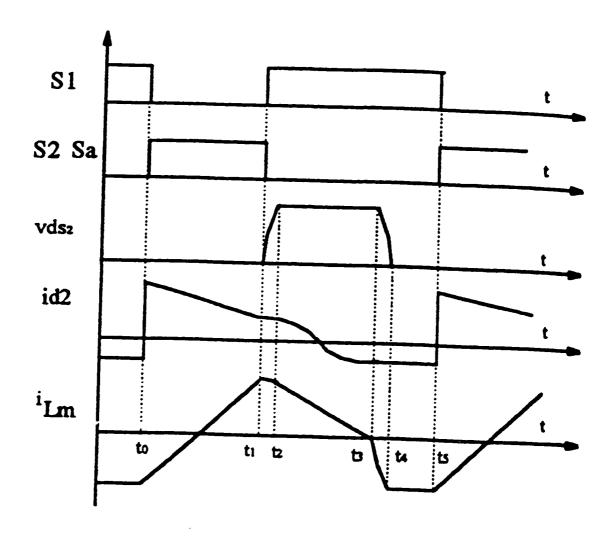

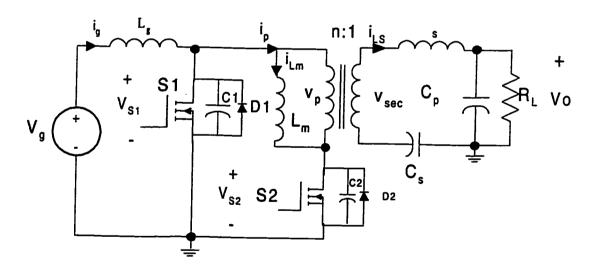

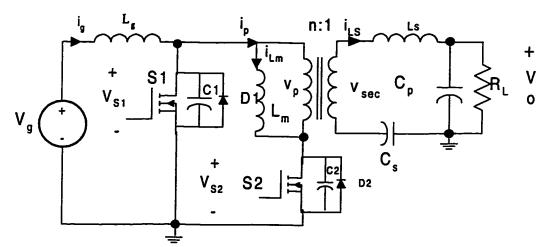

#### 4.2. Basic Circuit Operation

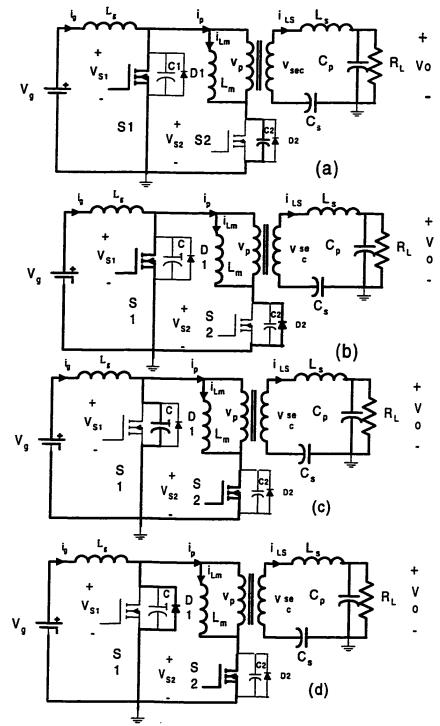

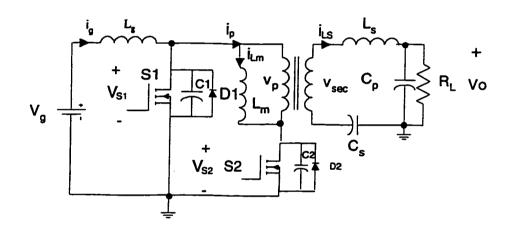

Figure 4.1 shows the simplified dc-to-ac converter circuit with output isolation and zero-voltage-switching (ZVS).

Fig. 4.1 DC-to-AC ZVS converter with isolation

The input inductor  $L_g$  is the main inductor with two MOSFET's  $S_1$  and  $S_2$  switching in complementary fashion. The capacitors  $C_1$  and  $C_2$  maybe used as the MOSFET's parasitic capacitance, and inductor  $L_m$  is the transformer magnetizing inductance. The components  $C_p$ ,  $C_s$  and  $L_s$  form the output resonant tank circuit that selects the output frequency and provides the resonance behavior to achieve ZVS for  $S_1$  and  $S_2$ .

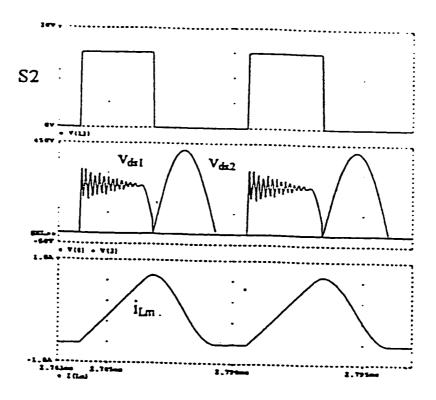

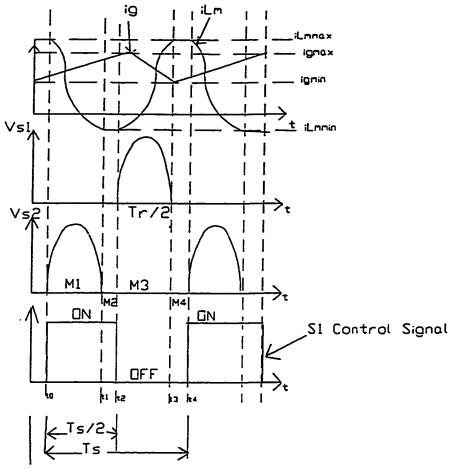

Fig. 4.2 Typical steady state waveforms

Figure 4.2 shows typical steady state waveforms of the input current,  $i_g$ , transformer magnetization current,  $i_{Lm}$ , the voltage across shunt switch  $S_1$ ,  $v_{S1}$ , the voltage across switch  $S_2$ ,  $v_{S2}$ , and the driving signal for switch  $S_1$ . The different modes of the circuit operating condition are shown in Fig. 4.3.

The basic circuit operation can be discussed as follows: At time to, assuming steady state of the converter is in mode M1,  $S_1$  is turned on and  $S_2$  is turned-off, causing  $L_m$ ,  $C_2$  to form a resonant tank circuit across the transformer primary side. From to to t1, the magnetization current sinusoidally drops from its positive peak,  $I_{lm,max}$  to its negative peak  $I_{Lm,min}$ . In Fig. 4.2, we define  $T_r$  as the resonant period of the tank circuit formed by  $C_1$ - $C_2$ - $L_m$ - $C_S$ - $C_P$ - $L_S$ . Also within this time interval,  $v_{S2}$  resonates sinusoidally for half a cycle to  $t_1$ while  $S_1$  is on. When  $v_{S2}$  decreases to zero at time  $t_1$ , the circuit mode changes from M1 to M2. In mode M2, diode D<sub>2</sub> conducts with  $v_{S2}$  clamped to zero voltage and  $i_{Ln}$  at its minimum,  $I_{Lm,min}$ , providing zero-voltage turn-on condition for  $D_2$ . This mode remains till time t2, entering mode M3 when switch S1 is turned off and S2 turned on. From t2 to t3 S1 is turned-off and S2 turned-on, resulting in the buildup of sinusoidal voltage across capacitor C1 from zero to its positive peak and back to zero again. During this time interval, the magnetization current,  $i_{Lm}$ , sinusoidally increases from its negative minimum, crosses zero, and reaches its positive maximum. At time  $t_2$ ,  $i_g$  increases sinusoidally until  $v_{sl}$  becomes equal to  $V_g$ , and then for  $v_{SI} > v_g$ ,  $i_g$  decreases nonlinearly until the time when  $v_{SI}$  becomes less than  $V_g$  when  $i_g$  increases non-linearly again, until time  $t_3$  when  $v_{sl}$  reaches zero. At  $t = t_3$ ,  $v_{sl}$ becomes zero, turning on  $D_1$ , while  $i_{Lm}$  is positive entering the circuit mode M4, in which  $i_{Lm}$ is maintained constant at its positive maximum. The voltage  $v_{SI}$  remains at zero allowing zero-voltage turn-on for  $S_1$ . The switching cycle repeats again at  $t_4 = T_S + t_0$  when  $S_1$  is turned on and  $S_2$  is turned off.

#### 4.3. Steady State Mathematical Model

In order to solve for the steady state response, the mathematical models for the four circuit modes of operation must be derived. The Transformer ratio is given by  $n=N_2/N_l$ . In this section, we provide mathematical model that must be solved to obtain the steady state response for the four modes given in Fig. 4.3.

#### Mode 1: $(t_0 \le t < t_1)$ :

In this mode,  $S_1$  is on,  $S_2$  is off, resulting in state variable Eq. (4.1). We should point out that when a switch is on, it implies that either the main switch is on or its fly-back diode  $D_1$  is on. In order to simplify the analysis, we assumed that the input current,  $i_g$ , is constant represented as  $I_g$ . Hence, this topology may be referred to as a current driven dc-to-ac converter [11].

Fig. 4.3 Modes of operation: a) Mode I(S1), b) Mode II (D2), c) Mode III (S2), d) Mode IV (D1)

Equation (4.1) may be represented in a compact form as follows,

$$\dot{X} = A_I \bullet X + B_I \bullet I_g \tag{4.2}$$

$$X = \begin{bmatrix} v_{C1} & v_{C2} & v_{CS} & v_{C\rho} & i_{LS} & i_{Lm} \end{bmatrix}^T \tag{4.3}$$

where X is the state vector given by,

#### Mode 2 $(t_1 \le t < t_2)$ :

In this mode,  $S_1$  is on and  $D_2$  is on. The state-space equation is given by, where  $A_2$  and  $B_2$  are given by,

$$\dot{X} = A_2 X + B_3 I_g \tag{4.4}$$

### Mode 3 ( $t \le t < t_3$ ):

This mode is similar to Mode 1, except that the resonant voltage is  $v_{SI}$  The state space equation is given by,

$$\dot{X} = A_3 \bullet X + B_3 \bullet I_g \tag{4.5}$$

where  $A_3$  and  $B_3$  are given by,

#### Mode 4 $(t_3 < t < t_4)$ :

In this mode,  $S_2$  and  $D_1$  are on. Magnetizing current is greater than input current and voltage across  $S_1$  is held zero due to diode  $D_1$  being on. The state space equation is given by

Equation (4.6) as follows,

$$\hat{X} = A_{4} \bullet X + B_{4} \bullet I_{g} \tag{4.6}$$

$$A_{4} = \begin{bmatrix}

0 & 0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & 0 & 0 & 0 \\

0 & 0 & 0 & 0 & \frac{n^{2}}{C_{s}} & 0 \\

0 & 0 & 0 & -\frac{1}{C_{p}R_{o}} & \frac{n^{2}}{C_{p}} & 0 \\

\frac{1}{n^{2}L_{s}} & -\frac{1}{n^{2}L_{s}} & -\frac{1}{n^{2}L_{s}} & 0 \\

0 & 0 & 0 & 0 & 0 & 0

\end{bmatrix}$$

when  $A_4$  and  $B_4$  are given by,

The above four state space equations represent a  $6^{th}$  order non-linear system, and give the complete mathematical model for the converter. Solving these equations is time consuming and difficult. Instead, sinusoidal approximation is used to obtain the steady state response. In the next section, we present such an analysis from which design characteristic curves are derived followed by a design procedure.

48

# 4.4 Mathematical Analysis

# 4.4.1 Sinusoidal Approximation

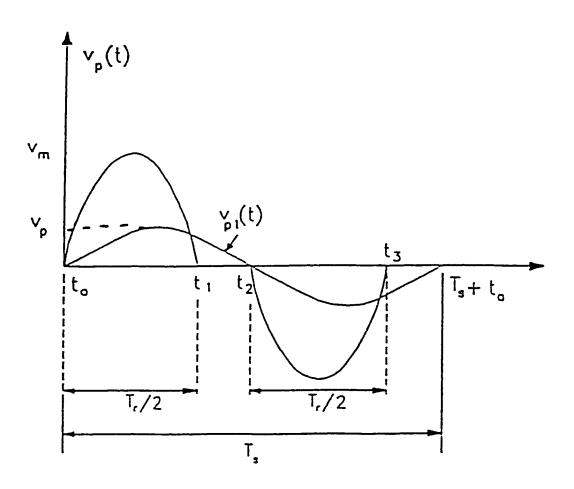

In order to simplify the analysis, sinusoidal approximation is used to derive expressions for the capacitor voltages,  $v_{sl}$ ,  $v_{s2}$  and the output voltage,  $v_o$ . The voltage across the transformer primary winding  $v_p(t)$  is shown in Fig. 4.4.

Figure 4. 4 Primary voltage  $v_p(t)$

The voltage  $v_p(t)$  is the difference between the capacitor voltages  $v_{sl}$  and  $v_{s2}$  as shown by Eq. (4.7).

$$v_p(t) = v_{s1} - v_{s2} \tag{4.7}$$

We can express  $v_p(t)$  as a Fourier series whose general form is given by:

$$f(t) = F_0 + \sum_{n=0}^{\infty} a_n \cos n\omega t + b_n \sin n\omega t$$

(4.8)

where  $\omega=2\pi/T$ , T is the period of the periodical waveform and F<sub>0</sub> is its DC component. Since  $\nu_p$  is symmetrical and odd around  $(t_1+t_2)/2+t_0$ , its DC component is zero, hence, the fundamental component is given by,

$$f_1(t) = a_1 \cos \omega_s t + b_1 \sin \omega_s t \tag{4.9}$$

$$=F_1 \sin(\omega_s t - \theta)$$

where,

$$F_{1} = \sqrt{{a_{1}}^{2} + {b_{1}}^{2}}$$

$$\theta = tan^{-1} \frac{b_1}{a_1}$$

$\alpha v\delta \omega_s = 2\pi/T_s$ ,  $T_s$  is the switching frequency and the coefficients  $a_I$ , and  $b_I$ , are given by,

$$a_I = \frac{2}{T_s} \int_0^{T_s} f(t) \cos(\omega_s t) dt \qquad (4.10)$$

$$b_{l} = \frac{2}{T_{s}} \int_{0}^{T_{s}} f(t) \sin(\omega_{s} t) dt \qquad (4.11)$$

In our case, the function f(t) is  $v_p(t)$  which is not continuous over one switching cycle, hence, we split the integration into two intervals:  $0 < \omega_s t < \pi - \alpha$  and  $\pi < \omega_s t < 2\pi - \alpha$ , where the dead time  $\alpha$  is defined as below:

where  $f_{rs}=f_s/f_r$ , and  $f_s=1/T_s$  and  $f_r=1/T_r$  are the switching and the resonant frequencies of the

$$\alpha = \omega_s \frac{(T_s - T_r)}{2} = \pi (l - f_{ns})$$

converter, respectively. It can be shown that  $f_r$  is given by,

$$f_r = f_{ir} \sqrt{I + \frac{L_m / n^2 L_s}{I + f_{nor}^2}}$$

(4.12)

where  $f_{ir}$  and  $f_{or}$  are the input and output side resonant frequencies defined by,

$$f_{ir} = \sqrt{l + \frac{L_m/n^2 L_s}{l + f_{nor}^2}}, f_{or} = \frac{l}{2\pi \sqrt{L_s(C_T/n^2)}}$$

(4.13)

where  $C=C_1=C_2$ ,  $C_T=C_SC_P/(C_S+C_P)$ .

The normalized output frequency,  $f_{non}$  is expressed as  $f_S/f_{or}$ . Let the fundamental component of  $v_p(t)$  be given by,

$$v_{p_1}(t) = V_p \sin(w_s t + \theta) \tag{4.14}$$

$V_p$  is the peak voltage of the fundamental component as shown in Fig. 4.4 and is given by

$$V_p = \sqrt{a_l^2 + b_l^2}$$

It can be shown that a<sub>1</sub> and b<sub>1</sub> are given by,

$$a_{1} = \frac{(V_{m}/\pi)\sin(\pi/2f_{ns})}{(l/f_{ns})^{2} - l} \left[ 2\sin\alpha\cos(\alpha/f_{ns}) - \frac{2}{f_{ns}}\cos\alpha\sin(\alpha/f_{ns}) + \frac{2}{f_{ns}} \frac{l - \cos(\pi/f_{ns})}{l - (l/f_{ns})^{2}} \right]$$

$$b_{1} = \frac{2V_{m}}{\pi}\sin(-\pi/2f_{ns}) \left[ \frac{\cos(\alpha/f_{ns})\cos\alpha + \frac{l}{f_{ns}}\sin(\alpha/f_{ns})\sin\alpha}{(l/f_{ns})^{2} - l} \right]$$

where  $V_m$  is the peak voltage of  $v_{SI}$  and  $v_{S2}$  as shown in Fig.4. 4.

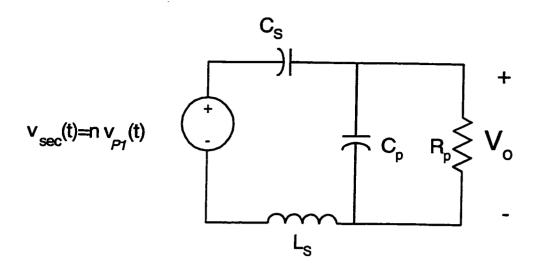

# 4.4.2 The output circuit analysis

The equivalent output circuit shown in Fig. 4.5, is a linear circuit driven by the fundamental component  $v_{pl}(t)$  whose voltage gain is given by

$$M = \frac{v_o(t)}{v_{sec}(t)} = \frac{v_o(t)}{n_{v_p} I(t)}$$

(4.15)

Figure 4.5 Equivalent output circuit

From Fig. 4.5, we obtain the following transfer function,

$$\frac{V_o}{V_{P1}} = \frac{l}{n} \frac{\left[R_o / - \frac{j}{\omega_s C_p}\right]}{\left(R_o / - \frac{j}{\omega_s C_p}\right) + j\left(\omega_s L_s - \frac{l}{\omega_s C_s}\right)}$$

and the magnitude of the voltage gain is given by:

$$M = \frac{1}{n\sqrt{(1+C_p/C_s)^2(f_{nor}^2-1)^2 + \frac{1}{Q_o^2}(\frac{1}{f_{nor}(1+C_s/C_p)} - f_{nor}^2)}}$$

where Qo is the output quality factor (normalized load) given by

$$Q_o = \frac{R_o}{Z_{or}} \tag{4.16}$$

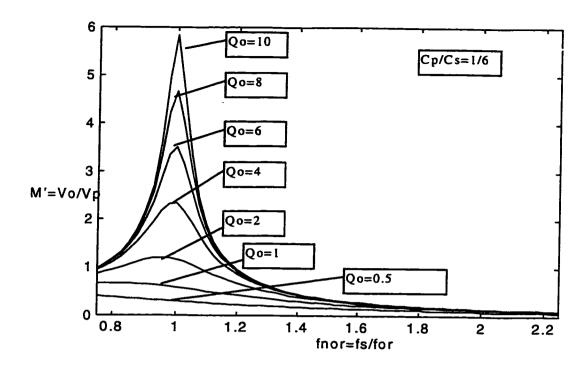

$Z_{or}$  is the output characteristic impedance given by  $Z_{or} = \sqrt{L_s/C_T}$ . Figure 4. 6 shows M vs.  $f_{nor}$  under different normalized loads,  $Q_o$ , and for  $C_s/C_p = 6$ . As expected, this is a boost converter whose voltage gain is larger than one.

Figure 4.6 Performance curves of the converter

# 4.4.3 The input circuit analysis

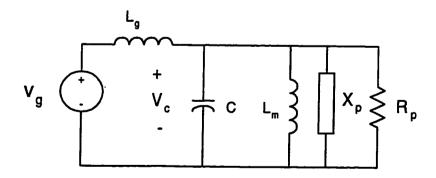

Next we turn to the input side to relate  $V_g$  to the voltage across the primary windings. The equivalent circuit for Mode 1 and Mode 3 are identical, since we assume  $C_1 = C_2$ , as shown in Fig. 4.7.

Fig.4.7 Equivalent input circuit for Modes I and III

The impedances  $X_p$  and  $R_p$  are given by,

$$R_p = X_{s'} \left( \frac{R_{s'}}{X_{s'}} + \frac{X_{s'}}{R_{s'}} \right)$$

$$X_{p} = R_{s'} \left( \frac{R_{s'}}{X_{s'}} + \frac{X_{s'}}{R_{s'}} \right)$$

where

$$R_{s'} = Z_o \left[ \frac{n^2 Q_o}{1 + f_{nor}^2 (1 + C_p / C_s)^2 Q_o^2} \right]$$

$$X_{s'} = Z_{o} f_{nor} \left[ \frac{(f_{nor}^{2} - I)n^{2} Q_{o}^{2} (I + C_{p} / C_{s})^{2}}{I + f_{nor}^{2} (I + C_{p} / C_{s})^{2} Q_{o}^{2}} \right]$$

Assume the transition between the modes makes it possible to treat the voltage across  $C_1$  or  $C_2$ ,  $v_c$ , as a transient voltage given by,

$$v_c(t) = Ae^{-\nu \tau} \sin_{\omega_r} t \tag{4.17}$$

where

$$\tau = 2 R_{p'} C$$

The constant A is obtained from the initial condition. In order to evaluate A, we obtain the average value of  $v_c$  (t) and set it to  $V_g$ , as follows,

$$V_g = \frac{I}{T_s} \int_0^{T_s} v_c(t) dt \tag{4.18}$$

From Equations (4.17) and (4.18), we obtain.

$$A = V_g T_s \frac{(l/\tau^2 + \omega_r^2)}{\omega_r (l + e^{-m/\tau}\omega_r)}$$

Hence,  $v_c(t)$  is given by,

$$v_c(t) = \frac{V_g T_s(1/\tau^2 + \omega_r^2)}{\omega_r (1 + e^{-s/\tau}\omega_r)} e^{-s/\tau} \sin \omega_r t$$

(4.19)

If we let the peak voltage of  $v_c(t)$  occur at  $t=t_{max}$ ,  $V_{c,peak}(t)$  is given by,

$$V_{c,peak} = \frac{V_g T_s(l/\tau^2 + \omega_r^2)}{\omega_r(l + e^{-\pi/\tau\omega_r})} e^{\frac{t_{max}}{\tau}} sin(\omega_r t_{max})$$

(4.20)

In terms of normalized quantities, we obtain

$$V_{nc,peak} = \frac{2\pi}{f_{ns}} \left[ \frac{1 + (f_{ns}/\tau_n)^2}{(1 + e^{-\pi f_{ns}/\tau_n})} \right] e^{-\theta_m/\tau_n} \sin(\theta_m/f_{ns})$$

where,

$$\tau_n = \frac{2(a^2+1)n^2Q_o f_{nor}(C/C_T)}{1+f_{nor}^2Q_o^2(1+C_p/C_s)^2}$$

$$\theta_m = f_{ns} \tan^{-1}(\tau_n / f_{ns})$$

$$a = f_{nor}(f_{nor}^2 - I)(I + \frac{C_p}{C_s})^2 Q_o$$

$$t_{max} = \frac{1}{\omega_r} \tan^{-1}(\omega_r \tau)$$

#### **4.5 Characteristic Curves**

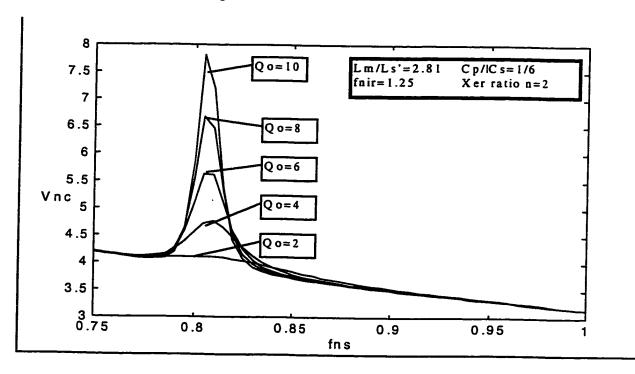

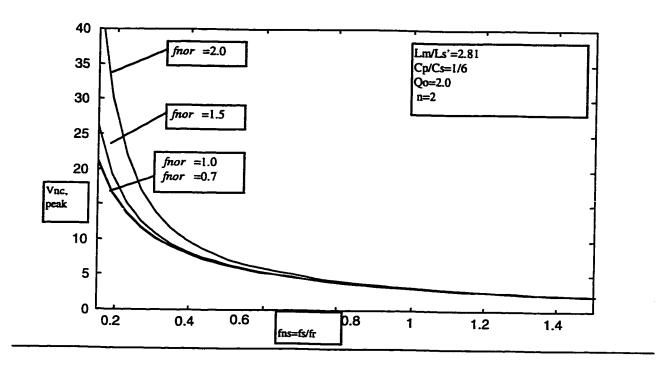

The characteristic curve for  $V_{nc,peak}$  vs  $f_{ns}$ , under different  $Q_0$ , is given in Figure 4.8. Figure 4.9 gives the characteristic curve for  $V_{nc,peak}$  vs.  $f_{ns}$  under different values of  $f_{nor}$ . These curves are derived under fixed circuit parameters.

Figure 4.8. Characteristic curve for  $V_{nc,peak}$  vs.  $f_{ns}$  under different values of  $Q_o$

Fig. 4.9 Characteristic curves for  $V_{nc,peak}$  vs.  $f_{ns}$  under different values of  $f_{no}$

# 4.6 Design Procedure and Example

Consider the following design specifications:

· Switching frequency,

$f_s = 100 \text{kHz}$

· Input voltage,

Vg = 60V

· Output power,

$P_o = 100W$

· Component Ratios:

$L_{\rm m}/L_{\rm s} = 2.81$ ,  $C_{\rm p}/C_{\rm s} = 1/6$ .

We follow the design procedure outlined as follows:

We choose  $f_{ns}=1$ ,  $f_{nor}=1.2$  and  $Q_0=2.0$ . This region is a compromise between a sensitive region at low  $f_{ns}$  (0.5-1), and the flat response for  $f_{ns} > 1.5$ . From Fig. 4.8,

we obtain an approximate value for V<sub>nc,peak</sub>≈3.34.

- 2) The actual  $V_{c,peak}$  value is 206.4 V.

- For given  $f_s$  and  $f_{nor}$ , we obtain  $f_{or} = 166.7$  kHz.

- From Fig. 4.6, with given  $f_{nor}$  and  $Q_o$ , we obtain M=0.671, hence, the output voltage  $V_o = 138.5 \text{ V}$ .

- 5) With  $P_0$  given, we obtain  $R_0 = 100\Omega$ .

- 6) From  $R_0$  and  $Q_0$ , we obtain  $Z_0 = 50\Omega$

- 7)  $Z_0$  and  $f_{or}$  are solved for resonant components  $L_s$  and  $C_T$ ,

$$C_T = 1/2\pi f_{or} Z_o \qquad L_s = 2\pi f_{or}/P_o$$

This yields L<sub>s</sub>=86.11 $\mu$ H, C<sub>p</sub>=47nF and C<sub>s</sub>=270nF C<sub>T</sub>=39.91nF

- For given  $f_{ns}$  and  $f_{nor}$ , we obtain  $f_{ir}$  from Eq. (4.12) and (4.13),  $f_{ir} = 136.4$ KHz, where  $f_{ns} = f_r / f_s$  normalized switching frequency

- 9) Solving  $f_{ir}$  and  $f_r$  for  $L_m$  and C, we obtain:

$$L_m = 0.97 \text{mH}, C=C_1 = C_2 = 10.0 \text{nF}$$

$$\frac{\Delta I_g}{T_s/2} = \frac{V_g}{L_g}$$

- 10) Finally, we estimate  $L_g$  by limiting  $I_g$  to 5% ripple on its average value, using the following relation,

- We obtain  $L_g = 3mH$ .

To summarize the design, Table 4.1 below shows the calculated parameters for this design.

Table 4.1

| DESIGN VALUE |

|--------------|

| 3.44         |

| 206.4 V      |

| 1.0          |

| 1.2          |

| 166.7kHz     |

| 2.0          |

| 0.671        |

| 138.5 V      |

| 100.0 Ω      |

| 50.0 Ω       |

| 39.91nF      |

| 47.0 nF      |

| 270.0 nF     |

| 136.4kHz     |

| 86.11µH      |

| 0.97mH       |

| 3.0mH        |

| 10.0nF       |

|              |

#### CHAPTER 5

# SIMULATION AND EXPERIMENTAL RESULTS FOR THE

#### DC-TO-AC INVERTER TOPOLOGY

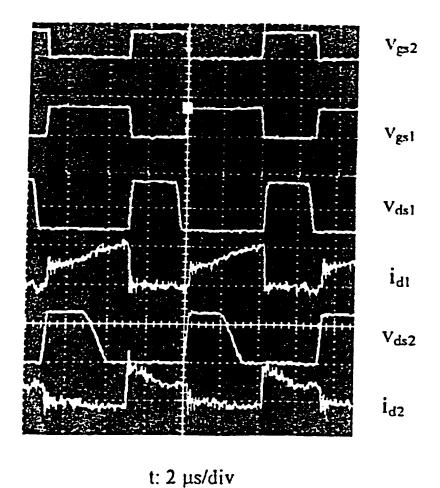

# 5.1 Modified DC-to-AC Zero Voltage Switching Inverter Topology

Figure 5.1 shows the simplified dc-to-ac converter circuit with output isolation and zero-voltage-switching (ZVS).

Fig. 5.1 DC-to-AC ZVS inverter with isolation

## 5.2 Simulation Results for the dc-to-ac inverter

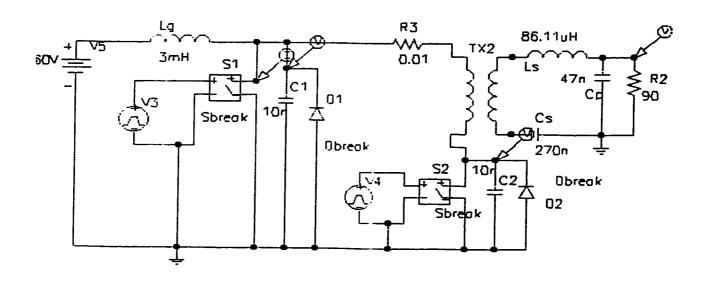

#### **5.2.1** Schematic for simulation

Figure 5.2 shows the PSPICE<sup>TM</sup> schematic diagram for the topology shown in Figure 5.1. The input voltage is a dc source of 60V. The values of the different parameters are

according to the design parameters determined in Section 4.6. A low value resistor R<sub>3</sub> is inserted in series with the primary of the isolating transformer for simulation purposes only. PSPICE does not accept a non-resistor inductor loop formed by the transformer TX2 and L<sub>8</sub>. This avoids convergence problems in the transient analysis of this topology. Ideal switches are used instead of MOSFETS. The MOSFET model is approximated by using D1 and D2 as the MOSFET's body diodes. Capacitor C1 and C2 are equivalent parasitic capacitances of the switch. This model also helps to understand the different modes of operation corresponding to the steady state waveforms.

Vin = 60 Vdc Fs = 100 kHz Po ave = 100 W

Figure 5.2 PSPICE schematic for the dc-to-ac ZVS inverter

#### 5.2.2 Simulation waveforms

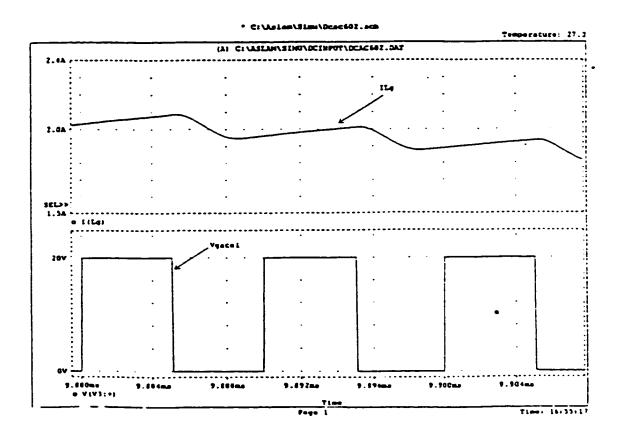

# 5.2.2.1 Input inductor current i<sub>Le</sub> and gate control voltage for switch S<sub>1</sub>

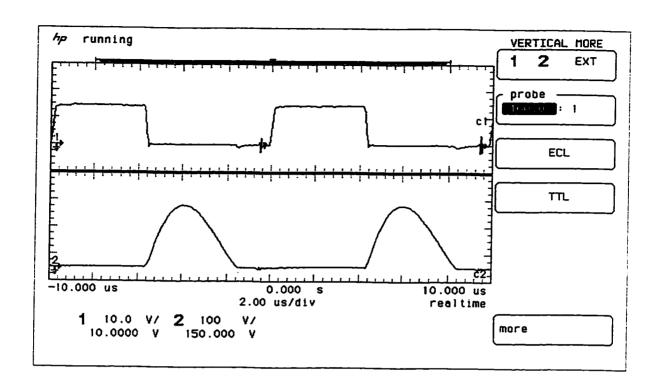

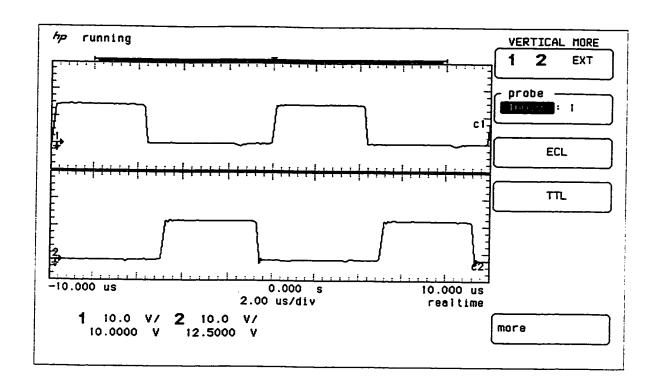

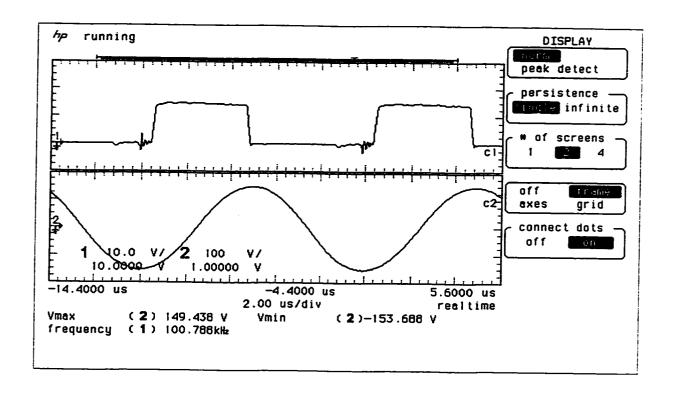

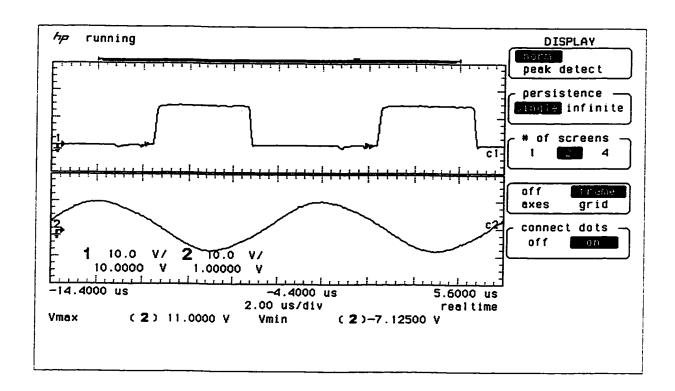

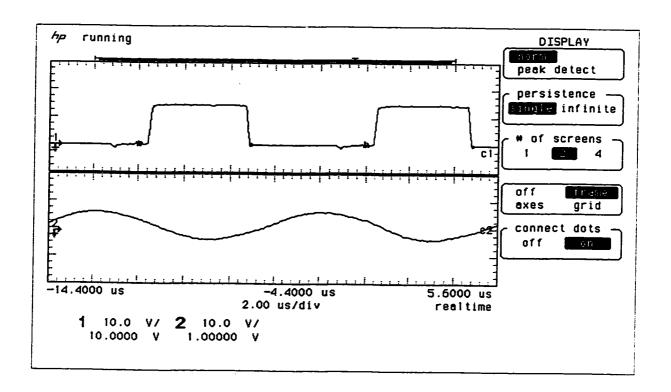

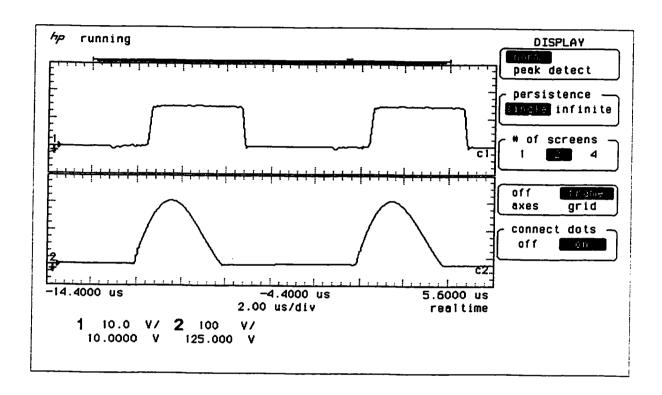

Figure 5.3 shows the input inductor current  $i_{Lg}$  and the gate control voltage for switch  $S_1$ . The current  $i_{Lg}$  is about 2.0 Amps and corresponds to the switching of gate voltage pulse of  $S_1$ . The current increases linearly when the switch is on and vice versa.