A unified approach to dynamic modeling of high switching frequency PWM converters Iannello, Christopher Joseph *ProQuest Dissertations and Theses;* 2001; ProQuest Dissertations & Theses (PQDT) pg. n/a

# **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

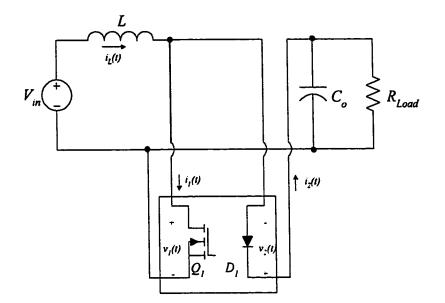

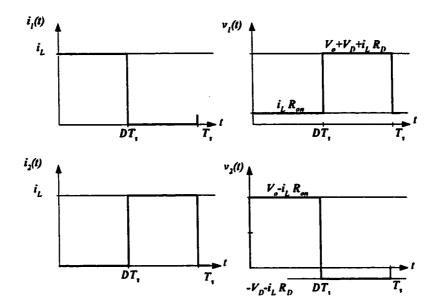

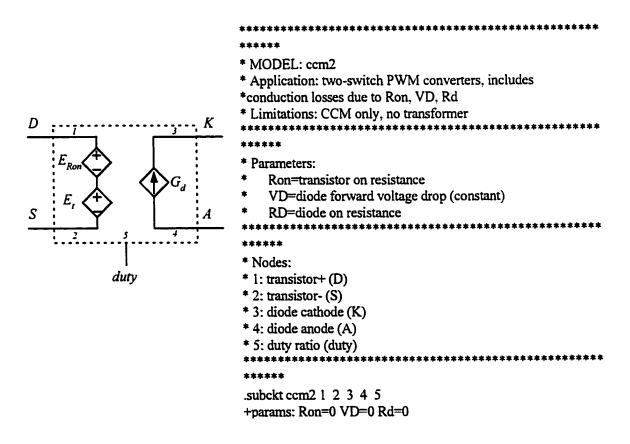

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{"} \times 9^{"}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# UMI®

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# A UNIFIED APPROACH TO DYNAMIC MODELING OF HIGH SWITCHING FREQUENCY PWM CONVERTERS

by

CHRISTOPHER J. LANNELLO B.S.E.E University of Central Florida, 1994 M.S.E.E University of Central Florida, 1999

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering at the University of Central Florida Orlando, Florida

Summer Term 2001

Major Professor: Issa Batarseh

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 3013908

# UMI®

#### UMI Microform 3013908

Copyright 2001 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### ABSTRACT

This dissertation will present the development of a unified approach for dynamic modeling of the PWM and soft-switching power converters. Dynamic modeling of non-linear power converters is very important for the design and stability of their closed loop control. While the use of equivalent circuits is often preferred due to simulation efficiency issues, no unified and widely applicable method for the formulation of these equivalents exists.

A review of conventional modeling technique via the method of state-space averaging will be carried out. Complete development of the averaged, equivalent circuit models for the nonlinear power switch/diode combination in modern power converters via the Vorperian method will also be given. After highlighting the limitation's of the Vorperian approach, a more widely applicable approach will be developed. This approach will capitalize on the notion that the derivative of the average of a time varying parameter is equal to the average of the derivative of that parameter.

First, the development will show the formulation of the dc modeling equations, then show how these modeling equations are implemented using PSPICE's Analog Behavioral Modeling capability. Next, the validation of the models produced will be presented via comparison to actual circuit simulation and experimental results.

ü

The unified approach presented has several advantages over conventional techniques. The unified approach is applicable to virtually any type of converter and is not restricted by topological issues. It is easily derived by a methodical approach, it simulates accurately and quickly, and it produces models that can work equally well in CCM and DCM. Model results agree well with other averaged models and the actual circuit.

In addition, the approach will be expanded to include non-ideal effects such as conduction loss for both CCM and DCM operational modes. It will also be applied to the more complicated class of soft-switching topologies.

The purpose of the research is to develop a methodology that makes more effective use of computer simulation tools during power converter prototype development. Although, predictions about converter operation are often very good when using this unified method, it should not be considered a substitute for actual circuit simulation or bench top prototyping which often reveal subtle issues not evident from average modeling. The following work will show that the types of computer-based analysis used in the design approach are the necessary and prudent first steps in the design process.

#### ACKNOWLEDGMENTS

The author wishes to express his sincere gratitude to his advisor, academic colleagues, coworkers, family, and friends for their constant support and understanding.

Dr. Issa Batarseh has, from the very beginning, inspired my pursuit of power electronics research, guided my efforts, and answered my seemingly endless stream of questions. His constant example of dedication and commitment to the students and to the task at hand has left a lasting impression that will continue to motivate me.

My colleagues, both at NASA and UCF, have always been there to support my efforts. In fact, their contribution made this all possible. At NASA, my co-workers and management stood behind my decision to pursue the degree, and kept up with my tasks while I was away at school. At UCF, my fellow students, past and present, gave me their insight and helped when the workload seemed too great. I am indebted.

As for my family and friends, I can only say I am so very fortunate to have such an understanding group behind me. I have been blessed with parents who have taught me the meaning of hard work and friends who care. To both, I have been more absent than not over the course of this work. With its completion, I look forward to spending more time with them. Overall, I am glad to have had the experience and to conduct this research. Having said all that, I am also glad this effort has come to an end.

i. .

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION 1                                                    |

|------------------------------------------------------------------------------|

| 1.1 PWM Converter Overview2                                                  |

| 1.2 The Method of State-Space Averaging7                                     |

| 1.3 Vorperian's Method of PWM Switch Modeling                                |

| 1.4 Theory of Unified Approach                                               |

| 1.5 Dissertation Outline                                                     |

| CHAPTER 2: THEORY AND METHODOLOGY OF UNIFIED APPROACH                        |

| 2.1 Introduction and Objectives                                              |

| 2.2 Variant Technique Evaluation                                             |

| 2.3 Fundamental Theory of Unified Modeling Approach                          |

| 2.4 Application of Modeling Theory to Boost Converter                        |

| 2.5 Implementation of Averaged Models in PSPICE                              |

| 2.6 Boost Model Validation76                                                 |

| 2.7 Application of Unified Approach to Separated PWM Switch Converter91      |

| CHAPTER 3: INCORPORATION OF LOSS MODELING                                    |

| 3.1 Introduction                                                             |

| 3.2 Conduction Loss Modeling in CCM114                                       |

| 3.3 Conduction Losses in DCM-Energy Equivalence                              |

| 3.4 Conduction Loss Modeling Implemented in the Unified Modeling Approach147 |

| 3.5 Experimental Validation of Newly Formed Loss Models165                   |

| 3.6 Evaluation of Conduction Loss Models175                                  |

| CHAPTER 4: APPLICATION TO SOFT-SWITCHING TOPOLOGIES-STEADY<br>STATE          |

| 4.1 Introduction                                                                   | . 177 |

|------------------------------------------------------------------------------------|-------|

| 4.2 The Concept of Soft-switching                                                  | . 178 |

| 4.3 Overview of High Voltage, High Power Converters                                | . 178 |

| 4.4 Topology Overview                                                              | . 180 |

| 4.5 Presentation of Target Topology                                                | . 183 |

| 4.6 Operational Modes                                                              | . 185 |

| 4.7 Steady-State Analysis of FB-ZCS with Design Example                            | . 203 |

| 4.8 Evaluation of Steady State Analysis                                            | . 222 |

| CHAPTER 5: APPLICATION TO SOFT-SWITCHING TOPOLOGIES-SMALL-<br>SIGNAL AND TRANSIENT | 224   |

| 5.1 Introduction                                                                   | . 224 |

| 5.2 Average Model development of FB-ZCS                                            | 224   |

| 5.3 Small Signal Analysis and Closed Loop Design                                   | 232   |

| 5.4 Transient Analysis                                                             | 240   |

| 5.5 Evaluation of Dynamic Model of FB-ZCS                                          | 242   |

| CHAPTER 6: CONCLUSIONS AND FUTURE WORK                                             | 244   |

| 6.1 Conclusions and Summary                                                        | 244   |

| 6.2 Future Work                                                                    | 247   |

| REFERENCES                                                                         | 249   |

# **LIST OF FIGURES**

# Number

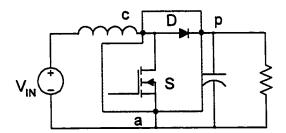

| Figure 1.1: Boost converter                                                 | 3  |

|-----------------------------------------------------------------------------|----|

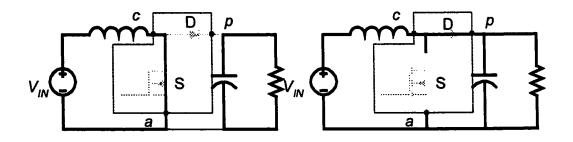

| Figure 1.2: Equivalent circuit modes                                        | 5  |

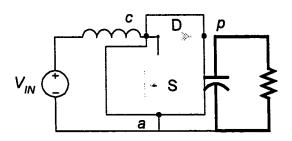

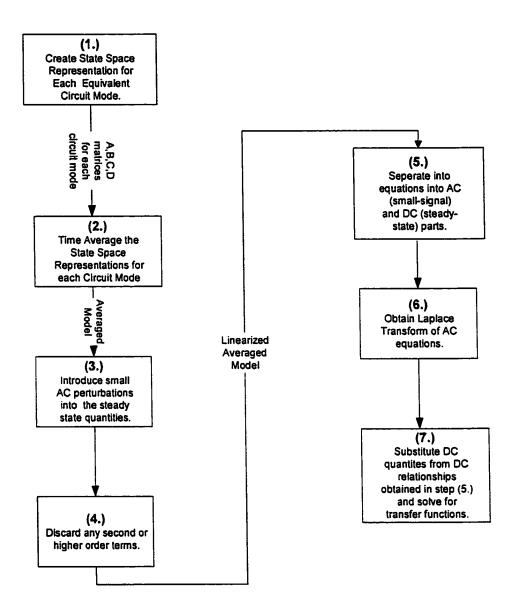

| Figure 1.3: State-space averaging step by step process                      | 10 |

| Figure 1.4: Inductor current in DCM                                         | 11 |

| Figure 1.5: Single-stage single switch converter                            | 13 |

| Figure 1.6: Modes of operation of single-stage single switch converter      | 13 |

| Figure 1.7: Instantaneous waveforms of single-stage single switch converter | 16 |

| Figure 1.8: Magnitude for single stage PFC converter (control-output)       | 24 |

| Figure 1.9: Phase for single stage PFC converter (control-output)           | 25 |

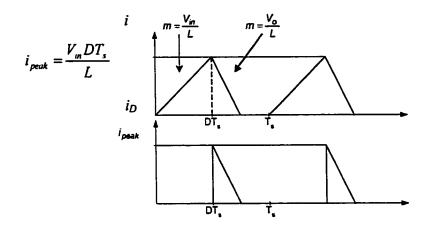

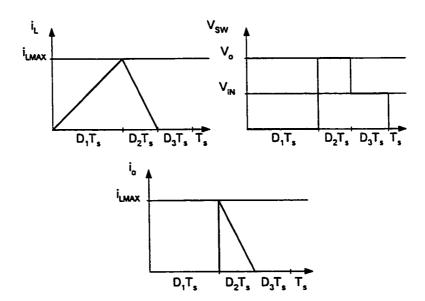

| Figure 1.10: Instantaneous waveforms for boost (DCM)                        | 28 |

| Figure 1.11: PWM Switch Model (DCM)                                         | 30 |

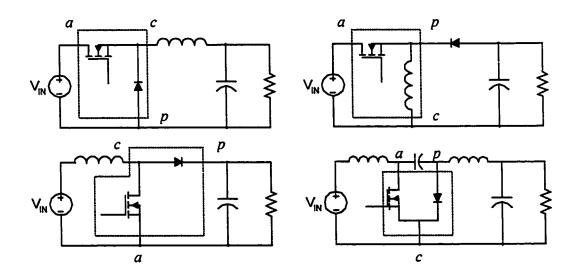

| Figure 1.12: PWM Switching Cell in classic topologies                       |    |

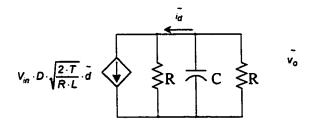

| Figure 2.1: Separated PWM switch topology in [6]                            |    |

| Figure 2.2: Buck-boost waveforms in DCM                                     | 45 |

| Figure 2.3: Modeling cell in Buck-Boost                                     | 46 |

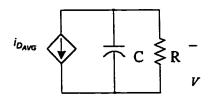

| Figure 2.4: Averaged equivalent circuit                                     | 47 |

| Figure 2.5: Linearized, averaged Circuit                                    | 48 |

| Figure 2.6: Boost converter.                                                | 55 |

| Figure 2.7: Instantaneous waveforms of boost (DCM)                          | 55 |

| Figure 2.8: Partial averaged equivalent for inductor                        | 57 |

| Figure 2.9: Partial averaged equivalent                                     | 58 |

| Figure 2.10: Complete averaged equivalent model                             | 60 |

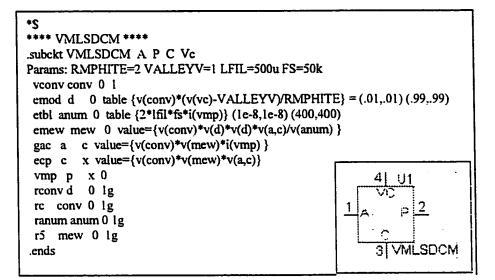

| Figure 2.11: PSPICE Subcircuit and model symbol for Vorperian DCM           | 67 |

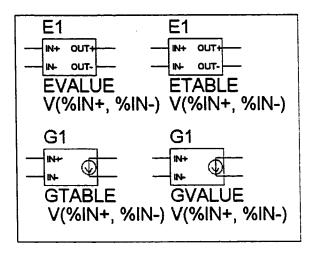

| Figure 2.12: PSPICE ABM Symbol                                              |    |

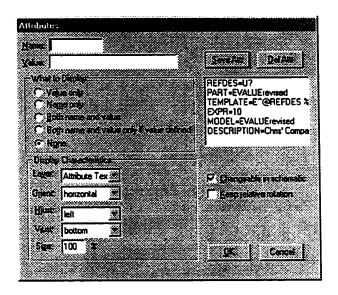

| Figure 2.13: PSPICE Attributes dialog box                                   |    |

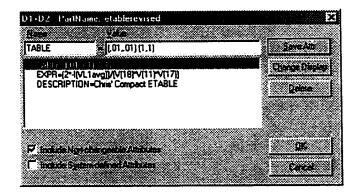

| Figure 2.14: PSPICE Definition dialog box                                   |    |

| Figure 2.15: PSPICE Pin dialog box                                          |    |

| Figure 2.16: PSPICE Template statement                                      |    |

| Figure 2.17: PSPICE Custom Library                                          |    |

| Figure 2.18: PSPICE custom source dialog box                                |    |

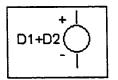

| Figure 2.19: PSPICE custom source symbol                                    |    |

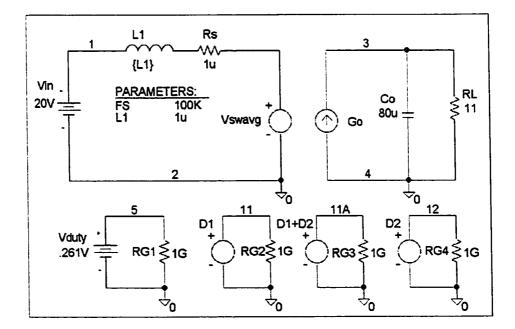

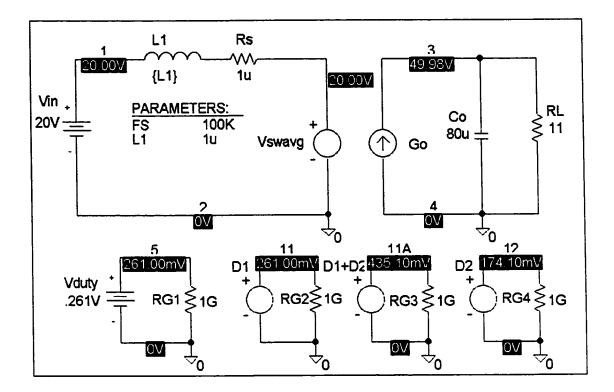

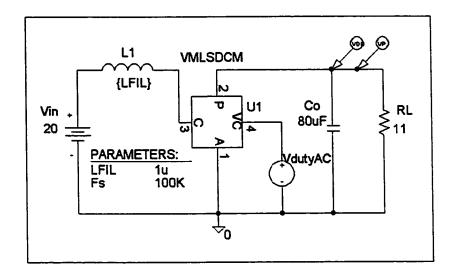

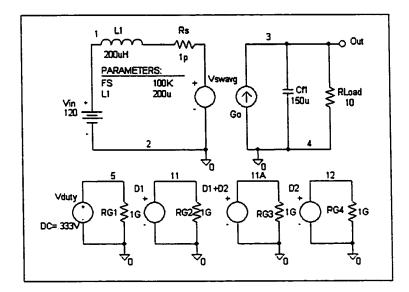

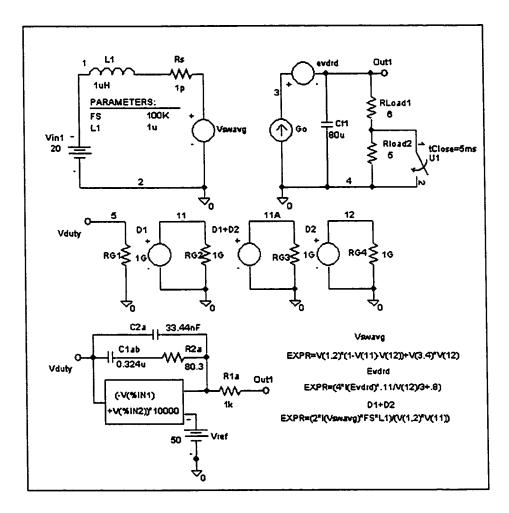

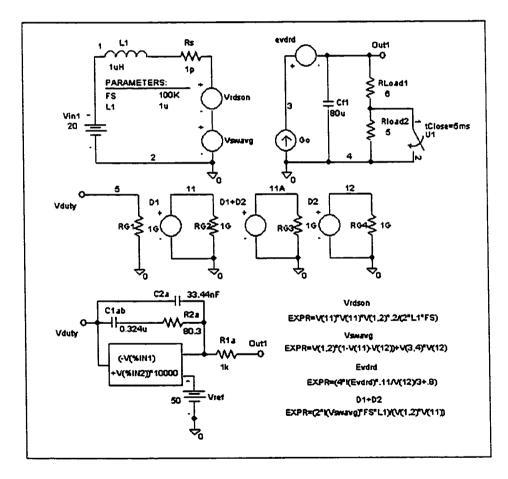

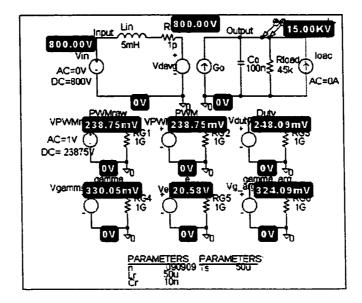

| Figure 2.20: PSPICE schematic model of boost                                |    |

| Figure 2.21: Bias point solution of boost model                             |    |

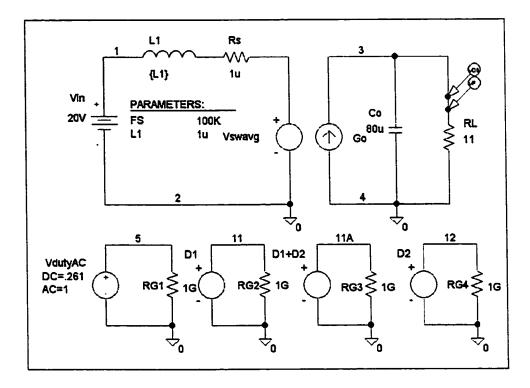

| Figure 2.22: AC Sweep Schematic: Vorperian                                                       |             |

|--------------------------------------------------------------------------------------------------|-------------|

| Figure 2.23: AC Sweep Schematic: New model                                                       | 80          |

| Figure 2.24: Small-signal curves superimposed                                                    | 82          |

| Figure 2.25: Boost schematic: Actual Circuit                                                     |             |

| Figure 2.26: Boost schematic: Vorperian                                                          | 83          |

| Figure 2.27: Boost schematic: New Model                                                          | 84          |

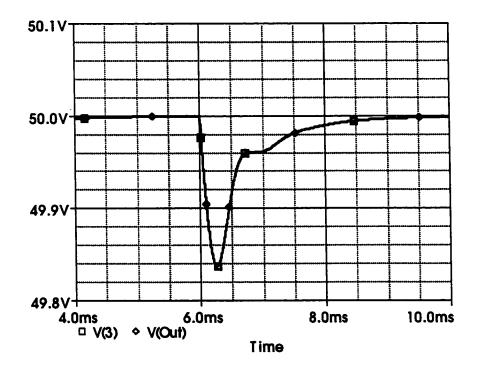

| Figure 2.28: Average model transient comparison                                                  | 85          |

| Figure 2.29: Simulation output comparison                                                        | . 86        |

| Figure 2.30: Boost CCM/DCM Schematic                                                             | , <b>90</b> |

| Figure 2.31: Single-stage single switch converter                                                | . 92        |

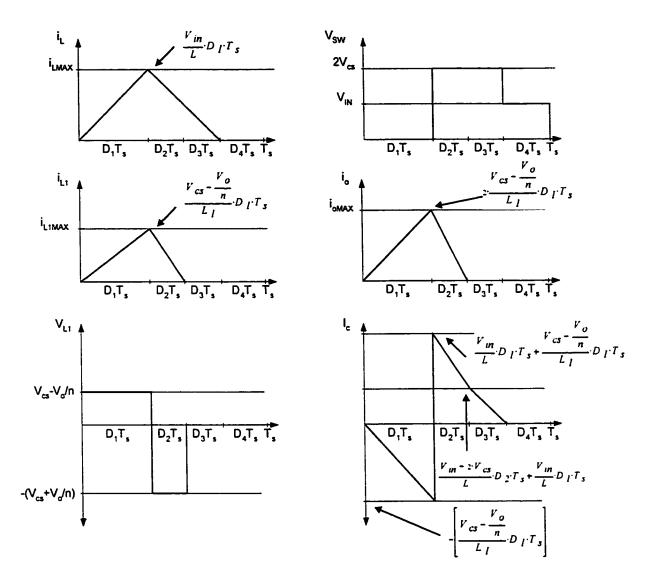

| Figure 2.32: Instantaneous waveforms of single-stage single switch converter                     | . 95        |

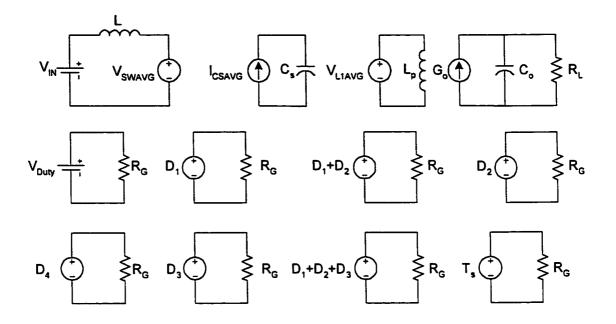

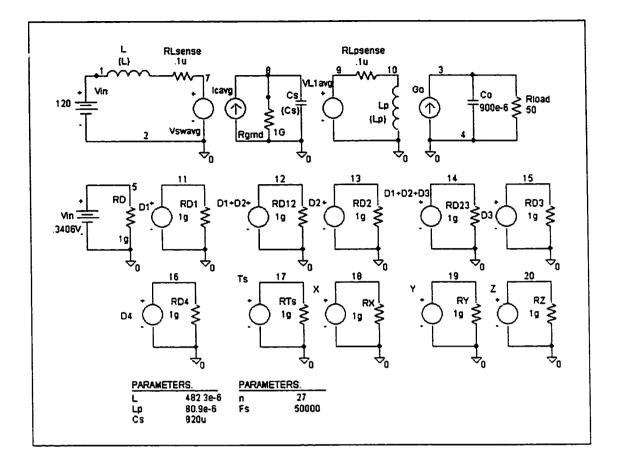

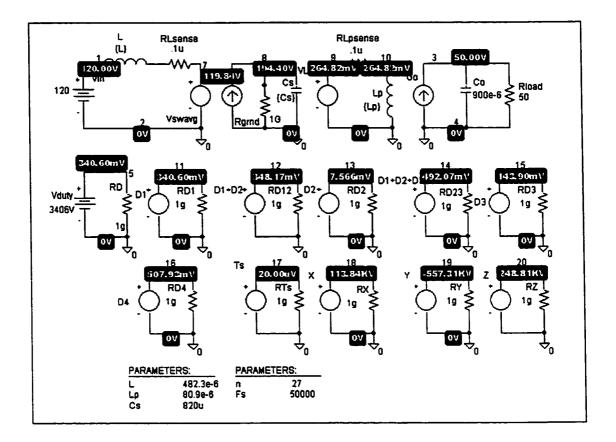

| Figure 2.33: Completed model for circuit of Figure 1.5                                           | . 97        |

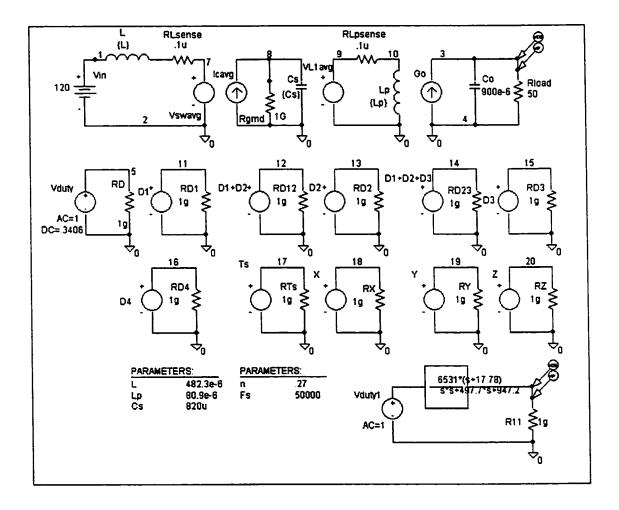

| Figure 2.34: PSPICE Schematic for model of Figure 2.33                                           | 100         |

| Figure 2.35: Bias point solution for Figure 2.34                                                 | 102         |

| Figure 2.36: AC Sweep Schematic for Figure 2.34                                                  | 103         |

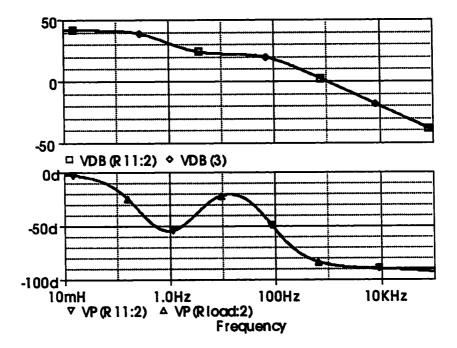

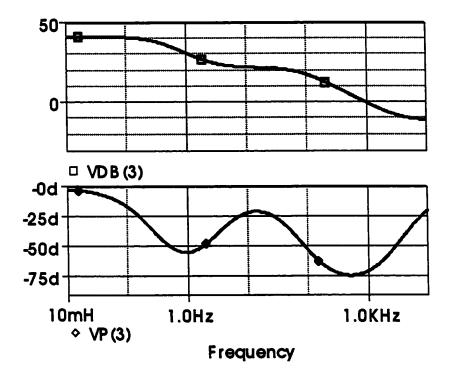

| Figure 2.37: Small-signal comparison: Model to SSA                                               | 104         |

| Figure 2.38: Simulated control-to-output response                                                |             |

| Figure 2.39: Experimental control-to-output response                                             | 106         |

| Figure 2.40: Actual circuit schematic-closed loop                                                | 107         |

| Figure 2.41: New model schematic-closed loop                                                     | 108         |

| Figure 2.42: Comparative model schematic-closed loop                                             | 109         |

| Figure 2.43: Averaged models' output voltage superimposed                                        | 111         |

| Figure 2.44: The output voltage of the models superimposed with that of the actual circu         | 1112 nit    |

| Figure 3.1: Erikson two-port network                                                             |             |

| Figure 3.2: Waveforms for Erikson two-port network                                               | 117         |

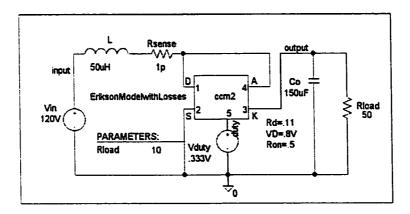

| Figure 3.3: Erikson PSPICE Model-CCM with losses                                                 | 118         |

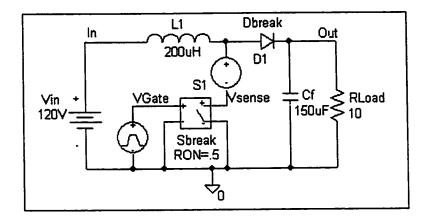

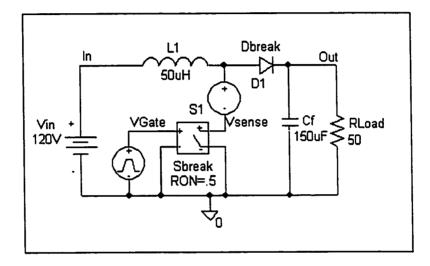

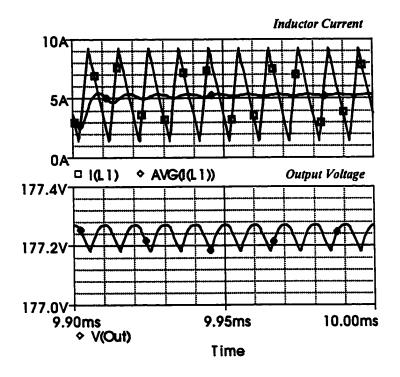

| Figure 3.4: Actual Boost with non-ideal components                                               |             |

| Figure 3.5: Actual Boost waveforms- $i_L(t)$ top and $v_o(t)$ bottom                             | 120         |

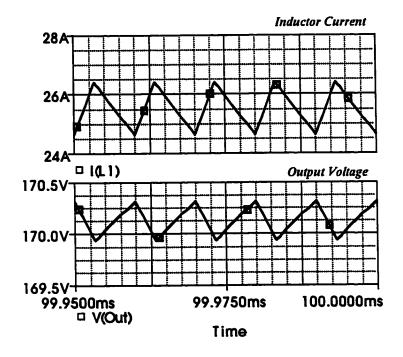

| Figure 3.6: Erikson loss-based, CCM model                                                        |             |

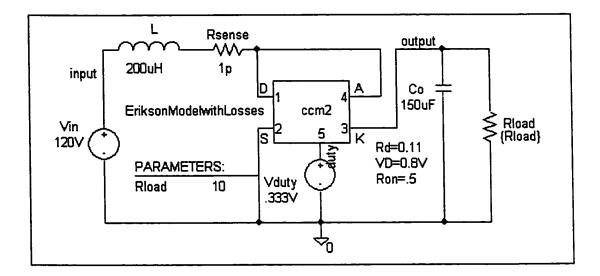

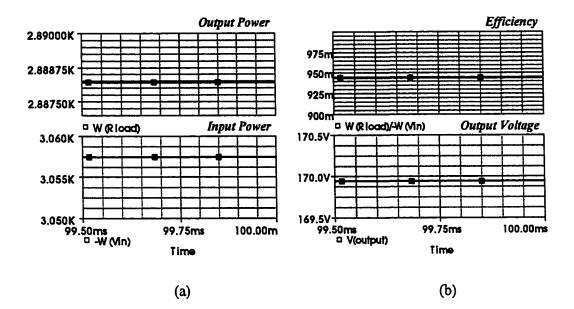

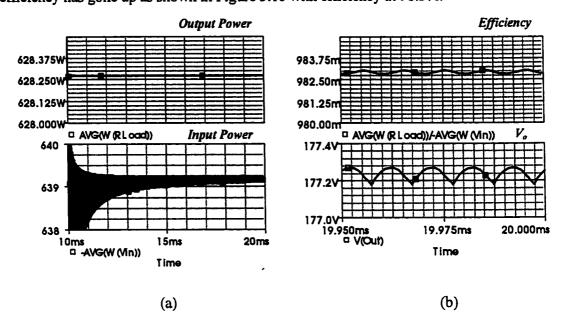

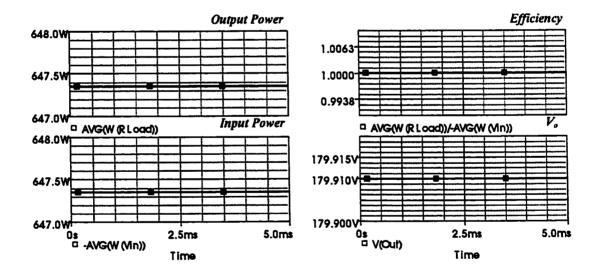

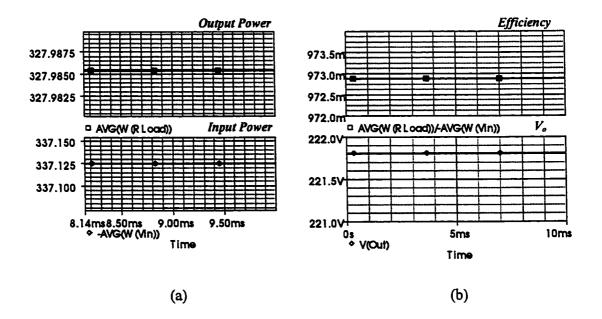

| Figure 3.7: Power balance and output for Erikson model (a) $P_{in}$ (top) $P_{out}$ (bottom)     |             |

| efficiency (top) V <sub>o</sub> (bottom)                                                         |             |

| Figure 3.8: Lossless boost model                                                                 |             |

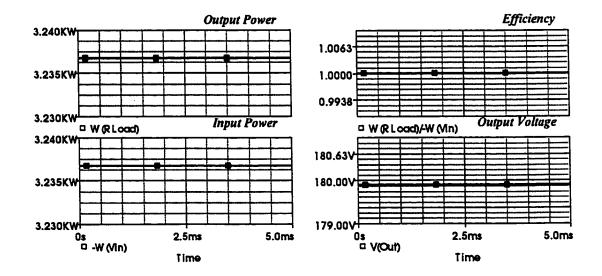

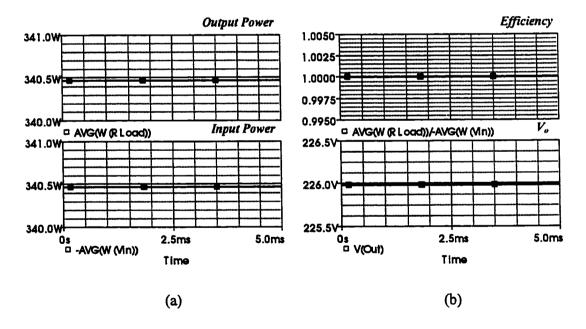

| Figure 3.9: Power balance and output for lossless boost model (a) $P_{in}$ (top) $P_{out}$ (both | tom)        |

| (b) efficiency (top) $V_o$ (bottom)                                                              |             |

| Figure 3.10: Actual circuit used for comparison simulation                                       |             |

| Figure 3.11: Power balance and output for actual circuit (a) $P_{in}$ (top) $P_{out}$ (bottom)   |             |

| efficiency (top) $V_o$ (bottom)                                                                  |             |

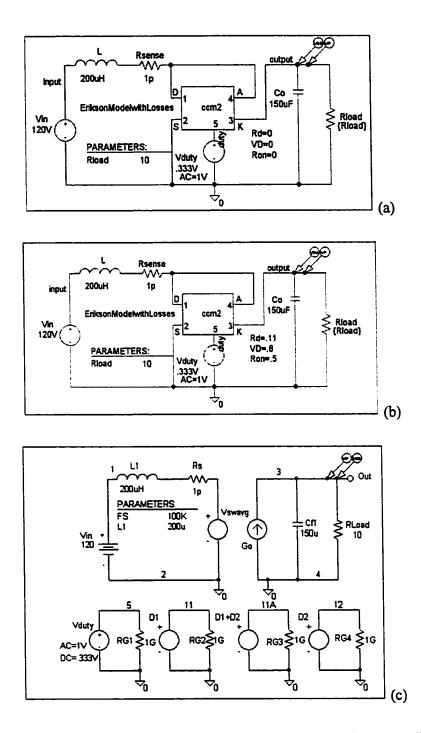

| Figure 3.12: Schematics for small-signal curves (a) Erikson lossless (b) Erikson with d          |             |

| and switch loss (c) Proposed model lossless                                                      |             |

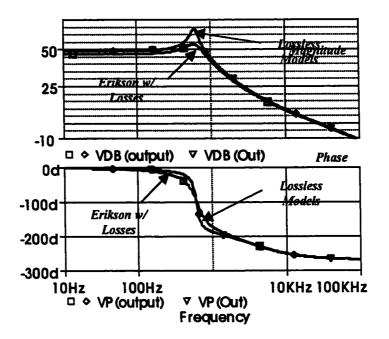

| Figure 3.13: Small-signal curves superimposed                                                    |             |

| Figure 3.14: Actual circuit with high ripple                                                     | . 129       |

е .

| Figure 3.15: Actual circuit waveforms for high ripple case- $i_L(t)$ top and $v_o(t)$ bottom 130                |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 3.16: Power balance and output voltage for high ripple case (a) $P_{in}$ (top) $P_{out}$                 |

| (bottom) (b) efficiency (top) $V_o$ (bottom)                                                                    |

| Figure 3.17: Erikson model for high ripple case                                                                 |

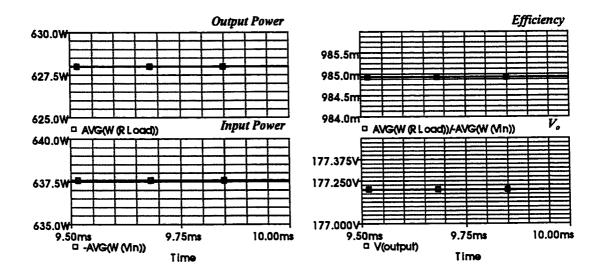

| Figure 3.18: Power balance and output voltage for high ripple using Erikson model (a) $P_{in}$                  |

| (top) $P_{out}$ (bottom) (b) efficiency (top) $V_o$ (bottom)                                                    |

| Figure 3.19: Lossless boost model for high ripple CCM case                                                      |

| Figure 3.20: Power balance and output voltage for high ripple using lossless model (a) $P_{in}$                 |

| (top) $P_{out}$ (bottom) (b) efficiency (top) $V_o$ (bottom)                                                    |

| Figure 3.21: Inductor current with ideal (solid line) and non-ideal (dashed line) components136                 |

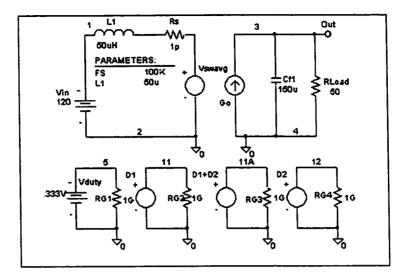

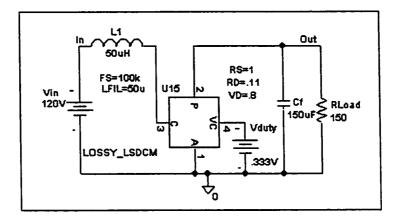

| Figure 3.22: DCM PWM switch circuit model with conduction losses                                                |

| Figure 3.23: PSPICE DCM conduction loss model 141                                                               |

| Figure 3.24: Actual boost circuit with losses operating in DCM 142                                              |

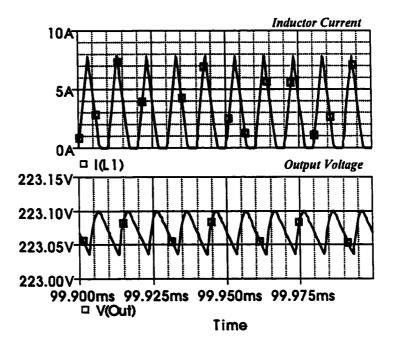

| Figure 3.25: Actual circuit waveforms for DCM- $i_L(t)$ top and $v_o(t)$ bottom                                 |

| Figure 3.26: Power balance and output voltage for the actual circuit (DCM) (a) $P_{in}$ (top)                   |

| $P_{out}$ (bottom) (b) efficiency (top) $V_o$ (bottom)                                                          |

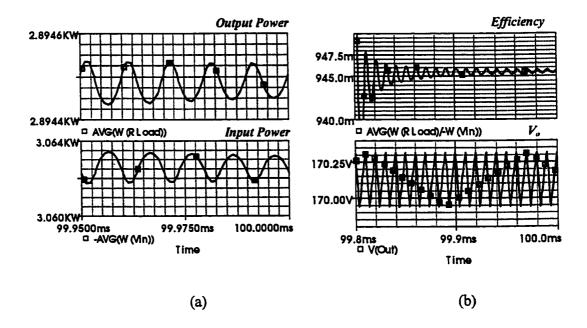

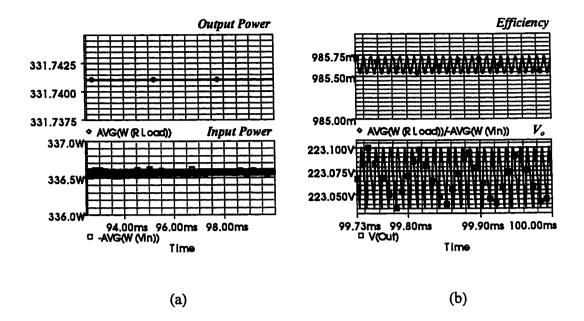

| Figure 3.27: DCM conduction loss model 144                                                                      |

| Figure 3.28: Power balance and output voltage for DCM conduction loss model (a) $P_{in}$ (top)                  |

| $P_{out}$ (bottom) (b) efficiency (top) $V_o$ (bottom)                                                          |

| Figure 3.29: Lossless boost model in DCM                                                                        |

| Figure 3.30: Power balance and output voltage for DCM lossless model (a) P <sub>in</sub> (top) P <sub>out</sub> |

| (bottom) (b) efficiency (top) $V_o$ (bottom)                                                                    |

| Figure 3.31: Approximated nonideal boost DCM waveforms                                                          |

| Figure 3.32: Diode loss element location in the boost model 150                                                 |

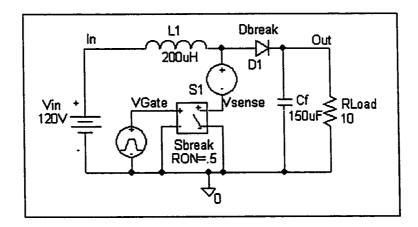

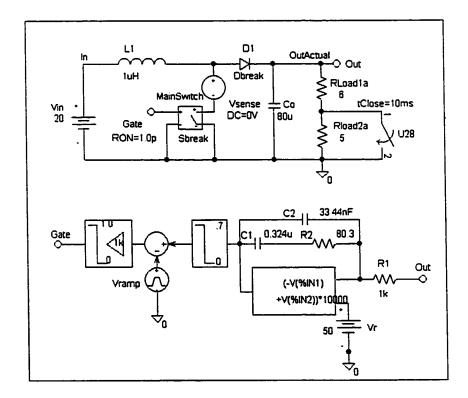

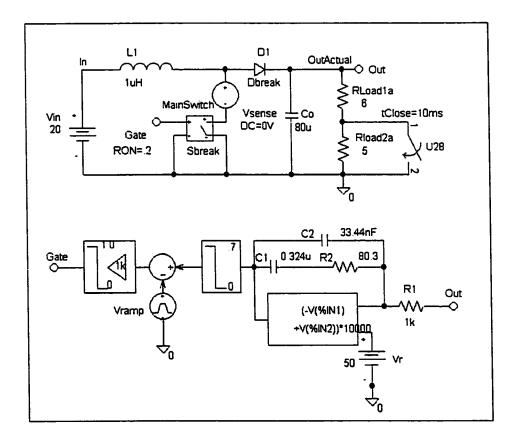

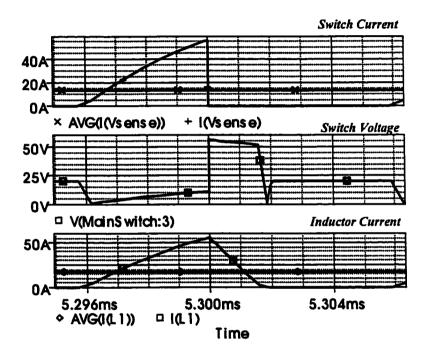

| Figure 3.33: Actual boost with Dbreak and ideal switch 152                                                      |

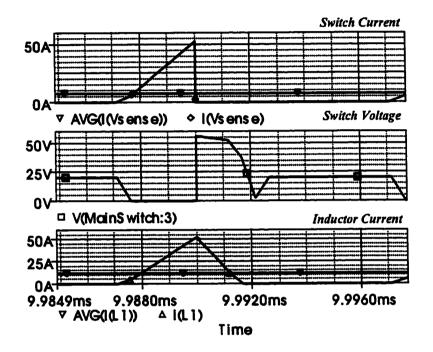

| Figure 3.34: Actual boost simulation results: switch current (top), switch voltage (middle),                    |

| inductor current (bottom)153                                                                                    |

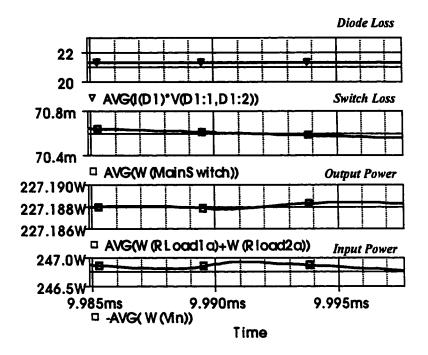

| Figure 3.35: Actual boost simulation results: diode loss (top), switch loss ,output power,                      |

| input power (bottom)154                                                                                         |

| Figure 3.36: Average boost model with diode loss model                                                          |

| Figure 3.37: Solution of average model with diode loss                                                          |

| Figure 3.38: Solution of the ideal average model without diode loss                                             |

| Figure 3.39: Boost model with diode and switch losses 161                                                       |

| Figure 3.40: Actual boost circuit with switch and diode losses                                                  |

| Figure 3.41: Key waveforms of actual boost circuit with switch and diode losses                                 |

| Figure 3.42: Prototype schematic diagram 166                                                                    |

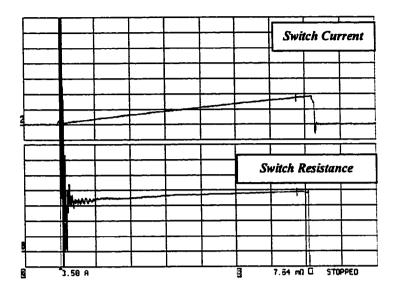

| Figure 3.43: Drain current and calculated on-resistance of main switch                                          |

| Figure 3.44: Loss-based model derived for circuit of Figure 3.42 171                                            |

| Figure 3.45: Actual circuit simulation of prototype 173                                                         |

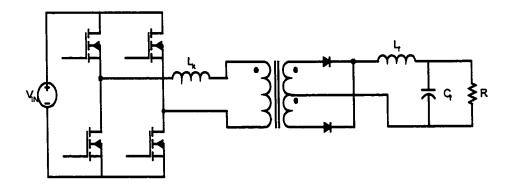

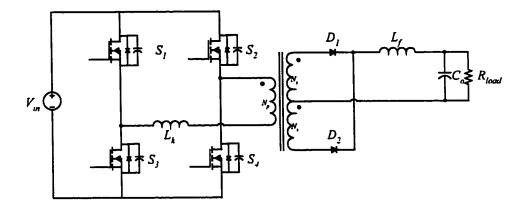

| Figure 4.1: FB-ZVS topology 181                                                                                 |

| Figure 4.2: FB-ZCS topology 182                                                                                 |

|                                                                                                                 |

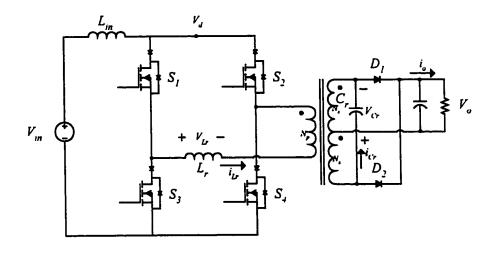

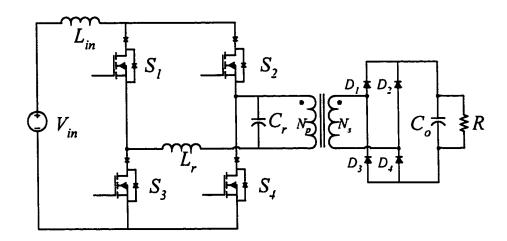

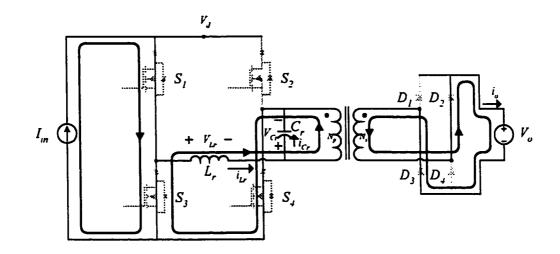

| Figure 4.3: Simplified high-voltage FB-ZCS converter                                 | 185        |

|--------------------------------------------------------------------------------------|------------|

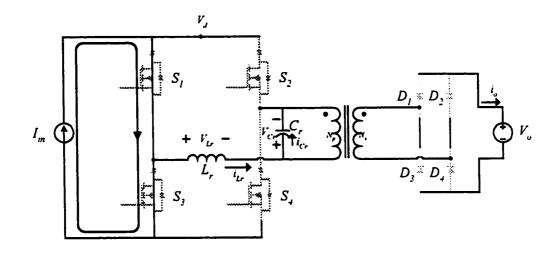

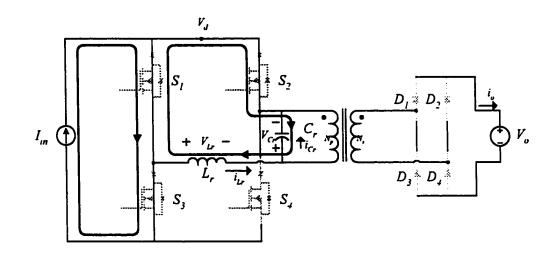

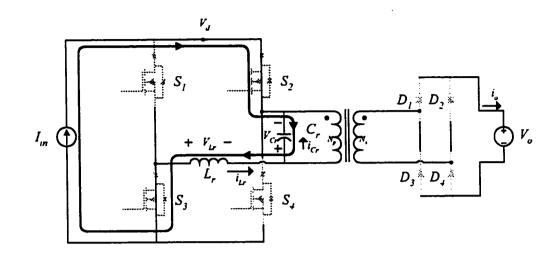

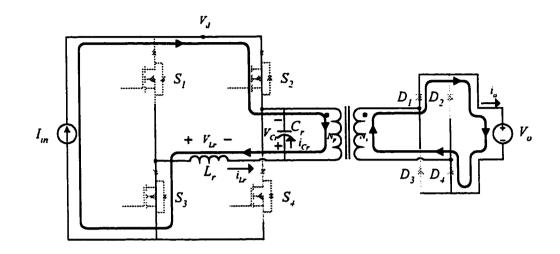

| Figure 4.4: FB-ZCS Mode I                                                            | 187        |

| Figure 4.5: FB-ZCS Mode II                                                           | 189        |

| Figure 4.6: FB-ZCS Mode III                                                          |            |

| Figure 4.7: FB-ZCS Mode IV                                                           | 194        |

| Figure 4.8: FB-ZCS Mode V                                                            | 196        |

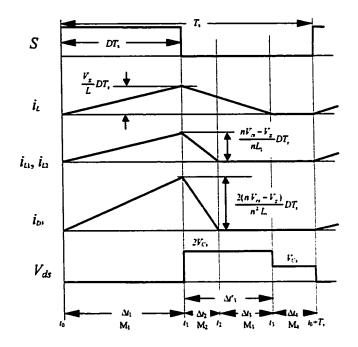

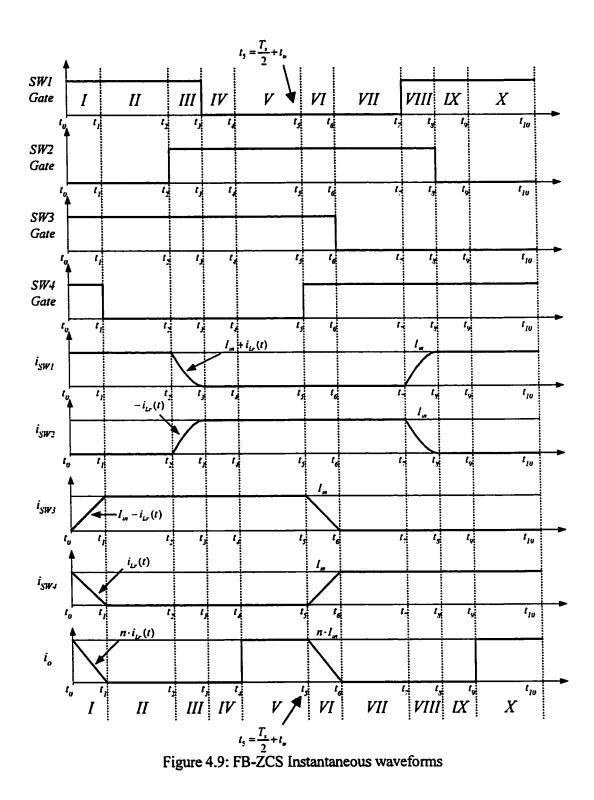

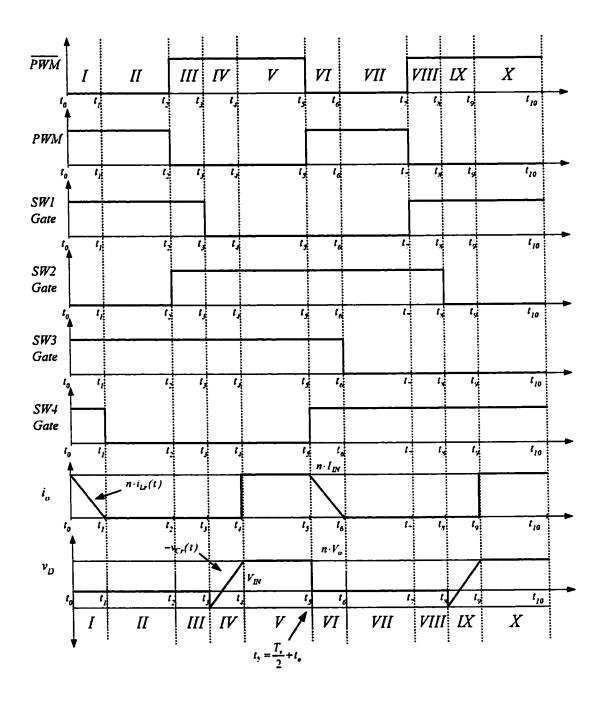

| Figure 4.9: FB-ZCS Instantaneous waveforms                                           | 200        |

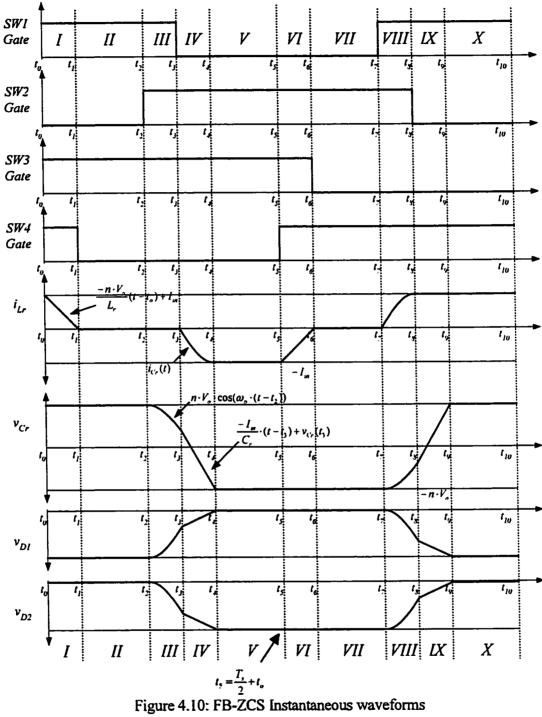

| Figure 4.10: FB-ZCS Instantaneous waveforms                                          | 201        |

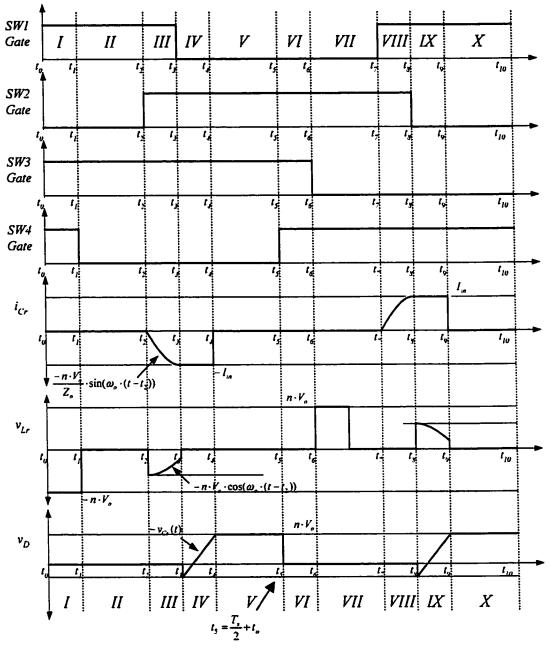

| Figure 4.11: FB-ZCS Instantaneous waveforms                                          | 202        |

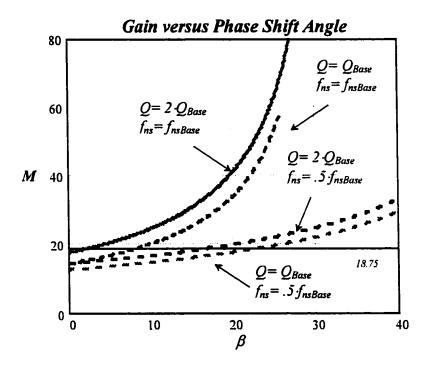

| Figure 4.12: Gain, M, vs. Phase shift angle, $\beta$ for various loads               | 208        |

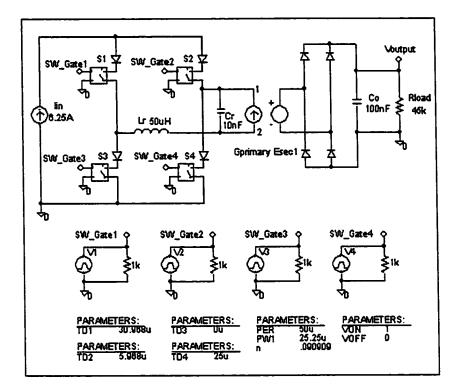

| Figure 4.13: Simulation of design example                                            | 215        |

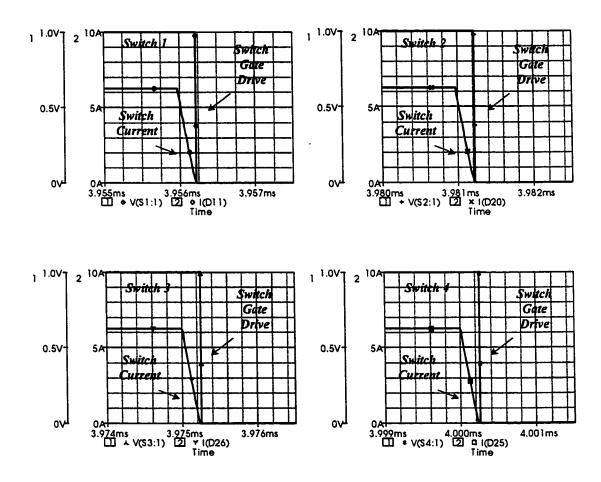

| Figure 4.14: Simulation results of design example-ZCS condition                      | 216        |

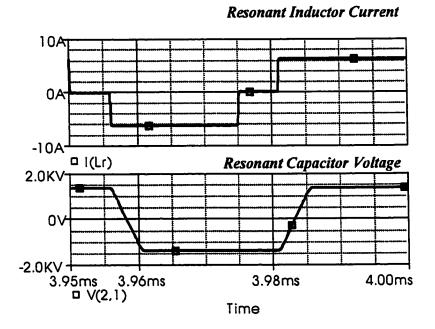

| Figure 4.15: Simulation results of design example (inductor current and capacitor vo | oltage)217 |

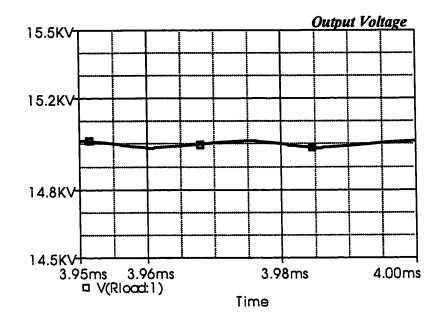

| Figure 4.16: Simulation results for design example-output voltage                    | 218        |

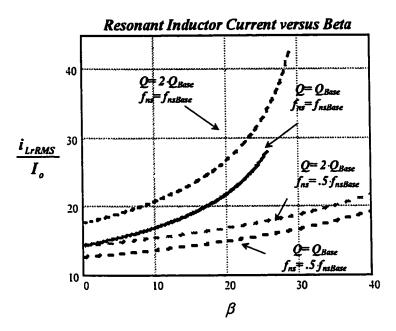

| Figure 4.17: Normalized resonant inductor current                                    | 221        |

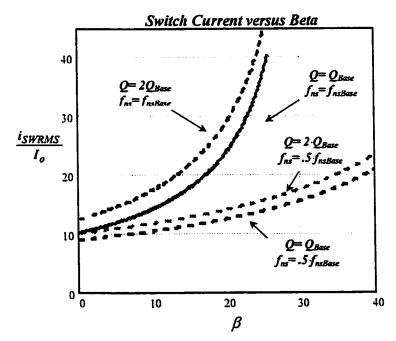

| Figure 4.18: Normalized primary switch current                                       | 221        |

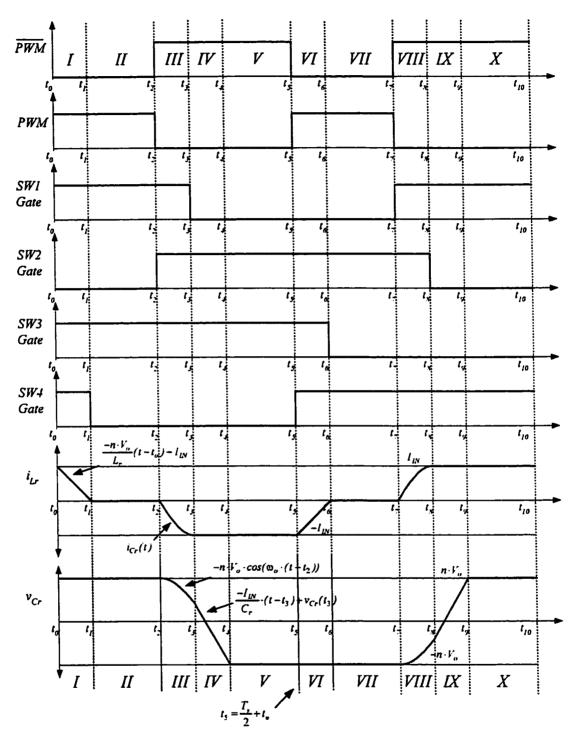

| Figure 5.1: FB-ZCS Instantaneous Waveforms                                           | 227        |

| Figure 5.2: FB-ZCS Instantaneous Waveforms                                           | 228        |

| Figure 5.3: Results of steady state analysis using MathCAD                           | 230        |

| Figure 5.4: Average model for DC and AC Simulations, $Q=Q_{base}$                    |            |

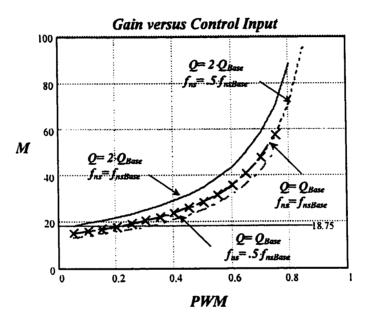

| Figure 5.5: Gain, M, versus control input, PWM                                       | 233        |

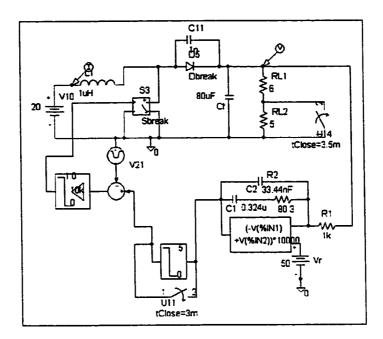

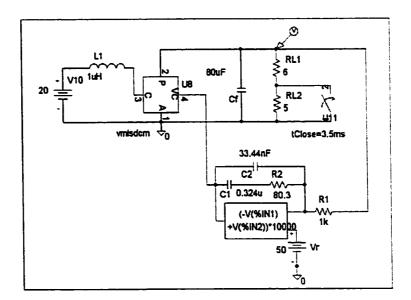

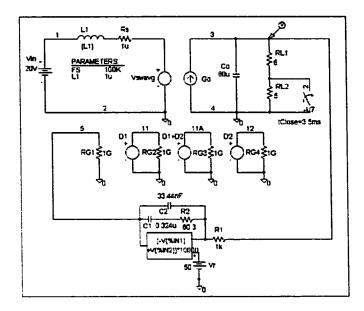

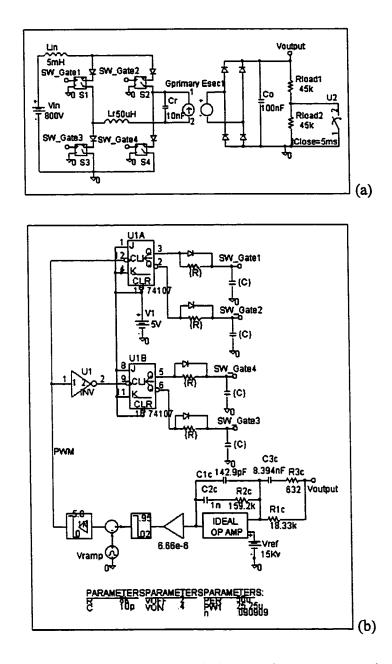

| Figure 5.6: Actual circuit for transient simulations (a) the power stage (b) control | oller and  |

| gate drive                                                                           |            |

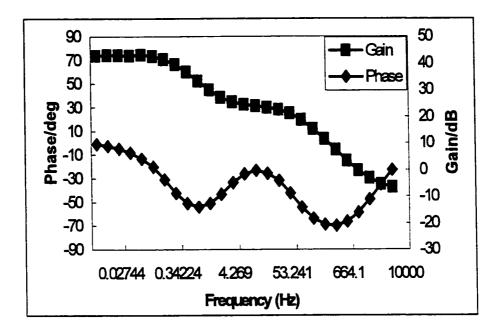

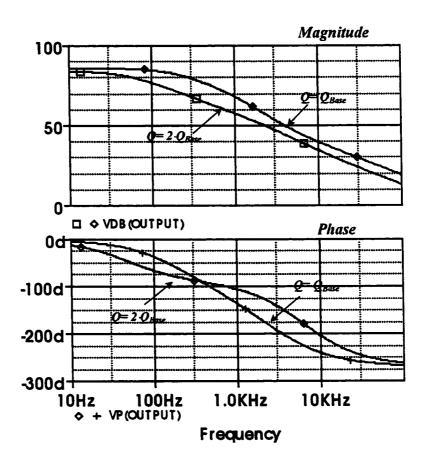

| Figure 5.7: Small-signal characteristics (magnitude and phase), control-to-output    |            |

| Figure 5.8: Small-signal characteristics (magnitude and phase), input-to-output      |            |

| Figure 5.9: Small-signal characteristics (magnitude and phase), output impedance     | 239        |

| Figure 5.10: Average model for transient simulations (a) average model of the pow    | ver stage  |

| (b) controller                                                                       |            |

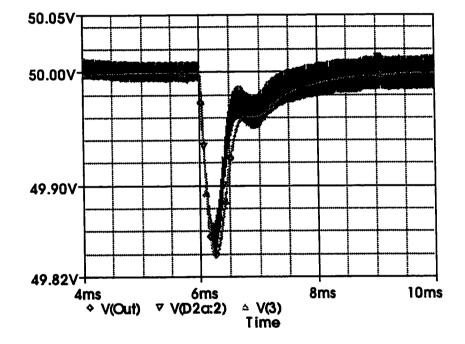

| Figure 5.11: Transient simulation results, step load change from 50% to 100%         | 242        |

•

# LIST OF TABLES

# Number

.

#### Page

| Table 2.1: Boost modeling equations                                |  |

|--------------------------------------------------------------------|--|

| Table 2.2: Modeling equations for Figure 2.34                      |  |

| Table 3.1: Loss comparison                                         |  |

| Table 3.2: Comparison of high ripple case                          |  |

| Table 3.3: DCM conduction loss comparison                          |  |

| Table 3.4: Results comparison for diode loss evaluation            |  |

| Table 3.5: Results comparison for switch and diode loss evaluation |  |

| Table 3.6: Comparison of loss predictions to experimental data     |  |

| Table 4.1: FB-ZCS Mode Summary Table                               |  |

| Table 4.2: Maximum stress table                                    |  |

| Table 4.3: Timing for design example, $Q=Q_{BASE}$                 |  |

| Table 4.4: Theoretical result validation                           |  |

| Table 5.1: PSPICE Model Equations- FB-ZCS                          |  |

| •                                                                  |  |

#### **CHAPTER 1: INTRODUCTION**

Power converter design requires a method for modeling the inevitable disturbances that cause the circuit to deviate from its normal operation (source and load variation, switching time perturbation, component drift etc). Traditionally, this has presented a significant obstacle to design engineers. This difficulty centers on the fact that, in modern power converters, the transistor operates as a switch in either saturation or cut-off states. As a result, depending on the switch's state, the circuit can take on drastically different configurations. This makes conventional circuit analysis significantly more difficult. Until recently, the bulk of converter modeling was done by the tedious but effective method of state-space averaging, introduced by Dr. S. Cuk, of Cal. Tech. [1]. This method involves formulating a time averaged, state-space representation as a model. The model is then linearized and equations are solved for the linear, or so called small-signal transfer functions. While the method is effective, it is heavily dependent on matrix algebra and equation manipulation, and seems far removed from the primary objective- circuit While model complexities such as on-state resistance and storage time modeling. modulation can be addressed in this method, it is not done in a straightforward manner. Further, the method is not well suited to computer simulation.

1

More recently, equivalent circuit models have been developed [2]. These models are more closely related to the actual circuit and as a result, non-ideal effects are accounted for in a more straightforward way. These equivalent circuits accurately model the non-linear power converter in terms of dc characteristics, as well as large signal, or transient behavior and can be directly input into circuit simulators for simulation. Further, through the use of circuit simulators such as PSPICE, these averaged models, which are generally nonlinear, can be linearized to obtain the converter's small-signal characteristics without any special manipulation of the equivalent circuit model. The small-signal transfer function curves can be used to characterize the power converter's frequency response and serve as the basis for the controller design.

#### 1.1 PWM Converter Overview

The largest and most common family of power electronic circuits is called switch-mode converters because they take on different circuit configurations cyclically during normal operation. This process is facilitated through the use of various nonlinear elements (such as transistors and diodes), which act as switches. As these switches change state, new circuit configurations or "modes" are developed. During operation, the main power switch is gated on for a period and then remains off until the next switching cycle begins. The combined on and off times of the main power switch is fixed and is referred to as the switching cycle, or period,  $T_s$ . While the switching period is, generally, a fixed quantity, the percentage of the period in which the switch is on, is varied, and is called the duty ratio,

D. While the switch is on, energy is drawn from the source and transferred into energy storage elements (inductors and capacitors). When the switch is turned off, this energy is transferred from the energy storage elements to the load of the power converter. By controlling the duty ratio, the energy transferred is also controlled. This process allows the output voltage of the converter to be regulated.

The number of modes of a power converter is dependent on the circuit configuration. By design, as the stored energy in the circuit is passed from one element to another, various nonlinear elements can change state creating additional circuit modes. This concept is more easily understood by example.

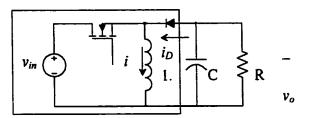

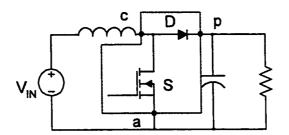

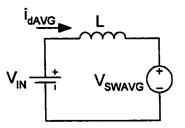

Figure 1.1: Boost converter

In Figure 1.1, one of the classic converter topologies known as boost is shown. On the diagram, the area in the box represents the nonlinear elements in the circuit. The terminal lettering scheme will be used to identify terminal characteristics when we begin to formulate the DC modeling equations.

In this circuit, Mode I begins when the switch is turned on as illustrated in Figure 1.2a. This reverse biases the diode forcing it off and separating the input portion of the circuit from the output portion. During this interval, energy is drawn from the source and stored in the inductor as a current. Controlling the time the circuit is in this mode, DTs, controls the amount of energy stored (where D is the duty ratio of the switch and takes values from 0 to 1). When the appropriate amount of energy is stored, Mode II begins and the switch is turned off as shown in Figure 1.2b. Energy stored in the inductor is transferred to the load as a current thus forcing the diode to conduct.

4

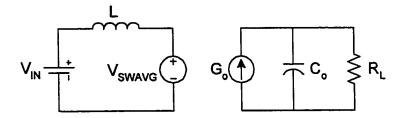

Figure (1.2a)

Figure (1.2c)

Figure 1.2: Equivalent circuit modes (a.) Mode I-S on, D off (b.) Mode II-S off, D on(c.)Mode III-S off, D off

When all the stored energy is transferred to the load, the diode ceases to conduct and converter enters Mode III as shown in Figure 1.2c. The load's energy requirement is now supported by the output capacitor until the beginning of the next switching cycle. It should be noted that the discussion above assumes all the energy in the inductor is passed to the load. As a result, the inductor current goes to zero during this interval. For this reason, this type of operation is called Discontinuous Conduction Mode (DCM). Another possibility is to design the circuit so that only a portion of the energy stored in the inductor is transferred.

This type of operation is called Continuous Conduction Mode (CCM) as the inductor current is not allowed to discharge to zero. This dissertation will largely deal with the DCM mode of operation as it is more widely applicable to Power Factor Correction, hence the focus of our research at UCF. For a detailed treatment of the CCM operation see [2]. The discussion above highlights the nonlinear nature of all modern power converters. This nonlinear nature presents several design problems caused by the difficulty in effectively using circuit modeling and simulation technique. In the subsequent chapters, we will discuss these problems and then present methods for resolution.

Here we will move the discussion to an overview of modeling and simulation as it pertains to modern power converters. In particular, a key goal here is to establish the benefit of modeling the converter versus the use of the actual circuit for simulation and controller design. It will be shown that the use of equivalent circuit models will facilitate control loop design and aid in the simulation process.

As with other systems, modeling and simulation play key roles in the design and development of power converters. During the design phase, modeling and simulation help to set the optimal converter operating point, chose circuit parameters wisely, and helps to produce an effective controller to regulate the output. During the development phase, simulation allows us to evaluate converter performance prior to prototyping.

In modern power converters, classical control loop design techniques (Bode, Nyquist, Root Locus, etc) are not directly applicable, and are only valid for linear systems. From the previous section its clear that the power converter is highly nonlinear. As a result, a linearized model of the power stage is necessary to facilitate the control loop design process. An objective here is to evaluate existing modeling techniques and develop our own method that will facilitate circuit modeling and computer simulation.

The following sections will provide the detail on both the several conventional modeling techniques. Thorough derivations will be presented so that a comparison can be made to the approach presented here.

#### 1.2 The Method of State-Space Averaging

Until recently, most power stage modeling was done by a matrix manipulation method called state-space averaging [1]. The method involves the formulation of a state matrix representation for each mode of operation. For the boost example given earlier, this would mean three different sets of matrices corresponding to the three modes of circuit operation. These state representations are then time averaged to create a single matrix representation of the "averaged" circuit. This single set of state equations can then be linearized by conventional algebraic techniques (Taylor Series Expansion) [1]. The final result is a small-signal transfer function representing the frequency response characteristics of the power stage. Based on this information, the design of the controller can be tailored to these characteristics.

While this method is functional, it has several significant shortcomings. First, since the method is primarily mathematical in nature, it is far removed from the actual circuit of interest. Although the method provides a closed form representation of the power stage in the frequency domain, it does not readily produce an equivalent circuit in terms of a time domain representation. In order to do time-based simulation (transient), designers must either use the actual circuit for simulation or fabricate a circuit model from the state equations generated earlier in the state-space averaging method. Often, the process of developing this equivalent circuit model from the equations requires some level of creativity and experience as no standard methods had existed [2].

The method of state-space averaging allows us to represent the power stage as a linear model (transfer function) and thereby allows the use of classic control theory for design of the closed loop control. However, in terms of time domain simulation, as stated earlier, the state-space averaging method does not readily produce a time domain model suitable for circuit simulation (complex circuit manipulation is required). At this point the reader might note that having tackled the control design issue what further need for modeling is there, particularly when the actual circuit can be used in the simulator for time domain simulations.

While the actual circuit can be used in the circuit simulator, an equivalent circuit model is often preferred. The abrupt discontinuities that occur in the actual circuit as the switch transitions state forces the calculated time step in PSPICE simulation to extremely small increments. These small increments mean an increased number of calculated points and result in more convergence problems and significantly longer simulation times [3].

As a result of these difficulties, the design process has traditionally followed in two different and separate areas. The first involved using state-space averaging to develop a frequency domain model of the power stage for control loop design. The second involved time domain simulation using cleverly formulated equivalent circuit models or the brute force approach, direct simulation of the actual circuit [2].

The discussion will now provide the detailed approach and illustrate the procedure. The topology to be modeled was chosen because it is not easily handled by conventional, averaged equivalent circuit techniques. These difficulties will be discussed in greater detail in subsequent sections. However, these issues do not effect the application of the state-space averaging method, which is generally, more widely applicable.

The methodology is shown in Figure 1.3 as a step by step process which culminates in small-signal transfer functions representing the power stage.

Examining the methodology confirms the notion that state-space averaging is, generally, straightforward. However, under the DCM condition, several assertions made by Cuk are not so obvious. Further, some of these assertions have been scrutinized in open literature [2].

9

Figure 1.3: State-space averaging step by step process

The DCM assumptions differ from the CCM development in the state-space averaging method. The most significant assertion is that Cuk states in [1] that, "the inductor current,

÷.

$i_L$ , ceases to be a true state variable since it has lost its dynamic properties"...(since it does not have free boundary conditions) and he goes further to say that as a result, Equation (1.1) is valid.

$$\frac{d}{dt}i_L = 0 \tag{1.1}$$

Thus, the system of the state model is reduced by an order for each inductor in DCM.

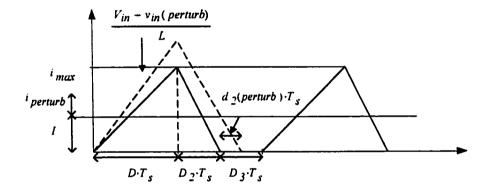

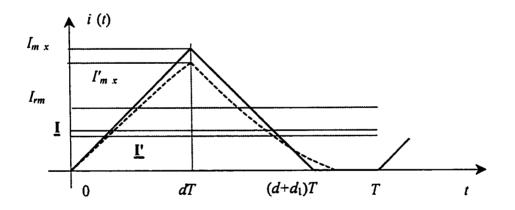

Figure 1.4: Inductor current in DCM

Figure 1.4 illustrates the dynamic properties of inductor current in DCM. Line voltage perturbation does introduce perturbations in the output voltage. Further, from the figure, it is clear that this also causes perturbations in the average inductor current, where the average takes on a unique definition and is defined over the interval,  $(D+D_2)T_s$ .

Cuk also states that the DCM case is in sharp contrast to the CCM case where the average inductor current does not change under small-signal perturbation but rather the initial and final conditions at 0 and  $T_s$  change to accommodate, maintaining the average value. Based on this, the Cuk's argument is finalized by stating that the average inductor current, as defined above, is the quantity that reflects the effect of the introduced perturbation.

To summaries the above discussion, the following assertions by Cuk in the method of statespace averaging set DCM apart from CCM.

- 1. Each discontinuous inductor current derivative is set to zero in the state-space representation.

- 2. An additional equation is added which represents the Cuk defined average inductor current to replace the "lost" state variable.

In particular, Cuk's assertion that system order reduction accompanies DCM operation is actively refuted in [2] stating that this is neither theoretically nor experimentally justifiable. Details about this argument will be explored in subsequent sections.

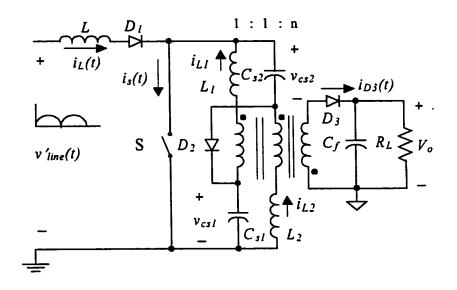

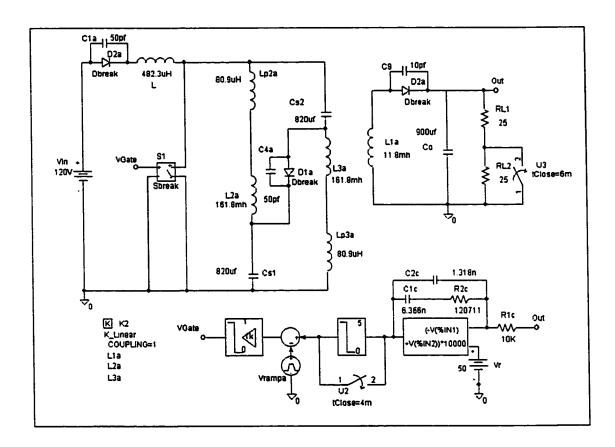

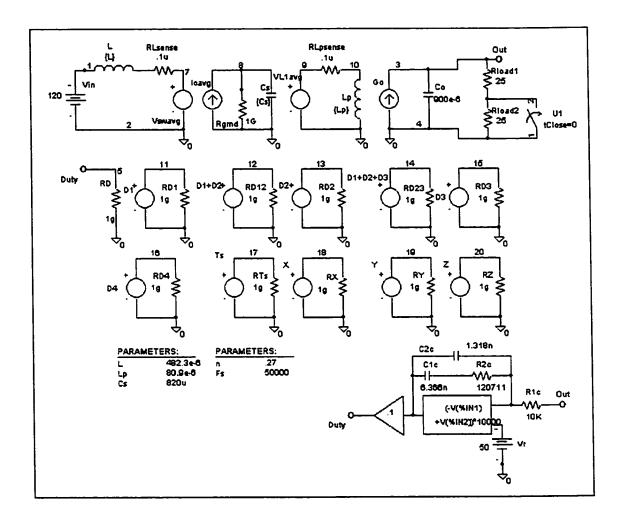

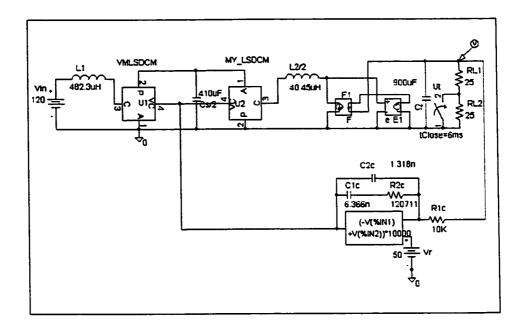

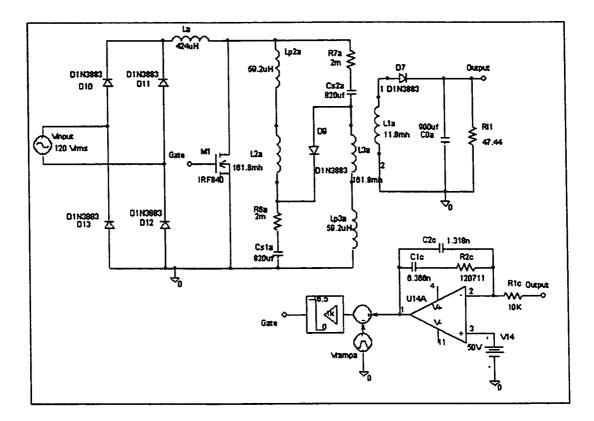

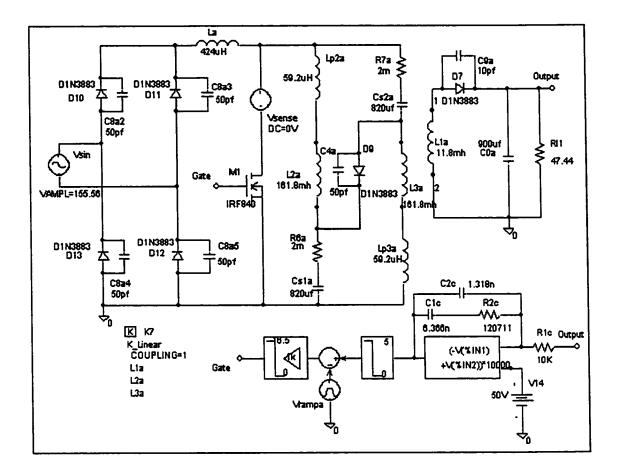

Having presented a flowchart of the methodology of state-space averaging, we now apply the approach to the single stage, single switch, separated PWM Switch converter of Figure 1.5 with its modes operation Figure 1.6. A description of the operation of this circuit is presented in [4] and will not be discussed here. However, it is important to note that the inductors in the circuit operated in DCM and as such, the assertions made previously apply.

Figure 1.5: Single-stage single switch converter

Figure 1.6: Modes of operation of single-stage single switch converter

From the flowchart of Figure 1.3, the first step is to create a state-space representation for each circuit mode of Figure 1.6. It should be noted that since  $L_p=L_l=L_2$  and  $C_s=C_{sl}=C_{s2}$  appear in identically functioning branches, inclusion of both branches in the state vector would lead to a non-minimal realization. Therefore, the state vector is fourth order and is given as:  $[v_{cs} v_{Co} i_L i_{Lp}]$ .

The A matrix development is step one in the methodology and is shown as Equations (1.2)-(1.4)

$$A_{1} \cdot d + A_{2} \cdot d_{1} + A_{3} \cdot d_{2} + A_{4} \cdot \left[ 1 - (d + d_{1} + d_{2}) \right] = A$$

(1.3)

(1.2)

$$A = \begin{bmatrix} 0 & 0 & \frac{(d_1 + d_2)}{C_s} & \frac{(-d + d_1)}{C_s} \\ 0 & \frac{-1}{(R \cdot C_0)} & 0 & 2 \cdot \frac{(d + d_1)}{(n \cdot C_0)} \\ -2 \cdot \frac{(d_1 + d_2)}{L} & 0 & 0 & 0 \\ \frac{-(-d + d_1)}{L_p} & \frac{-(d + d_1)}{(n \cdot L_p)} & 0 & 0 \end{bmatrix}$$

(1.4)

The next step is to average the state-space representations developed in step one above. This is done by Equation (1.3) and yields a final result shown as Equation (1.4).

The B and C matrices are formulated in a similar fashion and are shown as Equations (1.5) and (1.6).

$$B = \begin{bmatrix} 0 \\ 0 \\ \frac{(d + d_1 + d_2)}{L} \\ 0 \end{bmatrix}$$

(1.5)

$$C = (0 \ 1 \ 0 \ 0) \tag{1.6}$$

Based on the Cuk DCM assumptions presented earlier, additional equations are obtained by writing the expressions for the Cuk defined average inductor currents. These equations are readily obtained by inspection of the instantaneous waveforms of the converter shown in Figure 1.7.

Figure 1.7: Instantaneous waveforms of single-stage single switch converter

Although the DC and AC relationships are usually derived simultaneously by separation, the development here will derive the DC relationships first for the sake of clarity. The DC relationships can be found by setting derivative vector in the state-space representation to zero and substituting DC variable names throughout. In the DC state vector,  $I_L$  and  $I_{Lp}=$  $I_{LI}=I_{L2}$  are directly substituted

$$x = A \cdot x + B \cdot u \tag{1.7}$$

16

$$y = C \cdot x$$

$$A \cdot X + B \cdot U = 0$$

$$Y = C \cdot X$$

(1.8)

$$\begin{bmatrix} 0 & 0 & \frac{(D_{1} + D_{2})}{C_{s}} & \frac{(-D + D_{1})}{C_{s}} \\ 0 & \frac{-1}{(R \cdot C_{0})} & 0 & \frac{2 \cdot \frac{(D + D_{1})}{(n \cdot C_{0})}}{\frac{1}{2} \cdot \frac{U_{p}}{2} \cdot \frac{D}{L} \cdot D \cdot T_{s}} \\ -\frac{2 \cdot \frac{(D_{1} + D_{2})}{L} & 0 & 0 & 0 \\ \frac{-(-D + D_{1})}{L_{p}} & \frac{-(D + D_{1})}{(n \cdot L_{p})} & 0 & 0 \end{bmatrix} \cdot \begin{bmatrix} V_{cs} \\ V_{o} \\ \frac{1}{2} \cdot \frac{N_{gs}}{L} \cdot D \cdot T_{s} \\ \frac{1}{2} \cdot \frac{n \cdot V_{cs} - V_{0}}{n \cdot L_{p}} \cdot D \cdot T_{s} \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ \frac{(D + D_{1} + D_{2})}{L} \\ 0 \end{bmatrix} \cdot V_{g} = 0$$

$$(1.9)$$

Separating the matrix representation of Equation (1.9) and normalizing by Equation set (1.10), the DC relationships are presented in Equation set (1.11).

$$M = \frac{V_{0}}{V_{g}} \qquad m = \frac{V_{cs}}{V_{0}} \qquad \tau_{n} = \frac{L}{R} \qquad k = \frac{L_{p}}{L} \qquad (1.10)$$

$$\left[m \cdot n \cdot (D - D_{1}) + D_{1} - D\right] \cdot M + (-D_{1} - D_{2}) \cdot n \cdot k = 0$$

$$(m \cdot n - 1) \cdot D^{2} + (m \cdot n \cdot D_{1} - D_{1}) \cdot D - n^{2} \cdot k \cdot \tau_{n} = 0$$

$$2 \cdot m \cdot M \cdot (D_{1} + D_{2}) - D - D_{1} - D_{2} = 0$$

$$m \cdot n \cdot (D - D_{1}) - D - D_{1} = 0 \qquad (1.11)$$

Using MathCAD's symbolic solver, Equation set (1.11) can be solved for any variable in terms of constant circuit parameters. The solution of these equations provides the DC

operating point data used for substitution into the AC equations in step 7 of Figure 1.3. Next, the AC relationships will be presented as Equation set (1.12).

$$C_{s} \cdot \frac{d}{dt} v_{cs} = (d_{1} + d_{2}) \cdot i_{L} + (d_{1} - d) \cdot i_{Lp}$$

$$C_{o} \cdot \frac{d}{dt} v_{o} = \frac{-v_{o}}{R} + \frac{2 \cdot (d + d_{1})}{n} \cdot i_{Lp}$$

$$L \cdot \frac{d}{dt} i_{L} = -2 \cdot (d_{1} + d_{2}) \cdot v_{cs} + (d + d_{1} + d_{2}) \cdot v_{g}$$

$$L_{p} \cdot \frac{d}{dt} i_{Lp} = (d - d_{1}) \cdot v_{cs} - \frac{(d_{1} + d)}{n} \cdot v_{o}$$

$$i_{L} = \frac{1}{2} \cdot \frac{v_{g}}{L} \cdot d \cdot T_{s}$$

$$i_{Lp} = \frac{1}{2} \cdot \frac{\left(v_{cs} - \frac{v_{o}}{n}\right)}{L_{p}} \cdot d \cdot T_{s}$$

(1.12)

Next, small perturbations are introduced into the steady state quantities by substituting Equation set (1.13) into Equation set (1.12), and then by setting discontinuous inductor currents to zero in accordance with the Cuk method to yield Equation set (1.14).

$v_{g} \equiv V_{g} + v_{gac} \qquad i_{Lp} \equiv I_{Lp} + i_{Lpac}$   $v_{cs} \equiv V_{cs} + v_{csac} \qquad d \equiv D + d_{ac}$   $v_{o} \equiv V_{o} + v_{oac} \qquad d_{1} \equiv D_{1} + d_{1ac}$   $i_{L} \equiv I_{L} + i_{Lac} \qquad d_{2} \equiv D_{2} + d_{2ac}$

$$C_{s} \frac{d}{dt} v_{csac} = (D_{1} + D_{2}) \cdot i_{Lac} + (d_{1ac} + d_{2ac}) \cdot i_{L} + (D_{1} - D) \cdot i_{Lpac} + (d_{1ac} - d_{ac}) \cdot i_{Lp}$$

$$C_{o} \frac{d}{dt} v_{oac} = \frac{-v_{oac}}{R} + \frac{2}{n} \cdot \left[ (D + D_{1}) \cdot i_{Lpac} + (d_{ac} + d_{1ac}) \cdot i_{Lp} \right]$$

$$0 = -2 \cdot (D_{1} + D_{2}) \cdot v_{csac} - 2 \cdot (d_{1ac} + d_{2ac}) \cdot v_{cs} + (D + D_{1} + D_{2}) \cdot v_{gac} + (d_{ac} + d_{1ac} + d_{2ac}) \cdot v_{g}$$

$$0 = (D - D_{1}) \cdot v_{csac} + (d_{ac} - d_{1ac}) \cdot v_{cs} - \frac{1}{n} \cdot (D_{1} + D) \cdot v_{oac} - \frac{1}{n} \cdot (d_{1ac} + d_{ac}) \cdot v_{o}$$

$$i_{Lac} = \frac{I_{L}}{D} \cdot d_{ac} + \frac{I_{L}}{V_{g}} \cdot v_{gac}$$

$$i_{Lac} = \frac{\left(v_{csac} - \frac{v_{oac}}{n}\right)}{D} I_{ac} + \frac{I_{L}p}{d}$$

(1.13)

$${}^{i}Lpac = \frac{V_{o}}{\left(V_{cs} - \frac{V_{o}}{n}\right)} \cdot {}^{i}Lp + \frac{1}{D} \cdot {}^{d}ac$$

(1.14)

Taking the Laplace transform of the AC equations and making variable assignments to simplify we arrive at Equation sets (1.15) through (1.54) with the transfer function shown as Equation (1.55).

$$0 = A \cdot v_g(s) + B \cdot d_1(s) + C \cdot d_2(s) + E \cdot v_o(s) + F \cdot d(s)$$

$$(1.15)$$

$$G_{s} \cdot v_0(s) = H \cdot d_1(s) + I \cdot v_0(s) + J \cdot d(s)$$

(1.16)

$$\left( \operatorname{K} \cdot d_{1}(s) - \operatorname{L} \cdot v_{0}(s) - \operatorname{M} \cdot d(s) \right) \cdot s = \operatorname{N} \cdot d_{2}(s) + \operatorname{O} \cdot v_{g}(s) + \operatorname{P} \cdot d_{1}(s) + \operatorname{Q} \cdot v_{0}(s) + \operatorname{R} \cdot d(s)$$

$$(1.17)$$

$$A = (D + D_1 + D_2)$$

(1.18)

$$B = \frac{\left(2 \cdot D_1 \cdot V_0 + 2 \cdot n \cdot V_{cS} \cdot D - V_{g'} n \cdot D + 2 \cdot D_2 \cdot V_{cS} \cdot n + 2 \cdot D_2 \cdot V_0 + V_{g'} n \cdot D_1\right)}{\left[n \cdot \left(D_1 - D\right)\right]}$$

(1.19)

$$C = \left(-2 \cdot V_{cs} + V_{g}\right) \tag{1.20}$$

$$E = 2 \cdot \frac{\left(D_{1}^{2} + D_{1} \cdot D + D_{2} \cdot D_{1} + D_{2} \cdot D\right)}{\left[n \cdot (D_{1} - D)\right]}$$

(1.21)

$$F = \frac{\left(-2 \cdot D_{1} \cdot V_{cs} \cdot n + 2 \cdot D_{2} \cdot V_{o} - V_{g'} \cdot n \cdot D - 2 \cdot D_{2} \cdot V_{cs} \cdot n + V_{g'} \cdot n \cdot D_{1} + 2 \cdot D_{1} \cdot V_{o}\right)}{\left[n \cdot \left(D_{1} - D\right)\right]}$$

(1.22)

$$G = C_0 \tag{1.23}$$

$$H = 4 \cdot I_{Lp} \cdot \frac{\left(D_1 \cdot V_o + D \cdot V_{cs} \cdot n\right)}{\left[\left(-n \cdot V_{cs} + V_o\right) \cdot \left[n \cdot \left(D_1 - D\right)\right]\right]}$$

(1.24)

$$I = \frac{-\left(n \cdot V_{o} \cdot D_{1} - 4 \cdot I_{Lp} \cdot R \cdot D_{1}^{2} - n^{2} \cdot V_{cs} \cdot D_{1} - 4 \cdot I_{Lp} \cdot R \cdot D \cdot D_{1} - D \cdot n \cdot V_{o} + D \cdot n^{2} \cdot V_{cs}\right)}{\left[\left(-n \cdot V_{cs} + V_{o}\right) \cdot \left[n \cdot \left[\left(D_{1} - D\right) \cdot R\right]\right]\right]}$$

(1.25)

$$J = 2 \cdot \left( D_1^2 + 2 \cdot D \cdot D_1 - D^2 \right) \cdot \frac{I_{Lp}}{\left[ n \cdot \left[ \left( D_1 - D \right) \cdot D \right] \right]}$$

(1.26)

20

$$K = -C_{s} \cdot \frac{\left(n \cdot V_{cs} + V_{o}\right)}{\left[n \cdot \left(D_{1} - D\right)\right]}$$

(1.27)

$$L = C_{s} \cdot \frac{(D + D_{l})}{\left[n \cdot (D_{l} - D)\right]}$$

(1.28)

$$M = C_{s} \cdot \frac{\left(-n \cdot V_{cs} + V_{o}\right)}{\left[n \cdot \left(D_{1} - D\right)\right]}$$

(1.29)

$$N = I_{L}$$

(1.30)

$$O = (D_1 + D_2) \cdot \frac{I_L}{V_g}$$

(1.31)

$$P = \frac{(2 \cdot I_{Lp} \cdot V_0 + I_L \cdot V_0 - I_L \cdot n \cdot V_{cs})}{(-n \cdot V_{cs} + V_0)}$$

(1.32)

$$Q = 2 \cdot I_{Lp} \cdot \frac{D_1}{(-n \cdot V_{cs} + V_0)} \qquad R = \left[\frac{(D_1 + D_2)}{D} \cdot I_L + \frac{(D_1 - D)}{D} \cdot I_{Lp}\right] \qquad (1.33)$$

These equations can be solved to plot the small-signal characteristics for a given DC operating point. For the given DC operating point, the steady state parameters are solved from Equations (1.34) through (1.54), where voltage is in the unit volts, resistance is in ohms.

$$V_0 := 50$$

(1.34)

$$V_g := 120$$

(1.35)

$$M := \frac{V_0}{V_g}$$

(1.36)

$$T_s := \frac{1}{50000}$$

(1.37)

$$n := 27$$

(1.38)

$$R := 50$$

(1.39)

$$C_0 := 900 \cdot 10^{-6}$$

(1.40)

$$L := 482.3 \cdot 10^{-6}$$

(1.41)

$$L_p := 80.9 \cdot 10^{-6}$$

(1.42)

$$k := \frac{L_p}{L}$$

(1.43)

$$k_L := \frac{2L_p}{R \cdot T_s}$$

(1.44)

$$k_L := \frac{2L}{R \cdot T_s}$$

(1.45)

$$\tau_n := \frac{L_n}{T_s}$$

(1.47)

•

22

$$\mathbf{m} := \frac{1}{\left[8 \cdot \left(M^2 \cdot n\right)\right]} \cdot \left(n^2 \cdot \mathbf{k} + 2 \cdot \mathbf{M} \cdot \mathbf{n} + 4 \cdot \mathbf{M}^2 + \sqrt{n^4 \cdot \mathbf{k}^2 + 4 \cdot n^3 \cdot \mathbf{k} \cdot \mathbf{M} + 24 \cdot n^2 \cdot \mathbf{k} \cdot \mathbf{M}^2 + 4 \cdot \mathbf{M}^2 \cdot n^2 - 16 \cdot \mathbf{M}^3 \cdot \mathbf{n} + 16 \cdot \mathbf{M}^4\right)$$

(1.48)

$$V_{cs} := m \cdot V_o \tag{1.49}$$

$$I_{Lp} := \frac{(m \cdot n - 1) \cdot D \cdot V_o}{n \cdot k_{Lp} \cdot R}$$

(1.50)

$$D_2 := \frac{D}{2 \cdot m \cdot M - 1} - D_1 \tag{1.51}$$

$$I_{L} := \frac{V_{0} \cdot D}{M \cdot k_{L} \cdot R}$$

(1.52)

$$D_{1} := D \cdot \frac{(m \cdot n - 1)}{m \cdot n + 1}$$

(1.53)

$$D := \frac{1}{\left[2 \cdot \left[\sqrt{m} \cdot (m \cdot n - 1)\right]\right]} \cdot \sqrt{2} \cdot \sqrt{k} \cdot \sqrt{\tau_n} \cdot \sqrt{m^2 \cdot n^2 - 1}$$

(1.54)

Equation (1.55) shows the control to output transfer function with variable assignments. Equation (1.55) is solved for the control to output transfer function at the given operation point and shown in Equation (1.56).

$$\frac{\mathbf{v}_{0}(s)}{\mathbf{d}(s)} = -\mathbf{l} \cdot \frac{\left(\mathbf{C} \cdot \mathbf{s} \cdot \mathbf{M}_{new} \cdot \mathbf{H} + \mathbf{C} \cdot \mathbf{s} \cdot \mathbf{K} \cdot \mathbf{J} - \mathbf{C} \cdot \mathbf{P} \cdot \mathbf{J} + \mathbf{C} \cdot \mathbf{R} \cdot \mathbf{H} + \mathbf{B} \cdot \mathbf{N} \cdot \mathbf{J} - \mathbf{F} \cdot \mathbf{N} \cdot \mathbf{H}\right)}{\left(\mathbf{C} \cdot \mathbf{s} \cdot \mathbf{K} \cdot \mathbf{I} + \mathbf{B} \cdot \mathbf{N} \cdot \mathbf{I} + \mathbf{C} \cdot \mathbf{Q} \cdot \mathbf{H} + \mathbf{C} \cdot \mathbf{P} \cdot \mathbf{G} \cdot \mathbf{s} - \mathbf{C} \cdot \mathbf{P} \cdot \mathbf{I} + \mathbf{C} \cdot \mathbf{s} \cdot \mathbf{L} \cdot \mathbf{H} - \mathbf{C} \cdot \mathbf{K} \cdot \mathbf{G} \cdot \mathbf{s}^{2} - \mathbf{E} \cdot \mathbf{N} \cdot \mathbf{H} - \mathbf{B} \cdot \mathbf{N} \cdot \mathbf{G} \cdot \mathbf{s}\right)}$$

$$(1.55)$$

Substituting the previous equations into Equation (1.55), we arrive at the numerical control to output transfer function in Equation (1.56).

$$H_{d}(s) := \frac{653 \, \text{l}(s+17.78)}{s^2 + 497.7s + 947.2} \tag{1.56}$$

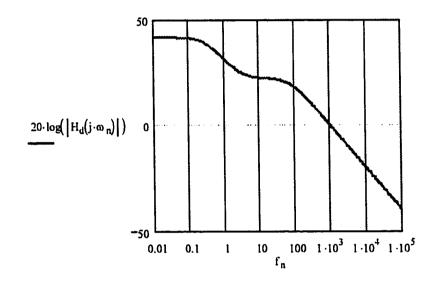

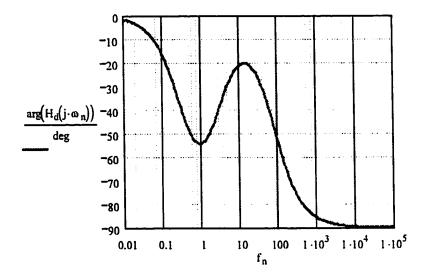

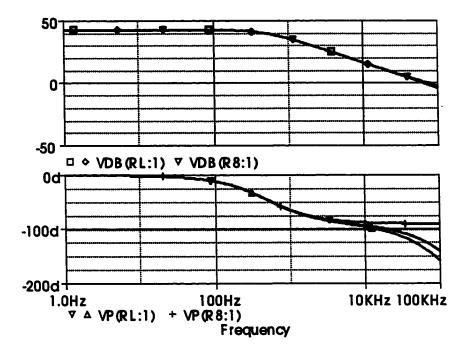

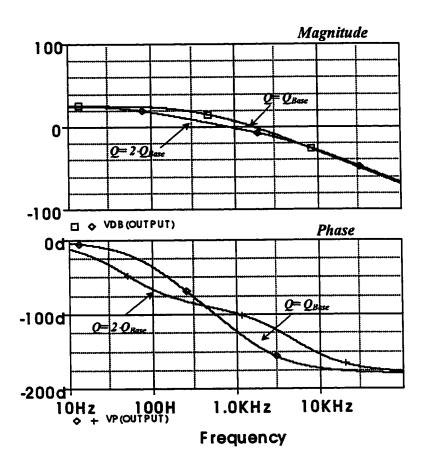

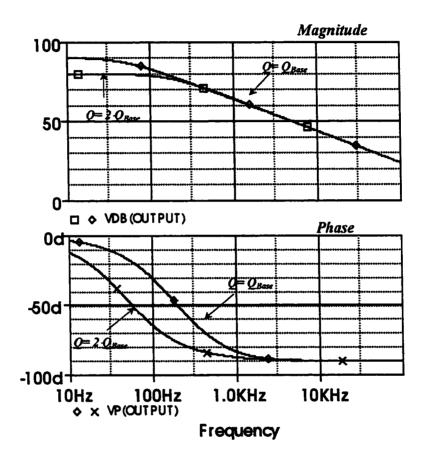

A plot of magnitude and phase of Equation (1.56) is shown in Figure 1.8 and Figure 1.9.

Figure 1.8: Magnitude for single stage PFC converter (control-output)

Figure 1.9: Phase for single stage PFC converter (control-output)

While tedious and strongly mathematical in nature, the method of state-space averaging introduced the notion of time-based averaging of circuit modes and the concept of system linearization to facilitate the use of classic design techniques. Its impact on the devlopment of power converter analyss and design are significant.

More recently, equivalent circuit models have been used in place of state-space averaging. One of the earliest and most prominent is the PWM Switch model [2]. The following section will provide an overview of this method.

#### 1.3 Vorperian's Method of PWM Switch Modeling

By the early 1990s, members of the technical community recognized the need for a more unified approach for modeling PWM converters. One of the most notable methods, called PWM Switch modeling by Vorperian, makes an analogy to BJT amplifier analysis and suggests that equivalent circuits be developed for the nonlinear elements in the circuit [2]. In this method, the nonlinear elements in the circuit are replaced by controlled sources representing the time averaged electrical quantities.

In many ways the method of PWM Switch modeling is similar to state-space averaging. Both methods use time averaging to develop a unified converter representation from its distinct and separate modes. However, unlike state-space averaging, a representation that is purely mathematical in nature (a set of state equations), PWM switch modeling produces an equivalent, averaged circuit model by a very methodical and standardized approach. This model is suitable for direct time domain simulation. Further, since this equivalent circuit is generated by time averaging the modes of the discontinuous, actual circuit, the abrupt jumps seen in the actual circuit are not present in the averaged model resulting in less convergence problems and faster simulation [2].

While PWM Switch modeling easily formulates the time domain circuit model, the linear or small-signal representation of the power stage is not. In general, the averaged equivalent circuit models are also nonlinear and must be linearized to do control loop design. Linearizing the converter's averaged equivalent circuit involves significant mathematical manipulation and might be more easily accomplished using state-space averaging. Fortunately, the advances in simulator software make this unnecessary. The averaged equivalent circuit model can be linearized directly in circuit simulators such as PSPICE. The linearization process traditionally carried by hand via equation manipulation is directly performed on circuit models in PSPICE via the AC Sweep analysis [3].

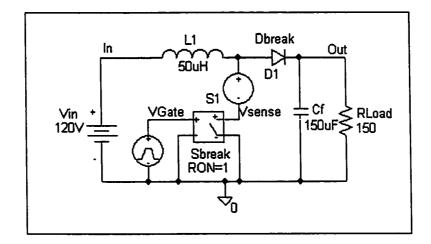

The preceding development gave a general overview of the modeling issue and described the method of PWM Switch Modeling. This modeling approach will be discussed in more detail and a DCM model for the circuit in Figure. 1.1 will be derived. It should be noted that although the boost converter will be used for the derivation, the model developed will be applicable to any converter in which the PWM Switch (3 terminal structure boxed in Figure 1.2 can be identified.

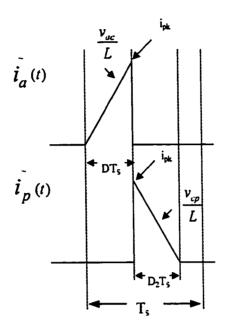

The first step is to draw the instantaneous waveforms of the actual circuit crossing the dashed boundary in Figure 1.1 for all modes of converter operation.

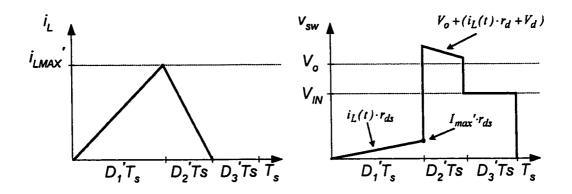

By inspection of Figures 1.2a-1.2c, we arrive at the instantaneous currents at nodes "a" and "p" as shown in Figure 1.10. We note the abrupt discontinuities as the circuit moves from one mode to another. The next step is to formulate modeling equations representing the average values of these current waveforms over the switching period,  $T_s$ .

Directly from the instantaneous terminal current waveforms of Figure 1.10, we can write the expressions for the average quantities as Equation (1.57)-(1.60).

Figure 1.10: Instantaneous waveforms for boost (DCM)

$$v_{cp} = L \cdot \frac{i_{pk}}{d_2 \cdot T_s} \tag{1.57}$$

$$v_{ac} = L \cdot \frac{i_{pk}}{d \cdot T_s}$$

(1.58)

$$i_p = \frac{i_{pk}}{2} \cdot d_2 \tag{1.59}$$

$$i_a = \frac{i_{pk}}{2} \cdot d \tag{1.60}$$

Where  $i_a$  and  $i_p$  are instantaneous values and  $i_a$  and  $i_p$  are the average values.

Rearranging the expressions, we relate these averaged quantities to one another to arrive at Equation (1.61)-(1.63).

$$v_{ac} = \frac{d_2}{d} \cdot v_{cp} \tag{1.61}$$

$$i_a = \frac{d}{d_2} \cdot i_p \tag{1.62}$$

$$d_2 = \frac{2 \cdot L \cdot F_s}{d} \cdot \frac{i_p}{v_{ac}}$$

(1.63)

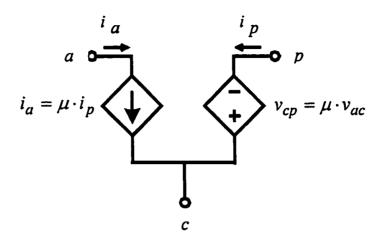

The averaged model follows directly as Equation (1.64)-(1.66).

$$i_a = \mu \cdot i_p \tag{1.64}$$

$$v_{cp} = \mu \cdot v_a \tag{1.65}$$

$$\mu = \frac{d^2}{2 \cdot L \cdot F_s} \frac{v_{ac}}{i_p}$$

(1.66)

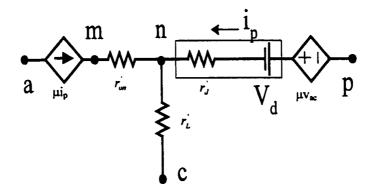

From the development above, we see that simple relationships exist between the input and output port of the PWM Switch. All that remains is to represent the modeling equations, Equation (1.64)-(1.66), in circuit form as shown in Figure 1.11. Figure 1.11 represents an averaged, equivalent circuit model for the dashed box in Figure 1.1.

Figure 1.11: PWM Switch Model (DCM)

By replacing the transistor and diode with this model we eliminate the abrupt discontinuities in the terminal characteristics and represent the instantaneous waveforms by their averaged values. In so doing, we will see that the time domain simulation run will be much faster at the expense of resolution.

Having addressed the time domain aspects of the model, we now ready move to the smallsignal or frequency domain characteristics. A close examination of the modeling equations reveals a nonlinear dependence on time varying circuit parameters, e.g. duty ratio. As a result of this nonlinearity, the averaged model must be linearized to produce the frequency response of the power stage. As pointed out in the previous section, armed with this information we will be able to design an effective controller tailored for this specific power stage. The linearization process is performed through the use of PSPICE's AC Sweep Analysis [3] to produce Bode plots of the converter's control to output transfer function  $(v_0(s)/d(s))$ . By classic control design theory, these plots provide all the information necessary to design an effective controller for a given power stage via classic techniques. For the sake of brevity the design process is not shown here.

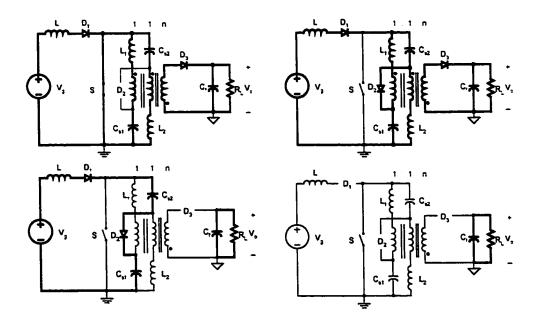

As mentioned above, the modeling technique presented by Vorperian [2] has several outstanding features including its simplicity and its direct application to the classic topologies. Unfortunately, his PWM Switch model is limited to applications involving converters that exhibit the PWM Switch cell. The reason for this can be understood by a more detailed evaluation of Vorperian's approach.

Figure 1.12: PWM Switching Cell in classic topologies

In the classic converter topologies (buck, boost, buck-boost, and Cuk) the PWM Switch Cell, as identified by Vorperian, consists of an active and passive switching device, which share a common node. Figure 1.12 boxes the PWM Switch Cell in each of the classic topologies.

Examining these diagrams reveals that the focus is on the portion of the circuit containing the switching elements while excluding the energy storage elements. By isolating this cell, it is possible to consider the entire nonlinear and discontinuous nature of the converter. After applying the averaging process to the current flowing into and out of the cell, Vorperian's model is able to replace the discontinuous switching elements with devices that represent the average electrical quantities at the ports of the cell. In so doing, the abrupt discontinuities of the actual circuit are substituted by smooth functions in the averaged equivalent model.

A second key issue is that the entire derivation of the Vorperian's model is based on the waveforms of the instantaneous currents through branches "a" and "p" as well as their dependence on cell port voltages  $v_{ap}$  and  $v_{ac}$ . Examining Figure 1.10, we see that the waveforms used in the derivation of Vorperian's model are not specific to any one of the classic converter topologies, but are in fact generic. Vorperian terms this "invariant" in that the terminal voltage and current characteristics of the PWM switch cell are the same regardless of the particular converter topology it is identified in. A comparison of Figures 1.10 and 1.12 reveals that Figure 1.10 could be the waveforms of any of the presented classic topologies when the generic labels  $i_a$ ,  $i_p$ ,  $i_o$ ,  $v_{ac}$ ,  $v_{cp}$  etc. are replaced by the topology 32

specific quantities seen in the actual circuit. For example, in the boost converter, the parameters  $v_{ap}$ ,  $i_c$ , and  $i_p$  are  $v_o$ ,  $i_L$ , and  $i_{out}$ , respectively It is for this reason that the Vorperian model can be directly applied to any of the classic topologies.

Clearly, Vorperian's choice of the PWM Switch Cell is deliberate. Choosing this cell establishes a common construct in the classic topologies that embodies the entire discontinuous nature of the circuit and presents a standard set of waveforms with regard to terminal currents and voltages in the derived model. However, when the switching elements cannot be localized to a particular region of the circuit, the waveforms at the nonlinear elements are not bound to behave as they do in Figure 1.10. The resulting conclusion is that Vorperian's model cannot be applied in converter topologies where the PWM Switch cell configuration and its associated terminal waveforms are not present.

Unfortunately, in many converter topologies, the inherent nonlinear and discontinuous nature is not localized to a particular area of the circuit as the switch-diode position in the conventional converters. In fact, many popular converters have switching elements spread throughout the topology with waveforms at these points not exactly matching those required by Vorperian's model. As a specific example, at UCF's Florida Power Electronics Research Center (FloridaPEC), work is being performed on a family of converter topologies that cannot be directly modeled by Vorperian's approach as they do not exhibit the PWM Switch Cell required. For topologies of this type, where switching elements are not localized to a particular region of the circuit, a new modeling approach is required.

Having reviewed the small-signal averaging and PWM switch modeling techniques, in the next section we will present a more unified modeling technique that uses concepts in the above methods.

## 1.4 Theory of Unified Approach

The method of PWM Switch modeling mentioned above provides a simple method for the formulation of averaged, equivalent circuit models. Clearly, the averaging of the instantaneous current waveforms and subsequent manipulations are the basis of this approach. Unfortunately, current waveform averaging is limited in its applications, particularly when energy storage elements are a part of the averaging cell. In that instance, inductor current is represented by a controlled current source whose magnitude is calculated by algebraic expression. By using an expression in place of the inductor, the natural time delays that would be created by the inductor are neglected in favor of a dependent current source which is effectively instantaneous. The net effect is a system order reduction which can lead to model inaccuracies at high frequency as shown later.

A more prudent approach is to maintain the integrity of the energy storage elements within the system by not averaging them out. This is a difficult task when a cellular modeling approach is used since the cell must necessarily contain all the nonlinear switching elements but should not contain energy storage components that effect the system's dynamic response. Many converter topologies exhibit a structure that cannot be adapted to this requirement easily. This results in a need for a more widely applicable methodology. The approach presented here discards the notion of inductor current waveform averaging exploiting the property that the average of a variable's derivative is equal to the derivative of the variable's average when the averaging process is defined as a time varying average over a sliding window. By using this property the method presented will ensure average differential voltage appears across each inductor and average current flows through each system capacitor making sure to keep all the energy storage elements which contribute to dynamic response.

As will be shown in subsequent chapters, this approach leads to a simple methodology which can be applied to virtually any converter topology. Application of the approach will be performed on several examples including: the conventional boost, a new PFC singleswitch converter, and a representative soft-switching. The models derived will then be compared with simulations of the actual circuit as well as other models.

### **1.5 Dissertation Outline**

This dissertation began in Chapter 1 with a review the method of state-space averaging, then discussed the creation of the averaged, equivalent circuit models for the nonlinear power switch/diode combination in modern power converters via the Vorperian method and via a more unified modeling approach. Detailed examples of these conventional

35

modeling techniques are presented and limitations to these approaches are discussed. An introduction to the unified theory of average modeling is also given in Chapter 1.

In Chapter 2, we will apply this unified approach to several examples and validate these models by simulation comparisons with the actual circuit and other models. Also we will show how the implementation of these modeling equations in PSPICE can be streamlined using its Analog Behavioral Modeling capability. The validation of the models produced will be presented in this chapter by making a comparison between simulation results obtained from the actual, switched circuit and those obtained from the averaged equivalent circuit models. Models will be further validated by comparison to experimental data.

Chapter 3 will investigate current techniques and concepts involved with loss modeling in modern power converters. It will then explore the validity of these concepts by performing a series of simulations to determine validity. Once the most appropriate modeling theory is determined, the work will strive to apply these theoretical concepts to the unified modeling approach presented in this dissertation. The intent is to produce loss models for conduction losses that can be easily implemented during the model design phase, account for both CCM and DCM operation, be as simple as possible, and yield relatively good predictions of component conduction loss.

In Chapters 4 and 5, the unified technique will be applied to a soft-switching topology. This will present new challenges as the instantaneous waveforms vary widely over the operating range. In addition, Chapter 5 will address a different type of control scheme, thus establishing that the unified approach here is applicable to non-duty ratio controlled converters.

The conclusion and future work will be presented in Chapter 6.

# CHAPTER 2: THEORY AND METHODOLOGY OF UNIFIED APPROACH

This chapter introduces the objectives of the unified modeling approach, investigates other techniques for average modeling, and presents the fundamental theory of the approach presented here. The basis for this approach is the mathematical property that the average of a variable's derivative is equal to the derivative of the variable's average when the averaging process is defined as a time varying average over a sliding window. Utilizing this equality, another approach at circuit averaging can be implemented which is more easily applied and more widely applicable.

## 2.1 Introduction and Objectives

Having established the need for a different modeling approach, it is appropriate to consider the desirable characteristics of the newly generated models. One may summarize the objective of the dissertation:

To produce a unified, methodical approach to modeling virtually any type of power converter circuits while achieving the following goals:

- 1. A high level of accuracy over a wide frequency range

- 2. Fast simulation time

38

3. Simple modeling methodology

4. Account for both CCM and DCM operation in a single model

5. Remain as close to the actual circuit as possible and total visibility of all circuit parameters  $(D_1, D_2, I_L, \text{ etc.})$

6. Allow for easy implementation in PSPICE

7. Serve as the precursor to conventional design techniques such as actual circuit simulation and experimental prototyping.

Certainly, objectives (1) and (2) are self-evident and require no further explanation. However, the remaining items will be discussed briefly.

Regarding item (3), there is a wide variety of modeling approaches published in the technical journals, [1], [2], [6], [7], [8]. Most of these modeling approaches trade the simplicity of Vorperian's approach for added functionality. In particular, the requirement of a more widely applicable modeling approach often results in significantly more complex modeling schemes. Further, the added complexity of these schemes often results in models that are more like mathematical abstractions than the circuit being modeled (item (5)). The modeling approach presented here will, whenever possible, avoid strict mathematical representations and attempt to capture the essence of the circuit's natural operation.

On item (4), the derivation of Vorperian's model is predicated on a particular set of waveforms. The waveforms shown in Figure 1.10 are drawn for the DCM case and result

in a model that is valid only for converter's operating in this mode. The result is that for any given Vorperian model, simulations are constrained to either DCM or CCM operation. This presents a problem during converter time domain startup modeling or transient modeling when the converter's operating point would transition from CCM to DCM operation or vice versa. When using a model that is CCM or DCM specific, the transition to the other operating mode cannot be simulated seamlessly. The designer is left with the task of piecing together results from two different simulation runs, one using the CCM model and the other using the DCM version. Certainly if the model can make this transition seamlessly while producing accurate results it would provide a significant functional improvement. Several of the recent modeling schemes in the published technical literature account for this need and present single models that accurately represent both CCM and DCM operation. The modeling approach presented here will also include this functionality.

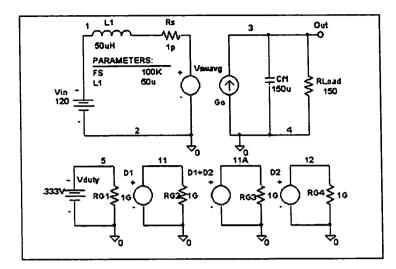

Regarding item (6), another consideration is the method by which the derived models are input into the software packages for simulation. Since it is a common trait of these models to involve lengthy algebraic expressions, it is often easier for developers to "code" their models using the script format supported by their simulator packages. In the case of PSPICE, the graphical interface does not come with device blocks that will support the necessary controlled sources. However, the scripting language used by PSPICE does support the required functionality. As a part of the unified approach generated here, custom devices will be created within the PSPICE package to facilitate direct input of model in schematic form rather than in script code.

On objective (5), when models are implemented using the scripting mechanism, the code or sub-circuit definition representing the model is usually represented as a rectangular block in the simulator schematic package. Various quantities, which are contained within the model's script, are inaccessible when running simulations. Clearly, there is often some interest in the activity or movement of these quantities as the simulation progresses, particularly during model debug. By employing, the graphical approach mentioned in the previous section, all the quantities of interest are visible to the modeler during simulation. As an example, during model debug, if the model has a problem the user might wish to ensure all the circuit parameters are converging to the proper values. In most cases the design engineer will have solved for the nominal operating point of the converter and need only place trace markers at the nodes of interest. The modeler can then compare the parameter's activity with its expected value. This is a significant improvement as the complex nature of the algebraic expressions employed often breeds model bugs. To correct these issues, good visibility into the activity of all model parameters is a must. If the user were working with the scripted form of the model, debug would be, at the very least, tedious if not impossible.

And finally, objective (7) establishes the notion of design order. While classic design techniques such as actual circuit simulation and experimental prototyping are effective and necessary, they are often not the logical first step in the design process. Initial efforts in

most designs include macroscopic evaluations of converter performance, component and operating point selection, and control loop design. Complications involving the simulation and construction of the actual topology often make this high-level evaluation difficult. The beauty of the unified model presented is that it allows the designer to gain significant insight into the design process providing an overview of every aspect of performance. Once these top-level issues are tackled, the detailed design process becomes fine tuning an already functional design.

L

### 2.2 Variant Technique Evaluation

Having covered the objectives of the new modeling approach, we are now prepared to discuss potential techniques. As the first candidate, the possibility of modifying Vorperian's approach will be discussed. The idea would be to expand Vorperian's approach to cases not exhibiting the PWM Switch cell and to incorporate the added functionality listed in the above objectives. Several papers were reviewed that make variations on Vorperian's approach and attempt to apply their new modeling schemes to converters where the PWM Switch cell is not present.

Certainly, this is an attractive methodology owing to the powerful and simplistic nature of the Vorperian scheme. Further, intuitively, we might expect that this approach could be extend to the more general circuit topologies with little effort while maintaining an accurate equivalent circuit model. In fact, a large portion of the research done for this dissertation was dedicated to doing just that. Unfortunately, as will be seen in the next section, the extension of Vorperian's approach is not so easily done. The intuitive way to apply Vorperian's modeling theory to the more general class of converters often yields inaccurate results. It was shown that at the core of Vorperian's methodology is the requirement that all the switching elements are contained within the block to be modeled and that this block does not contain any of the energy storage elements within the system.

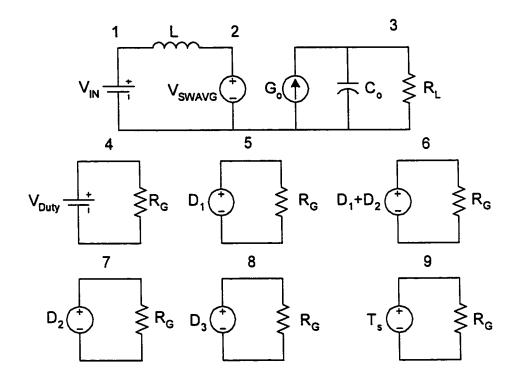

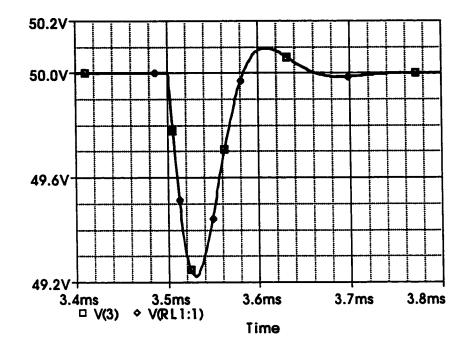

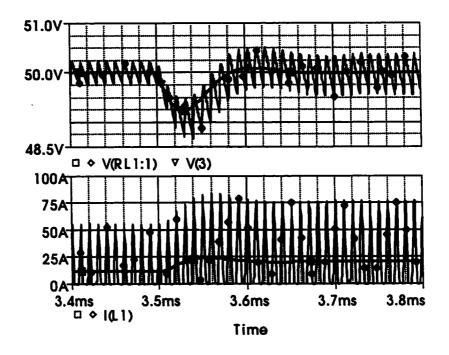

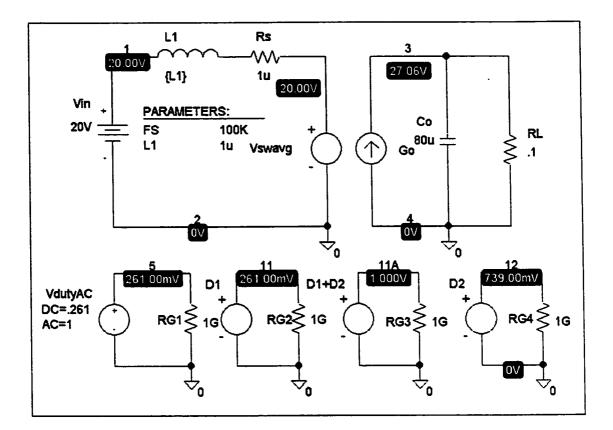

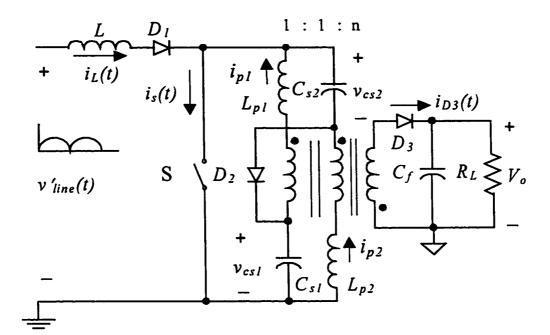

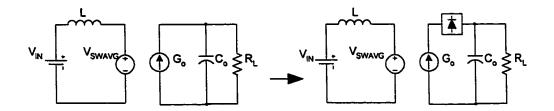

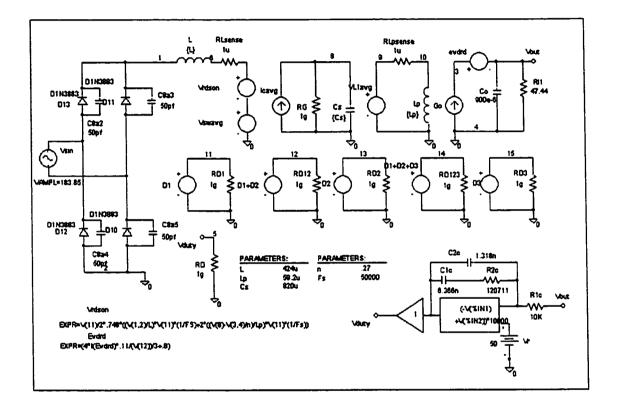

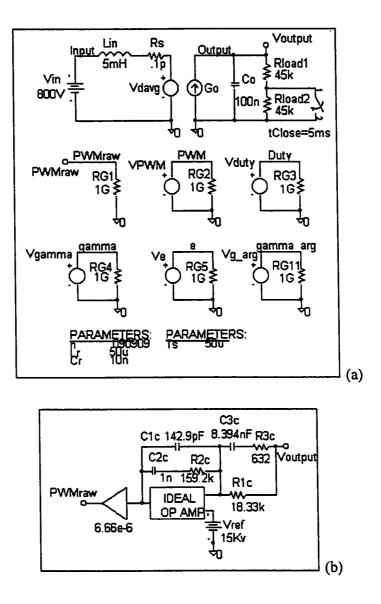

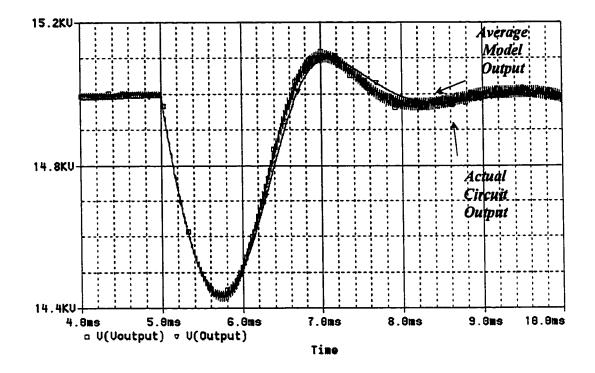

Figure 2.1: Separated PWM switch topology in [6]