# CONTROL AND TOPOLOGY IMPROVEMENTS IN HALF-BRIDGE DC-DC CONVERTERS

By

SONGQUAN DENG B.S. Xihua University, 1998 M.S. Chongqing University, 2001

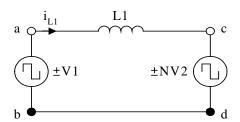

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term 2005

Major Professor: Issa Batarseh

#### **ABSTRACT**

Efficiency and transient response are two key requirements for DC-DC converters.

Topology and control are two key topics in this dissertation. A variety of techniques for DC-DC converter performance improvement are presented in this work.

Focusing on the efficiency issue, a variety of clamping techniques including both active and passive methods are presented after the ringing issues in DC-DC converters are investigated. By presenting the clamping techniques, a big variety of energy management concepts are introduced. The active bridge-capacitor tank clamping and FET-diode-capacitor tank clamping are close ideas, which transfer the leakage inductor energy to clamping capacitor to prevent oscillation between leakage inductor and junction capacitor of MOSFETs. The two-FET-clamping tank employs two MOSFETs to freewheeling the leakage current when the main MOSFETs of the half-bridge are both off. Driving voltage variation on the secondary side Synchronous Rectifier (SR) MOSFETs in self-driven circuit due to input voltage variation in bus converter applications is also investigated. One solution with a variety of derivations is proposed using zerner-capacitor combination to clamping the voltage while maintaining reasonable power losses.

Another efficiency improvement idea comes from phase-shift concept in DC-DC converters. By employing phase-shift scheme, the primary side and the secondary side two MOSFETs have complementary driving signals respectively, which allow the MOSFET to be turned on with Zero Voltage Switching (ZVS). Simulation verified the feasibility of the proposed phase-shifted DC-DC converter.

From the control scheme point of view, a novel peak current mode control concept for half-bridge topologies is presented. Aiming at compensating the imbalanced voltage due to peak current mode control in symmetric half-bridge topologies, an additional voltage compensation loop is used to bring the half-bridge capacitor voltage back to balance. In the proposed solutions, one scheme is applied on symmetric half-bridge topology and the other one is applied on Duty-cycle-shifted (DCS) half-bridge topology. Both schemes employ simple circuitry and are suitable for integration. Loop stability issues are also investigated in this work. Modeling work shows the uncompensated half-bridge topology cannot be stabilized under all conditions and the additional compensation loop helps to prevent the voltage imbalance effectively.

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to my advisor, Dr. Issa Batarseh, for his guidance, encouragement and support. Dr. Batarseh's extensive vision and creative thinking have been the source of inspiration for me throughout this work. His personality and management experience are examples for me.

This work is supported and funded by ASTEC Power. I would like to thank Mr. Geof Potter, Vice President of ASTEC Power, for his valuable insight, technical guidance and encouragement. I would like to thank Mr. Brad Huggins for his valuable suggestions and technical support.

I am grateful to my committee members, Dr. Louis Chow, Dr. Wasfy Mihkael, Dr. Christopher Iannello, Dr. Z. John Shen and Dr. Hong Mao for their valuable suggestions and abundant help.

It has been a great pleasure to work in the Florida Power Electronics Center at the University of Central Florida. I would like to thank our alumni members, Dr. Shiguo Luo, Dr. Weihong Qiu, Dr. Weikai Wu and Dr. Christopher Iannello, for the valuable discussions and suggestions. I would like to acknowledge my coworkers Dr. Hong Mao, Dr. Jaber A. Abu Qahouq, Ms. Yangyang Wen and Mr. Liangbin Yao for their useful discussion and support. I would like to thank all other Emerson team members, Dr. Louis Chow, Thomas Wu, Mr. Xiangcheng Wang, Dr. K. Ngo, Mr. Shangyang Xiao, Ms. Hua Zhou, Dr. Lei Zhou and Mr. Yeong Ren Lin. I would like to thank other members in the Power Electronics Laboratory, including Mr. Nattorn Pongratananukul, Ms. Yufang Jin and Mr. Khalid Rustom.

I would like to express my special appreciation to my former advisors Prof.

Zhengcheng Hou. Prof. Hou guided me to the field of Power Electronics. From him, I

learned not only extensive knowledge, but also from their excellent research attitudes and

personalities.

I would like to express my appreciation to Ms. Michelle Jordan for her invaluable

editing work on my dissertation.

Finally, I feel much indebted to my parents — they are always there to encourage

and pray for me. With much love, I would like to thank my wife, Yujing Yang, for her

encouragement and self-giving support.

Songquan Deng

October 2005

$\mathbf{v}$

To my wife - YujingYang

To my parents – Qijing Deng Zhenrong Lee

# TABLE OF CONTENTS

| LIST OF FIGURES                                                  | XII       |

|------------------------------------------------------------------|-----------|

| LIST OF TABLES                                                   | XVIII     |

| 1. INTRODUCTION                                                  | 1         |

| 1.1 Research background and motivation                           | 1         |

| 1.1.1 Centralized Power System (CPS)                             | 3         |

| 1.1.2 Distributed Power System (DPS)                             | 3         |

| 1.1.3. DPS architectures                                         | 7         |

| 1.2 Dissertation outline                                         | 11        |

| 2. KEY APPROACHES TO BUILD ON-BOARD DC-DC CONVE                  | RTER WITH |

| HIGH EFFICIENCY AND FAST TRANSIENT RESPONSE                      | 16        |

| 2.1 Topology and control scheme overview                         | 16        |

| 2.1.1 Full-Bridge topology                                       | 17        |

| 2.1.2 Half-Bridge topology                                       | 19        |

| 2.1.3 Symmetric Half-Bridge topology                             | 20        |

| 2.1.4 Asymmetric Half-Bridge topology                            | 21        |

| 2.1.5 Push-Pull topology                                         | 23        |

| 2.1.6 Forward topology                                           | 24        |

| 2.2 The relationship between efficiency and transient response   | 28        |

| 2.2.1 Efficiency concern                                         | 28        |

| 2.2.2 Transient response concern.                                | 30        |

| 2.2.3 The relationship between transient response and efficiency | 33        |

| 3. NEW PEAK CURRENT MODE CONTROL CONCEPT AND DERIVED                                |      |

|-------------------------------------------------------------------------------------|------|

| SCHEMES FOR HALF-BRIDGE TOPOLOGY                                                    | 34   |

| 3.1 Introduction                                                                    | . 34 |

| 3.2 Proposed voltage imbalance compensation concept                                 | . 35 |

| 3.2.1 The capacitor voltage imbalance problem in half-bridge topology               | 35   |

| 3.2.2 The proposed capacitor voltage compensation concept                           | . 38 |

| 3.3 Derived control scheme for symmetric half-bridge topology                       | 40   |

| 3.4 Derived control scheme for DCS half-bridge topology                             | 43   |

| 3.4.1 Introduction to DCS half-bridge topology                                      | 43   |

| 3.4.2 Derived control scheme for DCS half-bridge topology                           | 45   |

| 3.5 Experimental verification                                                       | 49   |

| 3.5.1 Experimental results for proposed peak current mode control scheme for        |      |

| symmetric half-bridge topology                                                      | 51   |

| 3.5.2 Experimental results for proposed peak current mode control scheme for DC     | CS   |

| half-bridge topology                                                                | 53   |

| 4. MODELING THE PEAK CURRENT MODE CONTROLLED HALF-BRIDG                             | E    |

| DC-DC CONVERTER                                                                     | 56   |

| 4.1 Motivation for the peak current mode controlled half-bridge modeling            | . 56 |

| 4.2 The small signal model for the peak current mode controlled half-bridge topolog | у    |

|                                                                                     | . 57 |

| 4.3 The small signal model for the voltage imbalance correction loop                | 64   |

| 4.4 Simulation verifications                                                        | . 68 |

| 4.5 Summary                                                                         | 71   |

| 5. CLAMPING TECHNIQUES IN DC-DC CONVERTERS                                   | 72      |

|------------------------------------------------------------------------------|---------|

| 5.1 Introduction                                                             | 72      |

| 5.2 Proposed energy management concepts                                      | 73      |

| 5.2.1 Energy freewheeling concept                                            | 74      |

| 5.2.2 Energy storage concept                                                 | 75      |

| 5.2.3 Energy storage and release concept                                     | 77      |

| 5.2.4 Lossless zener diode clamping concept                                  | 78      |

| 5.3 The energy freewheeling concept applied on half-bridge topology          | 80      |

| 5.3.1 Introduction                                                           | 80      |

| 5.3.2 The proposed energy freewheeling clamping on half-bridge topology      | 83      |

| 5.3.3 Simulation verifications                                               | 91      |

| 5.3.4 Summary                                                                | 94      |

| 5.4 The energy storage concept applied on half-bridge topology               | 95      |

| 5.4.1 Proposed active-clamping circuit                                       | 95      |

| 5.4.2 Main features and design considerations                                | 106     |

| 5.4.2.1 Main features                                                        | 106     |

| 5.4.2.2 Converter DC voltage gain                                            | 110     |

| 5.4.2.3 Design example                                                       | 111     |

| 5.4.3 Simulation and experimental verifications                              | 112     |

| 5.4.4 Summary                                                                | 121     |

| 5.5 The energy storage and release concept applied on active-clamp forward t | opology |

|                                                                              | 122     |

| 5.5.1 Introduction                                                           | 122     |

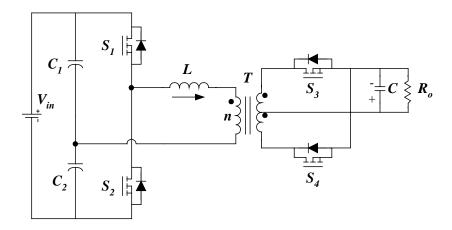

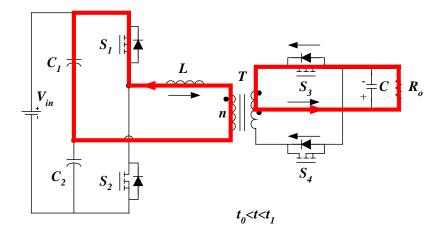

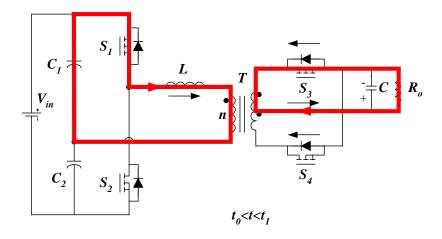

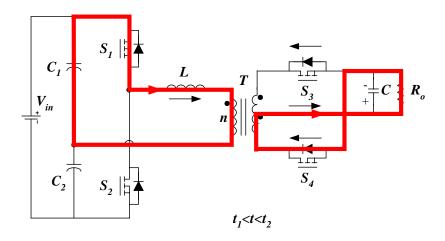

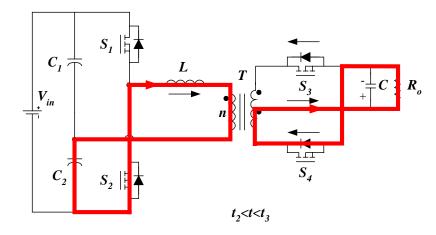

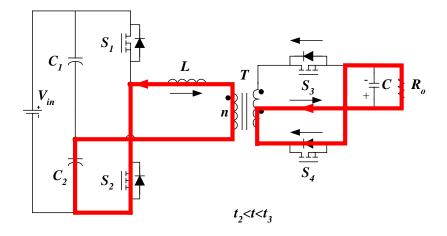

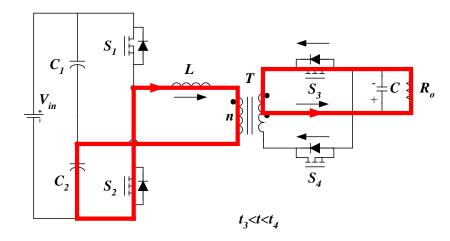

|    | 5.5.2 Operation modes analysis for the proposed active-clamp forward converter | 124 |

|----|--------------------------------------------------------------------------------|-----|

|    | 5.5.3 Simulation verifications                                                 | 132 |

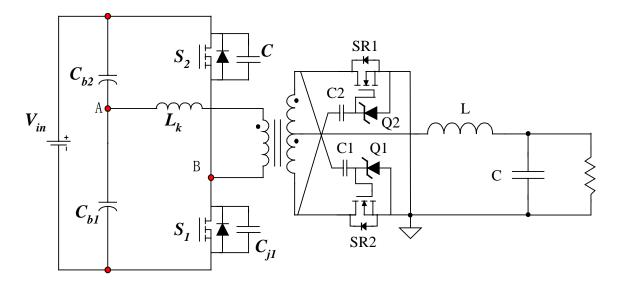

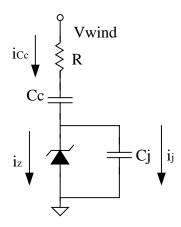

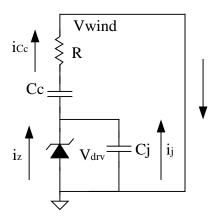

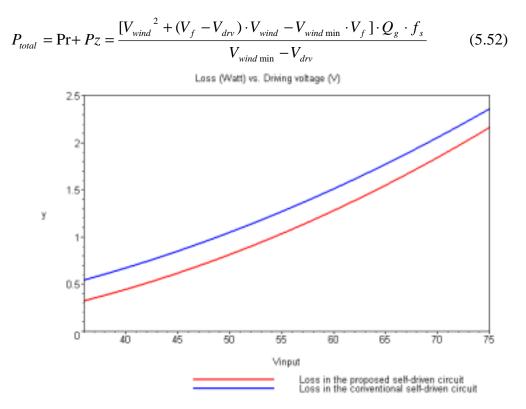

|    | 5.6 The lossless zener diode concept applied on self-driven circuit            | 134 |

|    | 5.6.1. Background introduction                                                 | 134 |

|    | 5.6.2 The proposed lossless zener diode clamping circuit                       | 138 |

| 6. | PHASE-SHIFT CONCEPT APPLIED ON HALF-BRIDGE DC-DC                               |     |

| C  | ONVERTERS                                                                      | 148 |

|    | 6.1 Introduction                                                               | 148 |

|    | 6.2 Proposed phase-shift half-bridge DC-DC topology                            |     |

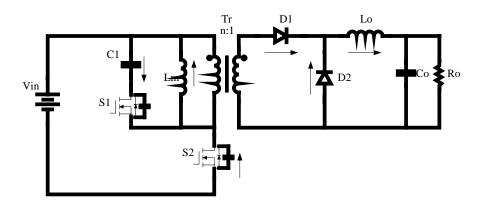

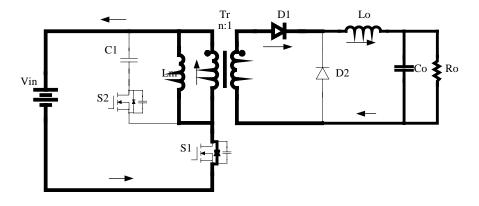

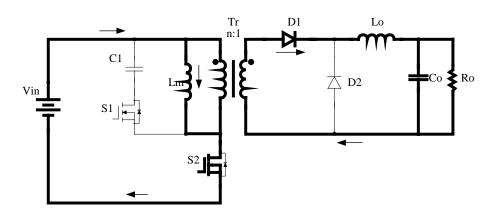

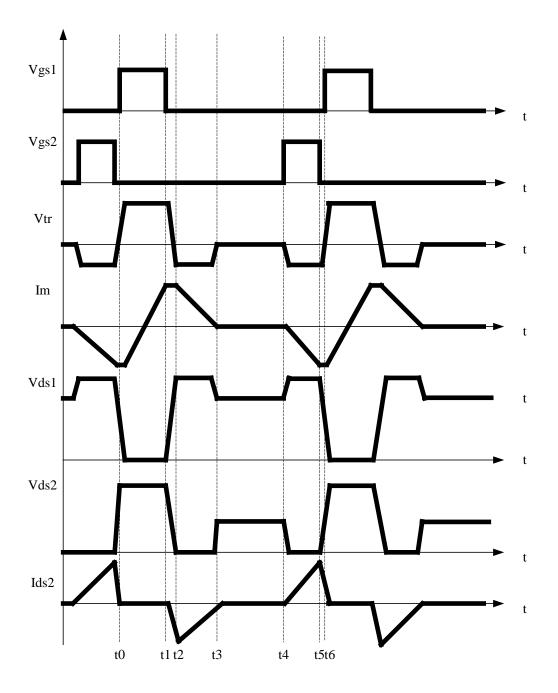

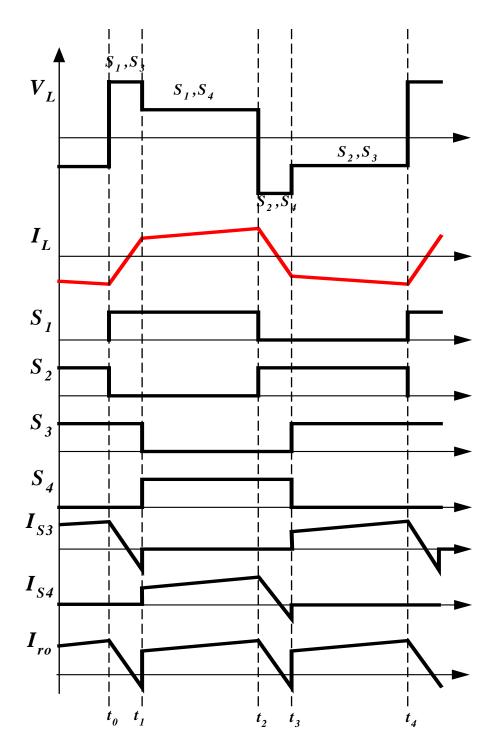

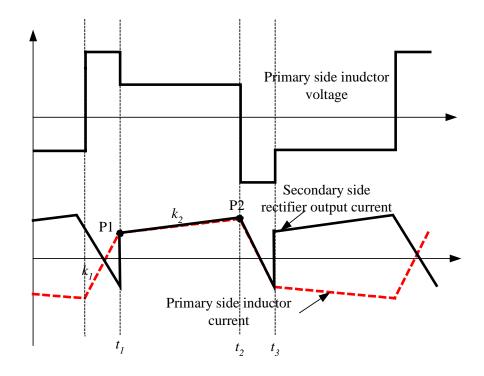

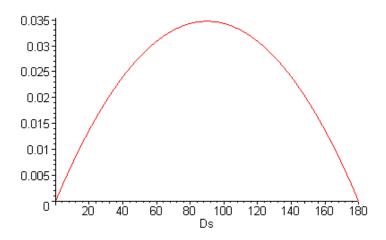

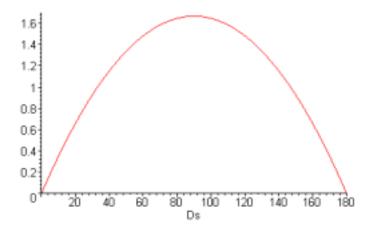

|    | 6.3 Operation modes analysis                                                   |     |

|    | 6.4 Simulation verifications                                                   |     |

|    | 6.5 Summary                                                                    |     |

| _  |                                                                                |     |

|    | THE POWER LOSSES ESTIMATION PLATFORM FOR POWER                                 |     |

| E] | LECTRONICS CIRCUIT                                                             | 172 |

|    | 7.1 Introduction                                                               | 172 |

|    | 7.2 Proposed analysis platform                                                 | 173 |

|    | 7.3 Features of the proposed platform                                          | 175 |

|    | 7.4 Platform operational principles                                            | 176 |

|    | 7.4.1 Losses on MOSFETs                                                        | 177 |

|    | 7.4.2 Losses on magnetic components                                            | 179 |

|    | 7.5 Simulation and experiment results                                          | 181 |

|    | 7.6 Conclusion                                                                 | 185 |

| 8. CONCLUSIONS AND FUTURE WORK                                                 | 186       |

|--------------------------------------------------------------------------------|-----------|

| 8.1 Conclusions                                                                | 186       |

| 8.2 Summary of the improvements                                                | 189       |

| 8.3 Suggestions for future work                                                | 191       |

| 8.3.1 Implementation study for the integration of the peak current mode cor    | ıtroller  |

|                                                                                | 191       |

| 8.3.2 Studies on the clamping techniques                                       | 191       |

| 8.3.3 Further investigation on the possible applications of the phase-shift co | oncept on |

| other topologies                                                               | 192       |

| REFERENCES                                                                     | 193       |

# LIST OF FIGURES

| Fig. 1.1 Parallel modules                                                          | 5  |

|------------------------------------------------------------------------------------|----|

| Fig. 1.2 Cascading structure                                                       | 5  |

| Fig. 1.3 Source splitting                                                          | 6  |

| Fig. 1.4 Load splitting                                                            | 7  |

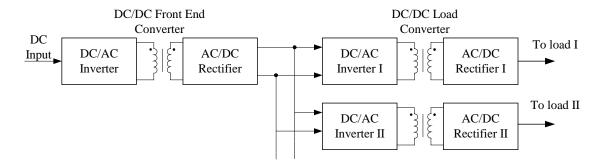

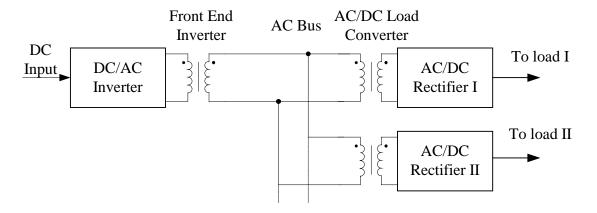

| Fig. 1.5 The DC-architecture block diagram                                         | 7  |

| Fig. 1.6 The AC-bus architecture block diagram                                     | 8  |

| Fig. 2.1. Full-Bridge topology                                                     | 17 |

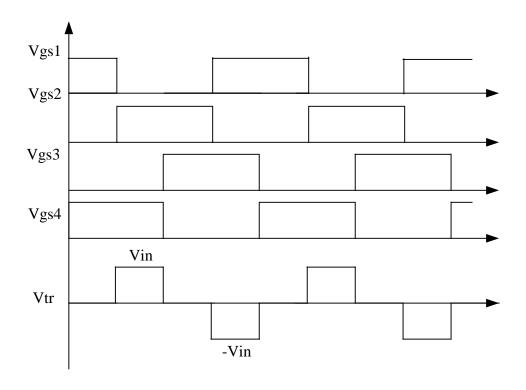

| Fig. 2.2. Driving signal                                                           | 17 |

| Fig. 2.3 Phase-Shift Full-Bridge driving signal and transformer winding voltage    | 19 |

| Fig. 2.4. Half-Bridge topology                                                     | 19 |

| Fig. 2.5. Symmetric Half-Bridge driving waveform                                   | 20 |

| Fig. 2.6 Asymmetric Half-Bridge driving waveform                                   | 22 |

| Fig. 2.7. Push-Pull topology                                                       | 23 |

| Fig. 2.8. The classical forward topology                                           | 24 |

| Fig. 2.9. The forward converter with RCD snubber                                   | 24 |

| Fig. 2.10. The forward converter with a LCDD snubber                               | 25 |

| Fig. 2.11. The forward converter with two switches                                 | 25 |

| Fig. 2.9. Active-clamp Forward topology                                            | 25 |

| Fig. 2.10 The power losses distribution of one DC-DC converter in one typical low- |    |

| voltage high-current application                                                   | 28 |

| Fig.2.11. DC-DC converter with load transient.                                     | 30 |

| Fig. 2.12. The Fourier component of the transient step current                     | 30 |

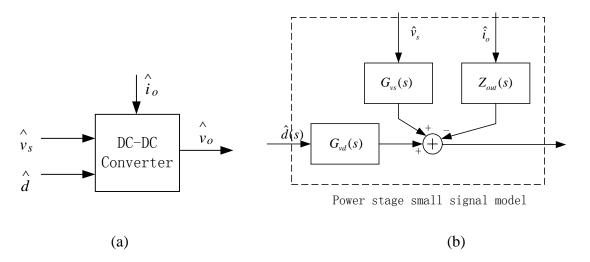

| Fig.2.13. Small-signal Model of the on-board DC-DC                                  | . 31 |

|-------------------------------------------------------------------------------------|------|

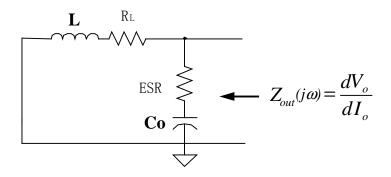

| Fig. 2.14. The output impedance model                                               | . 32 |

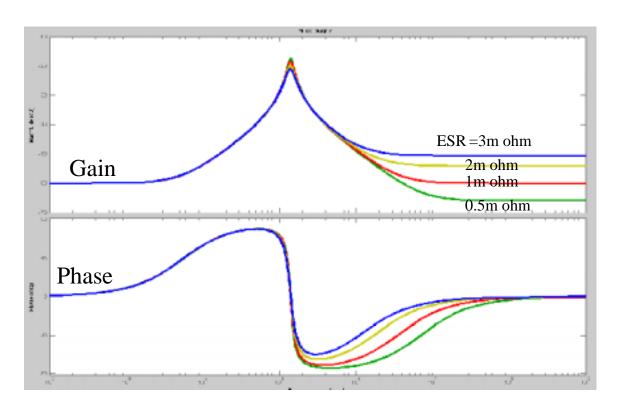

| Fig. 2.15. The output impedance vs. different capacitor ESR                         | . 32 |

| Fig. 3.1 Half-Bridge topology                                                       | . 36 |

| Fig. 3.2 One solution to balance capacitor voltages in half-bridge topology         | . 37 |

| Fig. 3.3 Half-Bridge topology                                                       | . 38 |

| Fig. 3.4 Key waveforms for the proposed compensation concept on symmetric half-     |      |

| bridge topology                                                                     | . 39 |

| Fig. 3.6 Capacitor voltage compensation loop implementation                         | . 41 |

| Fig. 3.7 Peak current mode control logic block                                      | . 43 |

| Fig. 3.8 Half-bridge topology                                                       | . 44 |

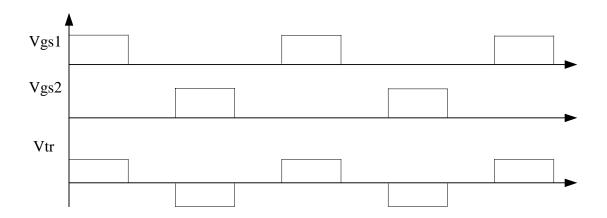

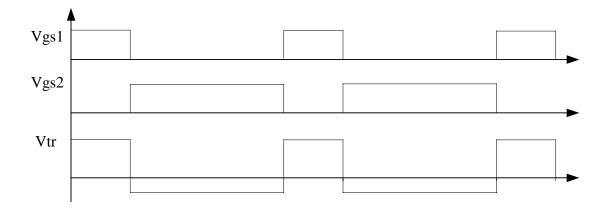

| Fig. 3.9 Symmetric PWM control.                                                     | . 44 |

| Fig. 3.10 DCS PWM control                                                           | . 45 |

| Fig. 3.12 Key waveforms for proposed compensation scheme                            | . 46 |

| Fig. 3.13 Voltage imbalance detection and compensation circuit                      | . 47 |

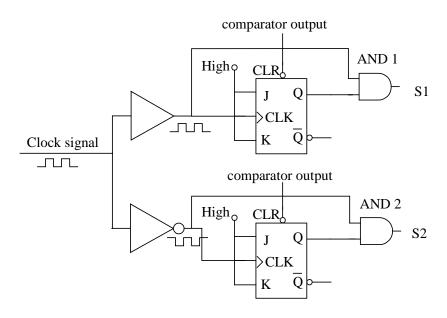

| Fig. 3.14 DCS scheme implementation logic circuitry                                 | . 48 |

| Fig. 3.15 Key waveforms for Fig. 3.14                                               | . 48 |

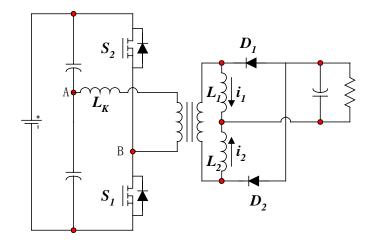

| Fig. 3.16 The power stage of the proposed peak current mode controlled DC-DC        |      |

| converter                                                                           | . 50 |

| Fig. 3.17 The control board employing proposed peak current mode control scheme for | r    |

| DCS half-bridge topology                                                            | . 50 |

| Fig. 3.18 The control board employing proposed peak current mode control scheme for | r    |

| symmetric half-bridge                                                               | . 51 |

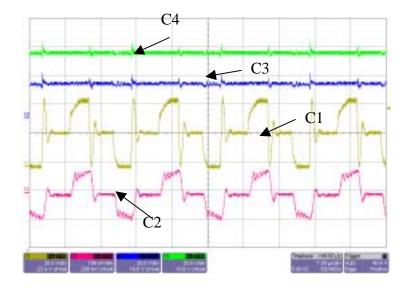

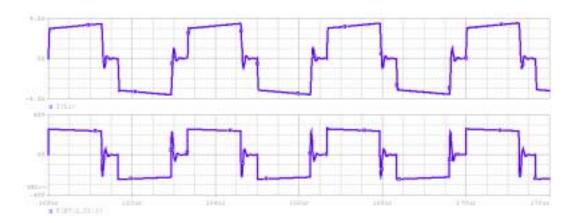

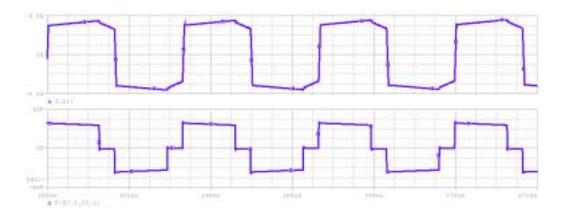

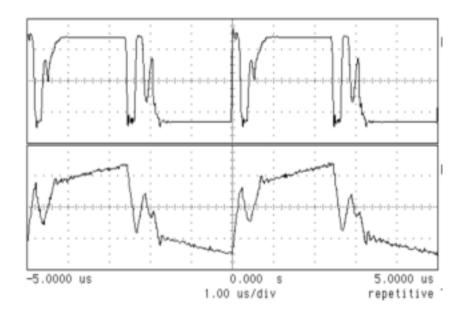

| Fig. 3.19 The key waveform from the power stage                                          | 52 |

|------------------------------------------------------------------------------------------|----|

| Fig. 3.20 The key waveform from the control board                                        | 52 |

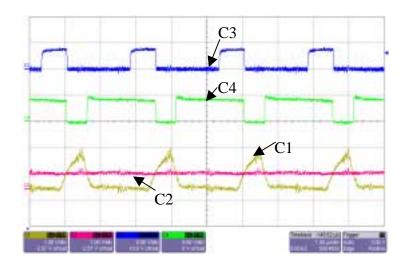

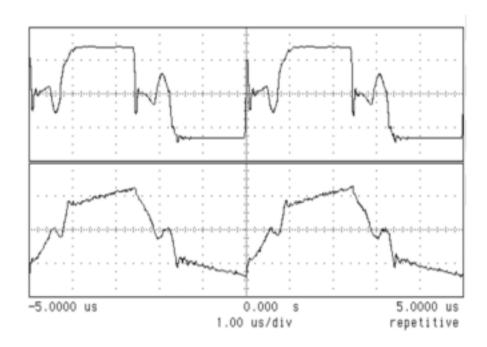

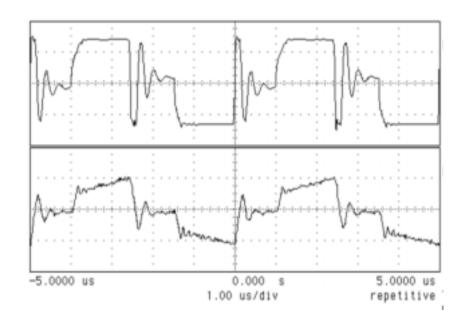

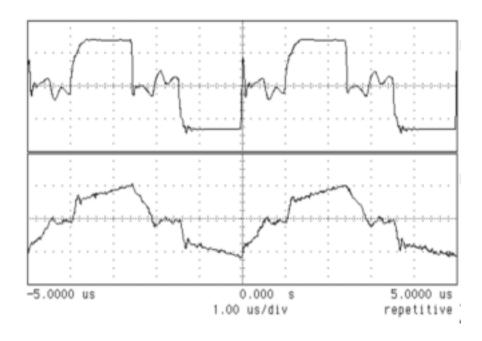

| Fig. 3.21 Key waveform from the power stage                                              | 53 |

| Fig. 3.22 Key waveform from the control board                                            | 54 |

| Fig. 4.1 Half-bridge topology                                                            | 57 |

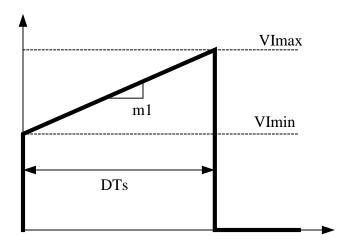

| Fig. 4.2 Duty ratio definition                                                           | 58 |

| Fig. 4.3 Peak current mode modulator                                                     | 59 |

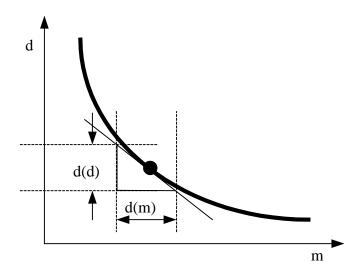

| Fig. 4.4 Duty ratio vs. output inductor current slope rate                               | 60 |

| Fig. 4.5 The block diagram for the voltage imbalance correction loop                     | 64 |

| Fig. 4.6 The PI controller used for the voltage imbalance correction loop                | 66 |

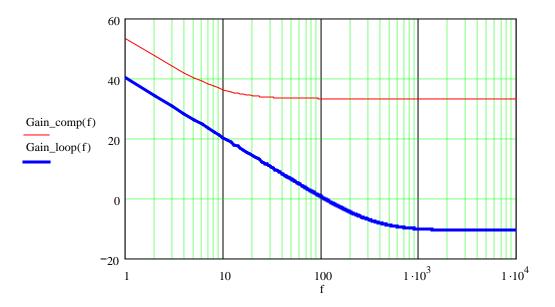

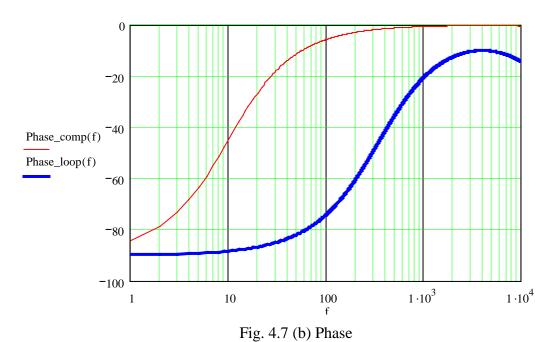

| Fig. 4.7 The bode plot of the compensation loop                                          | 67 |

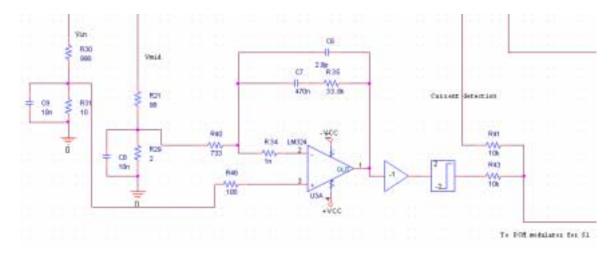

| Fig. 4.8 The controller for the voltage imbalance correction loop in the simulation mode | el |

|                                                                                          | 68 |

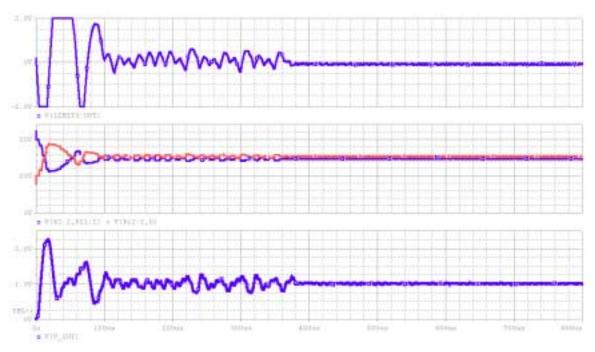

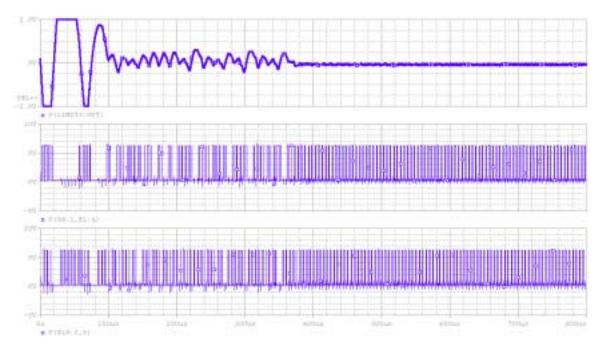

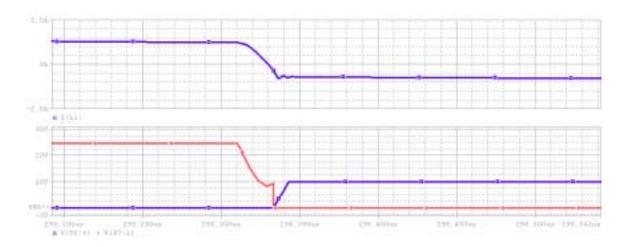

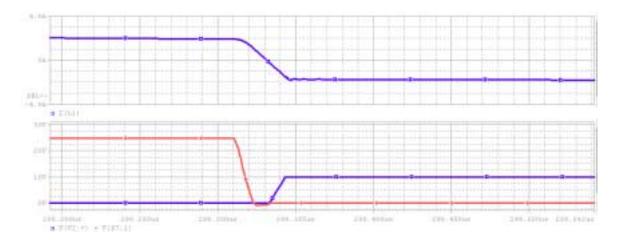

| Fig. 4.9 Simulation results for the peak current mode controlled half-bridge DC-DC       |    |

| converter                                                                                | 69 |

| Fig. 4.10 Simulation results for the peak current mode controlled half-bridge DC-DC      |    |

| converter                                                                                | 70 |

| Fig. 4.11 The key waveforms for the peak current mode modulator                          | 70 |

| Fig. 4.12 The capacitor voltage runs into imbalance when correction loop is disabled     | 71 |

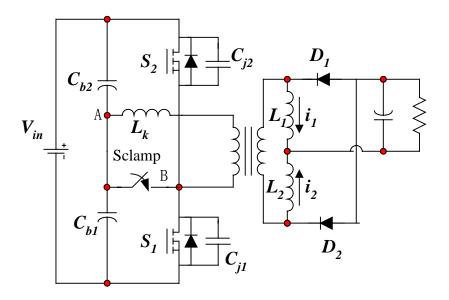

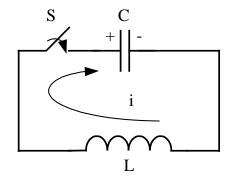

| Fig. 5.1 Energy freewheeling concept illustration                                        | 75 |

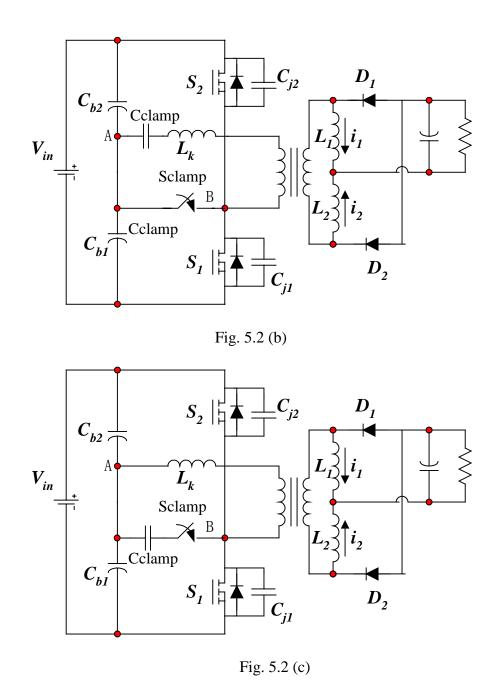

| Fig. 5.2 The illustration of energy storage concept with different clamping capacitor    |    |

| locations                                                                                | 76 |

| Fig. 5.3 The energy storage and release concept illustration                             | 77 |

| Fig. 5.4 The lossless zener diode concept illustration                            | 78 |

|-----------------------------------------------------------------------------------|----|

| Fig. 5.5 The lossless zener diode concept applied on self-driven circuit          | 79 |

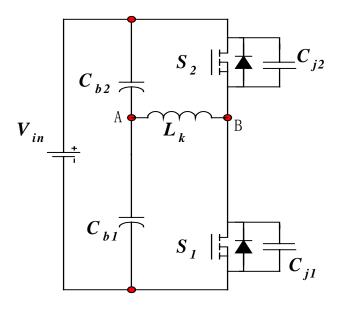

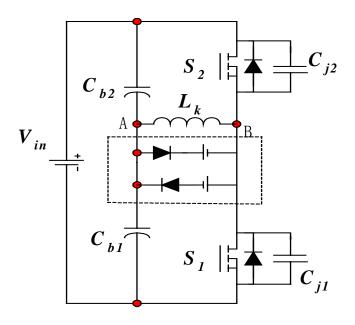

| Fig. 5.6 Half-bridge isolated DC-DC converter                                     | 82 |

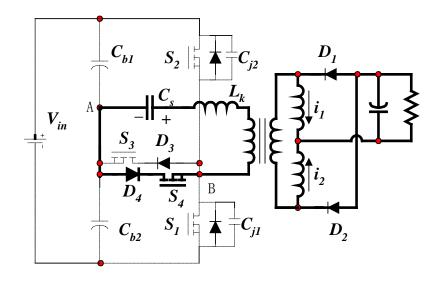

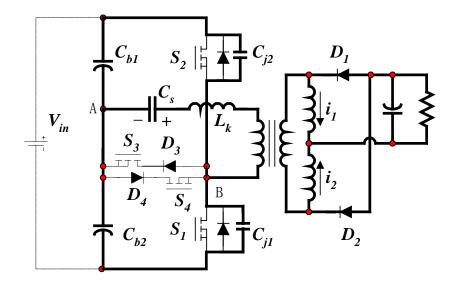

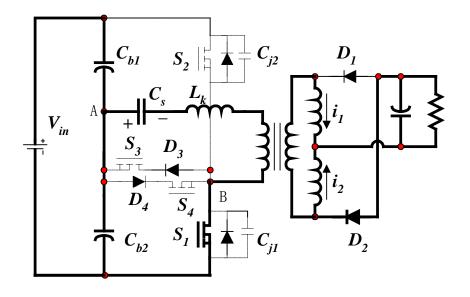

| Fig. 5.7 The proposed energy freewheeling concept applied on half-bridge topology | 84 |

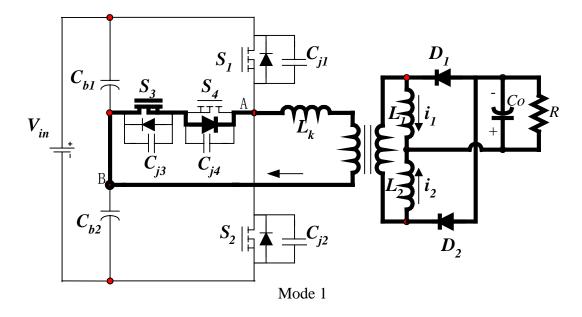

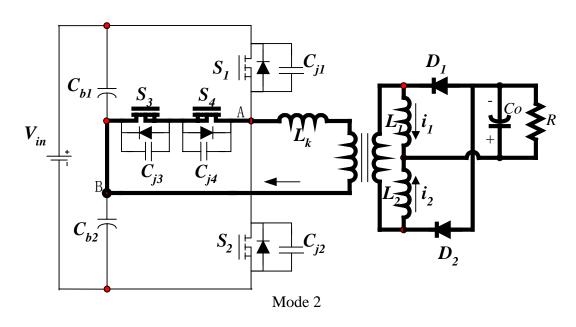

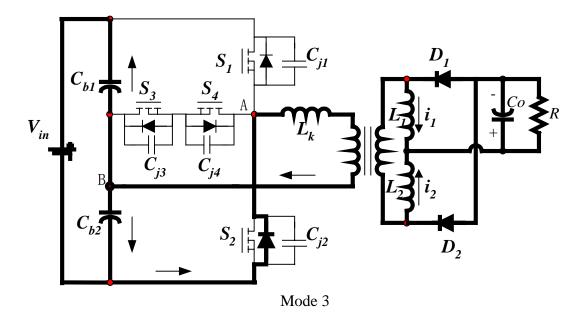

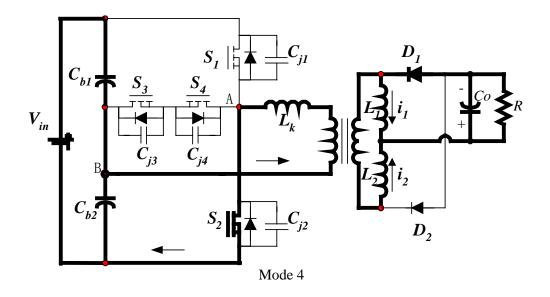

| Fig. 5.8 Operation modes description for the proposed half-bridge with the energy |    |

| freewheeling concept                                                              | 84 |

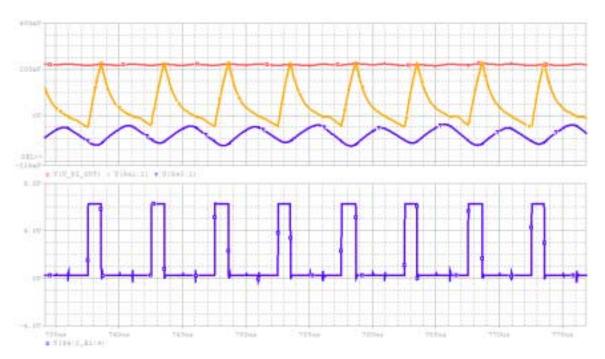

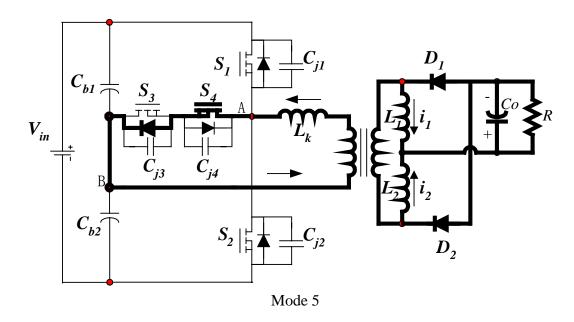

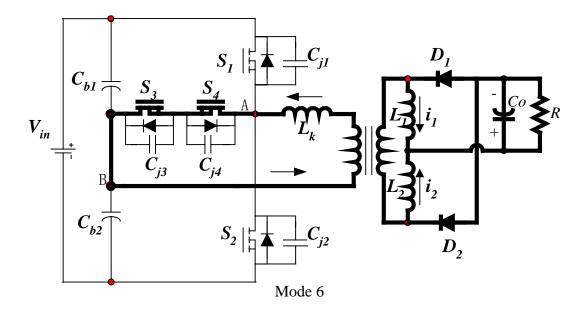

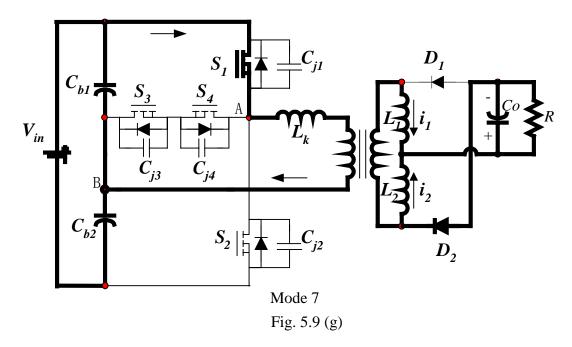

| Fig. 5.9 Operation mode analysis for the proposed clamped half-bridge topology    | 91 |

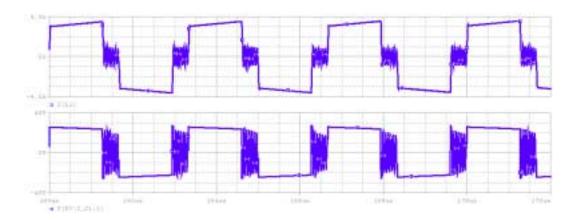

| Fig. 5.10 Transformer primary side winding current vs. voltage                    | 92 |

| Fig. 5.11 ZVS condition vs. load current                                          | 94 |

| Fig. 5.12 Equivalent circuits during the freewheeling period                      | 96 |

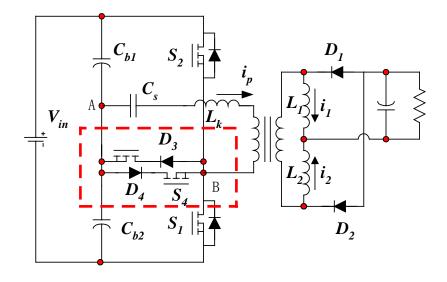

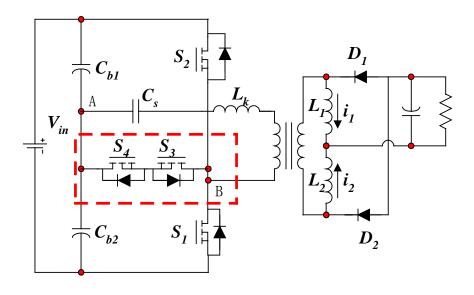

| Fig. 5.13 Proposed active-clamp snubber circuits in half-bridge DC-DC converter   | 97 |

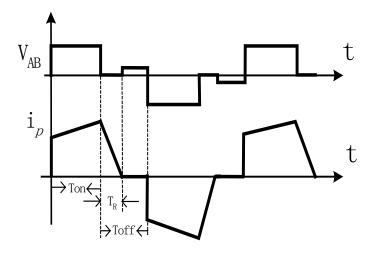

| Fig. 5.14 Key theoretical waveforms of the proposed topology 1                    | 02 |

| Fig. 5.15 Modes of operation equivalent circuits                                  | 05 |

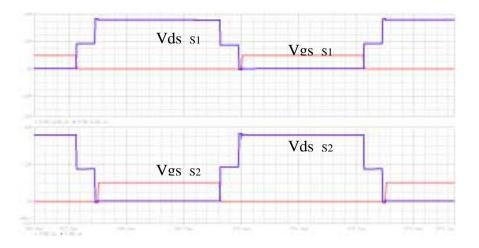

| Fig. 5.16 Two possible operation schemes for the proposed converter               | 08 |

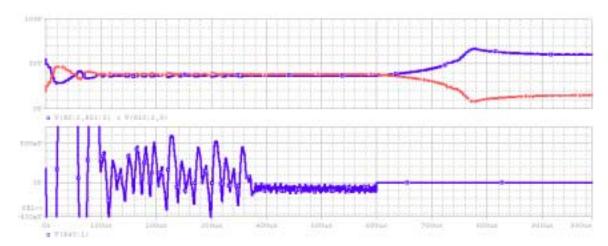

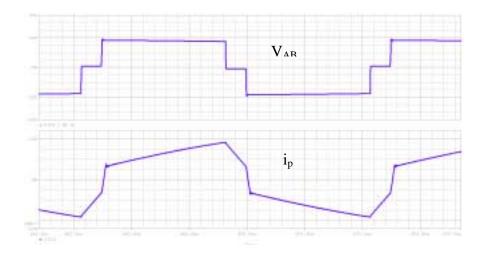

| Fig. 5.17 Simulation waveforms comparison                                         | 14 |

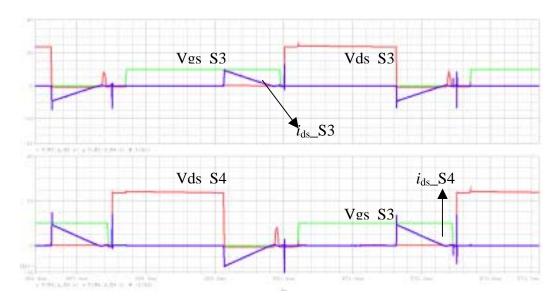

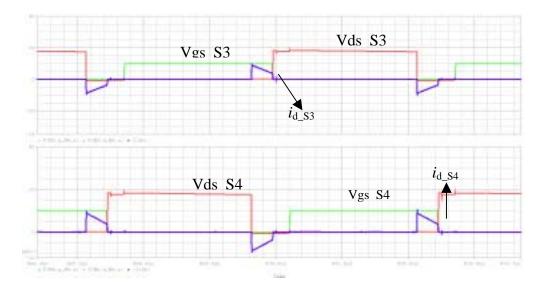

| Fig. 5.18 ZVZCS waveforms of auxiliary switches                                   | 15 |

| Fig. 5.19 Waveforms under the condition of $T_{\text{off}} < T_{R}$               | 17 |

| Fig. 5.22 Experimental waveforms of Vds across low-side switch and transformer    |    |

| primary current (Cs=6.6uF)                                                        | 20 |

| Fig. 5.23 Efficiency comparison between the proposed active-clamp snubber and the |    |

| conventional RC snubber                                                           | 21 |

| Fig. 5.24 The active-clamp forward topology                                       | 24 |

| Fig. 5.25 Operation modes of the proposed active-clamp DC-DC converter            | 27 |

| Fig. 5.26 Key waveforms                                                                | . 128 |

|----------------------------------------------------------------------------------------|-------|

| Fig. 5.27 The simulation waveform                                                      | . 132 |

| Fig. 5.28 Simulation waveforms                                                         | . 133 |

| Fig. 5.30 The on-resistance vs. driving voltage for MOSFET Si7868                      | . 137 |

| Fig. 5.31 The proposed clamping lossless zener clamping circuit for self-driven scher  | ne    |

|                                                                                        | . 138 |

| Fig. 5.32 The proposed clamping circuit                                                | . 139 |

| Fig. 5.33 The MOSFET turn-off transition analysis                                      | . 142 |

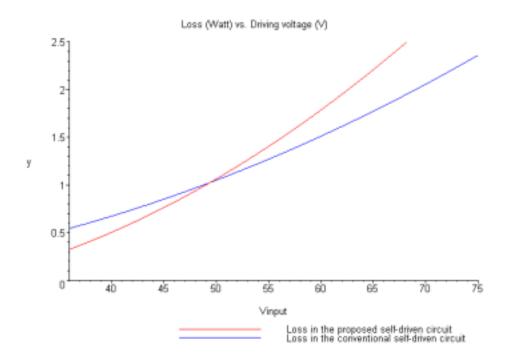

| Fig. 5.34 The loss comparison between two self-driven circuits vs. the converter input | lt    |

| voltage                                                                                | . 143 |

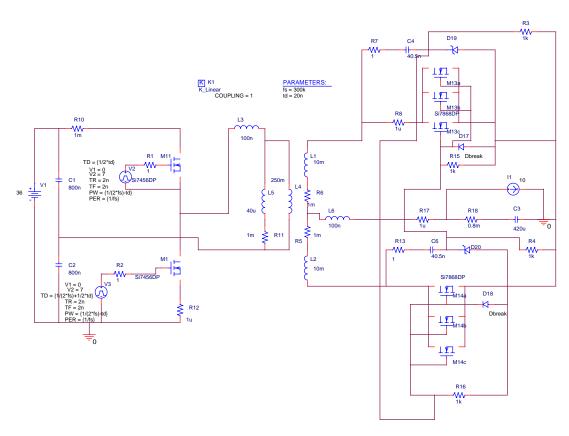

| Fig. 5.36 The simulation schematics                                                    | . 145 |

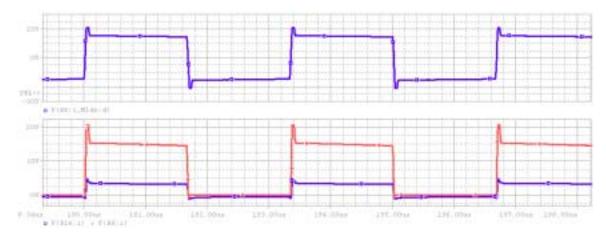

| Fig. 5.37 Simulation result for the proposed self-driven circuit with clamping         | . 146 |

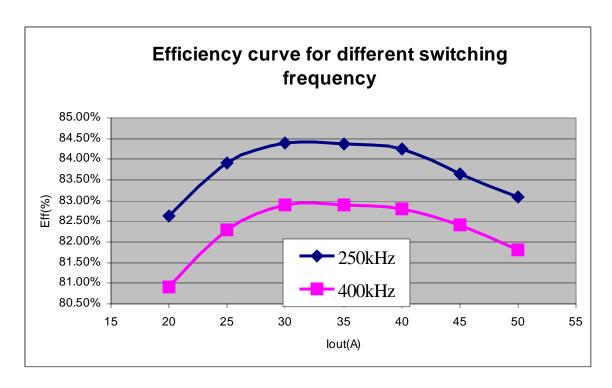

| Fig. 6.1 The experimental efficiency curve for one DC-DC converter with different      |       |

| switching frequency                                                                    | . 149 |

| Fig. 6.2 Losses distribution in one DC-DC converter                                    | . 150 |

| Fig. 6.3 The ZVS illustration                                                          | . 151 |

| Fig. 6.4 the phase-shift control block diagram                                         | . 153 |

| Fig. 6.5 the simplified model for phase-shift control                                  | . 153 |

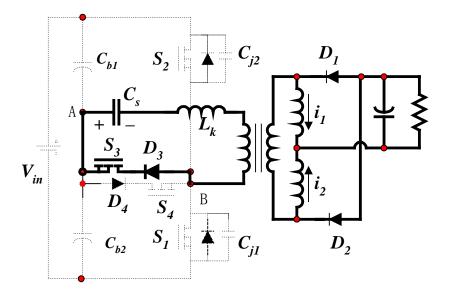

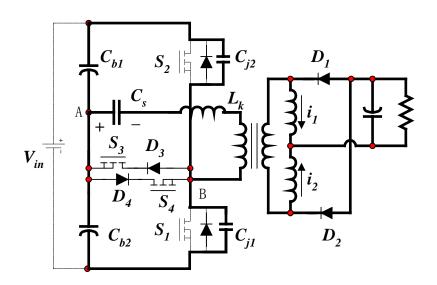

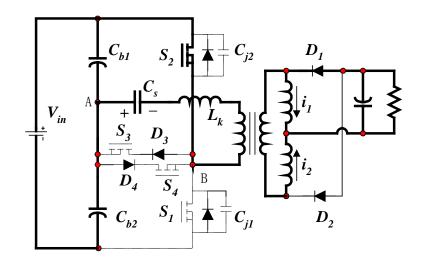

| Fig. 6.6 the proposed phase-shift bi-directional DC-DC converter                       | . 154 |

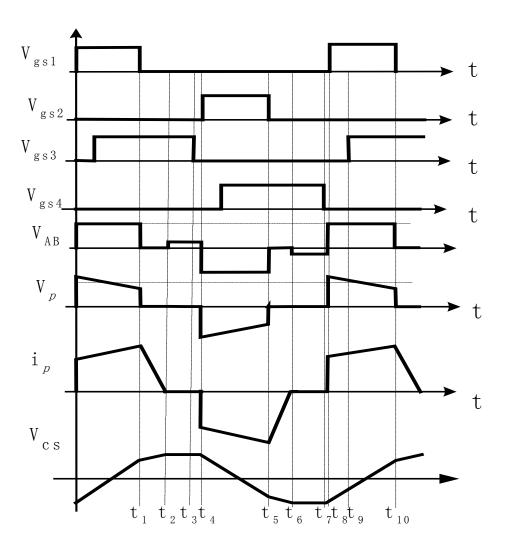

| Fig. 6.7 the key waveforms for the phase-shift bi-directional DC-DC converter          | . 156 |

| Fig. 6.8 The operation modes analysis                                                  | . 160 |

| Fig. 6.8 the key waveforms for the phase-shift bi-directional DC-DC converter          | . 161 |

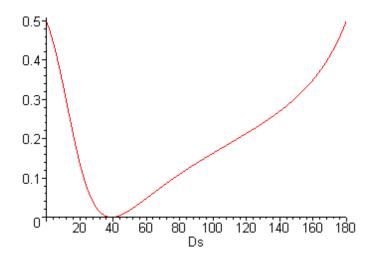

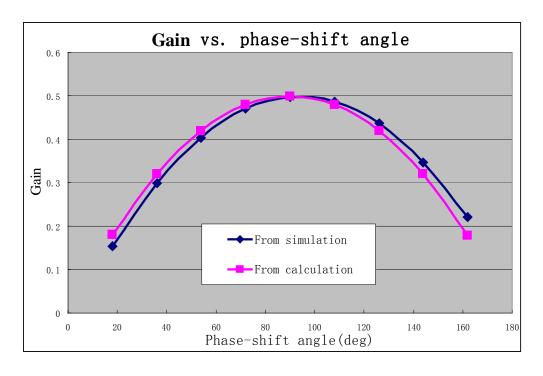

| Fig. 6.9 voltage gain vs. phase-shift angle                                            | . 162 |

| Fig. 6.10 output voltage vs. phase-shift angle                                         | 163 |

|----------------------------------------------------------------------------------------|-----|

| Fig. 6.11 Q/(Q+P) vs. phase-shift angle                                                | 164 |

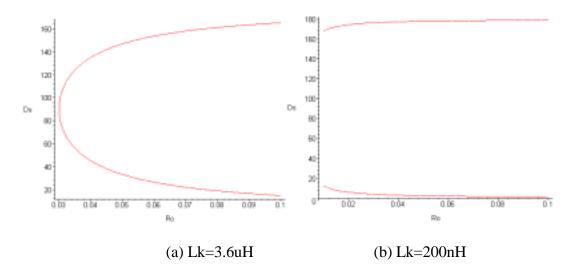

| Fig. 6.12 the phase-shift angle vs. different load                                     | 165 |

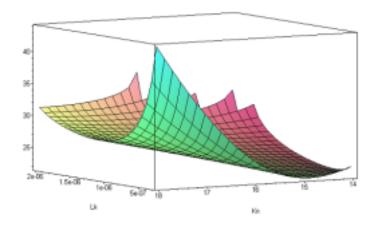

| Fig. 6.13 The optimum inductance and turns ratio for minimum rms current in switch     | 166 |

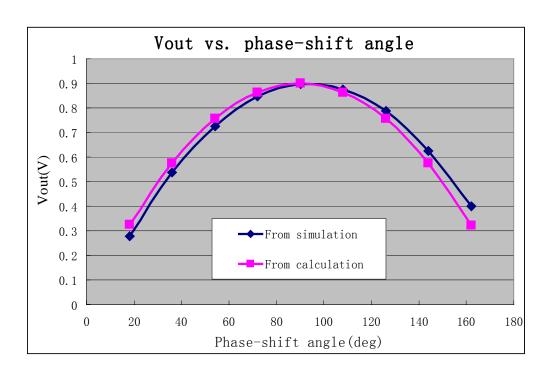

| Fig. 6.14 The comparison between calculation results and simulation results            | 167 |

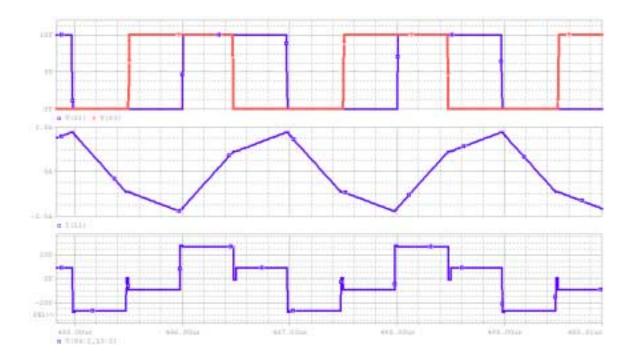

| Fig. 6.15 Key simulation waveform                                                      | 168 |

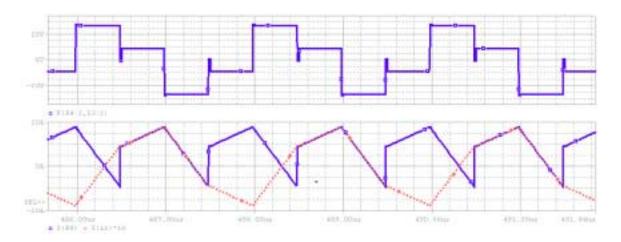

| Fig. 6.16 Key simulation waveforms                                                     | 169 |

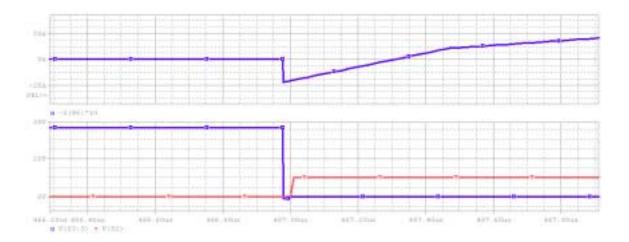

| Fig. 6.17 ZVS of the primary power MOSFET                                              | 170 |

| Fig. 7.1 Block diagram for the analysis platform                                       | 174 |

| Fig. 7.2 The trapezoid rule for power losses calculation                               | 177 |

| Fig. 7.3 The current distribution comparison for transformer structures with different |     |

| layers                                                                                 | 180 |

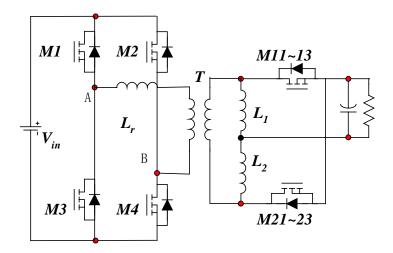

| Fig. 7.4 The topology of the DC-DC converter for simulation                            | 181 |

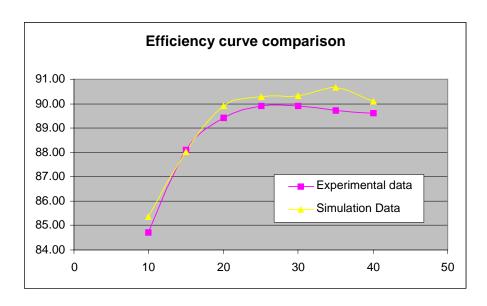

| Fig. 7.5 The efficiency curves comparison for DC-DC converter                          | 183 |

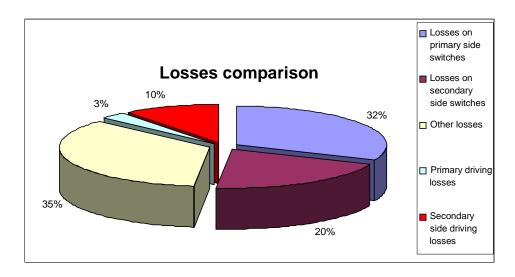

| Fig. 7.6 The distribution of the power losses                                          | 183 |

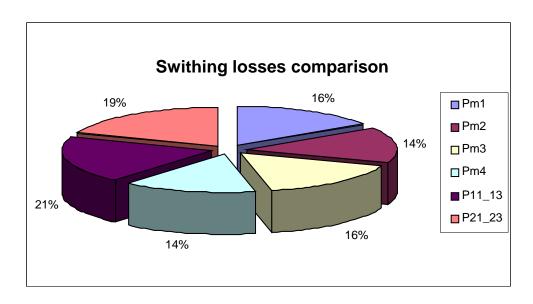

| Fig. 7.7 The switching losses comparison for the MOSFETs                               | 184 |

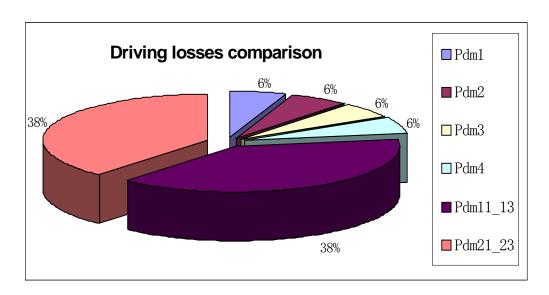

| Fig. 7.8 The driving losses comparison for the key MOSFETs                             | 184 |

# LIST OF TABLES

| Table 5.1 Power loss comparison between calculation and simulation                   | 147 |

|--------------------------------------------------------------------------------------|-----|

| Table 7.1 The AC resistance vs. the DC resistance of the copper layer with different |     |

| transformer winding structure                                                        | 180 |

| Table 7.2 The simulation parameters for key component                                | 182 |

| Table 7.3 Losses on the key components                                               | 182 |

| Table 7.4 Driving losses on the MOSFETs                                              | 182 |

#### 1. INTRODUCTION

#### 1.1 Research background and motivation

One of today's power supply design challenges is creating multiple-output Direct Current to Direct Current (DC-DC) converters with tight regulation on multiple low-voltage outputs connected to high slew rate dynamic loads. New generations of power supply architectures and specialized Pulse-Width-Modulation (PWM) controllers are emerging to meet these demands [A1]. Two application areas having very separate challenges in the past are beginning to converge: the 12V desktop power supply and the 48V telecom power supply. Both of these applications present unique challenges that are shaping the future of the power topologies and the power control technology used in modern DC-DC converters.

At the heart of communication systems and Desktop PCs are advanced microprocessors and a high-speed communication Application-Specific Integrated Circuit (ASIC) designed in deep sub-micron, low-voltage Metal Oxide Semiconductor (CMOS) logic technologies. Operating at GHz clock frequencies and supplying large currents (over 60A) on multiple tightly regulated, low-voltage supply rails (sub-2Vdc), presents major challenges to the DC-DC power conversion system [A2][A3]. In order to protect the expensive system chips from potentially destructive power conditions, multiple supply rails must be sequenced on-and-off in a prescribed order and ramped up and down within a finite amount of time and minimal overshoot beyond the desired output level.

New power supply topologies are emerging to meet the power conversion challenges of modern computing and communication systems. In communication systems, traditional 48V isolated power supply topologies (single-ended forward and flyback regulators) are yielding the way to higher power topologies (push-pull, half-bridge and full-bridge) [A4]. Also, new hybrid topologies, such as cascaded regulators, are emerging [A5][A6]. In computer systems, traditional non-isolated PC power supply topologies (multiphase buck regulators) are yielding the way to isolated power conversion topologies that take advantage of the transformer turns-ratio to create multiple low-voltage outputs in one conversion step to provide the many low-voltage rails required by advanced microprocessors [A7]. These ever changing power supply considerations create fresh opportunities for PWM control Integrated Circuit (IC) designers to match new process technologies with unique power integrated circuit design techniques to develop the next generation power system requirements.

A reversal in the roles of the traditional distributed power conversion architectures is emerging between computer and communication systems. Desktop PC power architectures are being proposed with developing multiple low-voltage supply rails from a 48V bus rather than a 12V distributed bus [A8]. This allows reducing the distribution losses expected with the ever-increasing power appetite of next generation processors. Conversely, telecom power architects are just now launching a new DC-DC modules to convert the 48V bus to a 12V distributed bus [A9] so they can take advantage of the vast array of point-of-load power controllers available on the market today. Some high-end workstation and server systems already use a 48V distributed power conversion system that maintains proper regulation while supplying very high load currents. Due to

the difficulty in achieving tight regulation on supplies with ever decreasing load voltages and geometrically increasing load currents, a 48V distributed power system is now being considered to replace the traditional 12V bus in desktop PC power supplies.

#### 1.1.1 Centralized Power System (CPS)

The term "centralized power" originated in early 1980's when a typical Alternating Current to Direct Current (AC-DC) power supply came packed in a silver-box chassis with an AC line cord on one side and a DC cable harness extending out the other side of the chassis for mating with a system power connector [A10]. Multiple DC voltages (typically +12V, +/-5V, +3.3V) were provided through the connector to the Printed Circuit Board (PCB) power planes [A11]. Advanced sub-micron CMOS technology emerged in the early 1990's changing the power supply requirements from traditional +5Vdc and +3.3V supplies to multiple non-standard low-voltage supplies (2.5V, 1.8V, 1.2V, etc.) with high load currents being demanded by advanced microprocessors and ASICs.

#### 1.1.2 Distributed Power System (DPS)

A combination of high slew-rate load currents and tight regulation specifications for very low-voltage outputs gave rise to usage of "distributed power" with point of load converters [A12-A16]. In a distributed power system, a single intermediate voltage (typically 12V or 48V) is generated by an offline AC-DC supply and converted to lower

voltages with a DC-DC regulator located on the motherboard closer to the point of the loading. The close proximity of the DC-DC regulator to the high slew-rate load reduces distribution impedances permitting more precise and easier to control regulation. Reduced parasitic elements in the control loop, lower voltage drop across the PCB power planes and a cost savings for distribution cables and connectors are obtained.

Several basic DPS structures can be identified according to the way the power processing functions are distributed among several different Power Processing Units (PPUs).

#### 1. Paralleling structure:

Paralleling [A18-A19] has been widely used in many power supply systems and is often referred to as a modular power supply system. The characteristics of paralleling include:

Good thermal management: Since each module handles only one part of the total power, the more modules in paralleling, the less power dissipated in each module.

High reliability: Since the power processed by each module decreased, and even though the system has more components, the overall reliability is improved. The n+1 redundancy helps to build highly reliable DPS systems.

Modularity and maintainability: The paralleling structure simplifies the power system design. For higher power requirement, simply put more modules in parallel. The design for each module can be standardized. On-line replacement makes maintenances even easier.

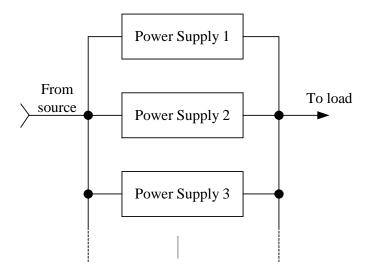

Fig. 1.1 Parallel modules

#### 2. Cascading structure:

Cascading structure [A17] [A21] is generally applied in DPS. It has the following characteristics:

Point-Of-Load (POL) regulation: Since the power supply is placed as close as possible to the load, the parasitic is significantly reduced and fast transient response is obtained as a result.

*High efficiency*: Higher mid-bus voltage reduces the losses on the traces, which greatly improves the system efficiency.

Wide line variation: Cascading connection has good response to wide line variation due to the cascading structure.

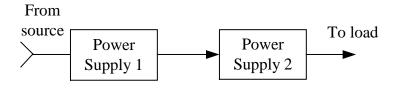

Fig. 1.2 Cascading structure

#### 3. Source splitting structure:

Source splitting [A17] is used when different available sources such as battery backup, which is most commonly used to provide temporary power when primary power fails. It is also used to achieve redundancy for highly reliable power systems.

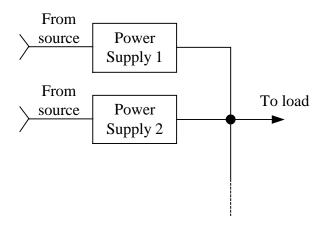

Fig. 1.3 Source splitting

#### 4. Load splitting structure:

Load splitting [A17] is employed due to the following considerations:

Distributed load: For physical reasons, the loads are distributed in significant distance. A DPS with an intermediate bus is a natural solution. Each load has its own power supply module placed as close as possible to reduce the power loss on the traces. The regulation is solved as well since the converter is in close proximity to each load.

Noise considerations: For a DPS with common bus, the noise coupling occurs between loads. The load-splitting technique introduces two load converters between any two loads with their associate filter to attenuate the noise.

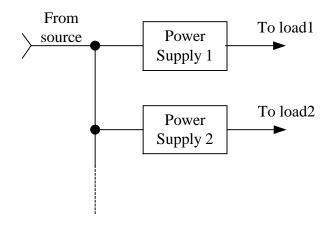

Fig. 1.4 Load splitting

#### 1.1.3. DPS architectures

There exist two fundamental DPS architectures with the difference of the bus voltage, that is, the DC-bus and AC-bus. They consist of a variety of combinations of the four DPS structures.

*DC-bus architecture vs. AC-bus architecture:*

The DC-bus architecture [A21] block diagram is illustrated in Fig. 1.5.

Fig. 1.5 DC architecture block diagram

In the DC-bus architecture, two DC-DC conversions are performed, that is, the front end DC-DC conversion and the load DC-DC conversion, which hurts system efficiency. The AC-architecture [A22], which is shown in Fig. 1.6, seems less complicated, since only one DC-DC conversion is performed and higher efficiency is expected. However, AC-bus structure has limited implementations. First, the AC bus brings Electromagnetic Interference (EMI) issues and special cables such as shielded or flat cables, and must be used to reduce the noise, which increases the cost. The skin effect from the AC bus increases the power losses especially at high switching frequency. For low frequency systems, bulky filter is required, which also increases the system cost. Furthermore, the AC voltage rectification injects current harmonics to the AC bus and hurts the power factor. As a result, DC-bus architecture has gained increased popularity and has become more and more mature due to the low noise and low power loss on the DC bus. The modularity of the DC-DC converter gains the DC-bus architecture wide acceptance and cost effective implementation in telecom and computing power supply systems.

Fig. 1.6 AC bus architecture block diagram

The main work of this dissertation focuses on the on-board DC-DC converter power module in the DC-bus architecture of DPS.

*Issues in power module:*

#### A. Efficiency:

Efficiency is one of the key specifications for the overall performance of the converters. Excessive heating and heat transport, i.e., thermal management, is probably the most important parameter in the system design since it has a direct impact on the system reliability and available performance. The power module, as well as the power board, account for 10-20% of the heat. It is important to state that, the efficiency is high not only at max load, but also over the whole or at least main part of the load range. Another parameter that could be important is the idling power, i.e., input power at no load conditions, especially in telecom battery operated equipments where normally many functions are inactivated. Synchronous rectification should substantially increase the efficiency once suitable semiconductor devices and circuit techniques are developed. To achieve small size of point-of-load converters, high-frequency DC-DC converter designs must be employed. New converter technologies should be explored to combine low switching losses with low device voltage and current stresses. Semiconductor and magnetic devices should be improved to meet challenges of high-frequency, high-density on-board converters.

#### B. Power density and packaging:

One of the most advertised parameters today is the power density. Very high figures in excess of 50 W/in<sup>3</sup> have been announced for high power DC-DC power modules. However, the physical laws give a relationship between the temperature rise,

power dissipation and the thermal resistance, i.e. the thermal conductivity and the effective cooling surface area, which in practice means that additional heat sinks and forced cooling have to be used, or that the output power has to be derated substantially, at these power densities. New packaging techniques need to be developed to allow increase of the power density of on-board converters. High-voltage integrated circuit technology must be employed to improve electrical performance and power density. Hybrid thick-film technology or similar techniques will be necessary to achieve the required density and provides adequate thermal management.

#### C. Noise:

Placement of a high-frequency on-board converter in a close proximity to noise-sensitive electronic circuits may cause EMI problems. Extensive research is necessary in this area to provide better understanding of the problem and to develop appropriate design tools and techniques. New circuit techniques must be sought to minimize the EMI generated by the load converters. Innovative packaging and shielding techniques will be necessary to reduce the EMI problems.

#### D. Safety:

Safety requirements for Information Technology and telecom equipment, including equipment intended to be connected to telecom networks and telecommunication networks are specified in EN60950 as well as CSA-C22.2. In certain applications there are requirements of electrical separation between the input and output of DC-DC converters. As specified in EN60950, there is a requirement of 1500Vdc or 100Vac electrical separation between the telecommunication network and parts and circuitry that can be touched by the test finger. The 1500 Vdc is required because there is

a risk of high voltage transients due to lightning interference in the telecommunication network and in the bonding network in smaller remote access nodes. Also, other AC mains disturbances can cause high voltage transients in the bonding network.

#### E. Cost:

Manufacturing costs (measured in dollars per watt) for distributed-power modules are currently higher than those for centralized power supplies. This may cause an economical barrier in some applications where DPS architecture is desired, but economical considerations are an overriding factor. To make the DPS approach attractive for these applications, the manufacturing costs must be reduced. This can be achieved by extensive standardization of the DPS subsystems and full utilization of the surface-mount technology.

#### 1.2 Dissertation outline

The dissertation consists of eight Chapters. In Chapter 1, the background introduction is carried out focusing on distributed power system. Important issues are discussed for on-board DC-DC converters. Efficiency is the first concern for a highly reliable distributed power system.

In Chapter 2, a review of existing converter topologies is carried out, which gives a general idea of the state-of-the-art work and techniques. Half-bridge is a promising topology for low-voltage high-current on-board DC-DC modules. Focusing on this topology, a variety of research work is done in the following Chapters, aimed at building the half-bridge topology based DC-DC converter with high efficiency and fast transient

response. To design a converter with fast transient response, high bandwidth is required. There generally exists several ways to obtain high bandwidth. The most straightforward solution is to go with high-frequency switching. The switching power supplies have limited bandwidth due to the limited switching frequency, which are limited by the switching losses. The switching losses are meaningful for frequencies higher than 500kHz. Also, high switching frequency and high-current increase the electromagnetic emissions, which creates interference in nearby electronic circuits. Employing control techniques can expand the bandwidth for a given switching frequency. Among the state-of-the-art control techniques, peak current mode control is widely employed which allow converter to have higher bandwidth for given switching frequency.

However, as introduced in Chapter 3, peak current mode control cannot be directly applied on half-bridge topology due to the voltage imbalance problem on the capacitors. A brand new capacitor voltage imbalance correction concept is proposed in Chapter 3, in which the voltage imbalance is detected and compensated. The error information is included in the driving signal, which corrects the voltage imbalance automatically. The novel compensation concept focuses on the control circuitry instead of modifications on power stage. As a result, the designer is free to design the power stage as it is and the converter electrical characteristics are not affected by the voltage imbalance correction. Based on the compensation concept, two control schemes are derived with one scheme for symmetric half-bridge topology and the other one scheme for Duty-Cycle-Shifted (DCS) half-bridge. Both proposed schemes focus on control to correct the capacitor voltage imbalance instead of modifying the power stage and are suitable for integration. For the first control scheme, the proposed compensation circuit

enable peak current mode control to be applied to conventional symmetrical half-bridge. For the second control scheme, the proposed circuit corrects the voltage imbalance and easily generates the DCS driving signal, which makes DCS topology simple for application in DC-DC on-board converters. With the proposed control scheme, DCS topology is now complete for implementation. Following this Chapter, detailed modeling work is demonstrated. The modeling methodology of the capacitor imbalance is different compared with the conventional modeling work since the control variable is the voltage imbalance of the half-bridge capacitors. The modeling results explained why peak current mode control cannot be directly applied on a symmetric half-bridge and the results are also applicable for Duty-Cycle-Shifted (DCS) half-bridge topology, which provides the theoretical understanding of the capacitor voltage imbalance in symmetrical half-bridge topology. The validity of the proposed control schemes is verified as well in the modeling point of view.

To reduce the power losses and improve the converter efficiency, a variety of clamping techniques are proposed in Chapter 4. For the primary side, the active-clamping-tank concept is proposed to manage the power stored in leakage inductor during the freewheeling interval. Three clamping tanks consisting of capacitor, diode and active switch are proposed along with stress analysis, schemes comparisons and practical design considerations. The proposed Two-FET-Clamping tank is suitable for larger duty cycle applications, in which freewheeling time is short. The oscillation caused by the leakage current and junction capacitance is eliminated and ZVS is obtained for both Metal-Oxide Semiconductor Field-effect Transistor (MOSFET)s. For small duty cycle applications, the proposed FET-Diode-Capacitor tank prevents current from freewheeling

through the switch during main MOSFET off-time. As a result, the conduction loss from current freewheeling is significantly reduced since leakage inductor current drops to zero in very short time and the diode blocked the oscillation between the clamp capacitor and the leakage inductance.

The power management concept in the clamping FET-Diode-Capacitor tank employs the clamping capacitor as energy storage so that the ringing in conventional half-bridge during main switch off-interval is not present due to the energy transferring from the leakage inductor to the clamping capacitor. The only disadvantage might be the non-ZVS turn-on of the main switch since the energy stored on the clamping capacitor is not effectively used to discharge the junction capacitor of the main MOSFETs prior to turning on them. In another proposed technique applied on active-clamp DC-DC converters, the energy stored in clamping capacitor is well used to realize the ZVS of the main switch and the freewheeling loss is reduced as well due to the fast charging to the clamping capacitor with the magnetizing energy. On the secondary side of the transformer, a lossless Zener-Capacitor clamping circuit is proposed to stabilize the driving voltage during line change. The proposed technique can be applied on all selfdriven topologies with wide input line change, which may have wide applications on telecom power supply systems since the general input line range is from 35V to 75V. Issues in this circuit are also discussed and trade-offs between power loss and voltage stabilization shall be carefully made.

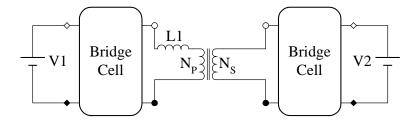

In Chapter 5, a novel phase-shift power delivery concept for the half-bridge topology is proposed. Since the MOSFETs are driven complimentarily for the primary side and secondary side MOSFET pair, the Zero Voltage Switching (ZVS) for the

MOSFET can be easily obtained. One important issue in the phase-shift half-bridge is the reactive power, which may affect efficiency significantly. Important conclusions are drawn from intensive analysis for the bi-directional phase-shift half-bridge DC-DC converter and design suggestions are given as well.

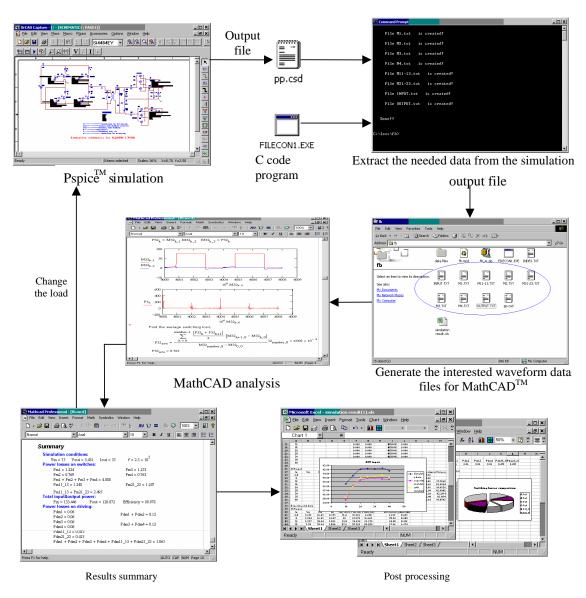

For the efficiency considerations, the power losses in converters are investigated using the proposed power losses estimation platform in Chapter 6. The proposed power losses estimation platform is based on simulation software such as Orcad suite, Maxwell and analysis software such as MathCAD and Microsoft Excel. With the proposed software platform, power losses estimation in any converters can be easily obtained, which gives a clear picture of the losses distribution and the percentage the losses on the key component amount to be. From one example given in Chapter 6 (a full-bridge DC-DC converter), it is illustrated the main losses come from the power MOSFET and the transformer in low-voltage high-current DC-DC converter. For low-voltage rated MOSFET, the driving loss has a relatively larger percentage compared to its high voltage rated counterpart. The efficiency curve comparison is also made for a specified converter between the software estimation and lab experimental results. The difference between them is less than 2 percent, which justifies the accuracy of the platform.

# 2. KEY APPROACHES TO BUILD ON-BOARD DC-DC CONVERTER WITH HIGH EFFICIENCY AND FAST TRANSIENT RESPONSE

#### 2.1 Topology and control scheme overview

In recent years, there have been many significant technological changes in power supply design. There became possible with advances in power transistors, integrated circuits, capacitors and design techniques. This has resulted in lower cost per watt with improved performance. For the on-board DC-DC converter applications, there generally exist non-isolated and isolated DC-DC on-board converters. A typical non-isolated DC-DC on-board converter is Voltage Regulator Module (VRM) [B1-B7], which has dominant applications in server and workstation computing systems. VRM emerges from the so-called "Point-Of-Load" (POL) power delivery concept. In a computing system, the silver box works as the center unit for power delivery. Due to the parasitics between the silver box and the CPU, POL is proposed to deal with the extremely fast transient response requirement from the CPU. The converter delivers power to the CPU and is placed as close as possible so that the parasitics are not significant enough to degrade the power delivery quality. Buck topology is widely employed in VRM. Since the step down is quite limited due to the degraded performance for small duty cycle, 12V is generally employed as the standard input voltage. With the help of an isolation transformer, the designer has more flexibility to design the isolated on-board DC-DC converters. By choosing transformer turns ratio, the duty cycle can be optimized to give the best performance of the on-board DC-DC converters. Buck derived topologies have the dominant applications in low-voltage DC-DC area due to their step down feature. The topology includes full-bridge, half-bridge, push-pull and forward.

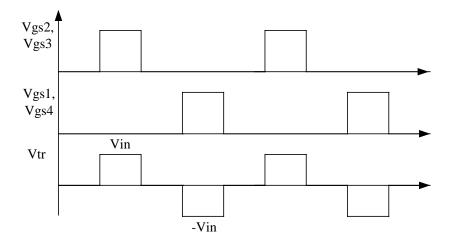

#### 2.1.1 Full-Bridge topology

The full-bridge topology [B8-B13] is shown in Fig. 2.1.

Fig. 2.1 Full-Bridge topology

Fig. 2.2 Driving signal

Full-Bridge topology is derived from Buck topology and has popular applications on high power (>500W) converters. Four switches with two in each leg switches alternatively to deliver the power to the load. When S2 and S3 conduct at the same time, Vin is applied to transformer primary winding. The polarity of the voltage applied on primary side winding reverses when S1 and S4 conduct. As a result, transformer core is fully utilized and no core resetting circuit required. Smaller core can be employed for full-bridge topology for given power. To prevent DC bias in the transformer, a capacitor is usually added in series with the transformer winding.

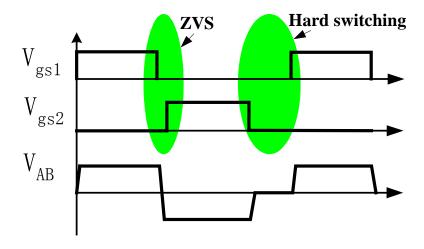

Another topology called Phase-Shift-Controlled Full-Bridge [B12-B16] also has wide applications in high power converters. The only difference is the switching sequence of the four switches as shown in Fig. 2.3. For each leg, the high-side MOSFET and low-side MOSFET have complimentary driving signal with very short dead-time between them. The overlaps between S1, S3 and S2, S4 driving signals are modulated by PWM controller to regulate the converter output. The short dead-time allows MOSFET body diode conduct due to the discharging of the junction capacitance of the MOSFET by the leakage inductor energy to obtain ZVS condition. The switching losses are reduced significantly and ringing between transformer leakage inductance and MOSFET junction capacitance in conventional PWM full-bridge topology is eliminated, which gives good solution for EMI issue. Issues in the topology are found as: a) Freewheeling energy leads to power losses and hurts the efficiency especially at high line input with small duty ratio. b) The lagging leg may more easily lose ZVS due to insufficient energy stored in leakage inductance to discharge the MOSFET junction capacitance.

Fig. 2.3 Phase-shift full-bridge driving signal and transformer winding voltage

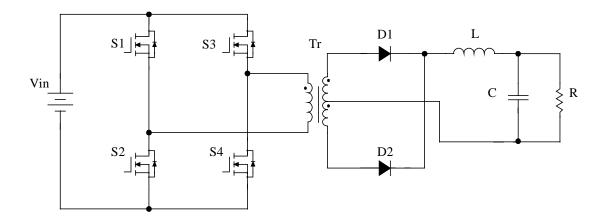

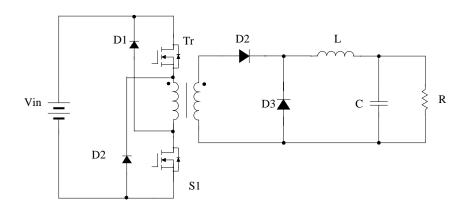

### 2.1.2 Half-Bridge topology

The half-bridge topology [B17-B25] is a promising topology for low and medium level power converters.

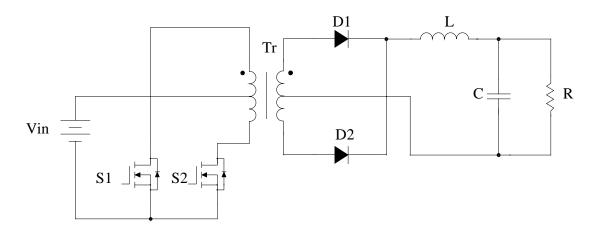

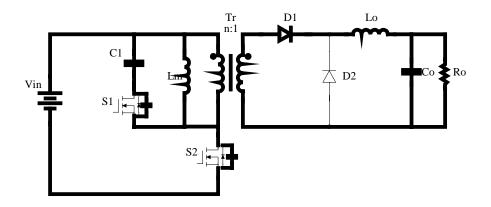

Fig. 2.4. Half-Bridge topology

The two switches connect the single transformer primary across the two capacitors alternately. The primary half-bridge voltages and currents are AC. DC current is not drawn from the center-tap of the input supply. Different with the full-bridge topology, no extra capacitor is needed to eliminate the DC bias in the transformer since the two capacitors automatically correct the mismatch of the switching by changing their voltage. Since two capacitors share the input voltage evenly, the voltage stress for the MOSFET is half of the input voltage compared with the case in full-bridge topology. As a result, lower voltage rated MOSFET is qualified for half-bridge topology application. Two half-bridge topologies are widely used in DC-DC converters, i.e., the symmetric half-bridge topology and the asymmetric half-bridge topology.

#### 2.1.3 Symmetric Half-Bridge topology

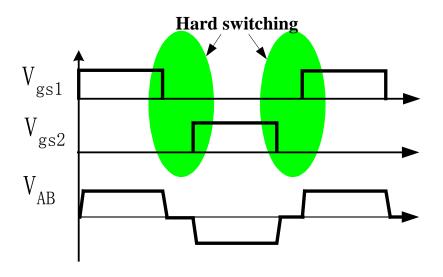

The switch driving signals and transformer voltage waveform of the symmetric half-bridge topology [B17][B20][B25] are shown in Fig. 2.5.

Fig. 2.5. Symmetric Half-Bridge driving waveform

Since the switches are driven symmetrically, all components including the secondary side synchronous rectifier MOSFETs have even stresses. The main drawback of the conventional symmetric half-bridge is that both primary switches in the converter operate with hard switching. Moreover, during the off-time interval of two switches, the oscillation between the transformer leakage inductance and junction capacitance of the switches results in energy dissipation and EMI emissions due to the reverse recovery of MOSFETs body diodes. To suppress the ringing, resistive snubbers are usually added. As a result, energy in the transformer leakage inductance is significantly dissipated in snubbers. Therefore, the symmetric half bridge is not a good candidate for high-switching frequency power conversion.

#### 2.1.4 Asymmetric Half-Bridge topology

The asymmetric (complementary) control was proposed to achieve ZVS operation for half-bridge switches [B21-B24]. Two drive signals are complementarily generated and applied to high-side and low-side switches respectively. Therefore, the two HB switches may be turned on at ZVS conditions, attributing to the fact that the transformer primary current charges and discharges the junction capacitance.

Fig. 2.6 Asymmetric Half-Bridge driving waveform

However, asymmetric stress distribution on the corresponding components may occur due to the asymmetric duty cycle distribution for the two primary switches. In other words, voltage and current stresses on the switches including both the primary side and secondary side MOSFETs are not identical. As a result, diodes or synchronous rectifiers with higher voltage rating are needed at the penalty of degrading the performance and efficiency of the rectifier stage. Furthermore, the DC gain of the converter is nonlinear, thus larger duty cycle variation is observed for the same input voltage variation in comparison with symmetric PWM control scheme. This makes the converter operate further beyond the optimum operating point at high input voltage. Therefore, the complementary (asymmetric) PWM control is more suitable for applications where the input voltage is fixed. As a solution to reduce the duty cycle variation for wide input voltage range, an asymmetric transformer turns ratio together with integrated-magnetic structure, was proposed in literature, such that rectifiers with lower withstanding voltage may be used to improve the performance. However, the power delivery of the transformer and current stresses in the switches and rectifiers are still uneven.

#### 2.1.5 Push-Pull topology

Push-pull topology [B26-B29] is suitable for low input voltage, and it tends to exhibit low primary-side conduction losses, since at any given instant only one switch is connected in series with the DC source. As shown in Fig. 2.7, transistors S1 and S2 are alternately switched on for time period. This subjects the transformer core to an alternating voltage polarity to maximize its usefulness.

Fig. 2.7. Push-Pull topology

Compared with the other symmetrical converters such as full-bridge and half-bridge, this circuit has the advantage that the transistor switches share a common signal return line so that the driving is relatively easy. Its chief disadvantages are that the transformer center-tap connection complicates the transformer design and the primary windings must be tightly coupled in order to avoid voltage spikes when each transistor is turning off. The push-pull drive automatically provides core reset on alternate half cycles, but these alternate half cycles must be quite symmetrical or the volt-seconds will not cancel, which results in core saturation.

### 2.1.6 Forward topology

The forward topology [B30-B34] has several versions different in resetting the magnetizing energy.

Fig. 2.8. The classical forward topology

Fig. 2.9. The forward converter with RCD snubber

Fig. 2.10. The forward converter with a LCDD snubber

Fig. 2.11. The forward converter with two switches

Fig. 2.9. Active-clamp Forward topology

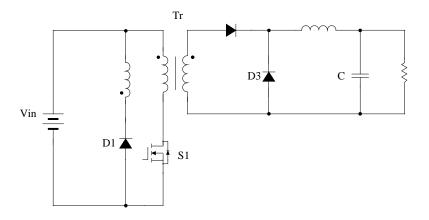

#### A. The classical forward converter:

When switch is on, power is delivered to the load. When switch is off, an auxiliary winding resets the transformer through diode D1. For the same number of turns of the reset winding as the power transformer, which is a common choice, the duty ration is less than 50%. Voltage stress on the MOSFET is typically 2.6Vinmax, this is considered high and it limits the performance of the converter, especially when the input voltage is high. Another disadvantage is that the reset winding increases the complexity and hence the cost of the transformer.

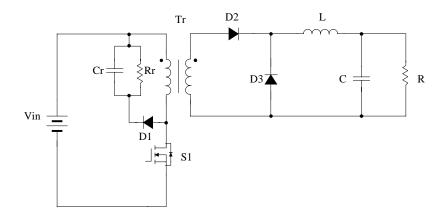

#### B. The forward converter with RCD snubber:

When the switch is on, the main power forwarding is the same as in the classic forward converter. When switch is off, a diode D1 and a capacitor Cr clamp the voltage to a level determined by the input voltage and duty ratio. A resistor R resets the capacitor. The voltage stress on the MOSFET is typically 2*Vinmax*.

#### *C. The forward converter with a LCDD snubber:*

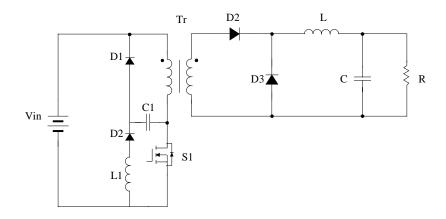

It recovers part of the energy dissipated in the previous scheme by the resistor. It uses an inductor, a capacitor and two diodes and is known as LCDD snubber. When the switch is on, the main power forwarding is as the previous forward converter, when the switch is off, a diode and a capacitor clamp the drain-source voltage in the same manner as in the case of a RCD snubber. Reset of the capacitors accomplished through a LC resonance formed by L1, C1 and D1, D2. The voltage stress on the MOSFET is typically 2*Vinmax*. This topology requires excessive design iterations to ensure proper operation over all load, line, and transient conditions due to the resonant features. The size of L1 can be large when the input voltage is high.

#### *D. The forward with two switches:*

At turn-off, two diodes connect the primary to the input, but in a reversed polarity resetting the transformer automatically. Because of the clamping, the voltage stress on the MOSFET is typically *Vinmax*. The disadvantage is it needs additional switch and one high side driver.

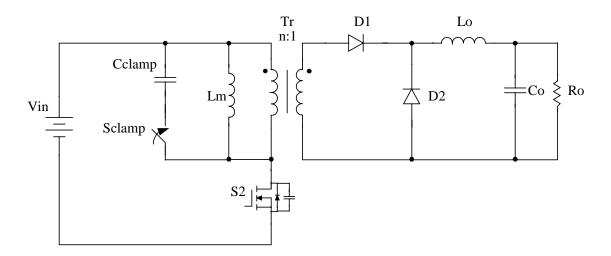

#### E. Active-clamp forward:

The operation during the turn-on interval of the main MOSFET is the same as the one before. When the main switch is off, an active device is used to reset the capacitor. The voltage stress on the MOSFET can be designed as low as 1.3Vinmax. A significant feature is that, it not only clamps the voltage across the main MOSFET during turn-off, but also provides improved switching condition at turn-on. The key to this soft switching scheme is that the drain-source current can be designed to start with a negative value. Since the current then has to flow in the body diode, the main MOSFET is switched on with virtually zero voltage. Furthermore, zero-voltage switching allows a lossless snubber to be used at turn-off. The auxiliary switch is also switched with zero voltage at turn-on and with a favorable condition at turn-off.

The disadvantage of this topology is that, an additional MOSFET and its associate driver are required. The conduction loss is increased by 30% to 50% due to small magnetizing inductance.

#### 2.2 The relationship between efficiency and transient response

Efficiency and transient response are two critical specifications for on-board DC-DC converters. As mentioned before, high efficiency can reduce the power losses; better thermal management leads to high reliability. Fast transient response enable the converter react quickly to the line change and load change. As a result, the overshoot and under shoot is greatly reduced which reduces the fault risk of the on-board DC-DC converters.

#### 2.2.1 Efficiency concern

Efficiency is defined as the ratio of the total output power to the input power.

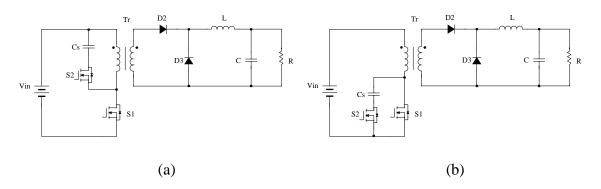

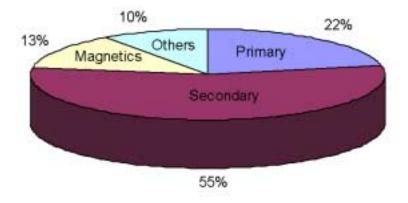

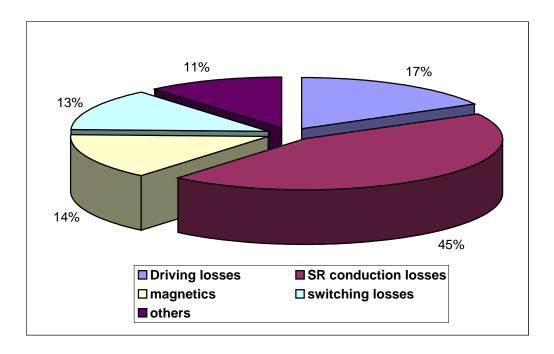

High efficiency means low power losses in the converter. Therefore, a clear understanding of the power losses in on-board DC-DC converters is very important. Fig. 2.10 shows the power losses distribution for one low-voltage high-current DC-DC converter with half-bridge& current doubler structure.

Fig. 2.10 The power losses distribution of one DC-DC converter in one typical low-voltage high-current application

Since secondary side of the transformer has high-current, the losses on the secondary side amount to be the main part. Generally, the power losses in DC-DC converters consist of the following part:

#### A. Losses in MOSFETs:

- Switching loss.

- Conduction loss (including body diode conduction).

- Driving loss.

- Body diode reverse recovery loss.

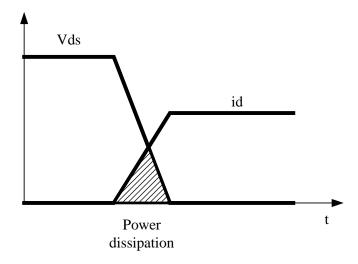

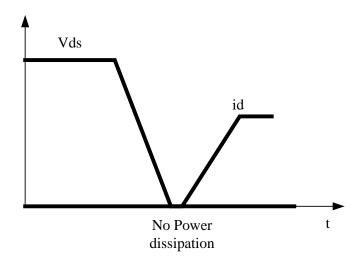

Switching loss and driving loss increase when switching frequency goes up. Soft switching techniques such as ZVS, Zero-Current-Switching (ZCS) can reduce the losses significantly. Conduction loss is decided by the current flows through it and the conduction resistance. Synchronous Rectification (SR) techniques replace the diode with MOSFET and is widely used in low-voltage high-current DC-DC converter applications where the body diode voltage drop is significant compared with the low converter output voltage. Connecting MOSFETs in parallel also reduce the conduction loss and is used quite popular in high-current applications.

#### B. Losses in magnetic components:

- Core loss.

- Copper loss.

Core loss is closely related to the material property and electrical performance of the circuit. Copper loss is related to current and winding trace physical properties, i.e., the trace resistance. When frequency goes up, core loss changes even the voltage-second keeps the same due to the magnetic material properties. The copper loss increases due to

the skin effect, which reduces the effective cross section area of the trace. For inductors, copper loss amounts to be the main part since DC current is relatively high compared with the AC ripple current while for transformers, core loss is larger due to the AC voltage applied on the windings.

#### 2.2.2 Transient response concern.

In the impedance point of view, transient response is the response of the converter when external disturbance applied. Fig. 2.11 shows the DC-DC converter being disturbed by the load current change. The load current with different step rate contains harmonics at all frequency level with different amplitude as shown in Fig. 2.12.

Fig.2.11. DC-DC converter with load transient.

Fig. 2.12. The Fourier component of the transient step current.

The transient response of the converter, i.e., the so called 'undershoot' and 'overshoot', is the overall response of the converter to all the harmonics brought by the load step change. To analysis the transient property of the DC-DC converters, it is necessary to start with the converter modeling. The DC-DC converter can generally modeled as shown in Fig. 2.13. The open-loop output impedance is firmly related to the output filter. As a result, the filter components and their parasitics play important roles in the transient behavior of the converter. The output impedance of one DC-DC converter with different Equivalent Series Resistance (ESR) is illustrated in Fig. 2.14. Feeding back the output can reduce the closed-loop output impedance significantly within the bandwidth while beyond the bandwidth, the transient behavior of the converter is decided by the parasitics and nothing can be done for the converter with given filter parameters as shown in Fig. 2.15.

Fig.2.13. Small-signal Model of the on-board DC-DC

Fig. 2.14. The output impedance model

Fig. 2.15. The output impedance vs. different capacitor ESR

#### 2.2.3 The relationship between transient response and efficiency

To obtain fast transient response, high bandwidth is required so that the closed-loop impedance can be controlled within the bandwidth in specific frequency range. There exists several ways to expand the bandwidth of DC-DC converters. The most straightforward one is choosing high switching frequency. With high-frequency switching, the filter may have smaller inductor, which reduces the output impedance of the converter. However, high switching frequency always means high losses and low efficiency. When switching frequency increases, the losses on the MOSFETs (switching loss, driving loss and body diode reverse recovery loss) go up, the losses on the magnetic component also increase due to the material property (core loss) and the skin effect of the windings (copper loss).

A large variety of solutions are proposed to expand the bandwidth in the literatures. From the topology point of view, soft switching techniques such as ZVS and ZCS are widely employed in high-frequency switching converters. From the control point of view, various control schemes are proposed to expand the bandwidth. Among which, the peak current mode control has long been introduced and applied in DC-DC converters.

# 3. NEW PEAK CURRENT MODE CONTROL CONCEPT AND DERIVED SCHEMES FOR HALF-BRIDGE TOPOLOGY

#### 3.1 Introduction

In recent years, the peak current mode control has been widely investigated for DC-DC converter applications [C1-C5]. In [C2], the peak current mode control is applied to a push-pull DC-DC converter topology for space applications. Dynamic current sharing between paralleled converters can be achieved by using peak current mode control [C3]. In [C5], small-signal model of a phase-shift full-bridge is presented based on the peak current mode control. The advantages for peak current mode control can be summarized as follows:

- a) One pole of the power stage is moved to higher frequency such that the voltage loop compensation becomes simpler and higher bandwidth and better transient response can be achieved.

- b) Feed forward control to the input line disturbance, and good output regulation can be achieved.

- c) Cycle-by-cycle current limit naturally provides over current protection.

- d) Easy to achieve current sharing for paralleled converters

Half-bridge is a suitable topology for low-voltage high-current DC-DC converters due to its simplicity [C6-C8]. However, peak current mode control cannot be directly applied on symmetric half-bridge DC-DC converter topology due to the capacitor voltage imbalance problem.

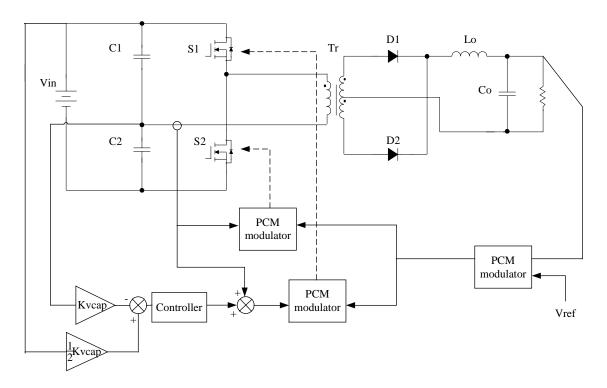

In this Chapter, a new compensation concept is proposed to correct the capacitor voltage imbalance. A voltage compensation loop is added to the control circuit so that no modification and extra components are needed in the power stage. Two schemes are derived from the proposed compensation concept. Experimental results verified the feasibility of the proposed control schemes. In Section 3.2, the proposed compensation concept is introduced in detail. The first derived control scheme for symmetric half-bridge is proposed and analyzed in Section 3.3, implementation circuit is introduced as well. In Section 3.4, the second derived control scheme for DCS half-bridge topology is proposed with detail for implementation. Prototype is built and verified with experimental results shown in Section 3.5.

#### 3.2 Proposed voltage imbalance compensation concept

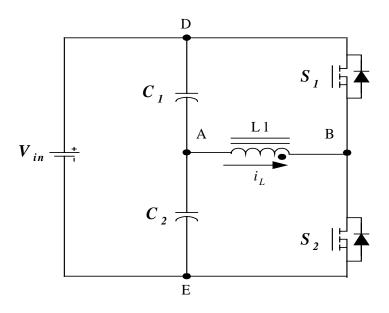

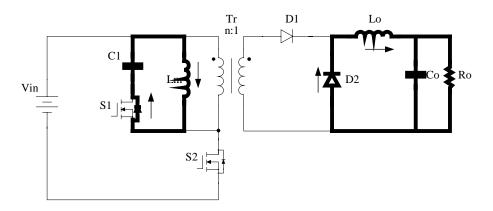

#### 3.2.1 The capacitor voltage imbalance problem in half-bridge topology

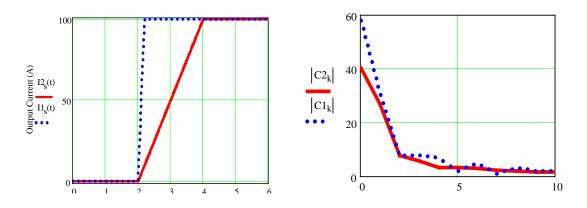

Fig. 3.1 shows the half-bridge topology. Capacitor C1 and C2 are necessary for circuit operation and the average voltages across them in one switching period are equal for ideal operation. However, the voltages across two capacitors C1 and C2 fall apart from equilibrium due to positive feedback induced from peak current mode control and finally one capacitor voltage (VC1 or VC2) drops to zero and the half-bridge topology stops working. For example, due to non-ideal component parameters when voltage across capacitor C2 is less than half of input bus voltage Vin and S2 is turned on, VAB=VAE<1/2Vin. It takes more time for iL to hit the current reference because of the

smaller di/dt induced by VAB. The capacitor C2 discharges more which leads to more voltage drop across C2. The positive feedback continues till VC2 drops to zero and half-bridge stops working. For VAE>1/2Vin case, the similar positive feedback exists and voltage across C1 is zero finally. Therefore, peak current mode control cannot be directly applied on half-bridge topology.

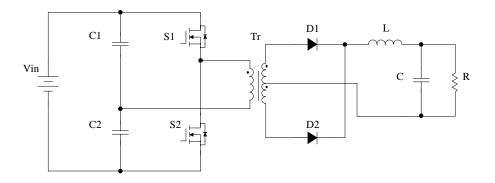

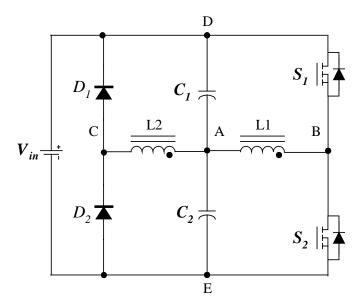

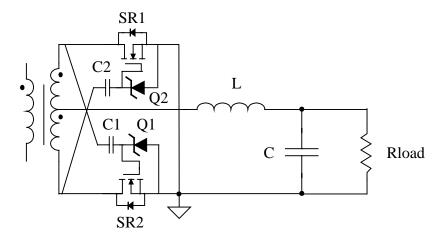

Fig. 3.1 Half-Bridge topology

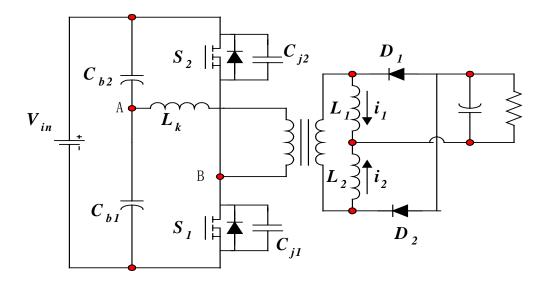

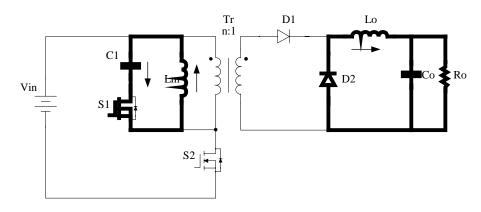

One solution shown in Fig. 3.2 is presented by an unknown engineer attending Unitrode seminar [C9]. Three extra components are added to the power stage to balance the capacitor voltage. Winding L2 has the same number of turns as the transformer primary side winding and is coupled with transformer. Two fast recovery diodes D1 and D2 are connected which forms an additional branch to balance the capacitor voltage. When VAE>1/2Vin and S2 is on, VAB=VAE>1/2Vin. Since L2 and L1 have the same number of turns, VCA=VAB>1/2Vin, VCE=VCA+VAE>Vin, diode D1 conducts and VCE is clamped to Vin. For VAE<1/2Vin case, when S1 is on, VBC>Vin, the low side

diode D2 conducts and clamps VBC to Vin. The positive feedback is avoided finally and the voltage across the capacitor is brought back to normal.

Fig. 3.2 One solution to balance capacitor voltages in half-bridge topology

The solution automatically corrects the voltage imbalance problem on the half-bridge capacitors and does not affect the efficiency much since power flow in the additional branch is not big. However, disadvantages are found as follows: a) Modifications on the power stage are required. b) An additional winding (even may be small but with the same number of turns as the transformer primary side winding) is needed which complicates the transformer structure and degrade the transformer performance.

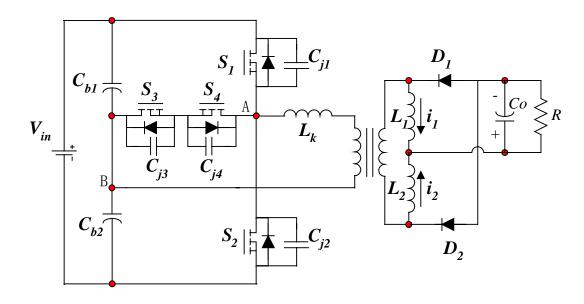

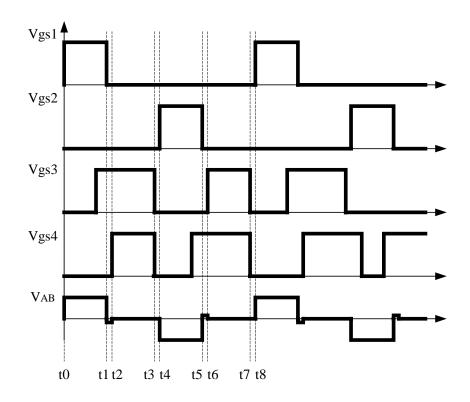

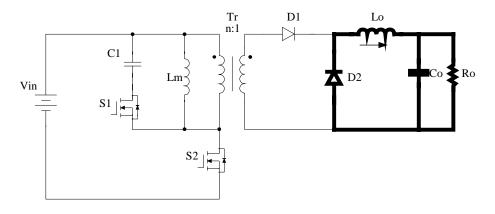

#### 3.2.2 The proposed capacitor voltage compensation concept

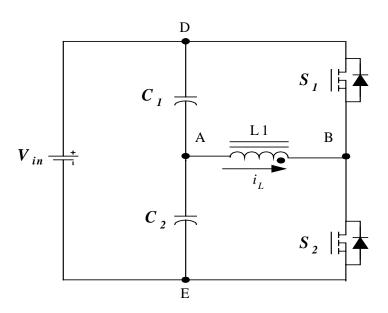

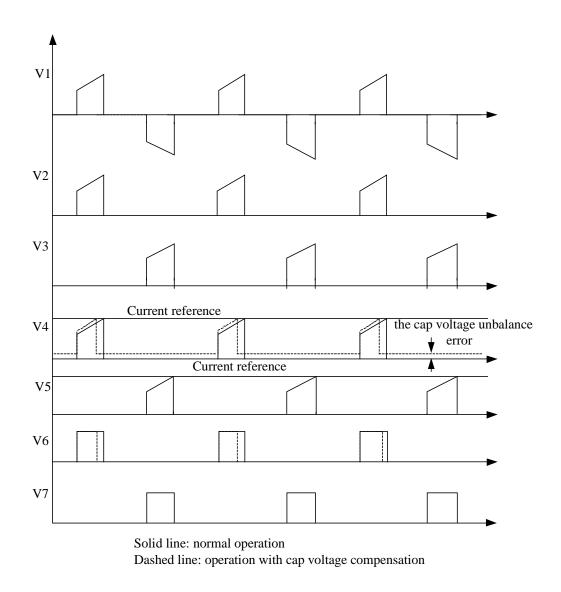

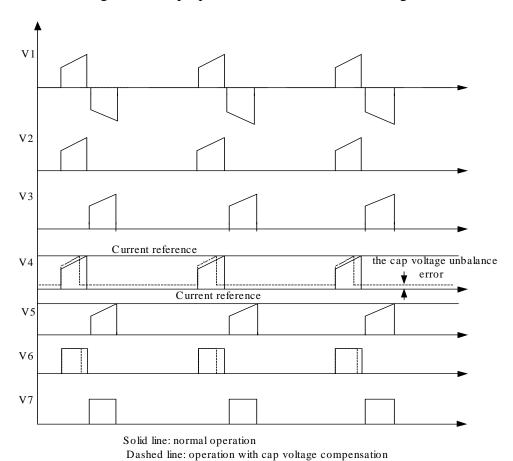

The idea to balance the capacitor voltage is to use an additional voltage compensation loop to correct the capacitor voltage imbalance. The the key waveforms for the proposed control scheme are shown in Fig. 3.4. Whenever voltage imbalance exists, the compensation loop corrects the capacitor voltage by changing duty ratio of one channel MOSFET driving signal to prevent positive feedback and bring the capacitor voltage back to balance. For example, if VAE is less than half of the input bus voltage Vin, the control loop decrease the duty ratio of S2 driving signal in spite of small current slop of iL. Less discharge of the capacitor prevents the positive feedback and brings back VC2 to normal. For the other case, the duty ratio is increased and the capacitor discharged more.

Fig. 3.3 Half-Bridge topology

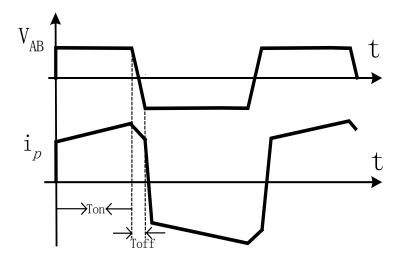

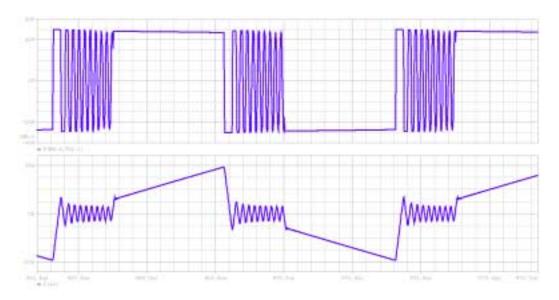

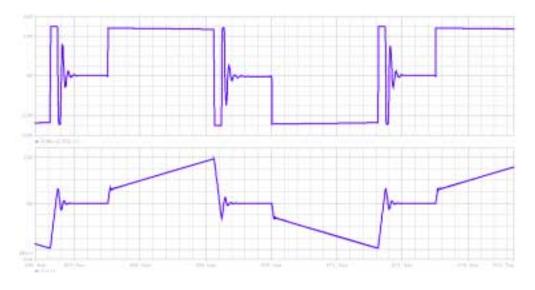

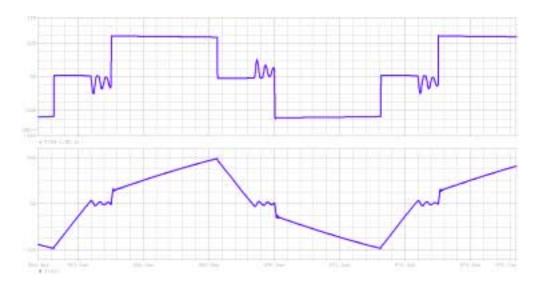

Fig. 3.4 Key waveforms for the proposed compensation concept on symmetric halfbridge topology

The proposed scheme has advantages as follows: 1) Positive feedback is prevented by proposed control scheme. Peak current mode control can be applied on half-bridge topology with the proposed control scheme. 2) No modification on the power stage, all compensations are done in control circuitry, no extra component needed for the power stage. 3) Simple control circuitry, suitable for integration.

#### 3.3 Derived control scheme for symmetric half-bridge topology

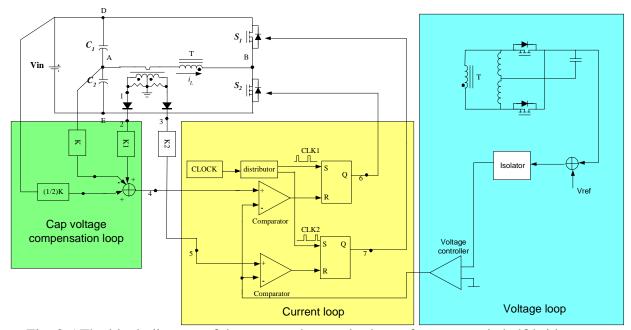

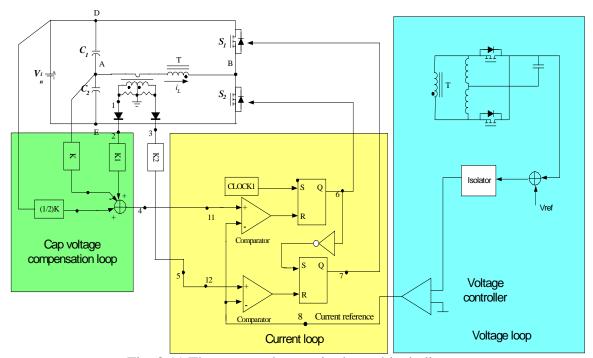

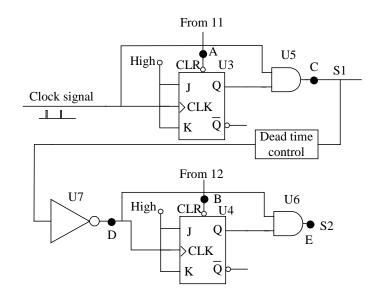

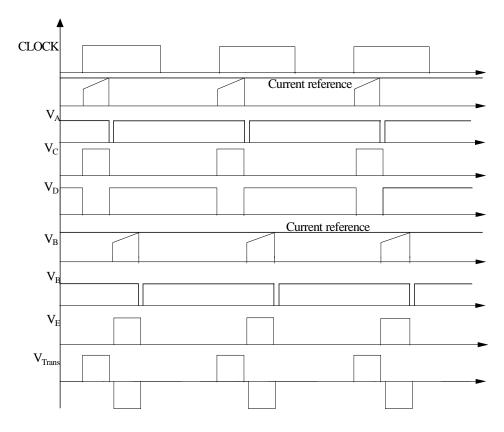

The proposed control scheme is shown in Fig. 3.5. Key waveforms are shown in Fig. 3.4. Current flowing through transformer primary windings is detected by current transformer and is split into two channel signals by two diodes. The two current signals correspond with the on-off states of the two switches in half-bridge. The voltage imbalance error information is added to one channel current signal to compensate the duty ratio of the related MOSFET driving signal. The other channel MOSFET driving signal keeps unchanged without any compensation. The compensation is implemented by sensing the input bus voltage and the low side capacitor voltage of the primary side halfbridge. For a given stable input, if two capacitor parameters are equal, the low side capacitor voltage is half of the input bus voltage. As a result, half of the detected input line voltage value is compared with the capacitor voltage value. The difference contains the information of the capacitor voltage deviation. To generate the reset signal for peak current mode control so that to control the falling edge of the MOSFET driving signal, circuit in Fig. 3.5 is proposed in which, a comparator is used with the non-inverting pin connected to the current signal and the inverting pin connected to the current reference provided by the outer voltage loop. When the current signal hits the current reference, the comparator output is set to high, the RS flip-flop is reset and the control signal falling edge is generated.

Fig. 3.5 The block diagram of the proposed control scheme for symmetric half-bridge topology

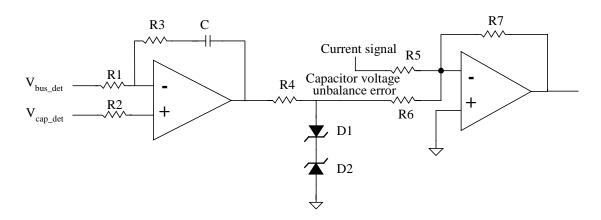

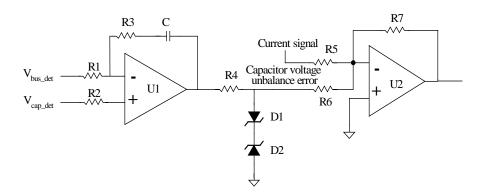

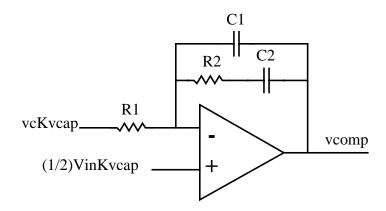

Fig. 3.6 Capacitor voltage compensation loop implementation

The detailed circuitry for compensation loop is shown in Fig. 3.6. Vbus\_det is the input bus voltage detection and Vcap\_det is the capacitor voltage detection. Both of them are from voltage divider and scaled to be equal if capacitor voltage is perfectly balanced. A PI controller is used to generate the error signal for the voltage imbalance correction.

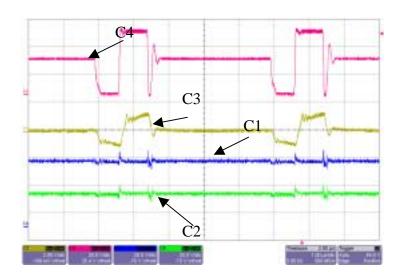

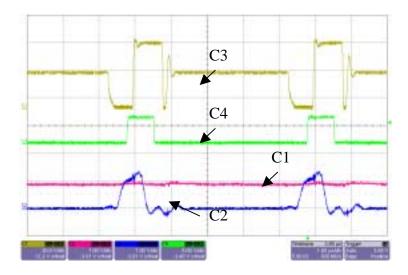

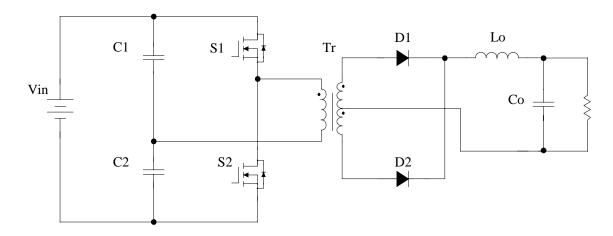

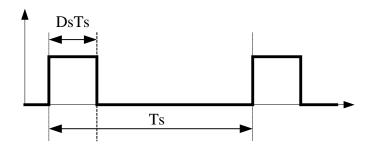

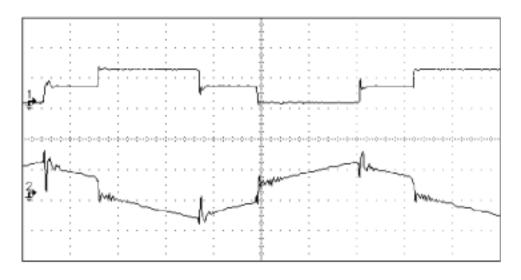

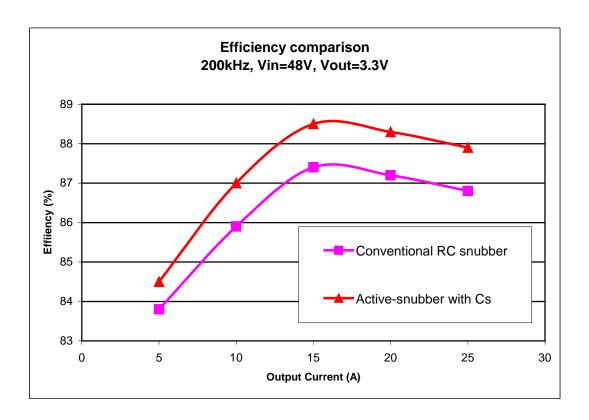

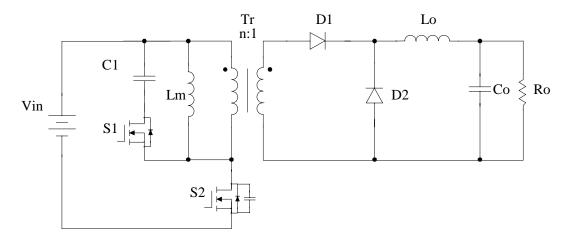

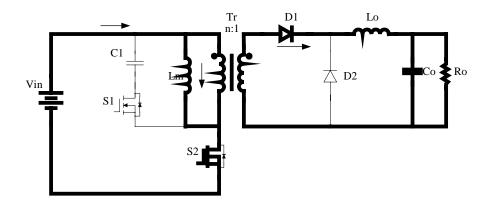

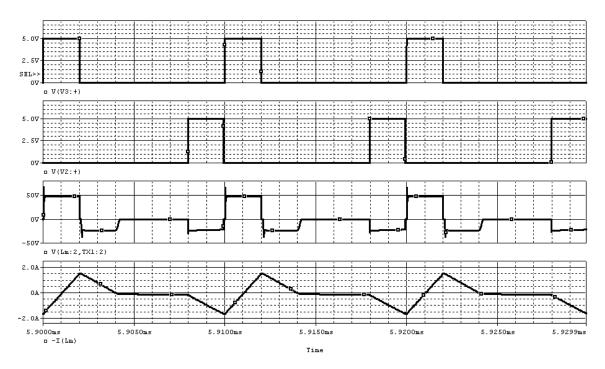

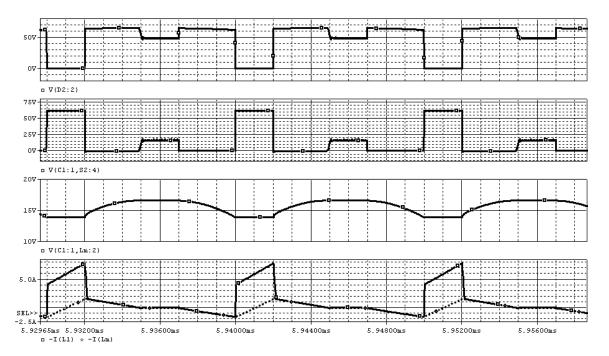

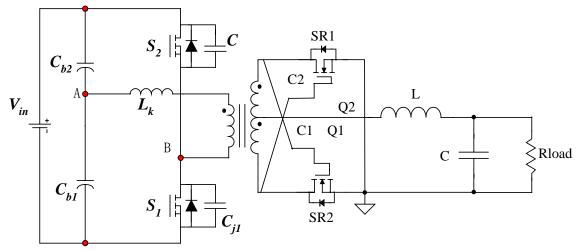

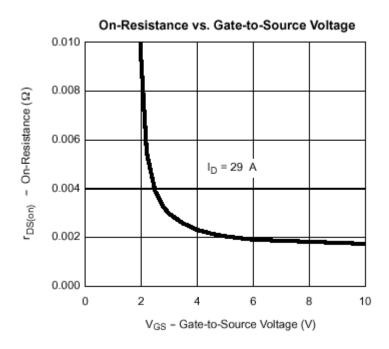

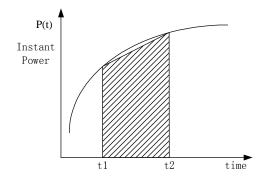

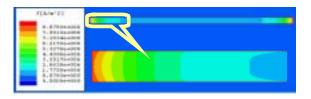

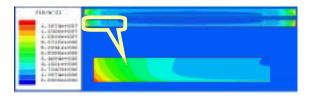

Since voltage imbalance correction does not require very fast compensation, the compensation loop does not need wide bandwidth. Low speed operation amplifier is qualified for implementation. One channel current signal and capacitor voltage imbalance error are fed into adder (or other equivalent circuitry) causing current signal biased according to the voltage imbalance error. The new current signal contains both current information and voltage imbalance information, which can be used to compensate the capacitor voltage. If the voltage of the low side capacitor (Vc2) is less than half of the input bus voltage, the output of the PI controller is negative. Recalling the fact that the adder shown in Fig. 3.6 has negative gain, the current detection signal is lifted by the value of the error signal. To reverse the polarity, an additional opam with negative unit gain is used. For a given current reference, it takes less time for the current signal to hit the reference compared with its uncompensated counterpart. A less-pulse-width driving signal is induced and switch S2 has less on time. Therefore, capacitor C2 discharged less, which breaks the positive feedback and brings the voltage back to normal.