# HIGH-DENSITY HIGH-CURRENT FAST-TRANSIENT LOW-VOLTAGE DC-DC CONVERTERS

By

## JABER A. ABU QAHOUQ

B.Sc. Princess Sumaya University/Royal Scientific Society, 1998 M.S. University of Central Florida, 2000

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Major Professor: Issa Batarseh

Fall Term 2003

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 3110042

## INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

### UMI Microform 3110042

Copyright 2004 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

To my parents

### ABSTRACT

Powering requirements of new and future high-performance, high-speed and highintegration density load of DSPs and microprocessors are continuously and increasingly becoming more stringent. More devices are being packaged on a single chip with increased integration density, causing higher load current demands and forcing their operating voltages to drop to levels below one volt. Moreover, such load speeds (operating frequency) are increasing at a fast pace, and they switch the current they draw with increasingly higher slew rates (faster) causing larger voltage deviation during their transients, which should be limited to a very small value especially at low voltages to guarantee safe and high performance operation.

To avoid distribution line parasitics and losses, such loads are not being powered by a DC voltage and current from a centralized power supply as used to be done in the past. Instead, a Distributed Power System (DPS) with a DC-DC converter at its near-load end is placed close to the load. These specially designed DC-DC converters are usually called Voltage Regulator Modules (VRMs) or Point-Of-Load (POL) Converters, and they must satisfy their stringent load requirements of low-voltage, high-current and fasttransient. At the same time, they should maintain high-efficiency and high power density (smaller size) as their loads integration densities becomes higher also. Converter optimizations include power stage and control loop optimization. The scope of this work is the POL and VRM DC-DC converters requirements, design and optimization. Topologies and control techniques for DC-DC converters are presented after reviewing loads powering requirements and DC-DC converters steady-state and transients design challenges and theoretical analysis.

Non-isolated multiphase voltage-mode hysteretic controlled DC-DC converter control scheme and topology with current sharing is presented and supported by theoretical analysis with output voltage ripple, switching frequency and stability condition equations along with experimental results. This method combines the advantages of the interleaving technique and hysteretic control while achieving current sharing, which results in advantages that include fast transient response and equal current sharing between converter phases.

Then, after reviewing selected isolated topologies, a control method for isolated half-bridge DC-DC converter topology, namely, Duty-Cycle-Shifted (DCS) control, is presented. This method allows soft-switching operation for half-bridge for higher efficiency at higher switching frequency and allows for reduced switching and isolation transformer-leakage inductance-related losses without the penalty of asymmetric components stresses and isolation transformer DC bias. Theoretical discussion and experimental results are presented and compared to other half-bridge control methods.

Another general control method for half-bridge topology, called Alternated Duty Cycle (ADC) control, is also presented. This method can achieve soft switching for halfbridge switches alternatively, if not for the two switches, and can do so without the penalty of asymmetric components stresses and isolation transformer DC bias, while improving efficiency and maintaining thermal balance of the half-bridge switches. Theoretical discussion and experimental results are presented.

Also presented is the interleaving method for isolated topologies, where the secondary side switches operate at lower switching frequency than the primary side switches to improve efficiency and to improve transient response. Meanwhile, both primary and secondary sides of the isolation transformers are connected in parallel, allowing sharing of currents at both primary and secondary sides. This method resulted in a family of interleaved isolated topologies. Theoretical description and experimental results are also presented.

A Coupled-Inductors Currenr-Doubler (CICD) topology is then presented to allow further output voltage step-down by coupled inductors and to reduce the secondary side current-doubler input current. This is followed by a presentation of a non-isolated Half-Bridge-Buck (HBB) topology, where CICD topology can be also used, resulting in advantages including larger output voltage step-down and better self current sharing, especially when compared to non-isolated, two-phase buck topology. Theoretical analysis and experimental results are presented.

The presentation of control methods and topology for isolated and non-isolated DC-DC converters is followed by initial candidate concepts and work for control and topology techniques as well as programmable digital control. Digital control is discussed as a candidate for future DC-DC converters, while digital system structure, advantages, disadvantages and initial experimental setup are presented also. Moreover, an initial concept for future work on digital control is discussed, namely, the Maximum Efficiency Point Tracking (MEPT) method, which can be used to optimize a switche's dead time

control issue by using adaptive control to achieve better efficiency and converter performance.

Finally, the work is summarized and concluded and future research directions are presented.

### ACKNOWLEDGMENTS

The author would like to express his sincere appreciation to his advisor, Professor Issa Batarseh, for his assistance and support and his efforts to plant the seeds of this work. His personality, directing experience and critical thinking were an example for the author to follow.

The author would like to thank members of the Power Electronics Laboratory at the University of Central Florida for their help, useful discussion and suggestions, including those who were at the Power Electronics Laboratory at the beginning of this work: Dr. Shiguo Luo, Dr. Huai Wei, Dr. Christopher Iannello, Dr. Guangyong Zhu, Dr. Wenkai Wu, Dr. Weihong Qiu and Dr. Peter Kornetzky, as well as those who are currently working with the author at the Power Electronics Laboratory: Dr. Hong Mao, Nattorn Pongratananukul, Jia Luo and Songquan Deng.

The author would like to express his appreciation to other members and colleagues at the Power Electronics Laboratory: Dr. Zaki Moussaoui, Dr. Wei Gu, Manasi Soundalgekar, Shilpa Kaluvala and the rest of the members.

Special thanks are also extended to this dissertation approval committee: Professor Issa Batarseh, Professor Wasfy Mikhael, Dr. Takis Kasparis, Dr. Thomas Wu, Dr. Christopher Iannello, and Professor Ram Mohapatra. The author is grateful to the University of Central Florida faculty and staff for their cooperation especially Dr. Jamal Nayfeh. Also, the author is grateful for his friends.

Finally, the author would like to express his undying love and gratitude to his mother, Nadia, and his father, Abdelmunem, whose love, encouragement and support have been the root of his success.

This work is supported partially by several agencies and companies including NSF, NASA STTR, ASTEC Power/Emerson, Intel and the University of Central Florida.

Jaber A. Abu Qahouq

October 2003

# TABLE OF CONTENTS

| LIST OF FIGURESxiv                                                          |

|-----------------------------------------------------------------------------|

| LIST OF TABLESxxiv                                                          |

| CHAPTER 11                                                                  |

| INTRODUCTION1                                                               |

| 1.1 Overview                                                                |

| 1.2 How High is High and How Low is Low: Demands, Growth and Roadmap2       |

| 1.3 Distributed Power Systems and the New Wave of On-Board DC-DC Converters |

|                                                                             |

| 1.4 Driving Market Applications and Research Driving Forces                 |

| CHAPTER 212                                                                 |

| DESIGN AND ANALYSIS OF ON-BOARD DC-DC CONVERTERS12                          |

| 2.1 Introduction                                                            |

| 2.2 Ideal DC-DC Buck Topology                                               |

| 2.3 Basic Design Equations and Considerations14                             |

| 2.4 Load Transients and Converter Response                                  |

| CHAPTER 3                                                                   |

| MULTIPHASE VOLTAGE-MODE HYSTERETIC CONTROLLED DC-DC                             |

|---------------------------------------------------------------------------------|

| CONVERTER WITH CURRENT SHARING                                                  |

| 3.1 Introduction                                                                |

| 3.2 Interleaving Versus High Switching Frequency and Smaller Output Inductor 26 |

| 3.3 The Voltage-Mode Hysteretic Control Concept                                 |

| 3.4 Multiphase Voltage-Mode Hysteretic Controlled DC-DC Converter with Current  |

| Sharing                                                                         |

| 3.5 Multiphase Voltage-Mode Hysteretic Control                                  |

| 3.6 Multiphase Voltage-Mode Hysteretic Control with Current Sharing             |

| 3.7 Method Generalization for "N" Interleaved Phases                            |

| 3.8 Theoretical Analysis47                                                      |

| 3.9 Simulation Results54                                                        |

| 3.10 Experimental Study                                                         |

| 3.11 Summary62                                                                  |

| CHAPTER 4                                                                       |

| REVIEW OF SELECTED ISOLATED TOPOLOGIES AND DUTY-CYCLE-SHIFTED                   |

|                                                                                 |

| CONTROLLED HALF-BRIDGE                                                          |

| 4.1 Introduction64                                                              |

| 4.2 Review of Selected Isolated DC-DC Converter Topologies                      |

| 4.3 Half-Bridge Topology's Two Conventional Control Schemes                     |

| 4.4 Duty-Cycle-Shifted Control for Half-Bridge72                                |

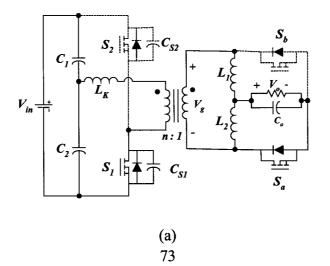

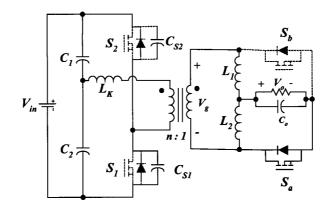

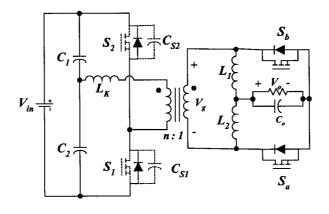

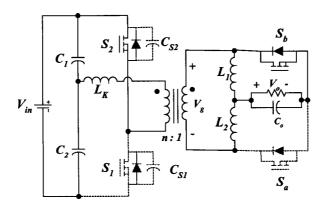

| 4.5 DCS-Controlled Half-Bridge Modes of Operation73                             |

| 4.6 Experimental Study77                                                        |

| 4.7 Summary                                                               |

|---------------------------------------------------------------------------|

| CHAPTER 5                                                                 |

| ALTERNATED DUTY-CYCLE CONTROL METHOD FOR HALF-BRIDGE DC-DC                |

| CONVERTER                                                                 |

| 5.1 Introduction                                                          |

| 5.2 Alternated Duty Cycle Control                                         |

| 5.3 Experimental Study91                                                  |

| 5.4 Summary94                                                             |

| CHAPTER 6                                                                 |

| INTERLEAVED CURRENT DOUBLERS WITH PARALLEL CONNECTED                      |

| TRANSFORMERS                                                              |

| 6.1 Introduction95                                                        |

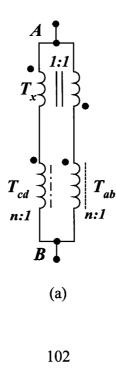

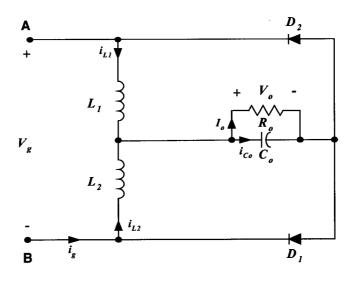

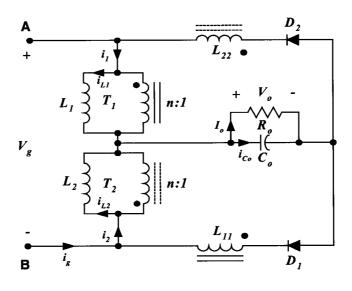

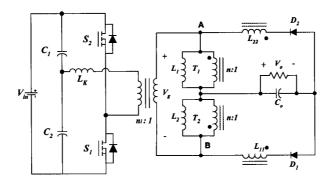

| 6.2 Transformer's Primary and Secondary Sides Connection Configurations96 |

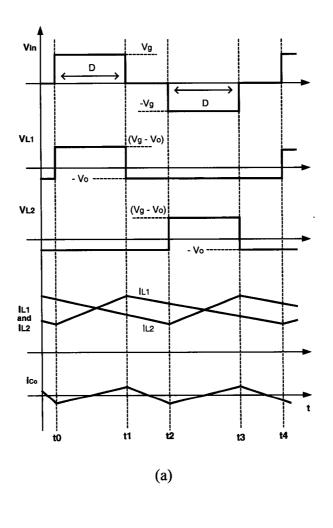

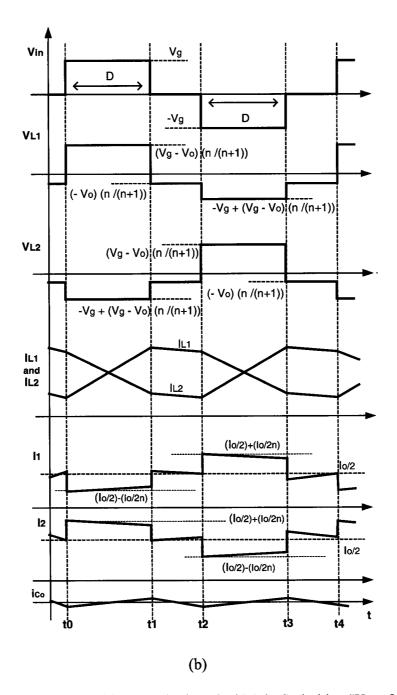

| 6.3 Topology Configuration97                                              |

| 6.4 Brief Theoretical Comparison101                                       |

| 6.5 Method Extension for More Interleaved Phases                          |

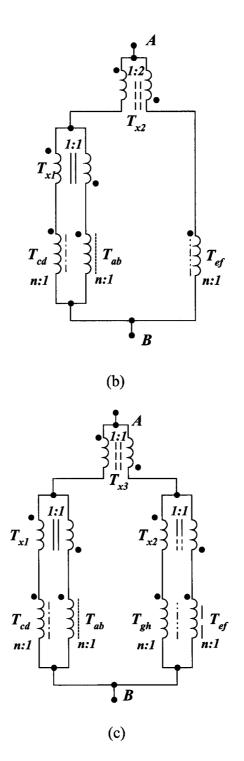

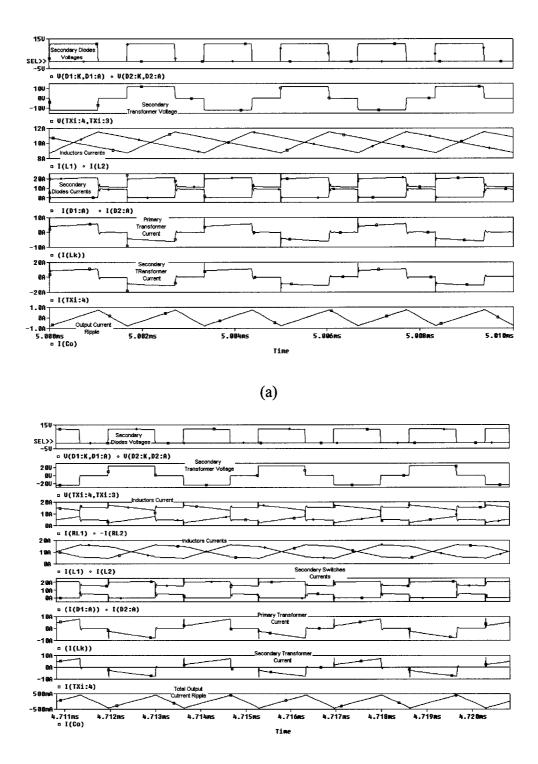

| 6.6 Simulation Results104                                                 |

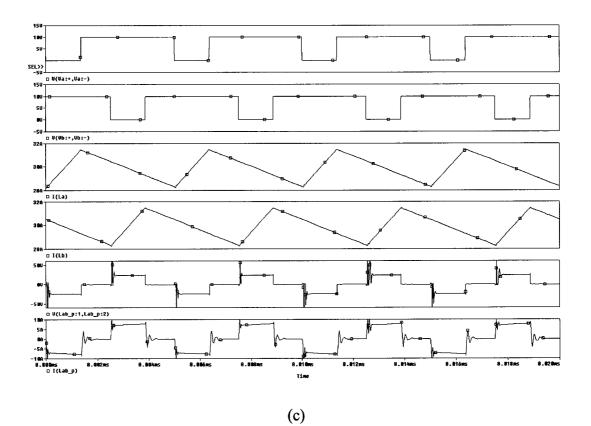

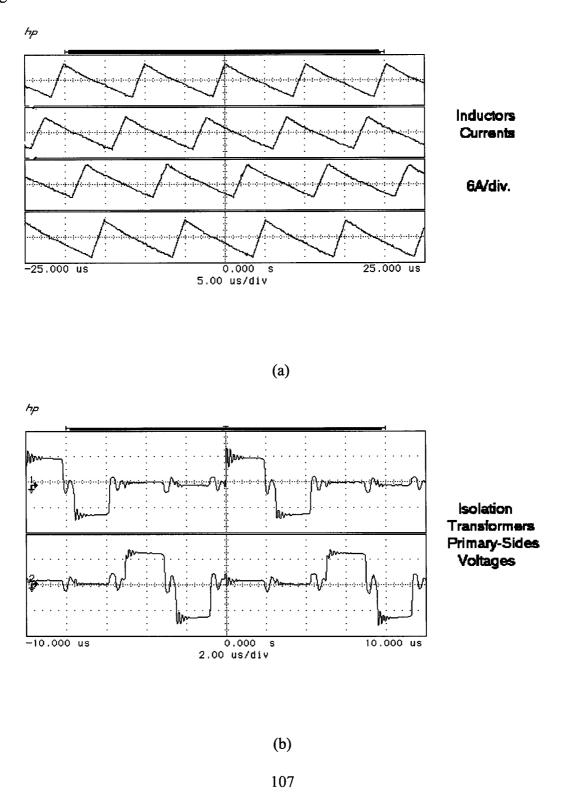

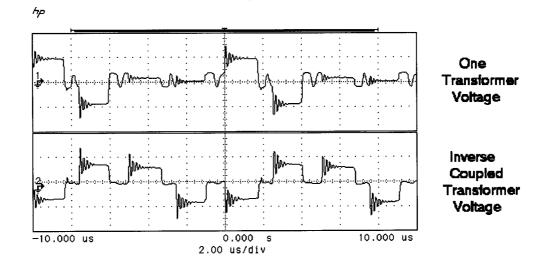

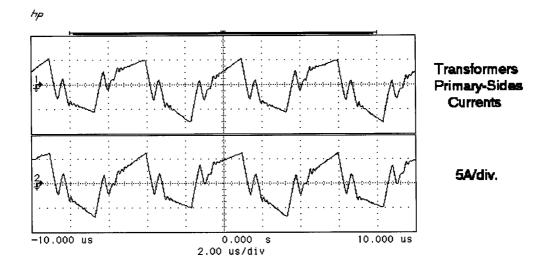

| 6.7 Experimental Work106                                                  |

| 6.8 Summary109                                                            |

| CHAPTER 7110                                                              |

| COUPLED-INDUCTORS CURRENT-DOUBLER DC-DC CONVERTER TOPOLOGY                |

|                                                                           |

| 7.1 Introduction                                              |

|---------------------------------------------------------------|

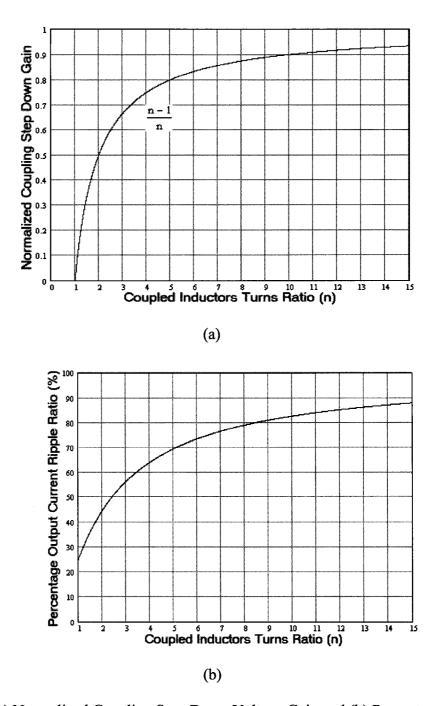

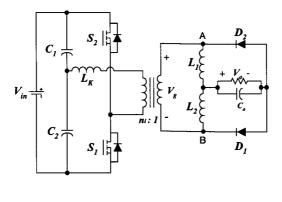

| 7.2 CICD Topology and Its Waveforms111                        |

| 7.3 Theoretical Analysis and Key Design Equations             |

| 7.4 Comparison Between the CICD and CCD Topologies and Design |

| Considerations119                                             |

| 7.5 Simulation Results120                                     |

| 7.6 Experimental Study124                                     |

| 7.7 Summary126                                                |

| CHAPTER 8128                                                  |

| NON-ISOLATED MULTIPHASE HALF-BRIDGE-BUCK TOPOLOGY WITH        |

| INHERENT CURRENT SHARING CAPABILITY AND SOFT SWITCHING        |

| 8.1 Introduction                                              |

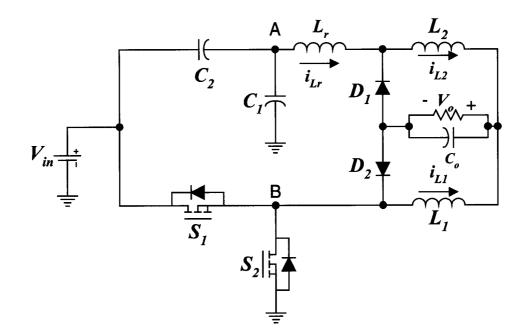

| 8.2 Topology and Possible Control Schemes                     |

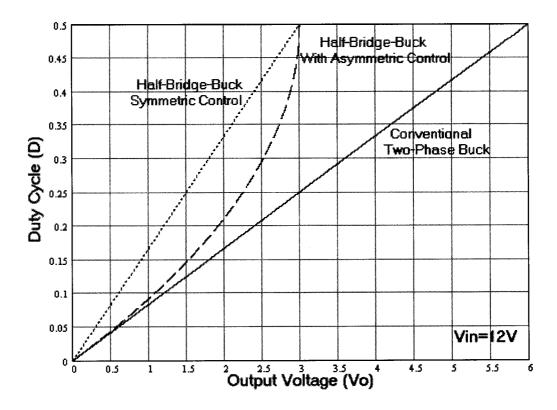

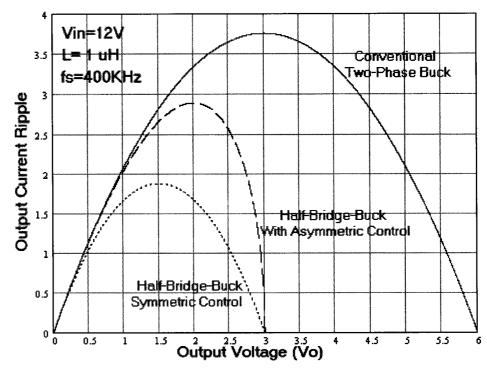

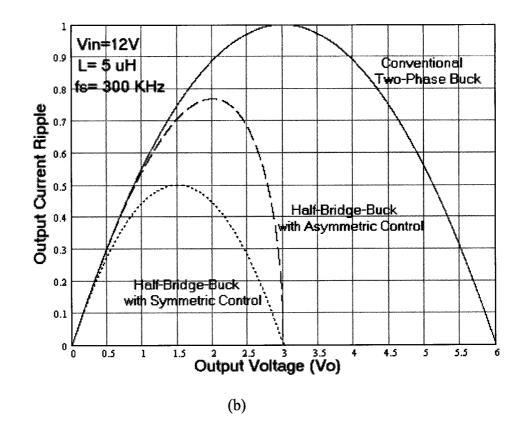

| 8.3 Topologies Comparison and Advantages132                   |

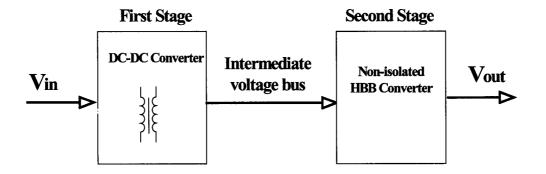

| 8.4 Two-Stage Approach for DC-DC Converters                   |

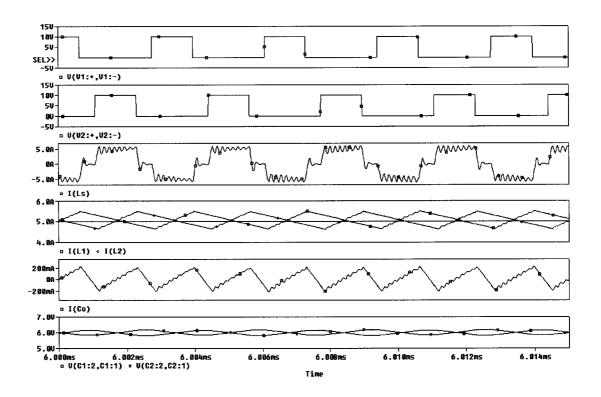

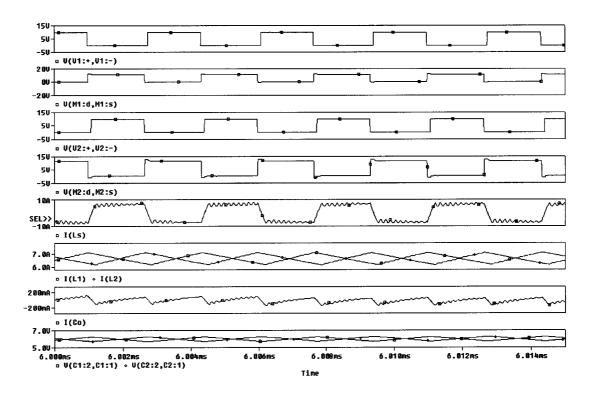

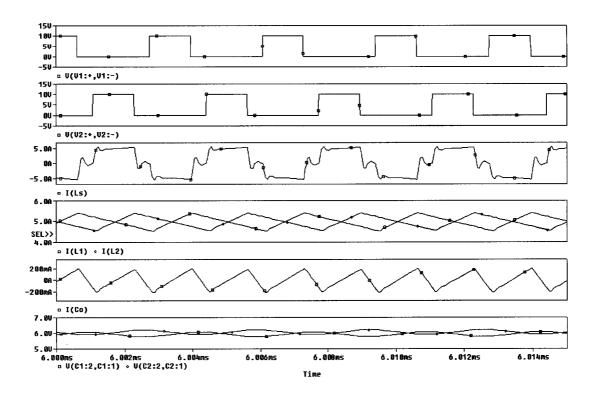

| 8.5 Simulation Results139                                     |

| 8.6 Experimental Study145                                     |

| 8.7 Summary152                                                |

| CHAPTER 9153                                                  |

| CONVERTER CONTROL TECHNIQUES AND DIGITAL CONTROL FOR FUTURE   |

| DC-DC CONVERTERS                                              |

| 9.1 Introduction                                              |

| 9.2 Closed Loop System154<br>xii                              |

| 9.3 Brief Review and Comparison of Control Techniques156                     |

|------------------------------------------------------------------------------|

| 9.4 A Look at Controller Sensed Signals161                                   |

| 9.5 Fast Transient Response Control Scheme                                   |

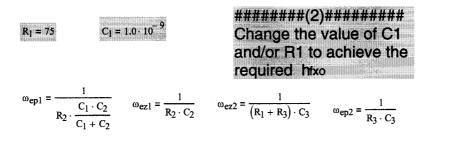

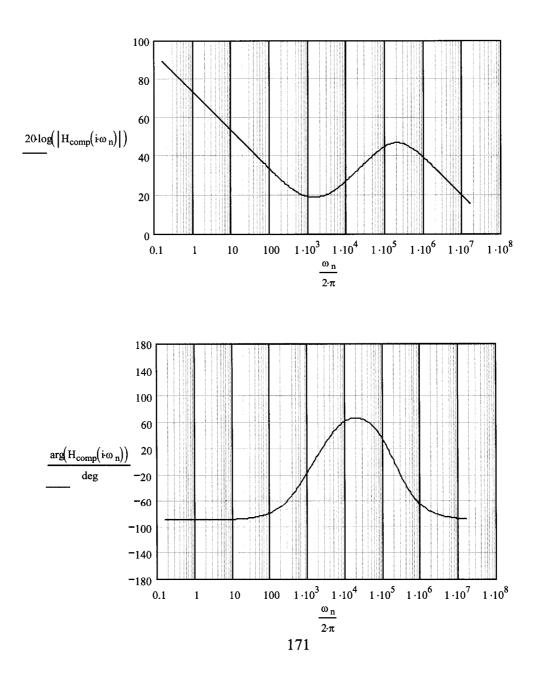

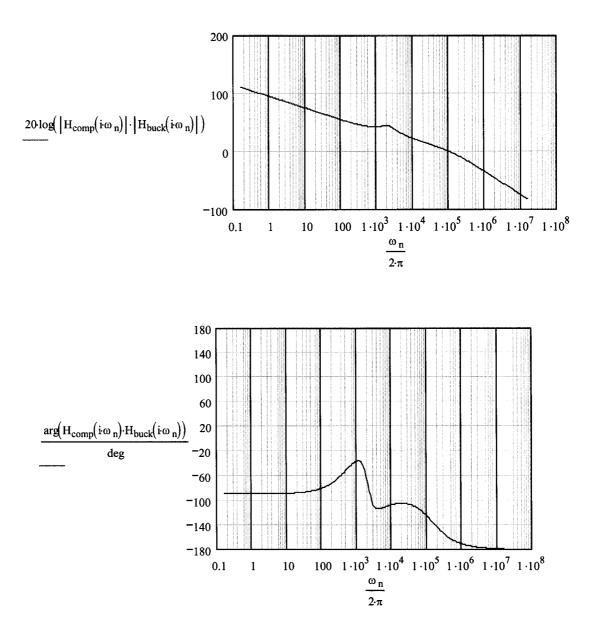

| 9.6 Design and Simulation Results164                                         |

| 9.7 A New Wave of Transient Compensator Converters                           |

| 9.8 Digital Control System                                                   |

| 9.9 Digital Control System Delays and Design                                 |

| 9.10 Initial Digital System Setup and DSP Controlled Multiphase Voltage-Mode |

| Hysteretic Converter                                                         |

| 9.11 Future Work to Be Continued on Digital Control                          |

| 9.12 Maximum Efficiency Point Tracking (MEPT) and Dead Time Control 189      |

| 9.13 Other Digital Control Algorithms                                        |

| 9.14 Summary                                                                 |

| CHAPTER 10 196                                                               |

| SUMMARY AND FUTURE RESEACH                                                   |

| REFERENCES                                                                   |

## LIST OF FIGURES

| Figure 1.1: Simplified General Power Delivery System Model                          |

|-------------------------------------------------------------------------------------|

| Figure 1.2: Example of Distributed Power System (DPS) Architecture Block Diagram 8  |

| Figure 2.1: (a) Ideal Buck topology, (b) Switches Drive and Output Inductor Current |

| Waveforms for CCM and DCM Operations and (c) Switches Drive and                     |

| Output Inductor Current Waveforms for QSW Buck15                                    |

| Figure 2.2: Buck Converter with Main Components Parasitics Consideration21          |

| Figure 2.3: Example of Step-Up Load Transient Output Current and Voltage Waveforms  |

|                                                                                     |

| Figure 2.4: Example of Step-Up Load Transient Output Current and Voltage Waveforms  |

| at Different $L_o/C_o$ Ratios                                                       |

| Figure 3.1: Four Interleaved (Multi-Phase) Synchronous Buck Converters27            |

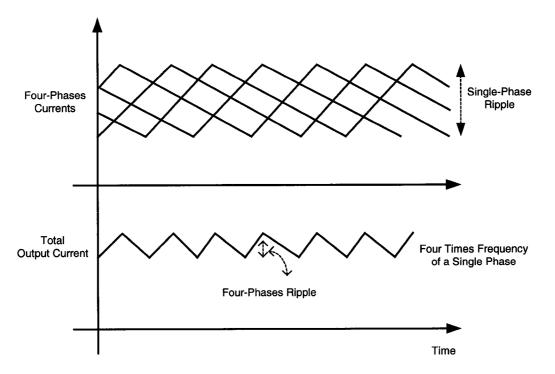

| Figure 3.2: Main Waveforms for Four Interleaved Buck Converters (90° Phase Shift    |

| Between the Phases)                                                                 |

| Figure 3.3: A Simplified Schematics and Waveforms for a Voltage-Mode Hysteretic-    |

| Controlled Buck Converter                                                           |

| Figure 3.4: Actual Output Voltage Ripple Waveforms for a Voltage-Mode Hysteretic-   |

| Controlled Converter                                                                |

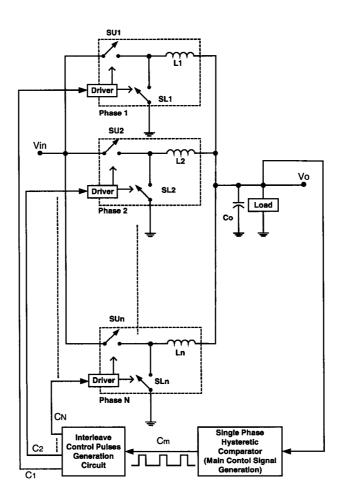

| Figure 3.5: Block Diagram of N Interleaved Buck Converters with Voltage-Mode      |

|-----------------------------------------------------------------------------------|

| Hysteretic Control                                                                |

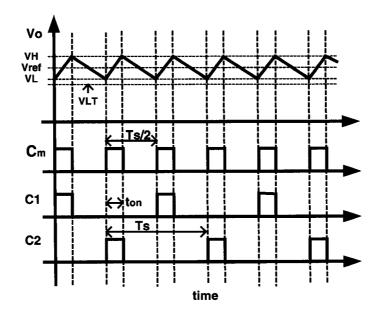

| Figure 3.6: Example of Control Signals for Two Interleaved Phases (N=2)           |

| Figure 3.7: Multiphase Logic Circuits to Generate Multiphase Control Signals:     |

| (a) Two Phase and (b) Four Phase                                                  |

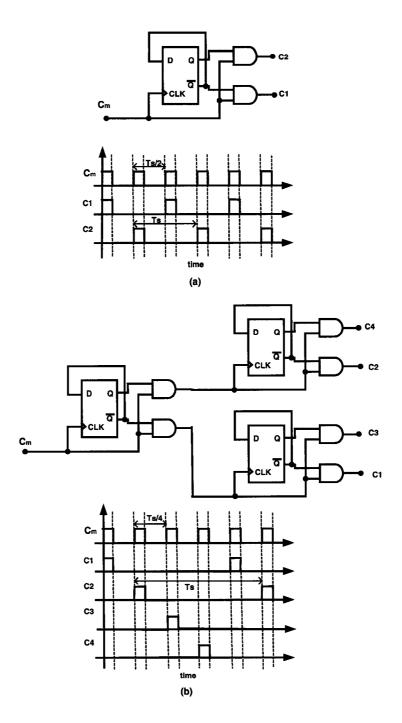

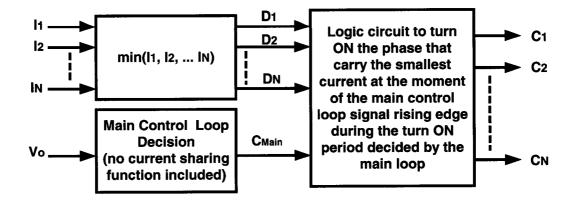

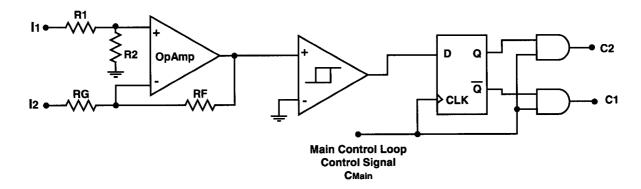

| Figure 3.8: Basic Block Diagram of the Proposed Current Sharing Method40          |

| Figure 3.9: Current Sharing Part for Two-Phase Buck DC-DC Converter40             |

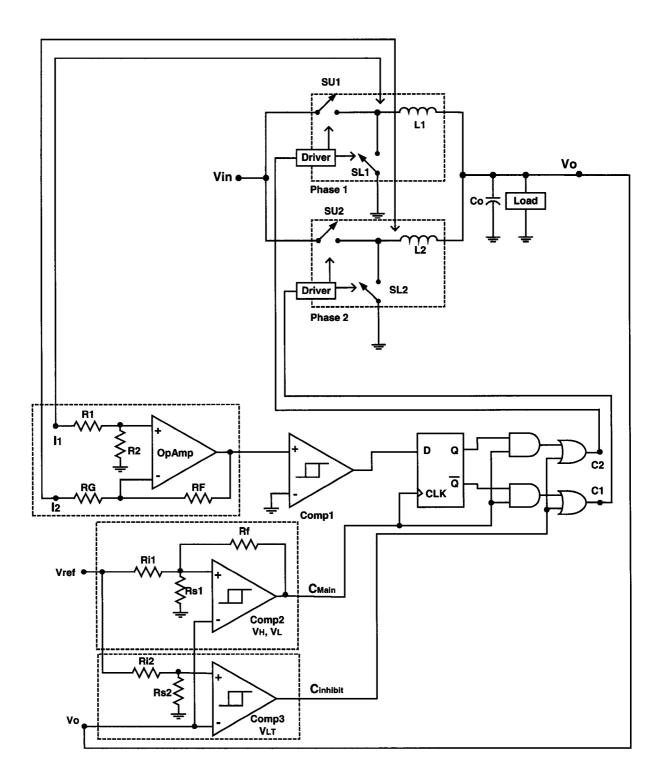

| Figure 3.10: Proposed Control Method Applied to a Two-Phase Converter             |

| Figure 3.11: General Waveforms Sample for the Current Sharing Process             |

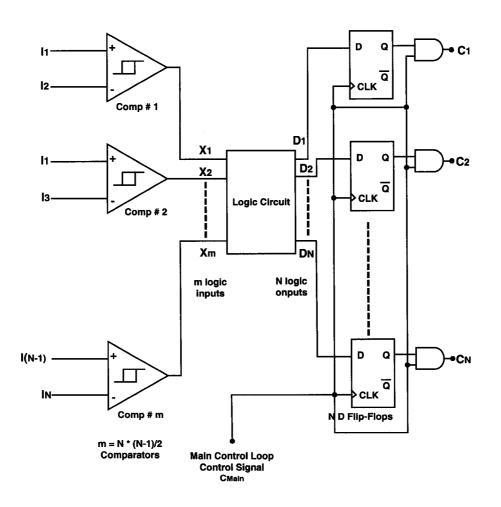

| Figure 3.12: Basic Controller Generalized Diagram for N Multiphase Voltage-Mode   |

| Hysteretic Controlled Current-Shared Converters                                   |

| Figure 3.13: Possible Arrangement for Current Sharing Circuit                     |

| Figure 3.14: Output Voltage with Its Ripple when the Equivalent Series Resistance |

| (ESR), the Equivalent Series Inductance (ESL) and Feedback Loop Delay             |

| Time $(t_{del})$ are Considered                                                   |

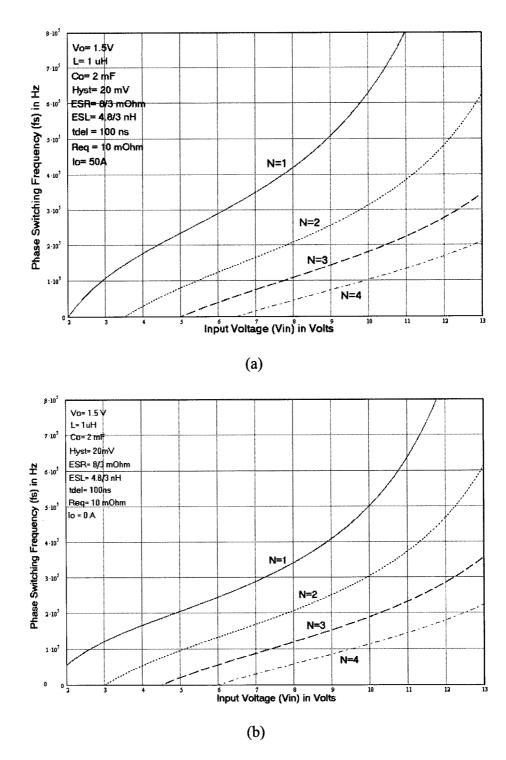

| Figure 3.15: Theoretical Phase Switching Frequency Versus Input Voltage for N     |

| Interleaved Phases at: (a) Full load Condition and (b) No Load Condition 52       |

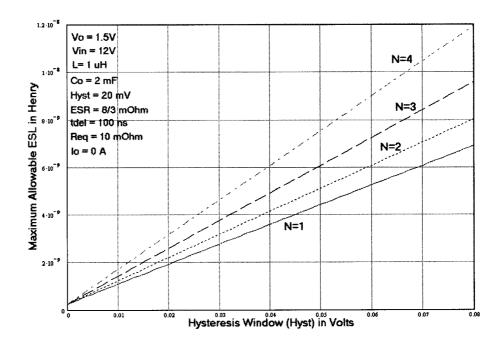

| Figure 3.16: Maximum Allowable ESL Versus Hysteresis Window for N Interleaved     |

| Phases54                                                                          |

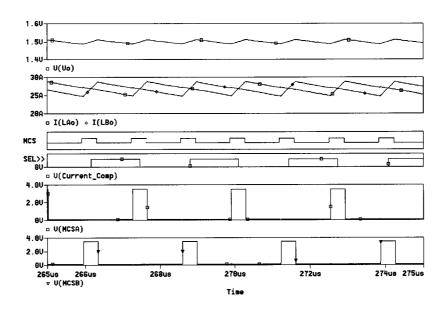

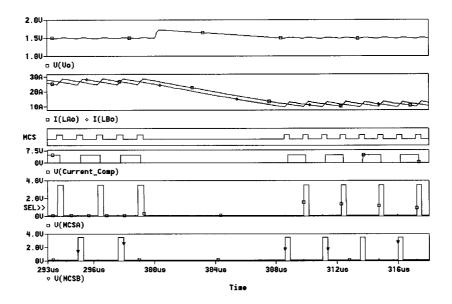

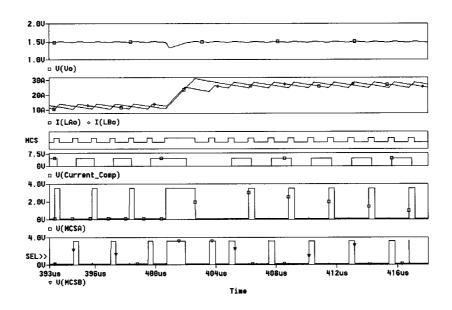

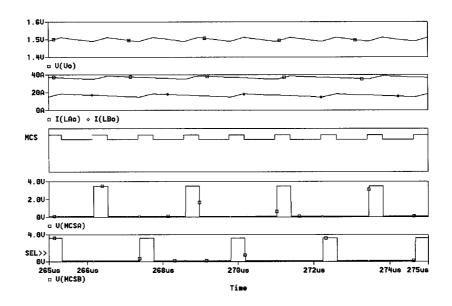

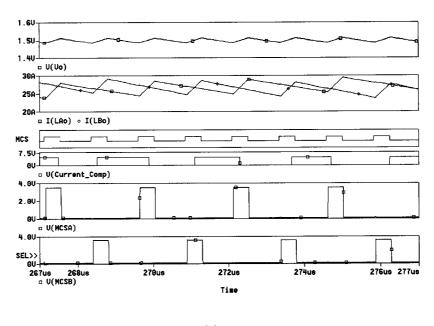

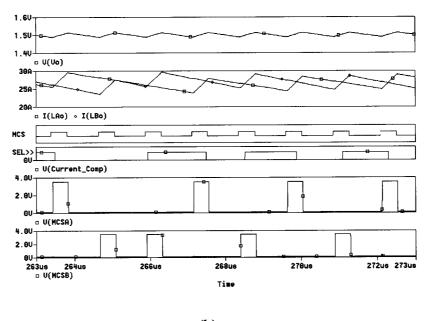

| Figure 3.17: Simulation Results in Steady-State Condition                         |

| Figure 3.18: Simulation Results in a High-to-Low Load Transient Condition56       |

| Figure 3.19: Simulation Results in a Low-to-High Load Transient Condition         |

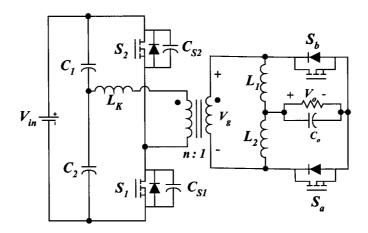

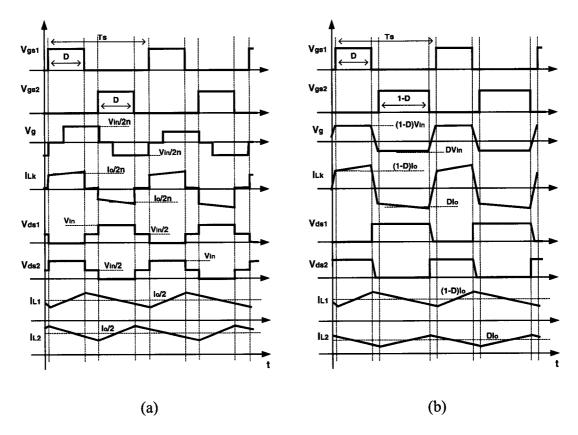

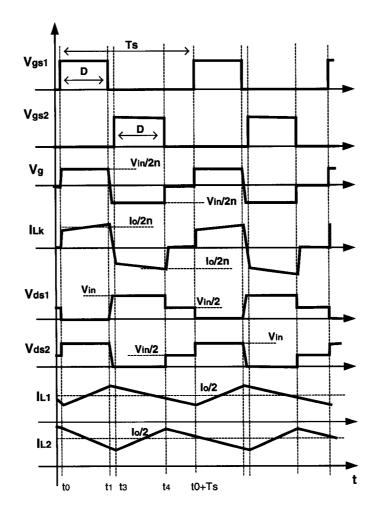

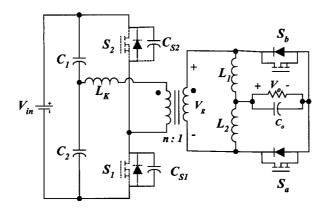

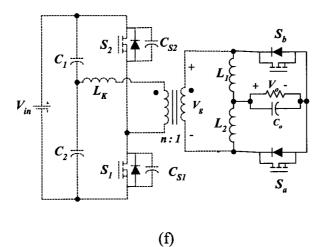

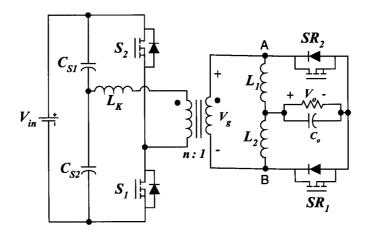

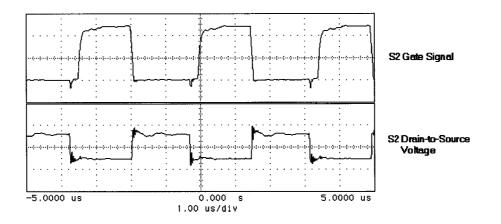

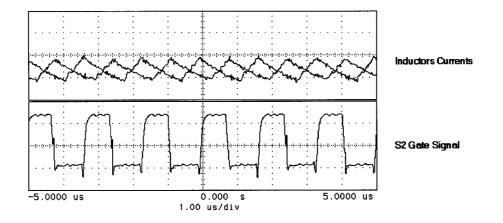

| Figure 4.4: Half-Bridge Topology with Current-Doubler Secondary Side                         | ) |

|----------------------------------------------------------------------------------------------|---|

| Figure 4.5: Main Switching Waveforms of Half-Bridge Topology of Figure 4.4 with: (a          | ) |

| Symmetric Control Scheme and (b) Asymmetric Control Scheme                                   | ) |

| Figure 4.6: Main Switching Waveforms of Half-Bridge Topology with DCS Control72              | 2 |

| Figure 4.7: DCS-Controlled Half-Bridge Modes of Operation Equivalent Circuits: (a            | ) |

| through (f) Equivalent Circuits for Modes 1 through 6                                        | 5 |

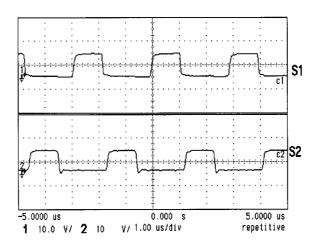

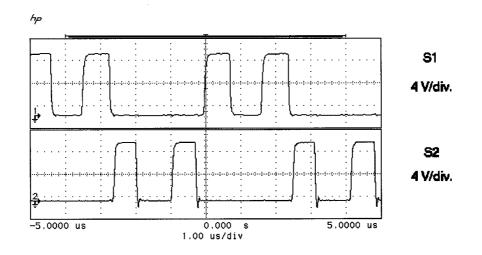

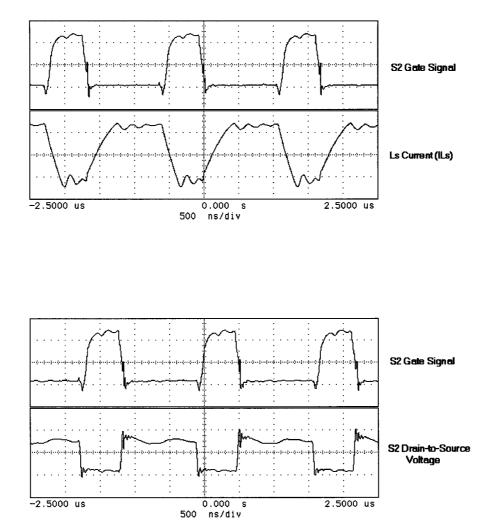

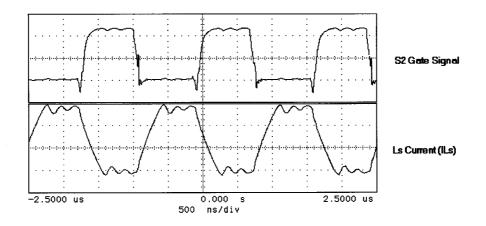

| Figure 4.8: Gate Drive Signals of $S_1$ and $S_2$                                            | ) |

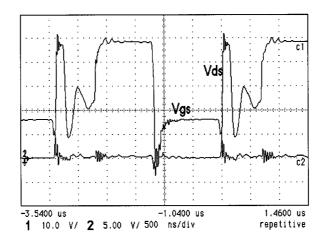

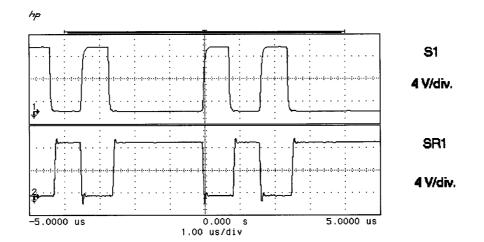

| Figure 4.9: Zero-Voltage-Switching of $S_2$ : Drain-to-Source Voltage of $S_2$ with Its Gate | e |

| Drive Signal Shown                                                                           | ) |

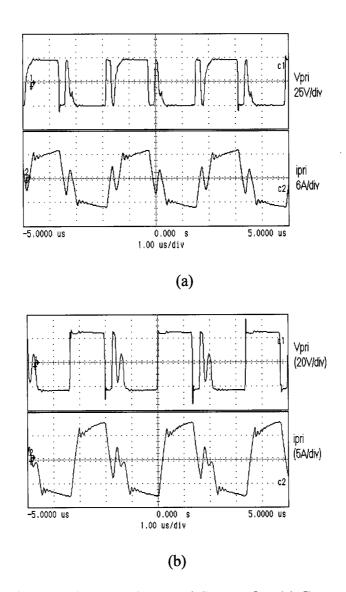

| Figure 4.10: Transformer Primary Voltage and Current for: (a) Conventional Symmetrie         | С |

| Control and (b) Duty-Cycle-Shifted Control                                                   | ) |

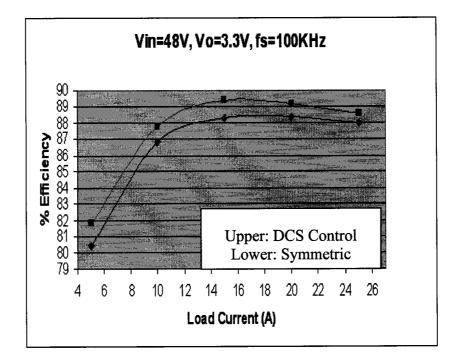

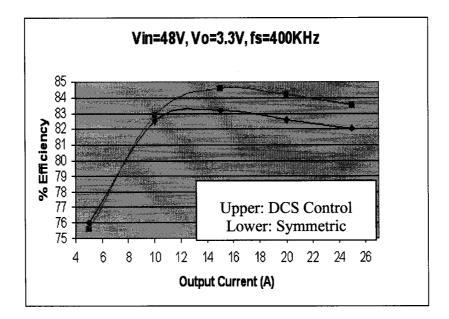

| Figure 4.11: Efficiency Comparison at 100KHz8                                                | 1 |

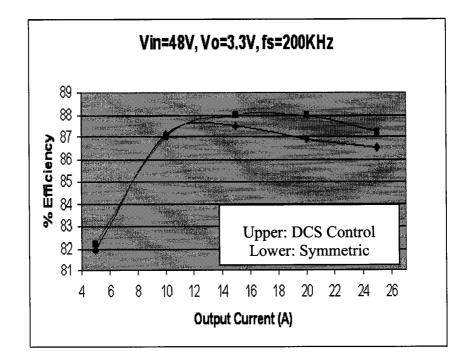

| Figure 4.12: Efficiency Comparison at 200KHz                                                 | 1 |

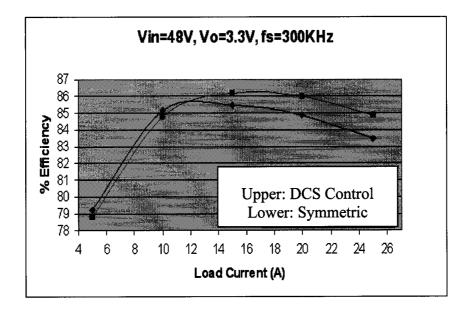

| Figure 4.13: Efficiency Comparison at 300KHz82                                               | 2 |

| Figure 4.14: Efficiency Comparison at 400KHz82                                               | 2 |

| Figure 5.1: Half-Bridge Topology with Current Doubler Secondary Side                         | 5 |

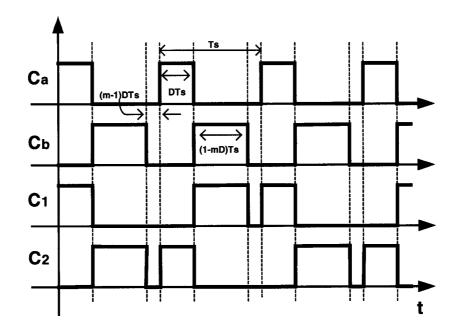

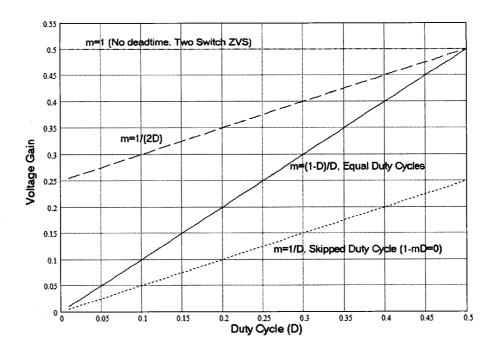

| Figure 5.2: Generalized Alternated Duty Cycle (ADC) Control Waveforms                        | 7 |

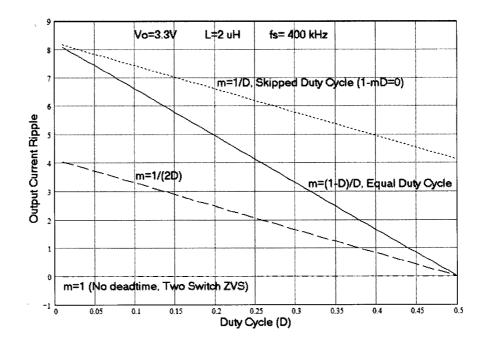

| Figure 5.3: Voltage Gain Versus Duty Cycle for Different Values of m                         | 9 |

| Figure 5.4: Output Current Ripple versus Duty Cycle at Different m Values for $V_o = 3.3V$   | , |

| $L = 2\mu H$ and $f_s = 400 kHz$                                                             | 0 |

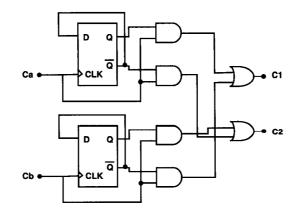

| Figure 5.5: Simple ADC Signals Generation Circuitry Implementation90                         | 0 |

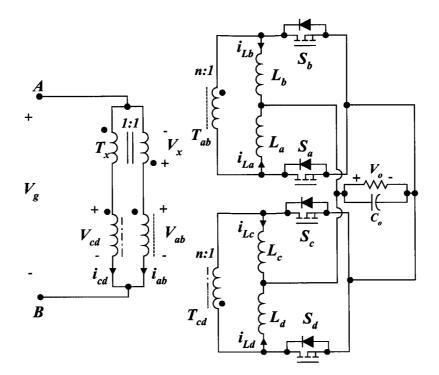

- Figure 6.2: Two Interleaved Current Doublers where Any Primary Side can Be Used Including Half-Bridge, Phase-Shifted Full-Bridge and Active-Clamp....... 100

### xviii

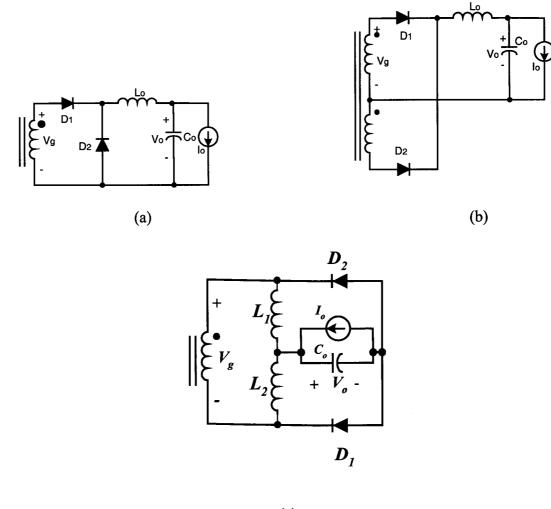

| Figure 7.1: Current-D | Ooubler Topologies:   | (a) Conventional | Current-Doubler (CCD) and |

|-----------------------|-----------------------|------------------|---------------------------|

| (b) Couple            | ed- Inductor Current- | Doubler (CICD)   |                           |

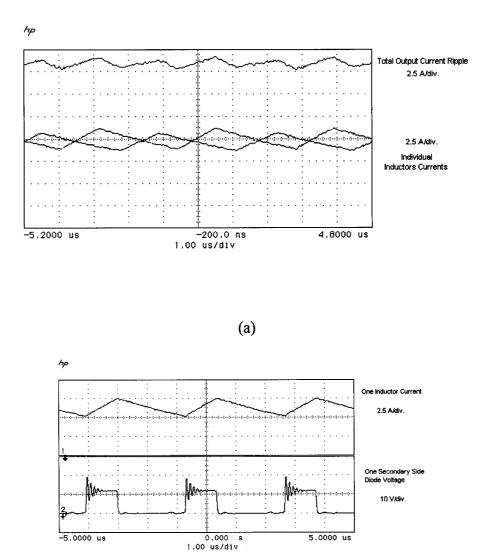

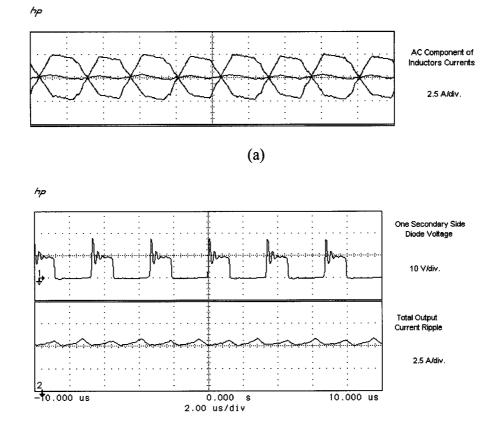

- Figure 7.6: Experimental Waveforms with the CCD Topology: (a) Inductors and Output Currents Waveforms and (b) One Inductor Current and One Secondary Side

Diode Voltage Waveforms......125

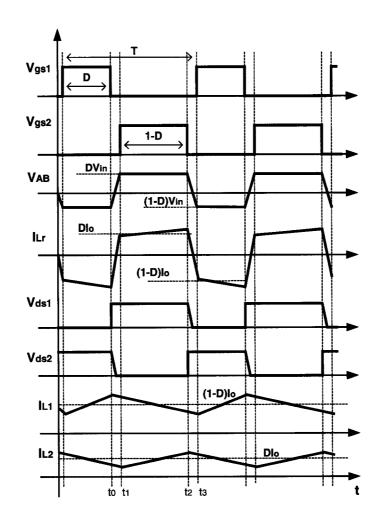

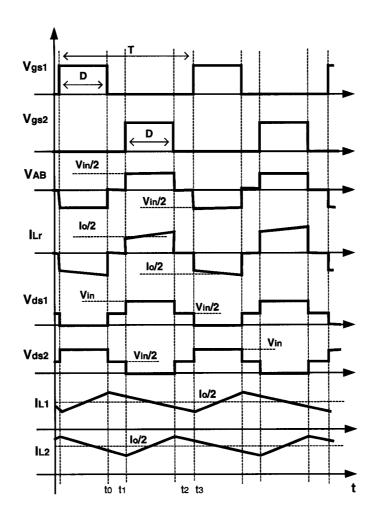

- Figure 8.3: Main Switching Waveforms of Figure 8.1 when Symmetric Control Is Used

| Figure 8.5: Output Current Ripple Comparison136                                |

|--------------------------------------------------------------------------------|

| Figure 8.6: Two-Stage Approach for High Step-Down Fast Transient Converter 139 |

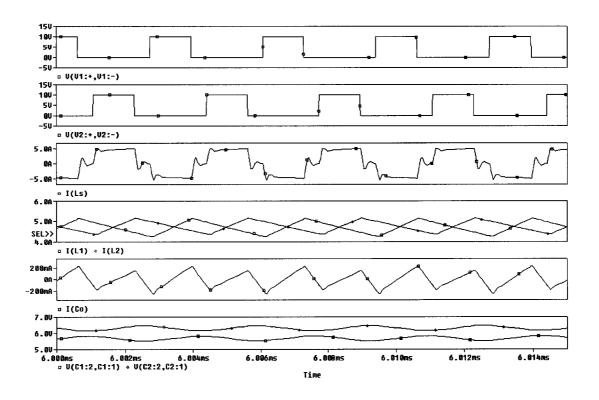

| Figure 8.7: HBB with Symmetric Control and Symmetric Traces and Components     |

| Simulation Results140                                                          |

| Figure 8.8: HBB with Symmetric Control and Symmetric Traces and Components     |

| Simulation Results with Soft Switching141                                      |

| Figure 8.9: HBB with Symmetric Control and Asymmetric Traces and Components    |

| Simulation Results when the Inductors Traces Resistances Were Deliberately     |

| Made Different By $10m\Omega$                                                  |

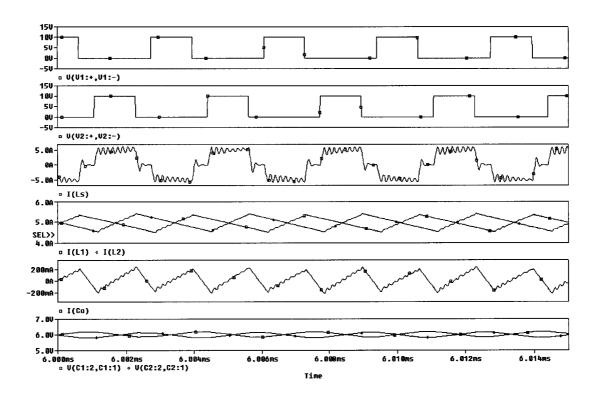

| Figure 8.10: HBB with Symmetric Control and Asymmetric Traces and Components   |

| Simulation Results when the Inductors Traces Resistances Were Deliberately     |

| Made Different By $50m\Omega$                                                  |

| Figure 8.11: HBB with Symmetric Control and Asymmetric Traces and Components   |

| Simulation Results when the Diodes Traces Resistances Were Deliberately        |

| Made Different By 10mΩ144                                                      |

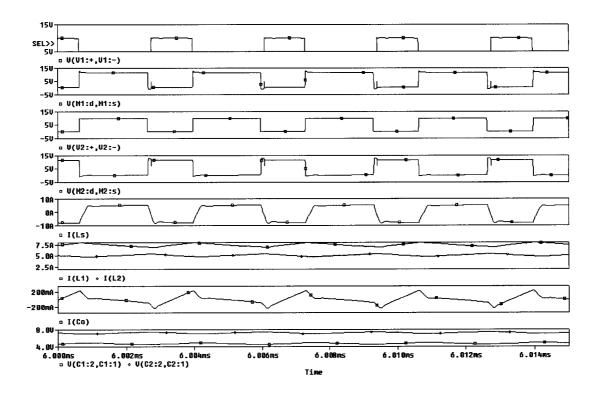

| Figure 8.12: HBB with Asymmetric Control Simulation Results145                 |

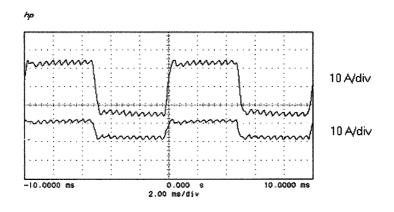

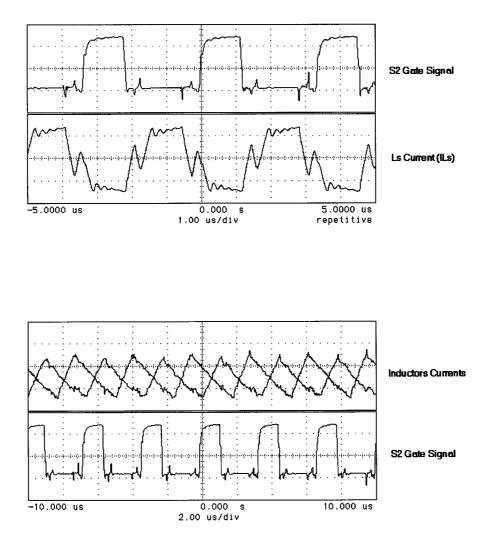

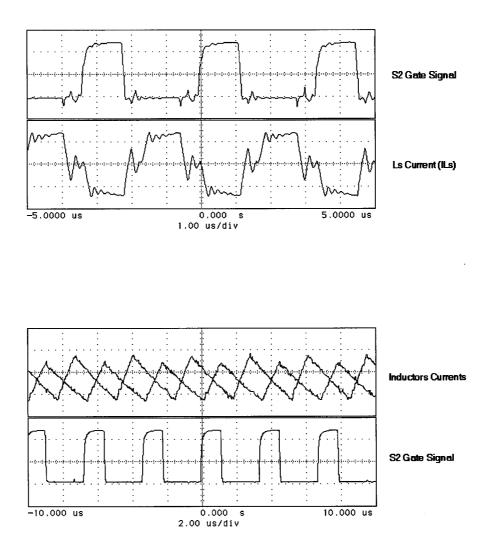

| Figure 8.13: HBB Experimental Waveforms with Symmetric Control and Symmetric   |

| Traces                                                                         |

| Figure 8.14: HBB Experimental Waveforms with Symmetric Control and             |

| $10m\Omega$ Asymmetry in the Inductors Traces                                  |

| Figure 8.15: HBB Experimental Waveforms with Symmetric Control and             |

| $10m\Omega$ Asymmetry in the $D_1$ and $D_2$ Traces                            |

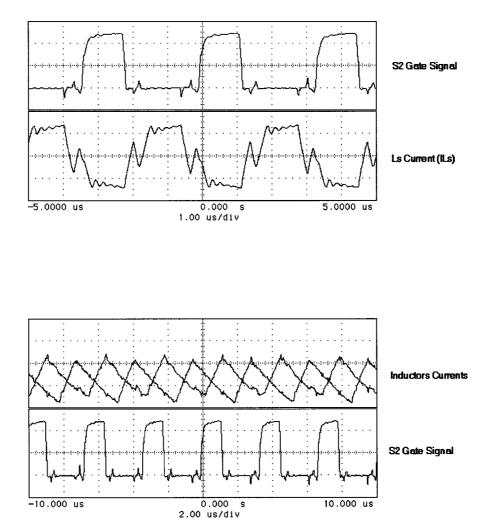

| Figure 8.16: HBB Experimental Waveforms with Asymmetric Control at Soft-Switching      |

|----------------------------------------------------------------------------------------|

| Condition at D=0.35                                                                    |

| Figure 8.17: HBB Experimental Waveforms with Asymmetric Control at Soft-Switching      |

| Condition at D=0.48152                                                                 |

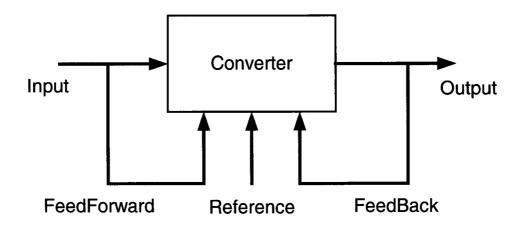

| Figure 9.1: General Basic Block Diagram for A Controlled Converter System              |

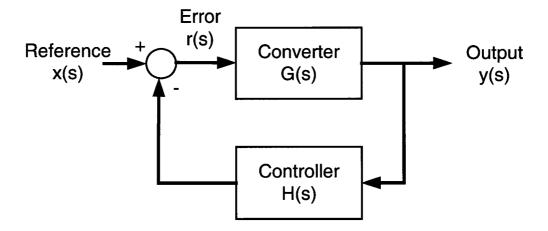

| Figure 9.2: A Block Diagram of a Negative Feedback Converter System with a Single      |

| Feedback Loop155                                                                       |

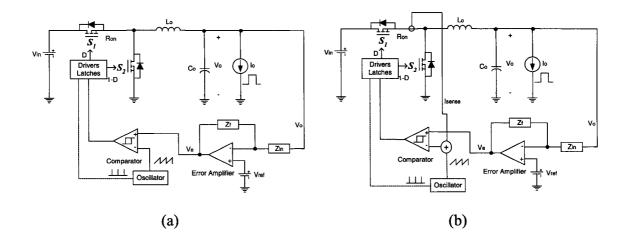

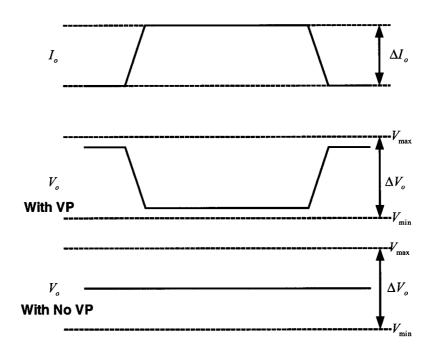

| Figure 9.3: Simplified Circuitries for Some Control Methods Applied to a Single Phase  |

| Buck Converter: (a) Voltage-Mode Control, (b) Peak-Current Mode Control,               |

| (c) Average-Current Mode Control, (d) Voltage Mode Hysteretic Control and              |

| (e) $V^2$ Control                                                                      |

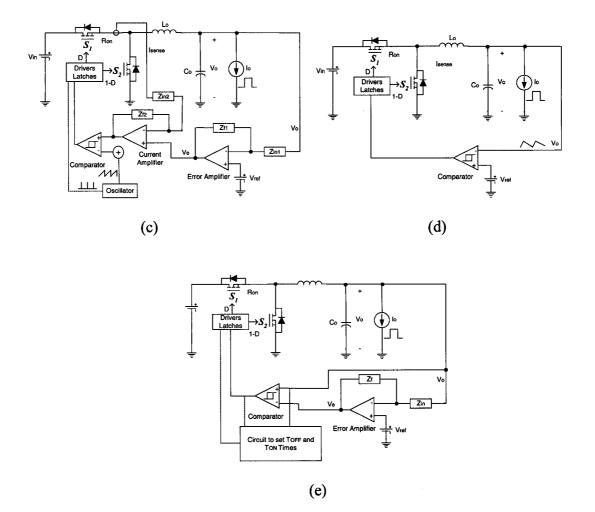

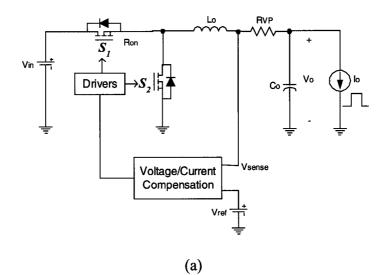

| Figure 9.4: The Idea of Voltage Positioning Control Technique159                       |

| Figure 9.5: Voltage Positioning Implementations: (a) Passive Voltage Positioning (PVP) |

| and (b) Active Voltage Positioning (AVP)160                                            |

| Figure 9.6: Converter Voltages and Current Varying During Load Transients              |

| Figure 9.7: Basic Schematics for the $v_c i_c$ Presented Method                        |

| Figure 9.8: Schematics of the Voltage-Mode Closed Loop Buck Converter with 2-Poles     |

| 2-Zeros Compensator166                                                                 |

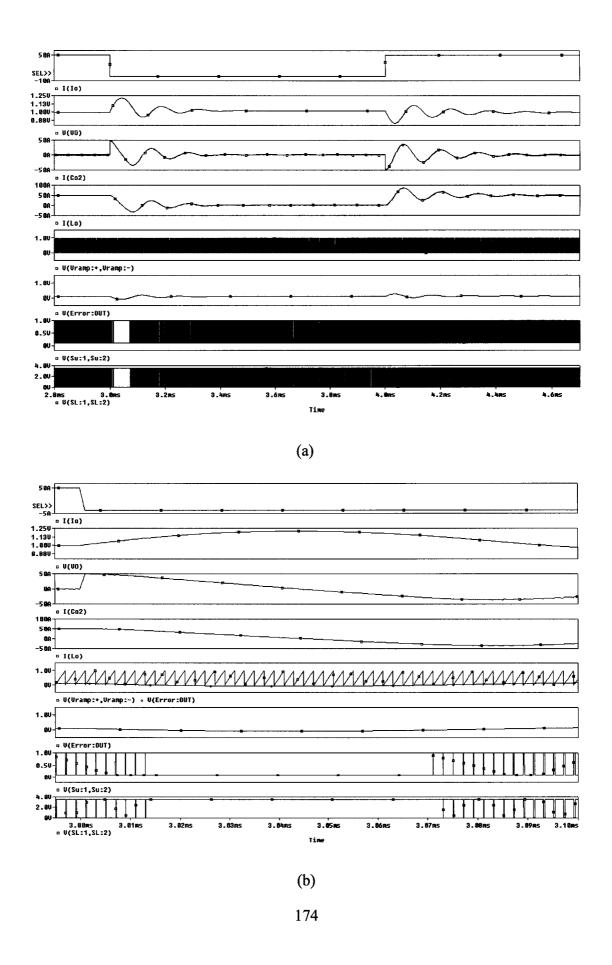

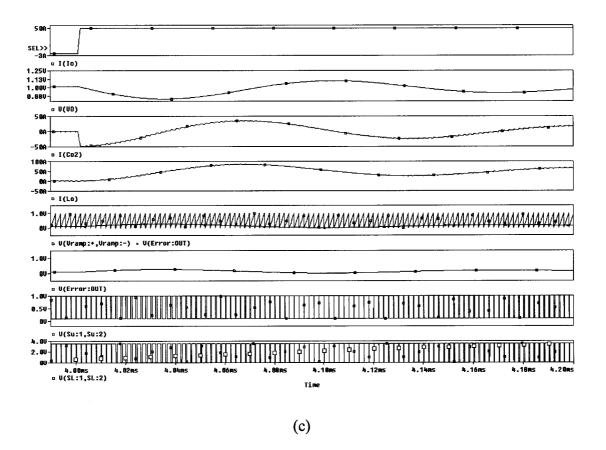

| Figure 9.9: Simulation Results for Voltage-Mode Controlled Buck with the Designed 2-   |

| Poles 2-Zeros Compensator Without Introducing the Capacitor Current                    |

| Signal: (a) Waveforms During Load Step-Down and Step-Up Transients                     |

| $(50A/\mu s)$ , (b) Zoom on Waveforms During Load Step-Down (213mV                     |

| Op (18811) Output Voltage Deviation)                                                   |

|----------------------------------------------------------------------------------------|

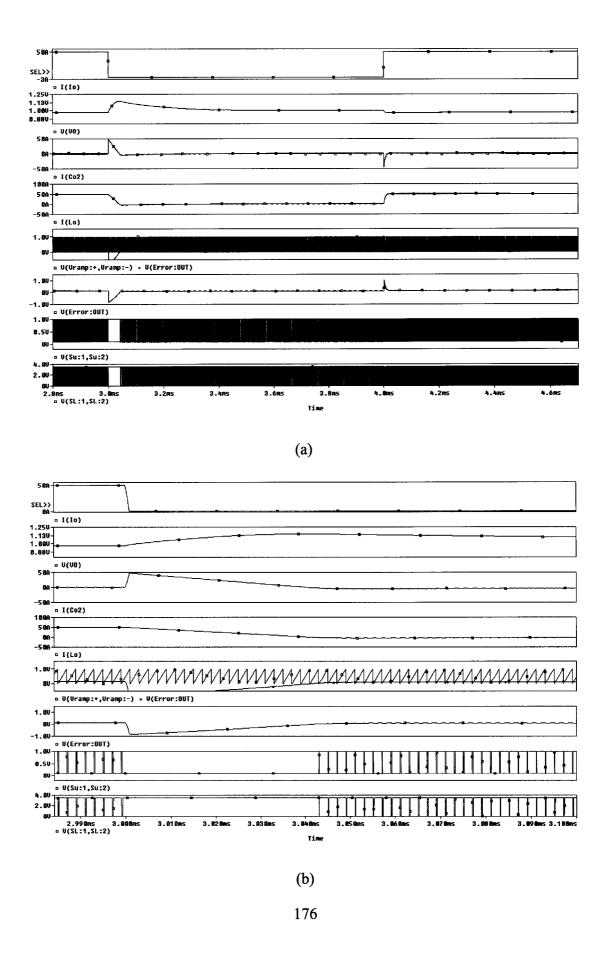

| Figure 9.10: Simulation Results for Voltage-Mode Controlled Buck with the Designed 2-  |

| Poles 2-Zeros Compensator with Introducing the Capacitor Current Signal                |

| and Added Extra 100ns Delay Time to Account for the Extra Summing                      |

| Amplifier Delay: (a) Waveforms During Load Step-Down and Step-Up                       |

| Transients (50 $A/\mu s$ ), (b) Zoom on Waveforms During Load Step-Down                |

| (170mV) Output Voltage Deviation) and (c) Zoom on Waveforms During                     |

| Load Step-Up (40mV Output Voltage Deviation)177                                        |

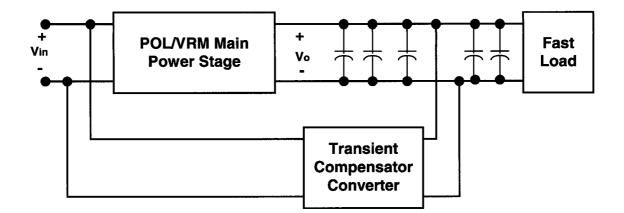

| Figure 9.11: A General Block Diagram With a Transient Current Compensator Used in      |

| Parallel with the Converter's Load179                                                  |

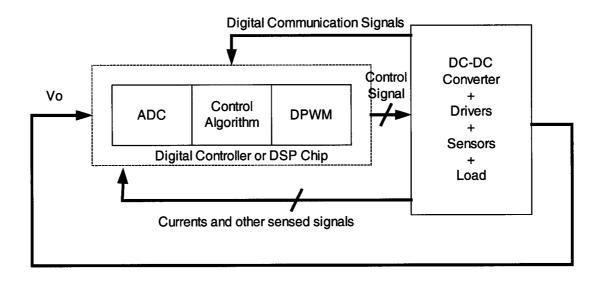

| Figure 9.12: A General Block Diagram Digital Controller System                         |

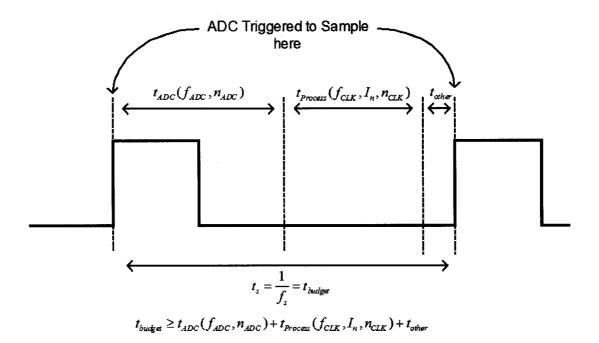

| Figure 9.13: Time Delay Budget Calculations as a Function of the DSP System Delay      |

| Parameters183                                                                          |

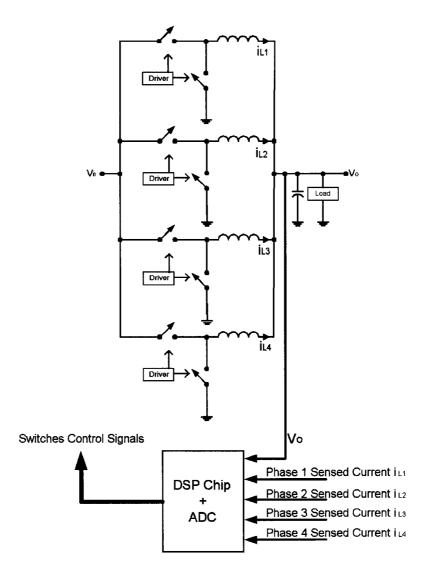

| Figure 9.14: Block Diagram of Four-Phase Voltage-Mode Hysteretic-Controlled            |

| Interleaved Converters with DSP Control                                                |

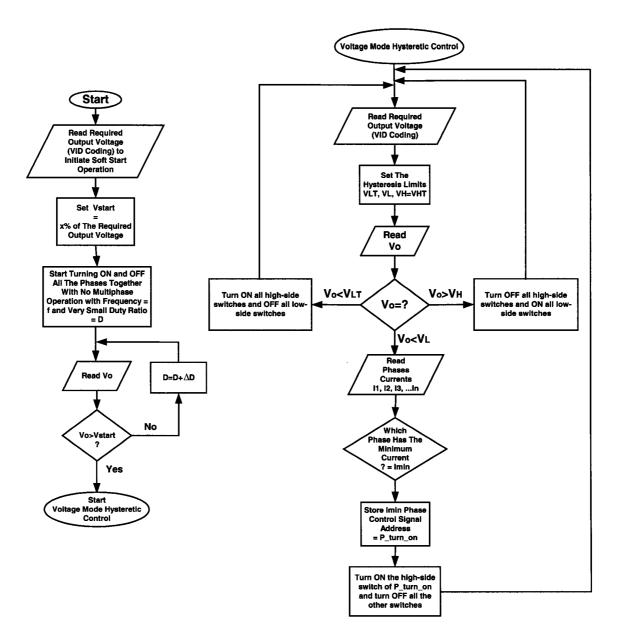

| Figure 9.15: DSP Chip Program Flowchart                                                |

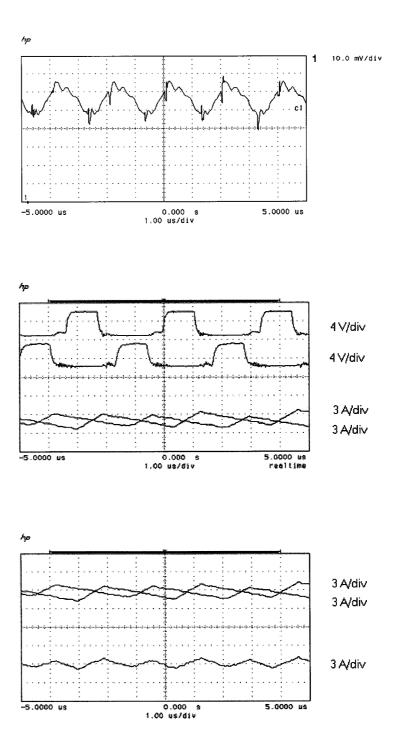

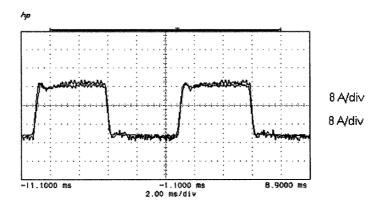

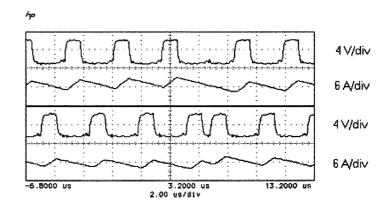

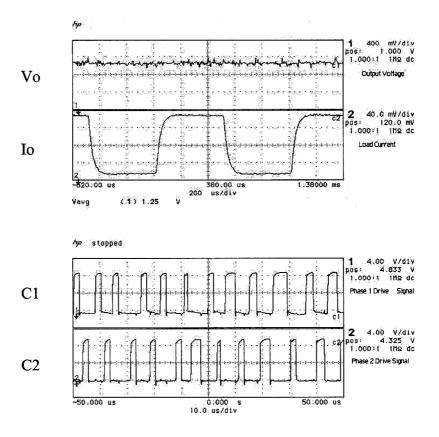

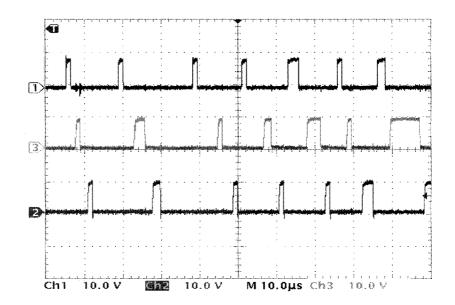

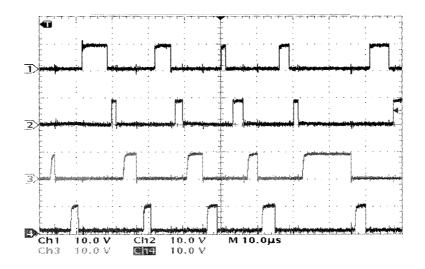

| Figure 9.16: Experimental Results for Two-Phase Power Stage                            |

| Figure 9.17: Experimental Results for Three-Phase Power Stage                          |

| Figure 9.18: Experimental Results for Four-Phase Power Stage                           |

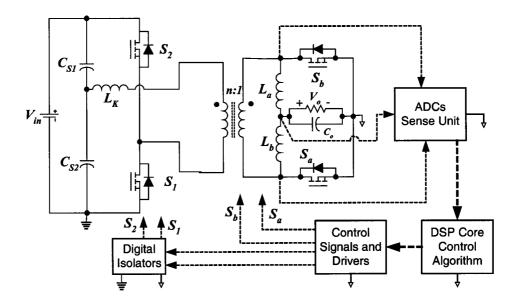

| Figure 9.19: Isolated Half-Bridge Converter with Secondary-Side Digital Control Scheme |

|                                                                                        |

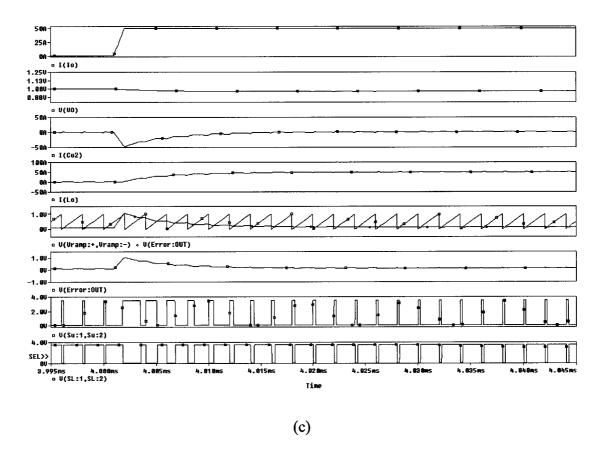

Output Voltage Deviation) and (c) Zoom on Waveforms During Load Step-

Up (188mV Output Voltage Deviation)......175

xxii

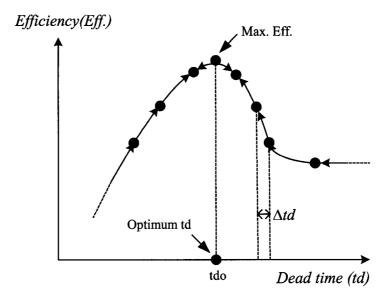

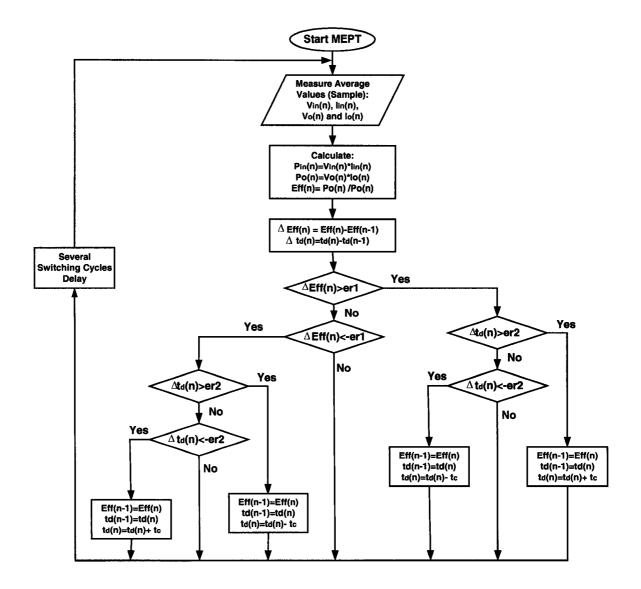

| Figure 9.20: Efficiency Versus Dead Time Curve that Presents How MEPT Can Be Used |

|-----------------------------------------------------------------------------------|

| to Optimize Dead Time Control191                                                  |

| Figure 9.21: One Possible MEPT DSP Program Algorithm for Dead Time Optimization   |

|                                                                                   |

## LIST OF TABLES

| Table | 1.1: E | xample Sp   | ecifications for l | Intel M  | icrop | processors Ov | ver the Past Few ` | Years 3  |

|-------|--------|-------------|--------------------|----------|-------|---------------|--------------------|----------|

| Table | 1.2: E | xample Sp   | ecifications fron  | n the I7 | rrs-  | 1999 Roadm    | ap                 | 4        |

| Table | 1.3:   | Example     | Specifications     | from     | the   | 2000/2001     | Semiconductor      | Industry |

|       |        | Association | n (SIA) Roadma     | p Sum    | mary  |               |                    | 4        |

## **CHAPTER 1**

## INTRODUCTION

### 1.1 Overview

Over the last few years, and at a fast pace, many DC loads powering requirements have become increasingly stringent [1-31]. These loads are mainly Digital Signal Processing (DSP) Integrated Circuits (ICs), including those used in communication systems and computers' microprocessors. On one hand, such loads, especially microprocessors, are becoming current hungry, while more functions are integrated in these ICs, which means larger number of transistors. On the other hand, their operating voltages are becoming much lower as the IC integration density increases. Moreover, the speed of these ICs is dramatically increasing, which causes the slew rate (current step change per unit time) of supply current to increase, causing larger supply voltages deviation during these transients at the same time where lower required supply voltages become smaller, and hence, the allowed deviation becomes tighter.

As a result, the steady state and dynamic requirements are becoming stricter, and the dynamic power dissipation reduction becomes important, which makes the power supply design process a difficult task. Moreover, these requirements, i.e., higher currents, lower voltages, lower allowed voltage deviation and faster current slew rate, can no longer be satisfied from the centralized power supply.

In addition, the required power/current density (smaller size) is continuously increasing, and therefore thermal problems arise, resulting in a high converter efficiency requirement.

In this chapter, powering requirements specifications and issues will be discussed.

### 1.2 How High is High and How Low is Low: Demands, Growth and Roadmap

In 1995, shipments of the 3.3V microprocessor and memory ICs exceeded the 5V shipment for the first time [21]. Since then, the demand for lower-output-voltage DC-DC converters starts to grow at a larger rate. According to the International Technology Roadmap for Semiconductors (ITRS), the Semiconductor Industry Association (SIA) roadmap, and Intel's Roadmap, the operating voltages for the new and future generation of microprocessors and ICs are in the range of lower than 1.5V and are expected to decrease below 1V while increasing the drawn current from the power supply from range of 50A to break the 100 amperes limit. All this while increasing the load (IC or microprocessor) current slew rate (change of current at faster rate or speed) and deceasing the allowed supply voltage deviation.

Table 1.1 shows example specifications for Intel microprocessors over the past few years [17-20], Table 1.2 shows example specifications from the ITRS-1999 Roadmap [31], while Table 1.3 shows the 2000/2001 Semiconductor Industry Association (SIA) roadmap summary [25,26]. It can be noticed from Table 1.1 that the required supply voltages dropped from 2.8V to lower than 1.6V from Pentium® II processor to 1.7GHz Pentium® 4 processor. In addition, from Table 1.1, the required supply currents increased from about 14A to above 50A as we go from the Pentium® II processor to the 1.7GHz Pentium® 4 processor.

| Parameter/Processor                       | Pentium® II | Pentium® III | Pentium <sup>®</sup> 4 |

|-------------------------------------------|-------------|--------------|------------------------|

|                                           | 233M        | 600M         | 1.4G                   |

| Clock Speed (Hz)                          | 2866M       | 550M         | 1. <b>5G</b>           |

|                                           | 300M        | 450M         | 1.7G                   |

|                                           |             | 2.05         | 1.56/1.7               |

| Core Voltage (V) min./max.                | 2.8         | 2.00         | 1.555/1.7              |

|                                           |             | 2.00         | 1.53/1.7               |

|                                           |             |              | 1.627/1.7              |

| Converter Voltage (V) min./max.           | -           | -            | 1.625/1.7              |

|                                           |             |              | 1.61/1.7               |

|                                           | 11.8        | 17.8         |                        |

| Core Current (A)                          | 12.7        | 17.0         | -                      |

|                                           | 14.2        | 14.5         |                        |

|                                           |             |              | 40.6                   |

| Converter Current (A)                     | -           | -            | 43.0                   |

|                                           |             |              | 52.7                   |

| Core Current Slew Rate ( $A/\mu s$ )      | 30          | 20           | -                      |

| Converter Current Slew Rate ( $A/\mu s$ ) |             | -            | 50                     |

Table 1.1: Example Specifications for Intel Microprocessors Over the Past Few Years

|                | Parameter/Year                | 2002 | 2003 | 2004  | 2005 |

|----------------|-------------------------------|------|------|-------|------|

| Supply         | Max.                          | 1.5  | 1.5  | 1.2   | 1.2  |

| Voltage<br>(V) | Min.                          | 1.2  | 1.2  | 0.9   | 0.9  |

| Maximu         | m Power with Heat Sink (W)    | 130  | 140  | 150   | 160  |

|                | Current (A)                   | 87   | 93   | 125   | 133  |

| Peak-to-Pe     | ak Voltage Tolerance (±3%) mV | <90  | <90  | <72   | <72  |

| (              | Chip Frequency (GHz)          | 2.1  | 2.49 | 2.952 | 3.5  |

Table 1.2: Example Specifications from the ITRS-1999 Roadmap

Table 1.3: Example Specifications from the 2000/2001 Semiconductor Industry

Association (SIA) Roadmap Summary

| Parameter/<br>Year              | 1993                                 | 1995             | 1999                                   | 2001                           | 2003                                  | 2005                                  | 2008                                   | 2011                | 2014                | 2016         |

|---------------------------------|--------------------------------------|------------------|----------------------------------------|--------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|---------------------|---------------------|--------------|

| Feature                         | 0.50                                 | 0.35             | 180                                    | 130                            | 100                                   | 80                                    | 70                                     | 50                  | 34                  | 22           |

| Size                            | microns                              | microns          | nm                                     | nm                             | nm                                    | nm                                    | nm                                     | nm                  | nm                  | nm           |

| Internal<br>Clock<br>Frequency  | 0.20<br>GHz                          | 0.30<br>GHz      | 0.75<br>GHz                            | 1.68<br>GHz                    | 2.31<br>GHz                           | 5.17<br>GHz                           | 6.74<br>GHz                            | 11.5<br>GHz         | 19.3<br>GHz         | 28.7<br>GHz  |

| Logic<br>Transistors<br>Density | $\frac{2}{10^6}$ $\frac{10^7}{cm^2}$ | $\frac{4}{10^6}$ | $\frac{6.6}{10^6}$ $\frac{10^6}{cm^2}$ | $\frac{13}{\frac{10^6}{cm^2}}$ | $\frac{24}{10^6}$ $\frac{10^6}{cm^2}$ | $\frac{44}{10^6}$ $\frac{10^6}{cm^2}$ | $\frac{109}{10^6}$ $\frac{10^6}{cm^2}$ | $\frac{10^6}{cm^2}$ | $\frac{10^6}{cm^2}$ | -            |

| Voltage                         | 5<br>Volts                           | 3.3<br>Volts     | 2.5<br>Volts                           | 1.2<br>Volts                   | 1.0<br>Volts                          | 0.9<br>Volts                          | 0.7<br>Volts                           | 0.6<br>Volts        | 0.5<br>Volts        | 0.4<br>Volts |

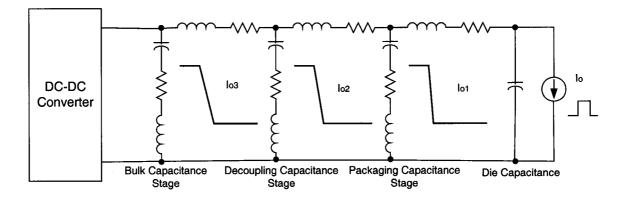

It must be noted that the output current slew required at the converter output is lower than the actual slew rate of the processors. For example, for Pentium® 4 processor, the processor current slow rate is  $510A/\mu s$ , which is translated to  $50A/\mu s$  at the converter output after sufficient capacitive decoupling [20]. This can be explained as shown in Figure 1.1, which shows a simplified general power delivery system model between a DC-DC converter and its load, such as a microprocessor load. In Figure 1.1, the power delivery system is modeled in three loops constructed by bulk capacitance stage, decoupling capacitance stage, packaging capacitance stage, capacitors and distribution prasatics and die capacitance and parasitics [1,17-20,60], which cause the current slew rate to be reduced as it approaches the converter output. Such model parameters are sometimes given, as in the case of the Pentium® processor design Guidelines [17-20]. The current slew rates at the processor output are expected to increase to approximately double or more of what it is now for Pentium® 4 processor ( $510A/\mu s$ ) in the near future, which will impose a current slew rate at the converter output of about double or more of  $50A/\mu s$ .

Figure 1.1: Simplified General Power Delivery System Model

Low supply voltage deviation during both steady-state and large-magnitude highslew-rate current transients is essential, and it is usually required to be less than 3 percent which becomes stricter as the supply voltages become lower. This means that lower than 30mV deviation will be required at voltages of about 1V or lower. The deviation can be undershot (lower than the nominal voltage) when there is a low-to-high (step-up) load transient, or can be overshot (higher than the nominal voltage) when there is a high-tolow (step-down) load transient. Undershot deviation will decrease the logic transistors speed and affect the signal-timing requirements [23], which will cause IC malfunctioning. Overshot deviation will affect the transistor junctions resulting in a transistor junction breakdown and causing IC destruction [23].

Another important specification is the power/current densities required for the converters that are used in ICs for communication devices and processors to reduce the converter size as it is the case for their loads. This imposes another requirement, which is higher efficiency, especially to reduce the heat generated from the losses and prevent thermal problems. Of course, the reduced cost will also keep playing an important role in such designs.

From Table 1.2 and Table 1.3, it can be noticed how low the future required voltages and how high the output supply currents are projected to be. As shown in Table 1.3 of the SIA 2000/2001 roadmap, output voltages are projected to be below 0.6V by year 2010, and below 0.4V by year 2016, all at increased current levels that are breaking the 100 amperes limit.

#### **1.3 Distributed Power Systems and the New Wave of On-Board DC-DC Converters**

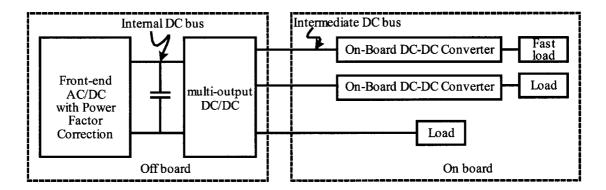

The strict requirements for powering new generations of ICs cannot be achieved directly from a centralized power supply because of distributed bus parasitics and losses. Therefore, Distributed Power System (DPS) is used to satisfy these requirements by using On-Board DC-DC converter located near the load [4,8,22,23]. Such DPS system block diagram is shown in Figure 1.2.

In recent years, DPS architectures have been extensively used in mainframe computer and communication systems. However, the basic concepts and design philosophies can be tailored for developing future computer system power supplies.

The off-board silver box is still kept to interface with the utility. An internal DC bus generally can be found in the bulk power supplies. The functions of this bulk power supply are to generate proper bus voltage for the on-board converters and to directly support some regular loads where the specs are relatively looser. To comply with the present standards, some low power level, low-cost AC-DC converters with power factor correction (PFC) and electrical isolation can be considered as options [32-39]. Normally, the on-board converter should be placed close to or packaged on the units that need strict regulated supplies to minimize the effects of parasitic parameters. If the load is far from its supply, the distribution wire or trace impedance will delay the ability to deliver the transient load current, forcing the supply voltage to deviate outside its upper or lower limits, and will result in large distribution losses especially at high currents. Hence, on-board converters take advantage of their closeness to their loads.

Another reason of adapting the DPS architectures is to realize modular openarchitecture systems, which require modular distributed power supplies for applications such as hubs, routers and signal and data processing in general [22]. Improved reliability and redundancy are also advantages of DPS architectures [22].

Several names are used for the on-board DC-DC converters, usually indicating the application it is used for. In communications applications for example, they are usually called Point-Of-Load (POL) converters, while Voltage-Regulator-Modules (VRMs) name is used in computers' microprocessor applications.

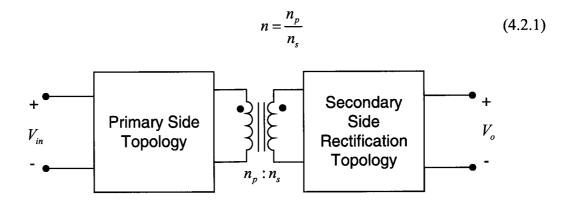

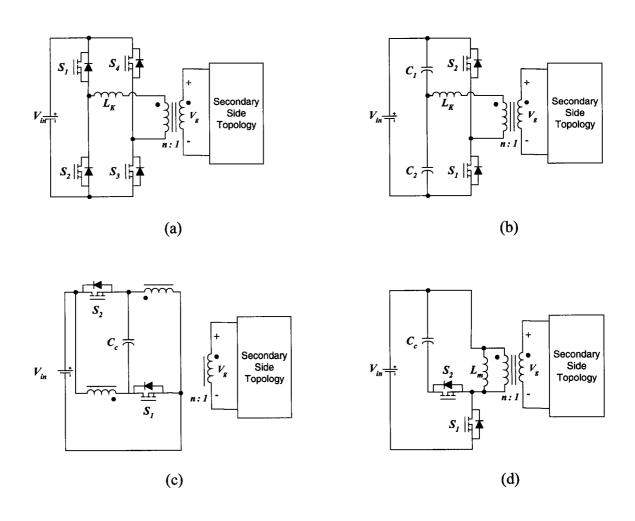

Figure 1.2: Example of Distributed Power System (DPS) Architecture Block Diagram

The on-board DC-DC converters can be isolated or non-isolated depending on the application they are used for. Isolated converters have an isolation transformer that is used to help in stepping the voltage down from its primary-side to its secondary-side, in addition to the electrical isolation it provides. Such isolated converters are usually used in communication system applications that, for example, have an input voltage range of  $36V \sim 75V$  (48V nominal). They are usually referred to as POL converters in such applications and they are such as symmetrical and asymmetrical half-bridge, full-bridge, active clamped forward, flyback forward and push-pull [4,7,40-52]. The secondary side of the isolated topology can have different schemes such as forward, center-tapped or current-doubler as discussed in [4]. Non-isolated converters have no isolation transformer and they are usually buck topology derived [4,6,7,10,15,53-56]. Such converters are used in computer's VRM applications with an input voltage range of  $5V \sim 12V$ . However, future VRMs may be isolated and non-isolated.

Moreover, DC-DC converters can be hard-switched or soft-switched [51,52,56-61]. The idea behind the concept of soft-switching is to shape the voltage or the current waveform by creating a resonant condition to force the voltage across the switching device to drop to zero before turning it ON or to force the current through the switching device to drop to zero before turning it OFF. By doing this, a Zero-Voltage Switching (ZVS) or a Zero Current Switching (ZCS) can be achieved. While in hard-switching, non of the both parameters, i.e., the voltage cross and the current through the switch, are zero, causing power losses during switching ON and OFF, i.e., switching losses. These switching losses become more significant as the switching frequency increases.

#### **1.4 Driving Market Applications and Research Driving Forces**

On-board converter applications include any IC that needs special powering requirements in terms of voltage, current, current slew rate, voltage deviation, etc. Such applications, which were discussed earlier in this chapter and are summarized here, include:

1. New generation of microprocessors.

2. Communication systems and equipment.

3. High-speed Integrated Circuits (ICs) especially those used in consumer electronics and hand-held electronic devices.

Moreover, as a summary, the future on-board DC-DC converters main design and research driving forces include:

- 1. Lower voltages.

- 2. Higher currents.

- 3. Faster transient response to high load current slew rates with larger magnitudes.

- 4. Lower output voltage deviation.

- 5. Higher power/current density (smaller size).

- 6. Higher efficiency and better thermal management with no heatsink.

- 7. Improved Electromagnetic Compatibility (EMC) and reliability.

- 8. Lower cost.

### **1.5 Dissertation Outlines**

The next chapter briefly discuses the steady-state and transient analysis and design equations of low-voltage, high-current, fast-transient DC-DC on-board DC-DC converters. Chapter 3 presents an interleaved (multiphase) parallel-connected converters control method for a multiphase voltage-mode hysteretic controlled VRM with current sharing technique. Chapter 4 reviews some common isolated topologies and presents a control method for the half-bridge DC-DC converter, namely, Duty-Cycle-Shifted (DCS) control. Chapter 5 presents a control method for half-bridge topology, to be called Alternated Duty Cycle (ADC) control. Chapter 6 presents an interleaving method for isolated topologies where the secondary side switches operate at lower switching frequency than the primary side switches to improve the efficiency and the transient response. Meanwhile, both primary and secondary sides of the isolation transformers are connected in parallel allowing sharing of currents at both primary and secondary sides. Chapter 7 presents a Coupled-Inductors Current-Doubler (CICD) topology. Chapter 8 presents a non-isolated Half-Bridge-Buck (HBB) topology. In Chapter 9, a brief review comparison between major control methods will be provided, followed by a presentation

for initial work on a control method concept and technique. Chapter 10 discusses digital control as a candidate for future DC-DC converters and presents digital system structure, advantages, disadvantages and initial experimental setup. Moreover, an initial concept for future work on digital control is presented, namely, the Maximum Efficiency Point Tracking (MEPT) method, which can be used to optimize the switch's dead time control issue by using adaptive control to achieve better efficiency and converter performance. Finally, Chapter 11 summarizes this work and presents future research directions.

## **CHAPTER 2**

# **DESIGN AND ANALYSIS OF ON-BOARD DC-DC CONVERTERS**

#### **2.1 Introduction**

As mentioned in the previous chapter, the on-board DC-DC converters can be isolated and non-isolated. The non-isolated buck topology is the simplest DC-DC topology and the most common used, especially nowadays in VRM applications where the input voltage is 5V or 12V. Studying the behavior and analysis of buck topology at both steady-state and transient conditions is usually sufficient to understand and to have a general feeling about isolated and non-isolated topologies, especially that most of the isolated and non-isolated DC-DC topologies are either buck derived, behave like buck topology, and/or can be equivalently transformed to buck topology format.

In this chapter, steady-state and transient analysis and design equations will be presented for a better understanding of the parameters' effect on such low-voltage, highcurrent, fast-transient DC-DC on-board DC-DC converters including parasitics. Nonisolated buck topology is used as example.

#### 2.2 Ideal DC-DC Buck Topology

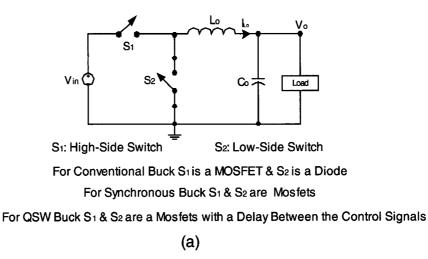

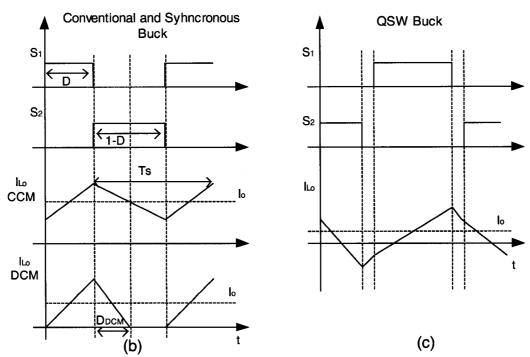

Figure 2.1(a) shows the ideal buck DC-DC converter used along with the main switching waveforms shown in Figure 2.1(b) and 2.1(c) for different types of operation.

In the conventional buck topology, the upper-side switch  $S_1$  is a MOSFET (Metal-Oxide Semiconductor Field-Effect Transistor), while the low-side switch  $S_2$  is a diode. However, the low-side switch is replaced by a MOSFET in low-voltage, high-current applications because the current available MOSFETS have lower ON-state resistance to reduce the conduction loss. At this case, when both  $S_1$  and  $S_2$  are MOSFETS, the topology is called Synchronous Buck and  $S_1$  and  $S_2$  are called Synchronous Rectifiers (SRs).

In the conventional buck topology, where  $S_2$  is a diode, depending on the value of the output inductor  $L_o$  as will be shown later, the converter may operate in Continuous Conduction Mode (CCM) or Discontinuous Conduction Mode (DCM) as shown in Figure 2.1(b). When the inductor value is smaller than a certain limit, the inductor current will discharge quickly when  $S_2$  is ON, before turning ON  $S_1$  to start charging up., and since the diode can conduct in one direction, a discontinuity will occur when the inductor current drops to zero and goes negative, then DCM mode occurs. When  $L_o$  value is large enough, the current will be always larger than zero and the converter will operate in CCM.

However, when SRs are used for both buck topology switches, there is no real DCM mode since the MOSFET body-diode will carry the inductor current when it goes

negative, resulting in what is called the Quasi-Square-Wave (QSW) buck topology as in [7].

In the QSW buck converter, a dead time delay is designed between the control signals of the two switches as shown in Figure 2.1(c). This delay results in both switches having soft-switching operation. Note that the body diode of the high-side switch is ON in the first delay period after turning  $S_2$  OFF, while the body diode of the low-side switch is ON in the second delay period after turning  $S_1$  OFF. As discussed in [7], faster transient response is achieved using QSW buck, since the used output inductor value is smaller. However, this causes the converter to have higher output current ripple and lower efficiency compared to the synchronous buck operating in CCM mode.

#### **2.3 Basic Design Equations and Considerations**

The design of a low-output-voltage converter requires detailed knowledge and understanding of the system as well as careful selection of the design parameters such as the output inductor, the output capacitor and the switching frequency.

In this section, steady-state and transient equations and considerations are discussed, taking the buck topology as an example, since this topology behavior represents most or all of the topologies used for this application, as mentioned earlier in this chapter. Some basic equations, assuming ideal components, are as follows:

1. Rate of the output inductor current change during step-up transient:

$$\frac{di_{L_o}}{dt} \approx \frac{V_{in} - V_o}{L_o}$$

(2.3.1)

14

Figure 2.1: (a) Ideal Buck topology, (b) Switches Drive and Output Inductor Current Waveforms for CCM and DCM Operations and (c) Switches Drive and Output Inductor Current Waveforms for QSW Buck

where:

$$\frac{di_{L_o}}{dt}$$

is the output inductor current rate of change (A/s)

- $V_{in}$  is the average input voltage (V).

- $V_o$  is the average output voltage (V).

- $L_o$  is the output inductor value (H).

- 2. Rate of the output inductor current change during step-down transient:

$$\frac{di_{L_o}}{dt} \approx \frac{-V_o}{L_o} \tag{2.3.2}$$

3. Output Voltage Gain/Current Gain:

$$D \approx \frac{V_o}{V_{in}} = \frac{I_{in}}{I_o}$$

(2.3.3)

where:

D is the switching duty ratio or duty cycle.

$I_{in}$  is the average input current.

- $I_o$  is the average output current.

- 4. The critical (must be larger than this value) output inductor value to operate in CCM:

$$L_{o,crit.} \approx \frac{V_o \max(D, 1-D)}{2I_o f_s}$$

(2.3.4)

where:  $I_o$  is the output load current.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

5. Output current ripple (inductor current ripple):

$$\Delta I_{Lo,ripple} \approx \frac{V_o \max(D, 1-D)}{L_o f_s}$$

(2.3.5)

where:  $\Delta I_{Lo,ripple}$  is the output inductor current ripple (A).

6. Output ripple voltage:

$$\Delta V_o \approx \frac{V_o \max(D, 1-D)}{8L_o C_o f_s^2}$$

(2.3.6)

where:  $C_o$  is the output capacitance.

7. Critical output capacitor value required to satisfy the required output voltage deviation  $\Delta V_o$  during the transient from [7] assuming ideal power stage and control:

$$C_{o,crit.} \ge \frac{1}{2} \frac{\Delta I_o}{\Delta V_o} \left( \frac{L_o}{V_o} - \frac{1}{di_o/dt} \right)$$

(2.3.7)

where:

$\Delta I_o$  is the maximum load current transient magnitude.

$\frac{di_o}{dt}$  is the output load current slew rate.

8. Critical input capacitor value required to satisfy the required input current slew rate

[7]:

$$C_{in,crit.} \ge \frac{1}{2} \frac{P_o^2}{\left(\frac{di_{in}}{dt}\right) (\Delta V_{in}) (V_{in})^2}$$

(2.3.8)

where:

$P_o$  is the output power.

$$\frac{di_{in}}{dt}$$

is the input current slew rate.

As mentioned before, one of the strict requirements of the POL and VRM onboard DC-DC converters is the fast transient response at a very high output current slew rate. This requires that the output inductor  $L_o$  to be is designed as small as possible, as noted from Equations (2.3.1), (2.3.2) and (2.3.7), at both step-up and step-down transients, assuming that the closed loop controller has sufficient bandwidth (fast enough).

Unfortunately, using small  $L_o$  to achieve faster transient response will cause the output voltage ripple to increase as shown in Equation (2.3.5) and will push the converter operation towered the DCM mode as in Equation (2.3.4), leading to lower efficiency because of increased conduction losses caused by the increased *rms* (root-mean-square) current value. Therefore, lower  $L_o$  will require the switching frequency to be increased.

Here, the trade off with efficiency comes out to the picture. The higher the switching frequency, the lower the efficiency is, since the switching devices have higher switching losses as the switching frequency is increased. Therefore, the selection of the switching devices and the advancement made in switching devices technology are very important. Increasing the switching frequency will improve the transient response, and the compensated control loop bandwidth can be increased and also will reduce the output voltage ripple.

Another way to decrease the output voltage ripple is to increase the converter output capacitor ( $C_o$ ) as in Equation (2.3.6). However, this capacitor will be very large, especially for future requirements, which is not preferred in the practical designs especially for the VRM and POL applications where the space is limited.

In practical designs, the loop gain crossover frequency is usually selected to be less or in the range of  $0.15f_s \sim 0.3f_s$ . Therefore, the higher the switching frequency, the faster the closed loop, the smaller the required value of  $C_o$  to keep the output voltage ripple within the required limits and the smaller  $L_{o,crit}$  required to operate in CCM to achieve less output current ripple.

Another conclusion that can be drawn from Equations (2.3.1) and (2.3.2) is that in low voltage output converters, the inductor current slew rate during step-down transients is much lower than it is for step-up transients since the voltage across the inductor is much lower ( $V_o$  compared to  $V_{in} - V_o$ ), causing the voltage deviation during step-down transients to be larger than it is during step-up transients, resulting in asymmetric transients responses, that becomes more sever as the output voltage becomes smaller.

Another requirement is the high converter input current slew rate, which requires a large converter input capacitor  $(C_{in})$  to be used. From Equation (2.3.8), it can be noted that in order to decrease the size of  $C_{in}$ , the input voltage,  $V_{in}$ , must be increased. This means that a DPS with high-voltage bus will require lower  $C_{in}$ , which is an advantage for the isolated converters over the non-isolated ones. Another advantage of isolated converters is that an isolation transformer can be used to step-down the voltage, resulting in a larger duty cycle as compared to the non-isolated converters. In non-isolated converters, the duty cycle becomes smaller as the output voltage becomes smaller as given by Equation (2.3.3). The smaller the duty cycle, the larger the input peak current, which increases the conduction losses because the *rms* current value increase and the more asymmetric the transient response is.

It must be noted that high power density is an important requirement and must be taken into consideration during the design, which place a restriction on the component value selection such as  $C_o$  and  $C_{in}$  and on the topology selection.

As can be seen from the above analysis, the design of POL and VRM encounters many requirements and restrictions, all of which need to be taken into consideration.

#### 2.4 Load Transients and Converter Response

As mentioned before, on-board converters loads, such as microprocessors, can switch from one load level (output current) to another with large magnitude and at fast transient slew rate. These load transients cause large converter output voltage deviation. Since the converter's output voltage is small, this voltage deviation percentage can be large and unacceptable. Current levels are also too high and small component's resistances can cause large  $I^2R$  power losses. Moreover, the converter, its component, and closed-loop control cannot be considered ideal anymore.

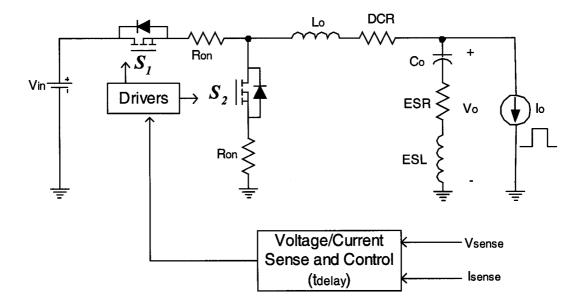

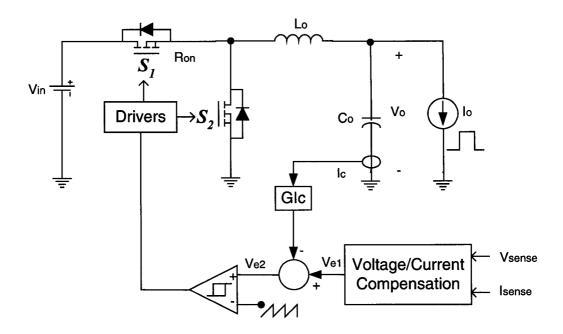

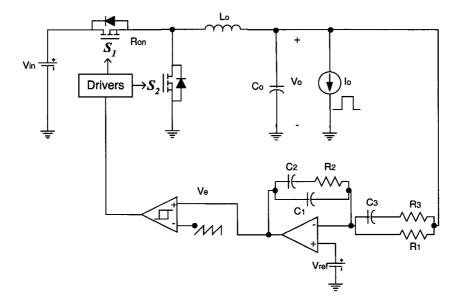

Figure 2.2 shows a buck converter with main component parasitics consideration, where:

$R_{on}$  is the MOSFET ON-state resistance ( $\Omega$ ).

DCR is the output inductor equivalent DC Resistance ( $\Omega$ ).

*ESR* is the Equivalent Series Resistance of the output capacitors ( $\Omega$ ).

ESL is the Equivalent Series Inductance of the output capacitors (H).

$t_{delay}$  is the total closed loop controller delay time until the appropriate switch is turned ON or OFF (s).

$V_{sense}$  and  $I_{sense}$  are the voltage(s) and current(s) sensed signals for control and protection.

Figure 2.2: Buck Converter with Main Components Parasitics Consideration

Because of the ESR and ESL of the output capacitance, the output voltage is given by:

$$v_o(t) = v_{C_o}(t) + v_{ESR}(t) + v_{ESL}(t)$$

(2.4.1)

Equation (2.4.1) should be considered especially for transient analysis since the average voltages drop across the ESR and the ESL are not zero during transients.

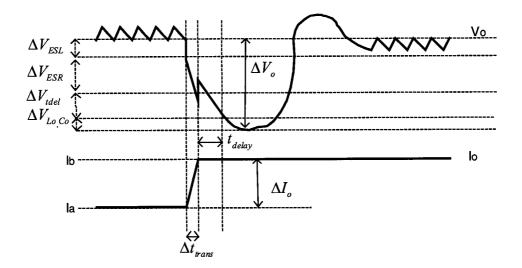

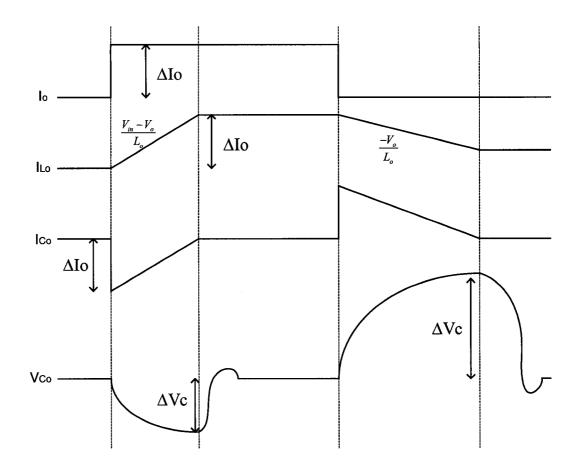

Figure 2.3 shows a load step-up transient output current and voltage waveforms as an example. The output current switches up by  $\Delta I_o = I_a - I_b$ ,  $I_b > I_a$  magnitudes during  $\Delta t_{trans}$  time causing output voltage deviation  $\Delta V_o$ .

Figure 2.3: Example of Step-Up Load Transient Output Current and Voltage Waveforms

From Figure 2.3, the output voltage transient response waveform can be divided into four transitions or parts before it settles back to its nominal value, as follows:

1. The ESL voltage transition  $\Delta V_{ESL}$ :

This voltage drop across the output capacitor ESL occurs because of the output load current rate of change and is given by:

$$\Delta V_{ESL} \approx ESL \cdot \frac{di_o}{dt_{trans}} = ESL \cdot \frac{\Delta I_o}{\Delta t_{trans}}$$

(2.4.2)

22

Equation (2.4.2) shows that this voltage increases as the output current slew rate and magnitude increase, and of course it increases as the ESL value increases. This fast, high-frequency voltage spike usually can be ignored, since it will be filtered out by the high frequency decoupling capacitors before the load.

2. The ESR voltage transition  $\Delta V_{ESR}$ :

This is the second transition that occurs because of the ESR instantaneous resistive voltage drop and is given by:

$$\Delta V_{ESR} = ESR \cdot \Delta I_{a} \tag{2.4.3}$$

Equation (2.4.3) shows that this voltage is directly proportional to the ESR value and the transient current magnitude. This voltage deviation part is important and cannot be ignored.

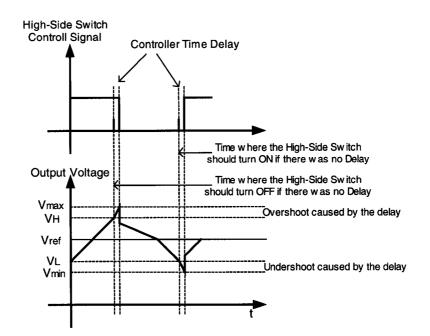

3. The closed loop control delay transition voltage:  $\Delta V_{tdel}$

This voltage is caused by the closed loop control delay time, which is the total delay time because of the controller bandwidth delay and control logic component delays until the time when the appropriate switch is turned ON or OFF. This voltage is proportional to parameters including the total loop delays time  $t_{delay}$ , the load current step magnitude  $\Delta I_o$  and the output filter characteristics  $L_o/C_o$ .

$t_{delay}$  is a function of the switching frequency, controller bandwidth and controller and drivers logic speed. Larger controller bandwidth, which means smaller  $t_{delay}$ , will result in smaller  $\Delta V_{tdel}$ . The other option to reduce  $\Delta V_{tdel}$  is to increase  $C_o$ , which is not a practical solution because of the space limitations, cost and the amount of  $C_o$  to be used are usually restricted to a certain maximum amount for each application. 4. The power stage output filter transition voltage  $\Delta V_{Lo,Co}$ :

This voltage deviation is mainly a function of the power stage output filter consisting of  $L_o$  and  $C_o$ . It is directly proportional to  $L_o$  and inversely proportional to  $C_o$ , which means either smaller  $L_o$  or/and larger  $C_o$  will result in smaller deviation. This deviation is also directly proportional to  $\Delta I_o^2$  and inversely proportional to the voltage across  $L_o$ .

If the converter were open loop, this voltage deviation will be equal to the multiplication of the current magnitude change by the output filter characteristics impedance as follows [27]:

$$\Delta V_{Lo,Co,OL} = \Delta I_o \cdot Z_o = \Delta I_o \cdot \sqrt{\frac{L_o}{C_o}}$$

(2.4.4)

Assuming ideal components and neglecting the current and voltage ripples, it can be shown that the maximum output voltage  $\Delta V_{Lo,Co}$  deviations at both step-down and stepup load transients are given by [27]:

$$\Delta V_{Lo,Co} = \frac{L_o}{C_o} \cdot \frac{\Delta I_o^2}{2V_{Lo}}$$

(2.4.5)

Where:  $V_{Lo}$  is the voltage across the output inductor  $L_o$ , and it is ideally equal to  $V_{in} - V_o$  at load step-up transients and equal to  $-V_o$  at load step-down transients.

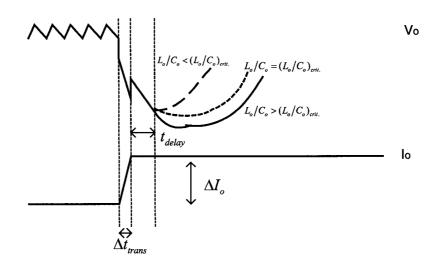

From equation (2.4.5), it is evident that reducing the ratio  $L_o/C_o$  will result in lower  $\Delta V_{L_o,C_o}$ . However, the second transition  $\Delta V_{ESR} = ESR \cdot \Delta I_o$  is still there and has to be considered. Reducing the  $L_o/C_o$  ratio by deceasing  $L_o$ , for example, will lower  $\Delta V_{Lo,Co}$  at the expense of increasing the current ripple and lowering the efficiency, and it may not lower  $\Delta V_{ESR}$ . Therefore, there is a minimum critical ratio  $(L_o/C_o)_{crit.}$  where  $\Delta V_{ESR}$  is equal and starts to be larger than  $\Delta V_{Lo,Co}$ . This is given by:

$$\left[\frac{L_o}{C_o}\right]_{crit.} = \frac{ESR \cdot V_{Lo}}{\Delta I_o}$$

(2.4.6)

The critical ratio from Equation (2.4.6) is smaller, which means smaller  $L_o$  or/and larger  $C_o$  is required, as  $\Delta I_o$  is getting larger. This means that the larger transient current magnitude change will strongly affect future designs. For  $L_o/C_o < (L_o/C_o)_{crit.}$ , the voltage deviation will not be reduced further, while the current ripple will increase and the efficiency will decrease, resulting in bad design. Hence,  $L_o/C_o$  should be selected to be equal, as much as possible, to  $(L_o/C_o)_{crit.}$ . This behavior can be described as shown in Figure 2.4.

Figure 2.4: Example of Step-Up Load Transient Output Current and Voltage Waveforms

at Different  $L_o/C_o$  Ratios

### **CHAPTER 3**

# MULTIPHASE VOLTAGE-MODE HYSTERETIC CONTROLLED DC-DC CONVERTER WITH CURRENT SHARING

#### **3.1 Introduction**

In this chapter, the interleaved (multiphase) parallel-connected converters method will be reviewed, followed by a presentation for a multiphase voltage-mode hysteretic controlled VRM with new current sharing [28,30,54]. Detailed theoretical analysis is provided and supported by simulation and experimental results for a specific design example.

#### 3.2 Interleaving Versus High Switching Frequency and Smaller Output Inductor

A way to reduce the output current and voltage ripples and to improve the transient response is to increase the switching frequency. Unfortunately, increasing the switching frequency will lower the converter's efficiency. Another way to reduce the output current and voltage ripples is to decrease the output inductor value, which unfortunately will result in slower transient response.

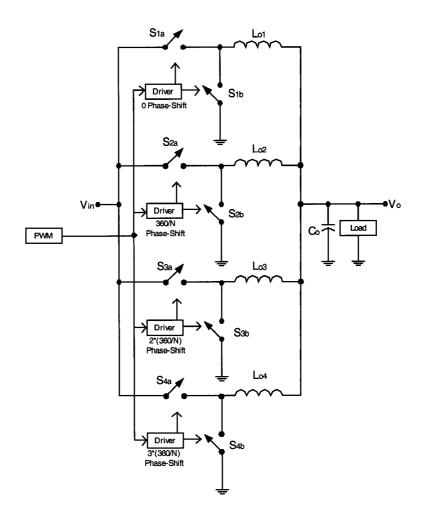

Here it comes the interleaving or multiphase technique [7,28,30,54,59,60]. This technique is implemented by paralleling several out-of-phase driven modules, as shown

in Figure 3.1 as an example for the synchronous buck topology with four phases. Figure 3.2 shows main waveforms of Figure 3.1.

Figure 3.1: Four Interleaved (Multi-Phase) Synchronous Buck Converters

Figure 3.2: Main Waveforms for Four Interleaved Buck Converters (90° Phase Shift Between the Phases)

The phase shift between the phases is  $360^{\circ} / N$ , where N is the number of the interleaved modules and the phase switch duty cycle is a function of the  $V_o/V_{in}$  ratio. The effective output inductor will be reduced as a result of paralleling. The effective output inductor, assuming all output inductors are equal with a value  $L_o$ , is given by:

$$L_{o,eff} = \frac{L_o}{N} \tag{3.2.1}$$

From Equation (3.2.1),  $L_{o,eff}$  is lower than the output inductor per phase, which results in a faster transient response as provided in Equations (2.3.1) and (2.3.2).

Moreover, the effective output current and ripple frequency  $f_{o,ripple}$  is N times the switching frequency of each of the phase shifted modules  $(f_s)$ . This yields:

$$f_s = \frac{f_{o,ripple}}{N} \tag{3.2.2}$$

Equation (3.2.2) shows that each interleaved phase is switched at lower switching frequency compared to a single-phase (non-interleaved) module for the same output ripple frequency and magnitude. Therefore, higher output ripple frequency can be achieved by interleaving while switching each phase at a lower frequency. This will result in a faster transient response and lower output current and voltage ripples as from Equations (2.3.5) and (2.3.6).

From the above, several design options are available to satisfy certain requirements. For example, to improve the transient response or to decease output ripple, instead of decreasing the inductor or increasing the ripple frequency, the number of phases can be increased. This results in lower effective output inductance and higher output ripple frequency as from Equations (3.2.1) and (3.2.2). However, it must be noted that the output capacitor value must still be able to maintain the maximum allowed output voltage deviation requirements during transients. Another important advantage of the interleaving technique is that the load current is shared (divided) between the interleaved phases.

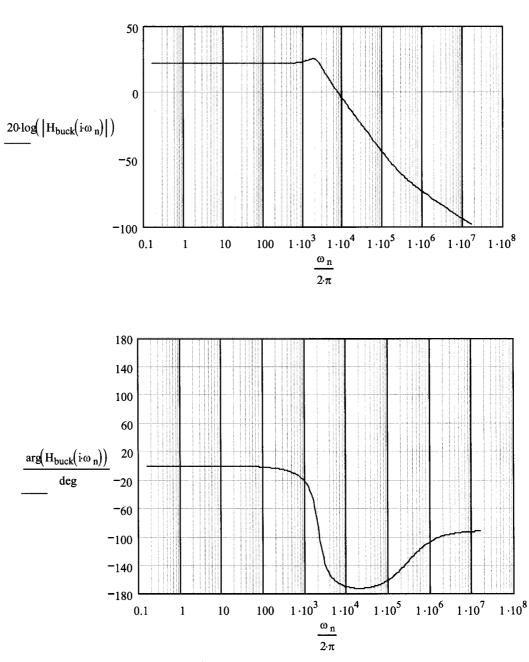

However, the feedback control loop is still a constraint that limits the speed of the transient response in interleaved converters, especially that the compensated feedback loop bandwidth is usually limited to the range of 20 percent  $\sim$  30 percent of the switching frequency.

#### 3.3 The Voltage-Mode Hysteretic Control Concept

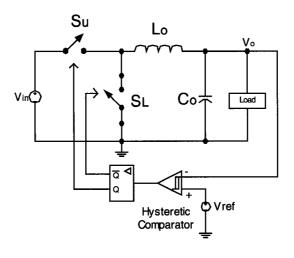

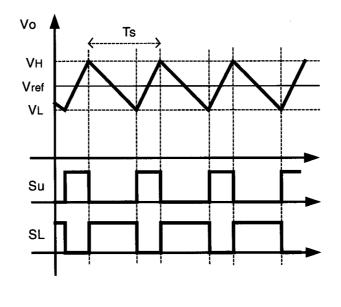

The Voltage-Mode Hysteretic Control [58,61] is to directly track the output voltage of the converter between an upper limit  $(V_H)$  and a lower limit  $(V_L)$  around a reference voltage  $(V_{ref} = V_o)$  to turn ON or OFF the appropriate switches, with no feedback compensation.

Figure 3.3 shows a simplified schematics and waveforms for a hysteretic controlled buck converter. The controller will turn the high-side switch ON and turn the low-side switch OFF if the output voltage drops bellow  $V_L$ , and it will turn the high-side switch OFF and turn the low-side switch ON if the output voltage exceeds  $V_H$ , keeping the output voltage regulated around  $V_{ref} = V_o$ .

The hysteretic controller keeps following the output voltage to produce the required control signals for the switches. If output-current or input-voltage transients occur, the hysteretic controller will keep the appropriate switches ON and OFF until it corrects the output voltage.

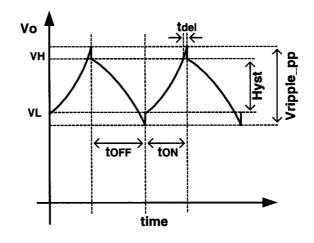

The feedback comparator and logic delays cause the actual output voltage waveform to be as illustrated in Figure 3.4. The extra small ripple caused by the delay must be considered in the design.

(a)

(b)

Figure 3.3: A Simplified Schematics and Waveforms for a Voltage-Mode Hysteretic-

Controlled Buck Converter

In addition to its advantage of controlling the ripple, the hysteretic control also does not need loop compensation, and the output voltage ripple becomes relatively independent of the output capacitor value. In fact, both the capacitor and the inductor values can be selected more freely now to satisfy only the transient requirements without taking into consideration the output voltage ripple requirements since the operation of the hysteretic control can take care of it.

Also, the response of this type of controller is fast, since the switches' control signals are derived directly from the output voltage ripple waveform. This allows the controller to respond within one switching cycle.

Figure 3.4: Actual Output Voltage Ripple Waveforms for a Voltage-Mode Hysteretic-

Controlled Converter

# 3.4 Multiphase Voltage-Mode Hysteretic Controlled DC-DC Converter with Current Sharing

Both the interleaving (multiphase) and the single-phase voltage-mode hysteretic control techniques can reduce the output voltage ripple. However, the overshoot and

undershoot requirements during large magnitude transients still have to be investigated. It is known that to obtain low output overshoot, the multiphase on-board converters require a design of high-performance feedback control that can also provide current sharing [7, 59,60]. Hence, even though the interleaving technique reduces the output voltage ripple and helps in achieving faster current transient response, a careful control design and/or increase in the output capacitance size will be needed to satisfy the maximum overshoot and undershoot limits during large load transients.

In the single-phase hysteretic voltage-mode control technique, the hysteretic window can be set to a certain level such that the controller will respond quickly to load transients and will correct the voltage before deviating from the maximum allowed overshoot and undershoot. Even though the output capacitor size still plays an important role here, its size is reduced significantly because of the hysteretic window.

On one hand, voltage-mode hysteretic control has many advantages over several other control techniques including simplicity, no feedback loop compensation is needed, near instantaneous response to load transients and no limitations on the switches' conduction time. On the other hand, the interleave technique has several advantages such as the high frequency output voltage ripple with lower switching frequency, ripple cancellation, current division (sharing) between the phases, which allows higher current carrying capability, and also fast transient response which is limited by the feedback control loop. From this summary of advantages, it is clear that combining the voltage-mode hysteretic control technique with the interleave technique will result in a VRM that has the advantages of both techniques [28,30,54].

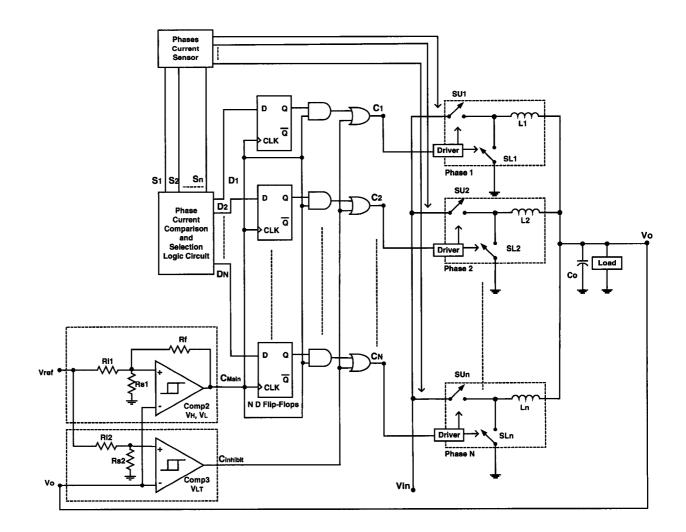

However, multiphase converters are required to have high-performance currentsharing functionality in order to keep an almost equal division of the load current between the phases at all load conditions in addition to the voltage regulation [4,7,28,30, 54,59,60].

A multiphase voltage-mode hysteretic-controlled DC-DC converter with current sharing is presented with theoretical and experimental verification. In the next section, the multiphase voltage-mode hysteretic control method will be discussed. Section 3.6 presents the concept of the proposed current sharing method and how it is applied to a two-phase interleaved voltage-mode hysteretic controlled DC-DC converter. In Section 3.7, the proposed method will be generalized for N interleaved phases. The theoretical analysis with key design equations is discussed in Section 3.8. The simulation and experimental results are given in Sections 3.9 and 3.10. Finally, the conclusion is given in Section 3.11.

#### 3.5 Multiphase Voltage-Mode Hysteretic Control

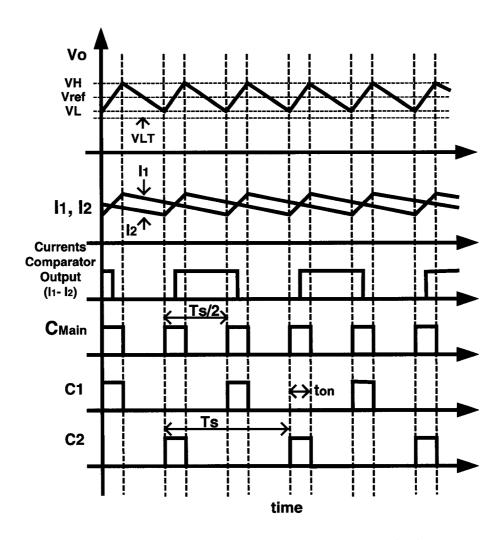

When applying the hysteretic voltage-mode control to interleaved buck converters, one must note that: 1) the derived control signal from the output ripple (hysteretic control) must be frequency divided while keeping the same control-signal ON-time (interleaving) and 2) during transients, multiphase control operation must be disabled so that all the phases' switches will switch ON and OFF at the same time. The first note is to keep the switching frequency low for the same output voltage ripple so that the interleaving can be achieved, whereas, the second note is to achieve faster transient response and synchronization between the phases during transients. Figure 3.5 shows the basic block diagram of N interleaved synchronous buck phases with voltage-mode hysteretic control, while Figure 3.6 shows an example of control signals for two interleaved phases (N = 2) for illustration purposes. It must be noted that the voltage waveform  $V_o$  of Figure 3.6 is true only when the voltage ripples across the output capacitor and its Equivalent Series Inductance (ESL) are zero.

Figure 3.5: Block Diagram of N Interleaved Buck Converters with Voltage-Mode Hysteretic Control

Figure 3.6: Example of Control Signals for Two Interleaved Phases (N=2)

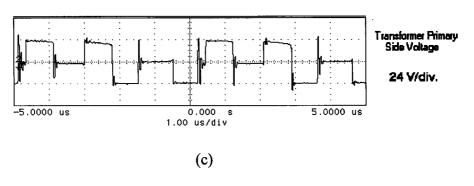

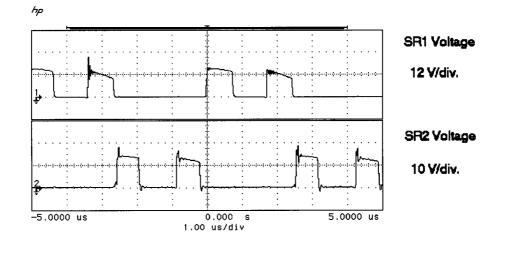

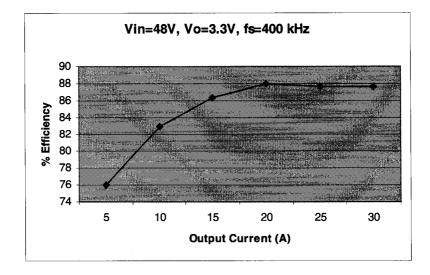

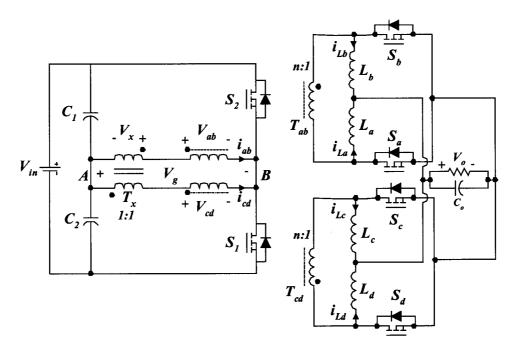

The main control signal  $(C_m)$  is generated by comparing the output voltage to a minimum value  $(V_L)$  and a maximum value  $(V_H)$ , forming a hysteretic window. Then, the generated pulses are distributed between the phases interchangeably so that only one phase high-side switch is ON at a time and all the other switches are OFF at that time. This will generate the required multiphase control-signals  $C_1, C_2, ..., C_N$ .